Изобретение относится к автоматике и вычислительной технике, в частности к устройствам для обработки даннык, и может быть использовано в различных информационно-измерительных и управляющих системах, где необходимо перемножать последовательности чисел, квантованных по уровню и по времени.

Цель изобретения - расширение функциональных возможностей за счет возможности выполнения умножения.

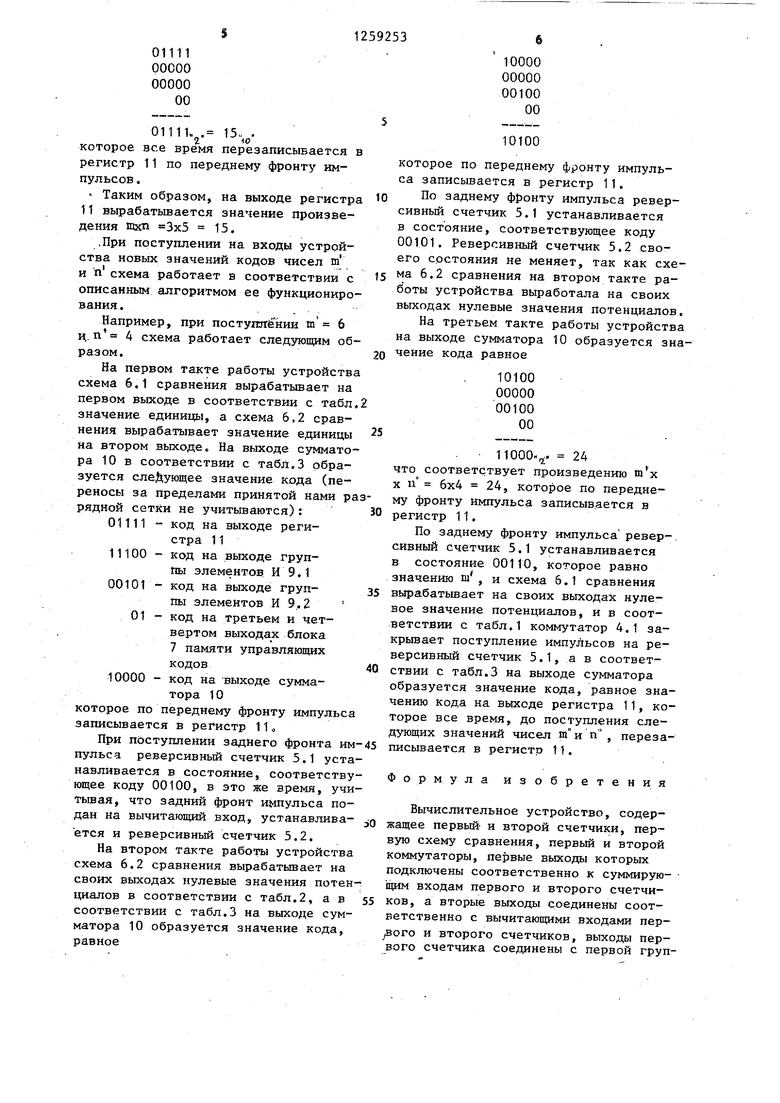

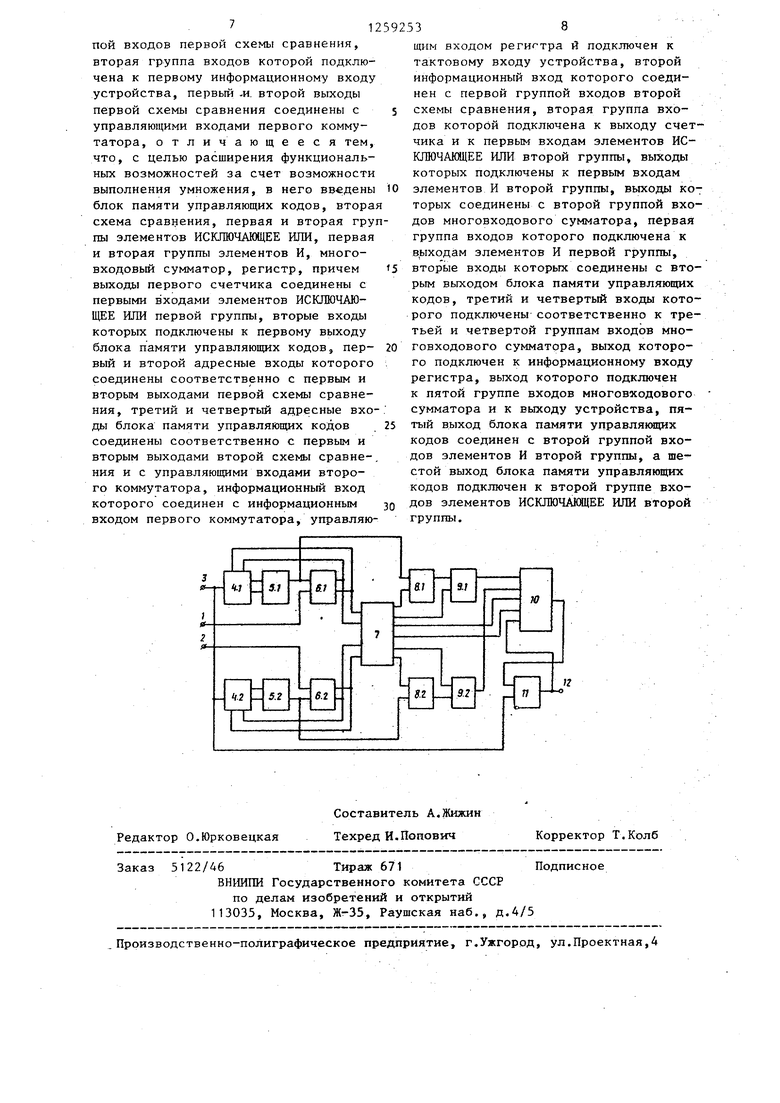

На чертеже представлена функциональная схема предлагаемого устройства.

Устройство содержит первый и второй информационные входы 1 и 2, тактовый вход 3, первый -и второй комму- таторы 4.1 и 4.2, первый и второй реверсивные счетчики 5.1. и 5.2 импульсов, первую и вторую схемы 6.1. и 6.2 сравнения, блок 7 памяти управляющих кодов, первую и вторую группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8.1 и 8.2, первую и вторую группы элементов И 9.1 и 9.2 многовходовый сумматор 10, регистр 11 и выход 12 устройства.

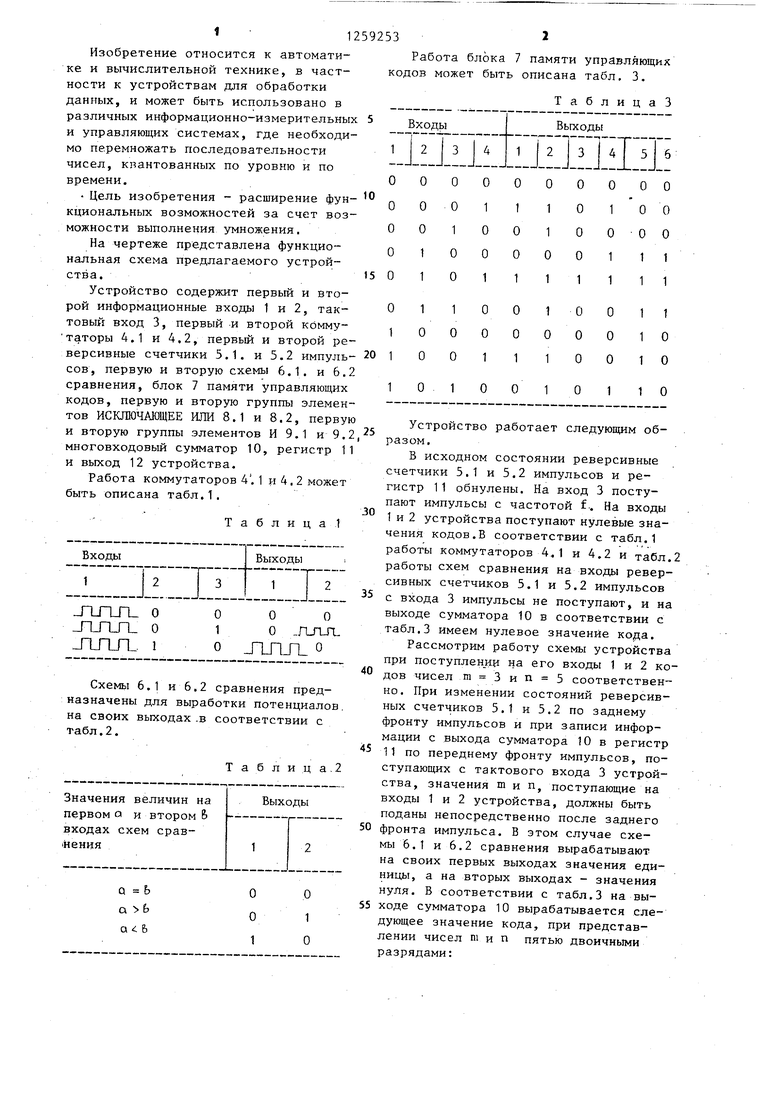

Работа коммутаторов 4. 1 и 4, 2 может быть описана табл.1.

Т а б л и ц а 1

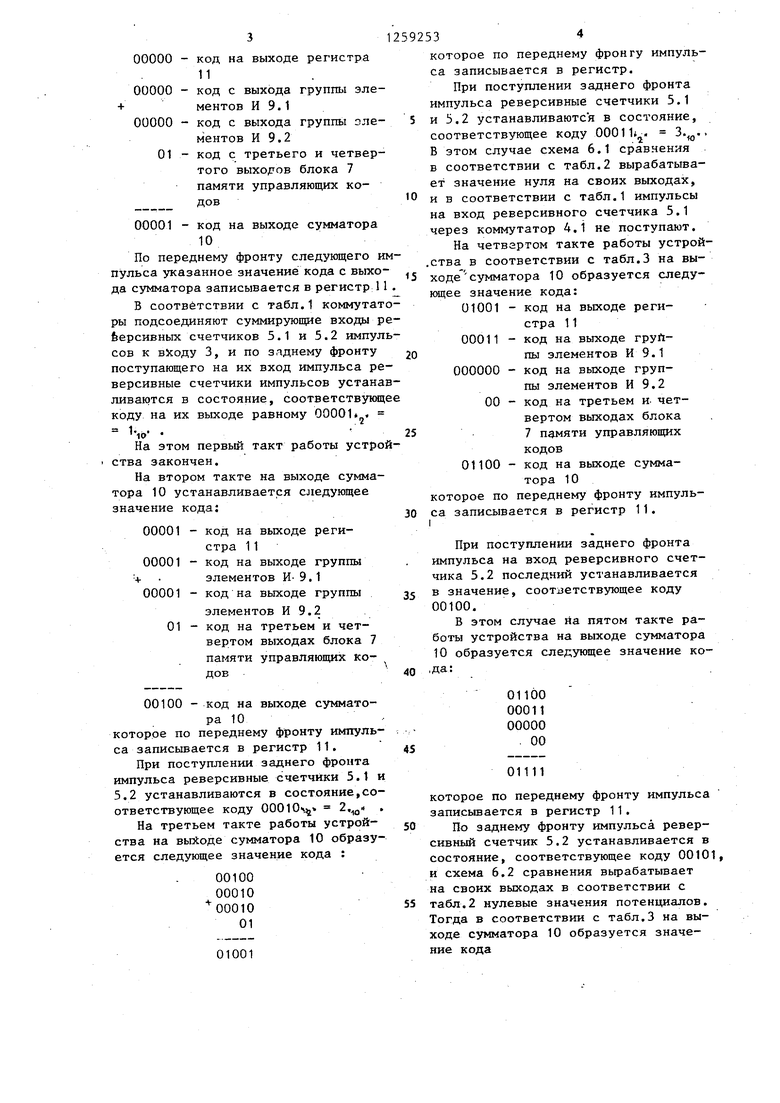

Работа блока 7 памяти управляющих кодов может быть описана табл. 3.

Устройство работает следующим образом.

В исходном состоянии реверсивные счетчики 5.1 и 5.2 импульсов и регистр 11 обнулены. На вход 3 поступают импульсы с частотой f-. На входы

Iи 2 устройства поступают нулевые значения кодов.В соответствии с табл.1 работы коммутаторов 4.1 и 4.2 и табл.2 работы схем сравнения на входы реверсивных счетчиков 5.1 и 5.2 импульсов

с входа 3 импульсы не поступают, и на выходе сумматора 10 в соответствии с табл.3 имеем нулевое значение кода.

Рассмотрим работу схемы устройства при поступлении на его входы 1 и 2 кодов чисел m 3 и и 5 соответственно. При изменении состояний реверсивных счетчиков 5.1 и 5.2 по заднему фронту импульсов и при записи информации с выхода сумматора 10 в регистр

IIпо переднему фронту импульсов, поступающих с тактового входа 3 устройства, значения тип, поступающие на входы 1 и 2 устройства, должны быть поданы непосредственно после заднего фронта импульса. В этом случае схемы 6. 1 и 6.2 сравнения вырабатывают на своих первых выходах значения единицы, а на вторых выходах - значения нуля. В соответствии с табл.3 на выходе сумматора 10 вырабатывается следующее значение кода, при представлении чисел ш и п пятью двоичными разрядами:

00000 - код на выходе регистра

11

00000 - код с выхода группы эле- + ментов И 9.1

00000- код с выхода группы элементов И 9,2

01 - код с третьего и четвертого выходов блока 7 памяти управляющих кодов

00001- код на выходе сумматора

10

По переднему фронту следующего ипульса указанное значение кода с выхо да сумматора записывается в регистр; 1

В соответствии с табл,1 коммутатры подсоединяют суммирующие входы р берсивньгх счетчиков 5.1 и 5.2 импулсов к входу 3, и по заднему фронту поступающего на их вход импульса реверсивные счетчики импульсов устаналиваются в состояние, соответствующ коду на их выходе равному 00001 .

1-10На этом первый такт работы устроства закончен.

На втором такте на выходе сумматора 10 устанавливается следующее значение кода:

00001 - код на выходе регистра 1 1

00001 - код на вьпсоде группы л- элементов И 9.1

00001 - код на выходе группы

элементов И 9.2 01 - код на третьем и четвертом выходах блока 7 памяти управляющих кодов

00100 - код на выходе сумматора 10

которое по переднему фронту импульса записывается в регистр 11.

При поступлении заднего фронта импульса реверсивные счетчики 5.1 и 5.2 устанавливаются в состояние,соответствующее коду 00010ч 2,Qii .

На третьем такте работы устройства на выходе сумматора 10 образуется следующее значение кода :

00100

00010

00010

01

01001

20

25

которое по переднему фронту импульса записывается в регистр.

При поступлении заднего фронта импульса реверсивные счетчики 5.1 5 и 5.2 устанавливаются в состояние, соответствующее коду 00011.. 3... В этом случае схема 6.1 сравнения в соответствии с табл.2 вырабатывает значение нуля на своих выходах, О ив соответствии с табл.1 импульсы на вход реверсивного счетчика 5.1 через коммутатор 4,1 не поступают.

На четвертом такте работы устрой- .ства в соответствии с табл.З на выходе сумматора 10 образуется следу- кщее значение кода:

01001 - код на выходе регистра 11 00011 - код на выходе rpyftпы элементов И 9.1 000000 - код на выходе группы элементов И 9.2 00 - код на третьем и- четвертом выходах блока 7 памяти управляющих кодов

01100 - код на выходе сумматора 10 которое по переднему фронту импуль30 са записывается в регистр 11.

I

При поступлении заднего фронта импульса на вход реверсивного счетчика 5.2 последний устанавливается 35 в значение, соотозетствующее коду 00100,

В этом случае йа пятом такте работы устройства на выходе сумматора 10 образуется следующее значение ко- 40 Ка.:

опОо

00011 00000 . 00

01111

которое по переднему фронту импульса записьшается в регистр 11 .

0 По заднему фронту импульса реверсивный счетчик 5.2 устанавливается в состояние, соответствующее коду 00101, и схема 6.2 сравнения вьфабатывает на своих выходах в соответствии с

5 табл.2 нулевые значения потенциалов, Тогда в соответствии с табл.З на выходе сумматора 10 образуется значение кода

5

01111

OOCOO

00000

00

0111V 15,,.

которое все время перезаписывается в регистр 11 по переднему фронту импульсов ,

Таким образом, на выходе регистра 11 вырабатьшается значение произведения шхп 3x5 15.

,При поступлении на входы устройства новых значений кодов чисел т и п схема работает в соответствии с описанным алгоритмом ее функционирования.

Например, при поступлении т 6 ц. п 4 схема работает следующим образом.

На первом такте работы устройства схема 6,1 сравнения вырабатывает на первом выходе в соответствии с табл, значение единицы, а схема 6,2 сравнения вырабатывает значение единицы на втором выходе. На выходе сумматора 10 в соответствии с табл.3 образуется следующее значение кода (переносы за пределами принятой нами рарядной сетки не учитываются): 01111 - код на выходе регистра 11

11100 - код на выходе группы элементов И 9.1 00101 - код на выходе груп-

пы элементов И 9.2 01 - код на третьем и четвертом выходах блока 7 памяти управляющих кодов

10000 - код на выходе сумматора 10

которое по переднему фронту импульса записывается в регистр 11 о

При поступлении заднего фронта им пульса реверсивный счетчик 5.1 устанавливается в состояние, соответствующее коду 00100, в это же время, учи тьгоая, что задний фронт импульса подан на вычитающий вход, устанавлива-

ется и реверсивный счетчик 5.2.

На втором такте работы устройства схема 6.2 сравнения вырабатывает на своих выходах нулевые значения потен циалов в соответствии с табл.2, а в соответствии с табл.3 на выходе сумматора Ю образуется значение кода, равное

10000

00000

00100

00

10100

которое по переднему фронту импульса записывается в регистр 11.

По заднему фронту импульса реверсивный счетчик 5.1 устанавливается в состояние, соответствующее коду 00101. Реверсивный счетчик 5.2 своего состояния не меняет, так как схема 6.2 сравнения на втором такте работы устройства выработала на своих выходах нулевые значения потенциалов

На третьем такте работы устройств на выходе сумматора 10 образуется знчение кода равное

10100

00000

00100

00

11000.- 24

что соответствует произведению ш х X п 6x4 24, которое по переднему фронту импульса записывается в регистр 11.

По заднему фронту импульса реверсивный счетчик 5.1 устанавливается в состояние 00110, которое равно значению ш, и схема 6.1 сравнения вырабатьшает на своих выходах нулевое значение потенциалов, и в соответствии с табл.1 коммутатор 4.1 закрывает поступление импуЛьсов на реверсивный счетчик 5.1, а в соответствии с табл.3 на выходе сумматора образуется значение кода, равное значению кода на выходе регистра 11, которое все время, до поступления следующих значений чисел п , перезаписывается в регистр 11.

Формула изобретения

Вычислительное устройство, содержащее первый- и второй счетчики, первую схему сравнения, первый и второй коммутаторы, первые выходы которых подключены соответственно к суммирую- щим входам первого и второго счетчиков, а вторые выходы соединены соответственно с вычитающими входами и второго счетчиков, выходы первого счетчика соединены с первой груп712

пой входов первой схемы сравнения, вторая группа входов которой подключена к первому информационному входу устройства, первый -и. второй выходы первой схемы сравнения соединены с управляющими входами первого коммутатора, отличающееся тем, что, с целью расширения функциональных возможностей за счет возможности выполнения умножения, в него введены блок памяти управляющих кодов, вторая схема сравнения, первая и вторая группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первая и вторая группы элементов И, много- входовый сумматор, регистр, причем выходы первого счетчика соединены с первыми входами элементов ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, вторые входы которых подключены к первому выходу блока памяти управляющих кодов, пер- вый и второй адресные входы которого соединены соответственно с первым и вторым выходами первой схемы сравнения, третий и четвертый адресные входы блока памяти управляющих кодов соединены соответственно с первым и вторым выходами второй схемы сравне-, ния и с управляющими входами второго коммутатора, информационный вход которого соединен с информационным входом первого коммутатора, управляюРедактор О.Юрковецкая

Составитель А.Жижин Техред И.Попович

Заказ 5122/46Тщ аж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

538

щим входом регистра и подключен к тактовому входу устройства, второй информационный вход которого соединен с первой группой входов второй схемы сравнения, вторая группа входов которой подключена к выходу счетчика и к первым входам элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы, выходы которых подключены к первым входам элементов И второй группы, выходы которых соединены с второй группой входов многовходового сумматора, первая группа входов которого подключена к выходам элементов И первой группы, вторые входы которых соединены с вторым выходом блока памяти управляющих кодов, третий и четвертый входы которого подключены соответственно к третьей и четвертой группам входов многовходового сумматора, выход которого подключен к информационному входу регистра, вькод которого подключен к пятой группе входов многовходового сумматора и к выходу устройства, пятый выход блока памяти управлякнцих кодов соединен с второй группой входов элементов И второй группы, а шестой выход блока памяти управляющих кодов подключен к второй группе входов элементов ИСКЛЮЧАЩЕЕ ИЛИ второй группы.

Корректор Т.Колб

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функций синуса и косинуса | 1985 |

|

SU1272331A1 |

| Устройство для вычисления функций тангенса | 1985 |

|

SU1365079A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Устройство для вычисления значений степенного ряда | 1985 |

|

SU1277100A1 |

| Устройство для вычисления квадратного корня | 1986 |

|

SU1359778A1 |

| Устройство для моделирования радиотелеграфного канала связи | 1981 |

|

SU1034053A1 |

| Устройство для отладки микропроцессорных систем | 1989 |

|

SU1735856A1 |

| Устройство для сравнения чисел в модулярном коде | 1985 |

|

SU1256013A1 |

| Устройство для LU-разложения матриц | 1987 |

|

SU1509933A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

Изобретение относится к области вычислительной техники и может быть использовано в различных моделирующих системах. С целью увеличения быстродействия гфи умножении совокупности чисел, представляющих собой детерминированные функции, квантованные по уровню и по времени, в устройстве применены две схемы сравнения, которые управляют коммутаторами для осуществления реверсивного режима работы счетчиков аргументов и схемой управления, передающей значения аргументов на накапливающий сумматор. Это позволяет сократить время перемножения, которое в этом случае пропорционально приращениям перемножаемых чисел. 1 ил. 3 табл. ГчЭ ел tsD СП

| Устройство для перемножения кодов | 1982 |

|

SU1108439A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| , Авторское свидетельство СССР fr 1198517, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-23—Публикация

1985-01-28—Подача