и с входами элемента И, выход которого соединен с вторым управляющим входом делителя частоты, выходы второго, третьего и четвертого реверсивных счетчиков соединены соответственно с первыми входами второй, третьей и четвертой схем сравнения, второй вход второй сравнения соединен с выходом второго двухвходовог.о многоразрядного сумматора, первый и второй входы которого соединены с входами абсолютной величины сомножителей устройства и с вторыми входами третьей и четвертой схем сравнения соответственно, третьи входы которых соединены соответственно с первым и вто,рьгн входами первого двухвходового многоразрядного сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения числа на постоянный коэффициент | 1984 |

|

SU1168928A1 |

| Устройство для возведения в квадрат | 1984 |

|

SU1239713A1 |

| Умножитель | 1986 |

|

SU1327093A1 |

| Устройство для деления | 1984 |

|

SU1226444A1 |

| Цифровая система регулирования скорости центробежного аппарата | 1983 |

|

SU1176302A1 |

| Способ магнитной записи асинхронных потоков цифровой информации и устройство для его осуществления | 1990 |

|

SU1788520A1 |

| Оптическое запоминающее устройство | 1986 |

|

SU1509993A1 |

| ГЕНЕРАТОР СЛУЧАЙНОГО ПРОЦЕССА | 1991 |

|

RU2050585C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| Запоминающее устройство | 1985 |

|

SU1280454A1 |

УМНОЖИТЕЛЬ, содержащий генератор тактовых импульсов, элемент И, два управляемых делителя частоты, реверсивный счетчик и схему сравнения, первый вход которой соединен с выходом реверсивного счетчика, отличающийся тем, что, с целью йовьшения быстродействия, в него введены делитель частоты, два двухвходовых и четырехвходовый многоразрядные сумматоры, два управляемых делителя частоты, восемь коммутаторов, семь реверсивных счетчиков, три схемы сравнения и четыре многоразрядных вьиитателя, причем выход генератора тактовых импульсов соединен с первыми управляющими входами делителя частоты и всех управляемых делителей частоты, выход делителя частоты соединен с информационными входами первого, второго, третьего и четвертого коммутаторов, первый и второй выходы которых соединены соответственно с суммирующими и вьмитающими входами первого, второго, третьего и четвертого реверсивных счетчиков, выходы которых соединены соответственно с первыми BxoAaMii первого, второго, третьего и четвертого многоразрядных вычитателей, выходы которых соединены соответственно с информационными входами первого, второго, третьего и четвертого управляемых делителей частоты, выходы соединены соответственно с информационными входа1-1и пятого, шестого, седьмого и восьмого коммутаторов, первый и второй выходы пятого и шестого коммутаторов соединены соответственно с суммирующими и вычитающиьш входами пятого и шестого реверсивных счетчиков, а первый и второй выходы седьмого и (Л восьмого коммутаторов соединены соотс ветственно с вычитающими и cyм Dфyющими входами седьмого и восьмого реверсивных счетчиков, выходы пятого, шестого, седьмого и восьмого реверсивных счетчиков соединены с информационными входами четырехвходового многоразрядного сумматора, выход которого соединен с выходом устройства, входы знаков сомножителей которого соединены с первым и вторым входами | первого двухвходового многоразрядного 00 4 сумматора, выход которого соединен с вторым входом первой схемы сравнения, выходы Больше всех схем сравнения соединены с первыми управляющими входами соответствующих пар коммутаторов, вторые управляющие входы которых соединены с вторыми входами всех многоразрядных вычитателей и с выходами Меньще всех схем сравнения, выходы Сравнение которых соединены с вторыми Управляющими входами соответствующих управляемых делителей частоты

1

Изобретение относится к цифровым (дискретным) вычислительным машинам, в которых по меньшей мере часть вычислений осуш;ествляется с помощью электрических устройств, к устройствам для обработки данных с воздействием на порядок их расположения или на содержание обрабатываемых данных, в частности, для умножения, и может быть использовано в различных устройствах цифровых (дискретных) вычислительных машин.

Целью изобретения является повьшхение быстродействия устройства.

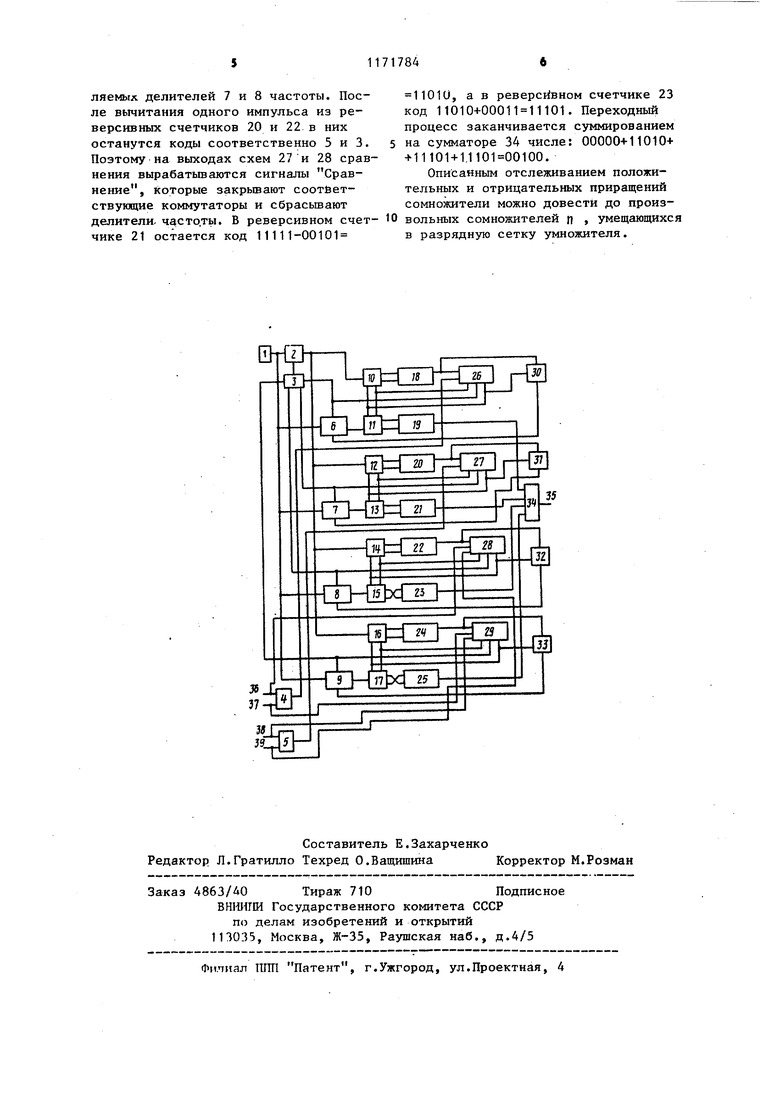

На чертеже представлена структурная схема умножителя.

Устройство содержит генератор 1 импульсов, делитель 2 частоты, элемент И 3, первый 4 и второй 5 двухвходовые.многоразрядные сумматоры, управляемые делители 6-9 частоты, коммутаторы 10-17, реверсивные счетчики 18-25, схемы 5б-29 сравнения, многоразрядные вычитатёли 30-33, четырехвходовый многоразрядный сумматор 34, выход 35 устройства, входы знаков первого 35 и второго 36 сомножителей, входы абсолютной величины первого 37 и второго 38 сомножителя.

Предлагаемое устройство работает следующим образом.

Числа в дополнительном коде, умножение которых производится в устройстве, можно представить как Хд 5с,х и ,У, где и у- янаки чисел, а X и у - абсолютные величины

/

при и или дополнения абсолютных величин при , .

Рассмотрим работу умножителя на примере двух чисел: 2 и , при

этом , , , у-З. В 1 сходном состоянир на входы 36-39 поданы нулевые коды, все реверсивные счетчики 18-25 сброшены в нуль, схемы 26-29 сравнения по этой причине вьфабатывают сигналы Сравнение, которыми сбрасываются управляемые делители 6-9 частоты и через элемент И 3 сбрасьшают делитель частоты 2, в результате чего импульсы из генератора 1 не поступают. После этого на вход 36 поступает знак числа Ха, который далее поступает на схему 28.сравнения и на вход сумматора 4. На вход 37 поступает знак числа Уц, который поступает на схему 29 сравнения и второй вход сумматора 4, с выхода которого результат 00 поступает насхему 26 сравнения. На вход 38 поступает абсолютная величина , которая подается на схему 29 сравнения, а также на вход сумматора 5. На вход 39 поступает абсолютная величина , которая подается на схему 28 сравнения, а также на вход сумматора 5, с выхода которого результат подается на схему 27 сравнения.

После этого схемы 26-29 сравнения вырабатьшают сигналы Больше, которые откроют коммутаторы 10-14 и 16 для поступлени5 импульсов на суммируюш;ие входы реверсивных счетчиков 18-22 и 24 и на коммутаторы 15 и 17 для поступления импульсов на вычитающие входы реверсивных счетчиков 23 и 25, где насчитьгоаются дополнения. Одновременно снимается сброс со всех делителей частоты и импульсы из генератора 1 импульсов начинают поступать во все делители и счетчики. В няия3. М

ле работы, так как на выходах Меньше схем 26-29 - нулевые сигналы, нулевые коды с выходов реверсивных счетчиков 18, 20, 22 и 24 через вычитателн 30-33 поступают на информационные входы управляемых делителей частоты, т.е. в начале работы устанавливаются нулевые управляющие коэффициенты. После занесения в реверсивные счетчики 18 и 20, 22 и 24 первых импульсов в реверсивных счетчиках 19, 21, 23 и 25 сохраняются нулевые коды, но управляющие коэффициенты уже равны 1. Кроме того, на выходе схемы 26 сравнения появляется сигнал Сравнение, которым сбрасывается управляемый делитель 6 частоты и закрьшаются коммутаторы 10 и 11, После занесения в реверсивные счетчики 20, 22 и 24 вторых импульсов в реверсивный счетчик 21 заносится один импульс, т.е. двоичный код 00001, а в реверсивных счетчиках 23 и 25 после вычитания одного импульса будут двоичные коды 11111. Управляющие коэффициенты.на управляющих входах делителей 6-9 установятся равными 2. После занесения третьих импульсов в реверсивные счетчики 20, 22 и 24 в реверсивный счетчик 21 заносятся еще два импульса и хранится код 00011, а из реверсивных счетчиков 23 и 25 вычитаются еще по два импульса и хранятся коды 11101. Кроме того, схема 29 сравнения вырабатьгоает сигнал Сравнение который сбрасывает -Управляемый делитель 9 частоты и закрывает коммутаторы 16 и 17. На информационных входах делителей 7 и 9 частоты устанавливаются управляющие коэффициенты 3.

После занесения четвертых импульсов в реверсивные счетчики 20 и 22 в реверсивный счетчик 21 заносятся еще три импульса и хранится код 00110, а из реверсивного счетчика 23 вычитаются еще три и шyльca и хранится код 11010. Кроме того, схема 28 сравнения вьфабатывает сигнал Сравнение который сбрасывает управляемый делитель 8 частоты и закрывает коммутаторы 14 и 15. На информационном входе делителя 7 частоты устанавливается управляющий коэффициент 4. После занесения двух очередных импульсов в реверсивный счетчик 20 в реверсивный счетчик 21 заносятся еще четыре и пять импульсов и }фанится код 11111, после этого схема 27 сравнения иыра844

оатывает сигнал Сравнение, котор1.ш сбрасывает управляемый делитель 7 частоты и закрывает коммутаторы 12 и 13, и с выхода элемента И 3 сбрасьшается делитель 2. Переходный процесс в-схеме завершается суммированием чисел 00000 + 11111 + 11010 + 11101 соответственно с реверсивных счетчиков 19, 21, 23 и 25 на сумматоре 34, после чего на выходе 35 появляется результат 00110, т.е. 2x3 6. Если теперь какой-либо из сомножителей или оба сомножителя получат положительное приращение, то соответствующая схема сравнения выработает на первом выходе сигнал Больше, откроет соответствуюп1ие коммутаторы и устранит сброс с соответствующего управляемого делителя и де-лителя 2 частоты, после чего полученное приращение сработается аналогач 1О описанному. Если один из сомножителей (или оба сомножителя) получит отрицательное приращение, то работа устройства несколько изменится. Допустим, отрицательное приращение - 1 получил сомножитель у 3, т.е. у . Тогда примем за исходное положение момент окончания переходного процесса в примере 2), т.е. в исходном состоянии с выхода реверсивного счетчика 22 через вычитатель 32 на информационный вход управляемого делителя 8 частоты подается коэффициент 4, а с выхода реверсивного счетчика 20 через вычитатель 31 на информационньй вход делителя 7 частоты подается коэффициент 6. После прихода приращения - 1 на вход 39 оно поступает на вход схемы 28 сравнения. С выхода сумматора 5 результат поступает на вход схемы 27 сравнения. На выходах схем 27 и 28 сравнения вырабатываются сигналы Меньше, которые поступают в младший разряд вычитателей 31 и 32. Управляющий коэффициент с выхода вычитателя 31 устанавливается на информационном выходе делителя 7 частоты, а управляющий коэффициент 3 - на информационном входе делителя 8 частоты. Сигналы Меньше открьшают коммутаторы 12-14 так, что импульсы поступают на вычитающие входы реверсивных счетчиков 20-22, а импульсы с выхода коммутатора 15 на суммирующий вход реверсивного счетчика 23, кроме того, снимается сброс с делителя 2 частоты и упраяляемых делителей 7 и 8 частоты. После вычитания одного импульса из реверсивных счетчиков 20 и 22 в них останутся коды соответственно 5 и 3, Поэтому на выходах схем 27и 28 сравнения вырабатьшаются сигналы Сравнение, которые закрьшают соотбетствующие коммутаторы и сбрасьшают делители, ча:Сто.ты. В реверсивном счетчике 21 остается код 11111-00101

-11010, а в реверсивном счетчике 23 код 11010+00011 11101. Переходный процесс заканчивается суммированием 5 на сумматоре 34 числе: 00000+11010+ -«11101 + 1,1101 00100.

Описанным отслеживанием положительных и отрицательных приращений сомножители можно довести до произвольных сомножителей п , умещающихся в разрядную сетку умножителя.

i-TV

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ-ДЕЛЕНИЯ | 0 |

|

SU392495A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1976 |

|

SU590735A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-08-07—Публикация

1984-02-22—Подача