ным входом 1-го коммутатора логических условий и является i-м входом логических условий группы устройства, второй информационный вход i-ro коммутатора логических условий соединен с выходом i-ro триггера первой группы, вход установки в единицу которого соединен с выходом i-ro элемента И первой группы, входы установки в ноль i-x триггеров первой и второй групп соединены с выходом i-ro элемента И третьей группы, вход установки в единицу i-ro

триггера второй группы соединен с выходом i-ro элемента И второй группы, второй вход которого соединен с четвертым выходом генератора тактовых импульсов, единичный выход i-ro триггера второй группы соединен с третьим входом i-ro элемента И третьей группы и с первым управляющим входом 1-го коммутатора логических условий, второй управляющий вход которого соединен с нулевым выходом i-ro триггера второй группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное управляющее устройство | 1987 |

|

SU1527634A1 |

| Мультимикропрограммное устройство управления с контролем | 1985 |

|

SU1272333A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1282121A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1256026A1 |

| Многоканальная микропрограммная управляющая система | 1985 |

|

SU1280628A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1381506A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Мультимикропрограммное устройство управления | 1983 |

|

SU1161942A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок памяти микропрограмм, регистр адреса микрокоманд, регистр микрокоманд, генератор тактовых импульсов, триггер пуска и коммутатор адреса микрокоманд, причем группа выходов блока памяти микропрограмм соединена с группой информационных входов регистра микрокоманд, группа выходов кода микроопераций которого является группой управляющих выходов устройства, выход признака конца команды регистра микрокоманд соединен с управляющим входом коммутатора адреса микрокоманд, группа выходов которого соединена с группой информационных входов регистра адреса микрокоманд, группа выходов которого соединена с группой адресных входов блока памяти микропрограмм, вход пуска устройства соединен с входом установки в единицу триггера пуска, выход которого соединен с входом запуска генератора тактовых импульсов, первый и второй выходы которого соединены соответственно с входами синхронизации регистра адреса микрокоманд и регистра микрокоманд, j-й выход (J 1,2, ...,п, где п - количество немодифицируемых разрядов адреса микрокоманды) немодифицируемого разряда адреса микрокоманды которого соединен с J-M информационным входом первой группы коммутатора адреса микрокоманд, вторая группа информационных входов которого является группой входов кода команды устройства, отличающееся тем, что, с целью сокращения оборудования, оно содержит элемент И, первую, вторую и третью группы m элементов И (гп 1,2,..., где m - количество анализируемых логических условий), первую и вторую группы m триггеров, группу m коммутаторов логических условий, мультиплексор логических условий и дешифратор логических условий, причем выход признака конца работы регистра микрокоманд соединен с первым входом элемента И, второй вход которого соединен с вторым выходом генератора тактовых импульсов, выход элемента И соединен с входом € установки в ноль триггера пуска, группа выходов кода логических условий регистра миксл рокоманд соединена с группой управляющих входов мультиплексора логических условий и с группой входов дешифратора логических условий, стробирующий вход которого соединен с выходом признака задержки анализа логических условий регистра микрокоманд, выход признака проверки логических условий которого соединен с первыми входами гп элементов И третьей группы и со о: стробируюшим входом мультиплексора логических условий, i-й информационный вход СХ) которого (i 1,2, ..., m) соединен с выхосо со ;о дом i-ro коммутатора логических устовий группы, (т + 1)-й информационный вход мультиплексора логических условий соединен с выходом модифицируемого разряда адреса микрокоманды регистра микрокоманд, выход мультиплексора логических условий соединен с (п + 1)-м информационным входом первой группы коммутатора адреса микрокоманд, третий выход генератора тактовых импульсов соединен с первыми входами элементов И первой и второй групп, вторые входы которых соединены с соответствующими выходами дещифратора логических условий, третий вход i-ro элемента И первой группы соединен с первым ннформашиш

1

Изобретение относится к вычислительной технике и может быть использовано в устройствах управления ЭВМ.

Цель изобретения - сокращение объема оборудования устройства путем сокращения объема блока памяти микропрограмм.

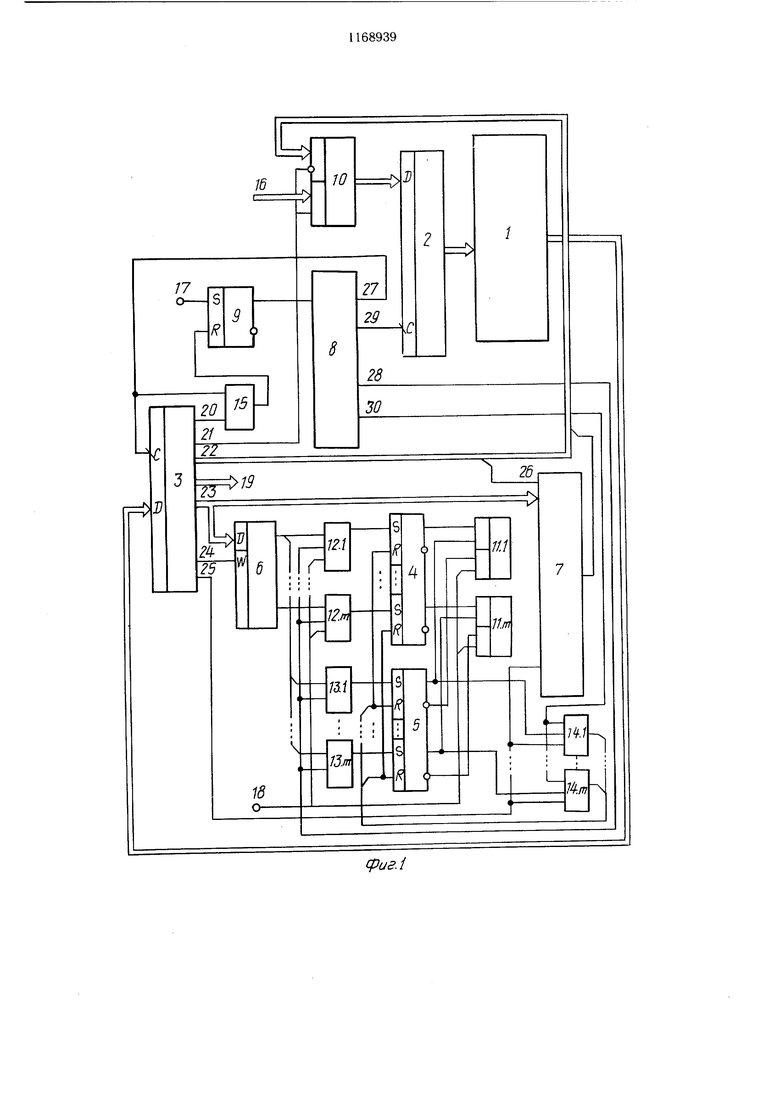

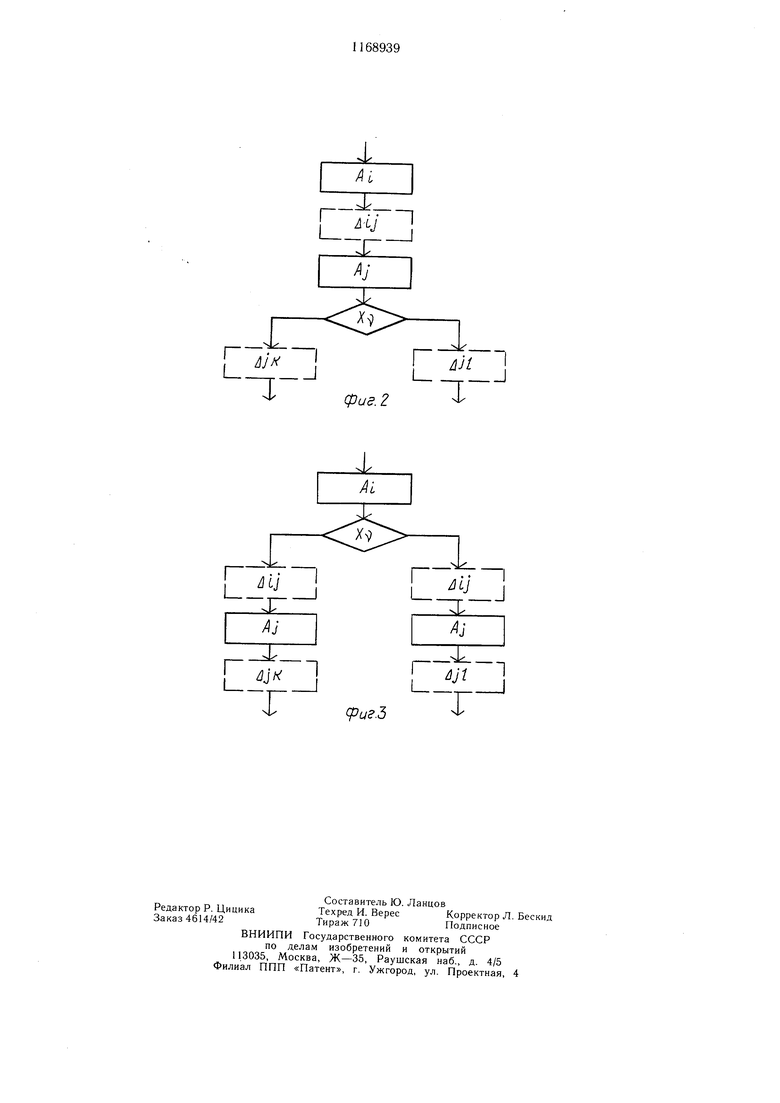

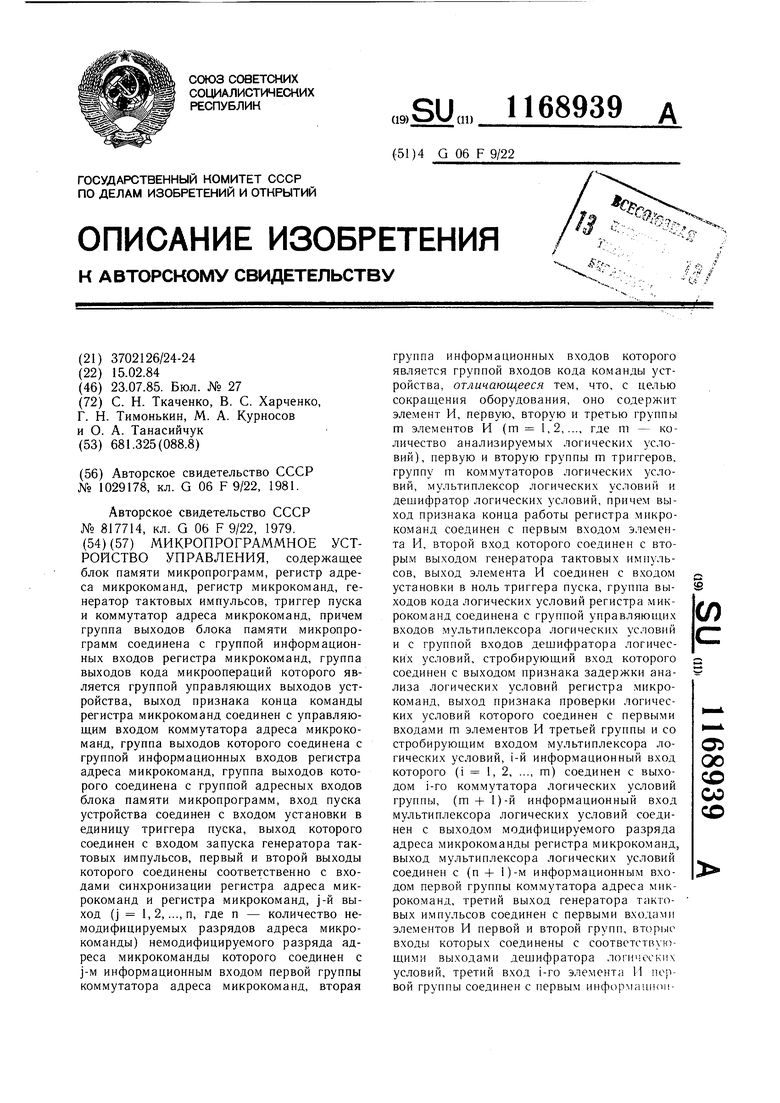

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 и 3 - фрагменты граф-схем соответственно алгоритма нерасщепленной и расщепленной микропрограмм.

Устройство содержит блок 1 памяти микропрограмм, регистр 2, адреса микрокоманд, регистр 3 микрокоманд, первую 4 и вторую 5 группы триггеров, дешифратор 6 логических условий, мультиплексор 7 логических условий, генератор 8 тактовых импульсов, триггер 9 пуска, коммутатор 10 адреса, группу коммутаторов 11.1 -11.гп логических условий, группы 12.1 -12.т, 13.1 -13.ш, 14.1 - 14.m элементов И, элементИ 15, группу 16 входов кода команды, вход 17 пуска, группу 18 входов логических условий, группу 19 управляющих выходов, выход 20 признака конца работы регистра микрокоманд, выход 21 признака конца команды регистра микрокоманд, группу 22 выходов немодифицируемых разрядов адреса регистра микрокоманд, группу 23 выходов кода логических условий регистра микрокоманд, выход 24 признака задержки анализа логических условий регистра микрокоманд, выход 25 признака проверки логических условий, выход 26 модифицируемого разряда адреса регистра микрокоманд и выходы 27-30 генератора тактовых импульсов.

Предлагаемое устройство работает следующим образом.

Рассмотрим его функционирование по тактам в пределах одного рабочего цикла.

Импульс запуска поступает на вход 17 устройства, устанавливая триггер 9 пуска в

единичное состояние. Единичный сигнал с

выхода триггера 9 запускает генератор 8,

который начинает последовательно формировать тактовые импульсы на выходах 29 и 30.

Первому такту рабочего цикла соответствует сигнал на выходе 27 генератора 8. Тактовый импульс с выхода 27 поступает на вход синхронизации регистра 3, обеспечивая занесение в данный регистр кода микрокоманды, установленного на выходе блока 1.

Одновременно данный тактовый импульс поступает на вход элемента И 15, который однако в данном цикле (и последующих, за 5 исключением вспомогательного) закрыт нулевым сигналом с выхода 20 регистра 3, так что сброс в «О триггера 9 и соответственно останов устройства не происходит.

Второму такту соответствует сигнал на выходе 28 генератора 8. В данном такте в зависимости от состояния признаков g и р возможны следующие три режима и соответствующие им действия.

В первом режиме g Onp 0. В данном случае позиционный код на выходе 5 дещифратора 6 не вырабатывается, т.е. элементы 12.1 -12.m и 13.1 -13.m находятся в закрытом состоянии и блокируют прохождение тактового импульса на вход соответствующих триггеров 4.1-4.П1, 5.1-5.т. Информация на входах мультиплексора 7 не ° меняется и модифицируемый разряд передается с выхода 26 на выход без изменения, т.е. в данном режиме модификация адреса следующей микрокоманды не происходит и осуществляется режим последовательной д выборки микрокоманд.

Во втором режиме g 1 и р 0. В данном случае дешифратор 6 под действием единичного управляющего сигнала, поступающего с выхода 24, осуществляет дешифрацию кода логических условий, поступающего 0 на группу его информационных входов и

формирует на выходе позиционный код, содержащий единичное значение в одном из разрядов. Единичный сигнал с i-го (i 1, m) выхода дешифратора. 6 поступает на вход элементов И 12.i и 13.i. На второй вход элементов И 12.i и 13.i поступает тактовый импульс с выхода 28 генератора 8, который разрешает установку соответствуюш,его значения логического условия с отложенной проверкой, поступаюш.его с группы 18 входов устройства, триггера 4.1, и вызывает установку единичного значения в триггере 5.1. На этом действие тактового импульса заканчивается. Независимо от возможного изменения информации на входах значений логических условий мультиплексора 7 модифицируемый разряд адреса следующей микрокоманды передается с выхода 26 на выход мультиплексора без изменения (так как р 0), т.е. осуществляется режим последовательной выборки микрокоманд.

В третьем режиме g О и р 1. В данном случае осуществляется проверка логического условия и модификация адреса следующей микрокоманды. Единичный сигнал поступает на управляющий вход мультиплексора 7, обеспечивая тем самым реализацию модификации адреса следующей микрокоманды. Модифицируемый разряд поступает по выходу 26 на мультиплексор 7. Непосредственное значение i-й (1 1, m) логической переменной, определяющее порядок модификации адреса, поступает на соответствующий вход мультиплексора 7 через соответствующий коммутатор ll.i. Если в предществующих циклах значение данной логической переменной запоминалось в триггере 4.i, то на выходе коммутатора 11 .i имеет место эта переменная. Прохождение данного сигнала через коммутатор 11.1 обеспечивается единичным сигналом на прямом выходе триггера 5.i. Значение логической переменной, постуцающее с группы 18 входов на соответствующий вход коммутатора ll.i, в данном случае блокируется нулевым сигналом на его другом входе, который поступает с инверсного выхода триггера 5.1.

Таким образом, обеспечивается возможность запоминания логических условий с отложенной проверкой в триггерах 4.1-4.т до момента проверки. В момент проверки таких условий проверяется то значение, которое было сформировано ранее, независимо от того, в каком состоянии находится соответствующая ему переменная в данный момент.

Значения логических переменных не запоминаются в триггерах 4.1-4.т, если они формируются и используются в пределах одного цикла, т.е. являются мгновенными. В этом случае значение 1-й мгновенной логической переменной поступает на группу 18 входов и через соответствующий коммутатор 1 1.1 поступает на соответствующий вход мультиплексора 7. Прохождение значения 1-й мгновенной логической переменной через коммутатор ll.i обеспечивается единичным сигналом с инверсного выхода триггера 5.{ . Этот разряд находится в нулевом состоянии, так как запоминание значения логической переменной с отложенной проверкой в триггерах 4.1-4.m не проводилось, а соответственно не устанавливались 0 триггеры 5.1-5.т, отмечающие факт готовности данного логического условия для проверки.

Третий такт определяется сигналом на выходе 29 генератора 8. Тактовый импульс

5 поступает на синхровход регистра 2 адреса микрокоманд, обеспечивая занесение адреса следующей микрокоманды, установленного на выходе коммутатора 10. Установка адреса микрокоманды на выходе коммутатоQ ра 10 происходит следующим образом. В первом такте первого цикла реализации каждой микропрограммы в регистр 3 заносится микрокоманда, расположенная в блоке 1 по нулевому адресу. Это обеспечивается тем, что в исходном состоянии регистр 2 адреса

5 микрокоманд находится в нулевом состоянии. Данная микрокоманда является исходной и содержит единичное значение в разряде, соответствующем выходу 21 регистра 3. Единичный сигнал с данного выхода поступает на прямой управляющий вход ком0мутатора 10, обеспечивая возможность передачи с группы 16 входов на его выход кода команды, являющегося адресом начала микропрограммы ее реализации. Код команды должен быть установлен на группе 16

5 входов к началу третьего такта исходного цикла. Сигнал с выхода 21 одновременно поступает на инверсный управляющий вход коммутатора 10, блокируя подачу на его выход адреса следующей микрокоманды с группы 22 выходов регистра 3 в течение данного

0 цикла. Очередная и все последующие микрокоманды микропрограммы содержат в разряде, соответствующем выходу 21 регистра 3, нулевое значение. Нулевой сигнал ,поступает на прямой управляющий вход коммутатора 10, блокируя подачу кода операции на информационные входы регистра 2. Одновременно данный сигнал поступает на управляющий вход коммутатора 10, обеспечивая возможность подачи через него адреса очередной микрокоманды на информацион0ные входы регистра 2 с группы 22 выходов регистра 3.

Четвертый такт определяется сигналом на выходе 30 генератора 8. Тактовый импульс поступает на входы элементов И 14.1 -

5 14.т, которые используются для установки в нулевое состояние соответствующего триггера 4.1 и 5,1. Единичный сигнал с прямого выхода триггера 5.1 поступает на соответствующий вход элемента 14.i. Если, кроме того, на другом входе элемента 14.1 установлен единичный сигнал с выхода 25 регистра 3, т.е. в данном цикле была осуществлена проверка хранящегося в триггерах 4.1-4.т значения логических условий, то под действием тактового импульса элемент И 14.1 открывается и на его выходе появляется единичный сигнал. Данный сигнал поступает на вход установки нулевого состояния триггеров 4.1-4.т и 5.1-5.т, сбрасывая i-й разряд триггеров 4.i и 5.1 в ноль. Таким образом, если во втором такте данного цикла осуществлялась проверка логического условия с отложенной проверкой, то в четвертом такте оно обнуляется. Во всех циклах реализации микропрограммы устройство функционирует акалогично. В последнем цикле реализации микропрограммы в регистр 3 заносится микрокоманда, содержащая нулевое значение адреса следующей микрокоманды и единицу в разряде, соответствующем выходу 20. Единичный сигнал с данного выхода открывает элемент И 15. Поэтому в первом такте следующего (вспомогательного) цикла тактовый импульс с выхода 27 генератора 8 через данный элемент поступает на вход установки нулевого состояния триггера 9 пуска, сбрасывая его в ноль. Нулевой сигнал с прямого выхода триггера 9 выключает генератор 8 и устройство переходит в исходное состояние. С приходом очередного импульса запуска на вход 17 может быть ипициировано выполнение очередной микропрограммы аналогично описанному. Таким образом, предлагаемое устройство управления реализует как расщепленные так и нерасщепленные микропрограммы. При реализации расщепленных микропрограмм необходимость в запоминании логических условий отсутствует, так как логические условия формируются и используются в течение одного цикла. Схемно это реализуется так, что значение логической переменной, по.ступая на вход логических условий устройства через соответствующий коммутатор, непосредственно поступает на мультиплексор, определяя порядок модификации адреса следующей микрокоманды микропрограммы. Однако при реализации расщепленных микропрограмм требуется значительно больший объем блока памяти микропрограмм. При реализации нерасщепленных микропрограмм существует необходимость в запоминании логических условий, которые могут формироваться в одном цикле, а использоваться в другом. Для запоминания данных логических условий вводится соответствующая группа триггеров 4.1-4.т, а для идентификации факта запоминания логических условий и обеспечения возможности их коммутации на мультиплексор вводится группа триггеров 5.1-Б.гп. Введение данных групп триггеров и соответствующих им логических схем не оказывает существенного влияния на экономичность устройства, так как нерасщепленная микропрограмма требует значительно меньщего объема блока памяти микропрограмм. На фиг. 2 приведен фрагмент граф-схемы алгоритма, в которой логическое условие х входит в распределение сдвигов Aj (вырабатывается оператором Ai), а используется после выполнения оператора AJ. Если в устройстве управления не предусмотрен элемент для запоминания данного логического условия, то к моменту выполнения микрокоманды Aj, которая использует условие xi, оно будет потеряно, что может привести к нарушению порядка выполнения микрокоманд. Чтобы исключить возникновение подобных ситуаций, не усложняя устройство управления элементами для запоминания таких логических условий, осуществляют их перенос к микрокоманде выработки (расщепление) соответствующего оператора по значениям логической переменной. Тогда микропрограмма преобразуется так, как это показано на фиг. 3, где осуществлен перенос логического условия х к оператору его выработки Ai (осуществлено расщепление оператора AI). Очевидно, что при реализации расщепленной микропрограммы нет необходимости в запоминании и хранении мгновенных логических условий. Однако при увеличении числа условных верщин метод расщепления микропрограмм приводит к значительному увеличению длины программы за счет появлеййя дополнительного числа одинаковых микрокоманд в линейных участках соседних ветвей микропрограммы. Поэтому расщепленная микропрограмма требует по сравнению с исходной значительно больщего объема блока памяти и снижает экономичность устройства.

(pus.i

| Микропрограммное управляющее устройство | 1981 |

|

SU1029178A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Пикопрограммное устройство управления | 1979 |

|

SU817714A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-23—Публикация

1984-02-15—Подача