Изобретение относится к вычислительной технике, может применяться в устройствах обработки данных с конвейерным выполнением микропрограмм .

Цель изобретения - повьпиение быстродействия микропрограммного .управляющего устройства

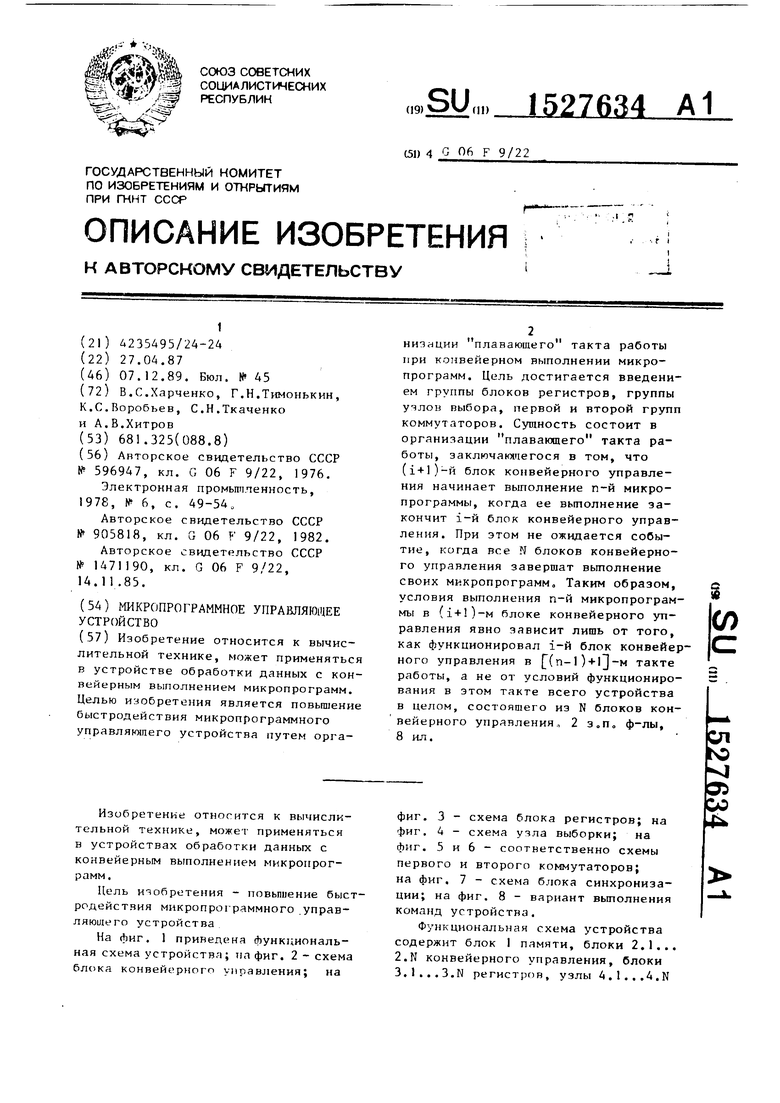

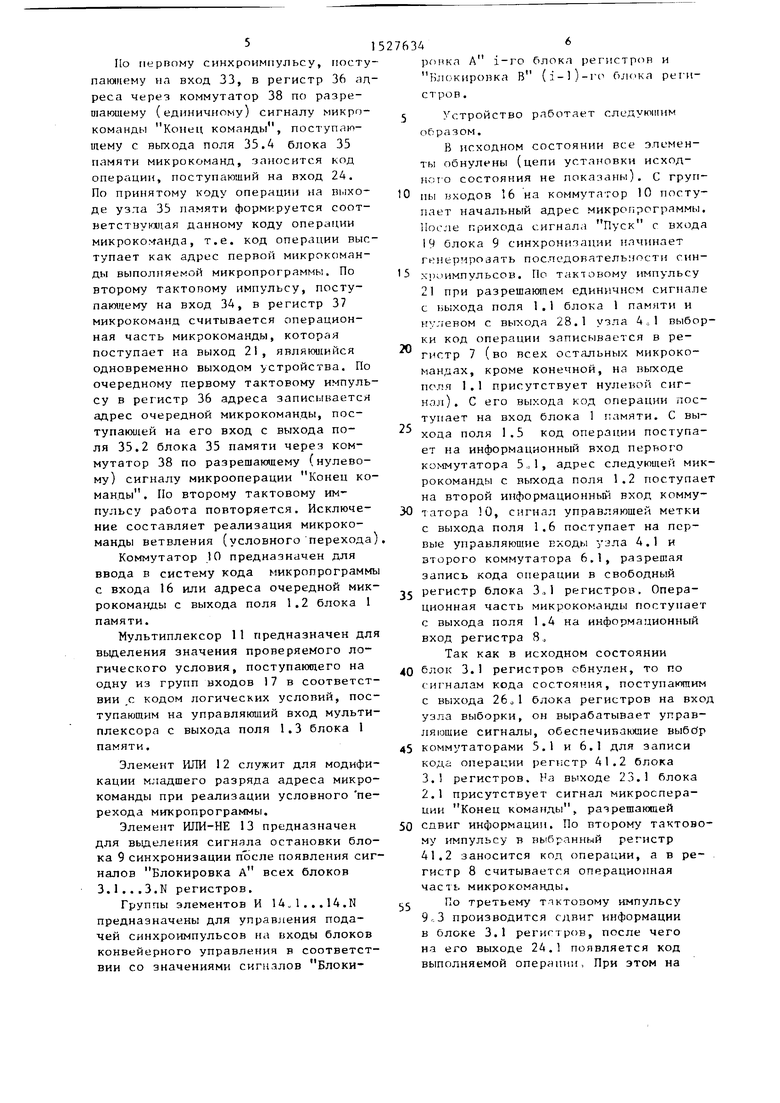

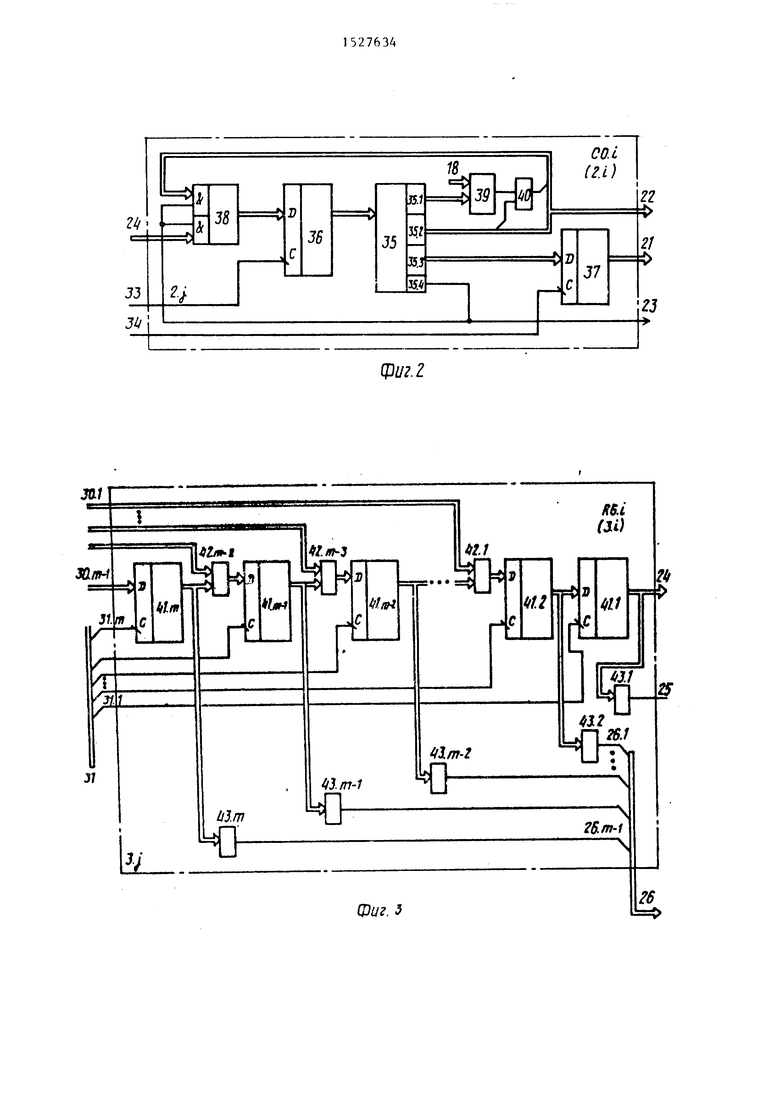

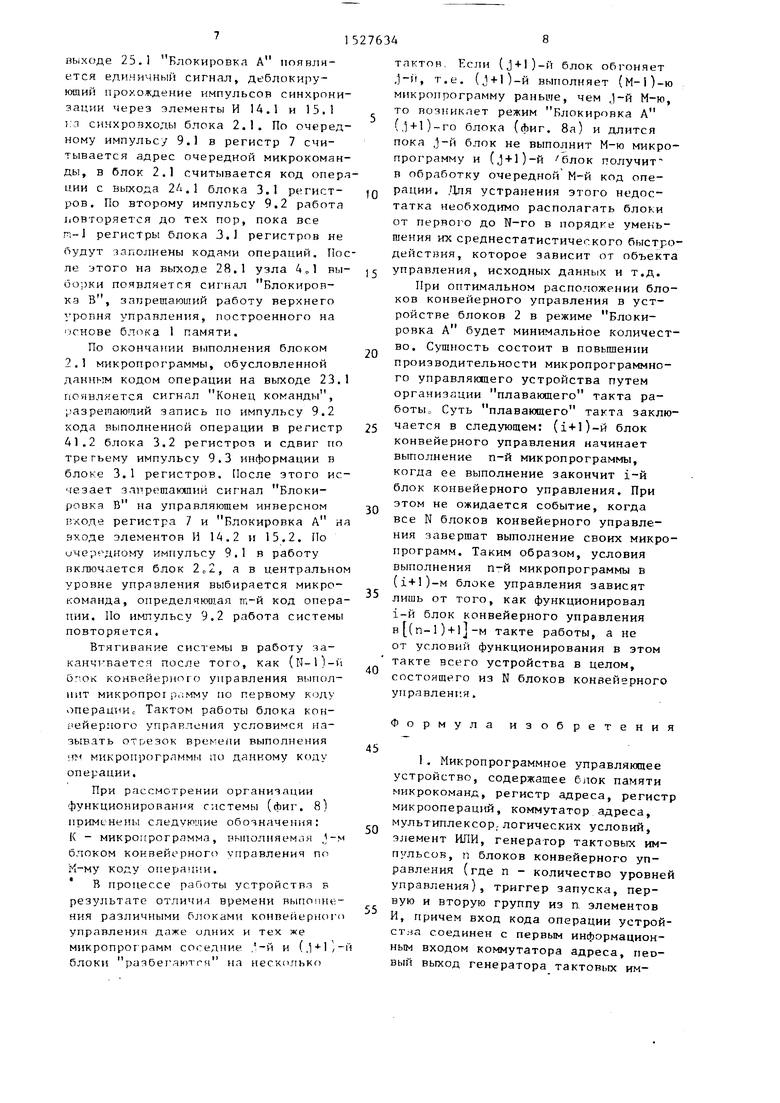

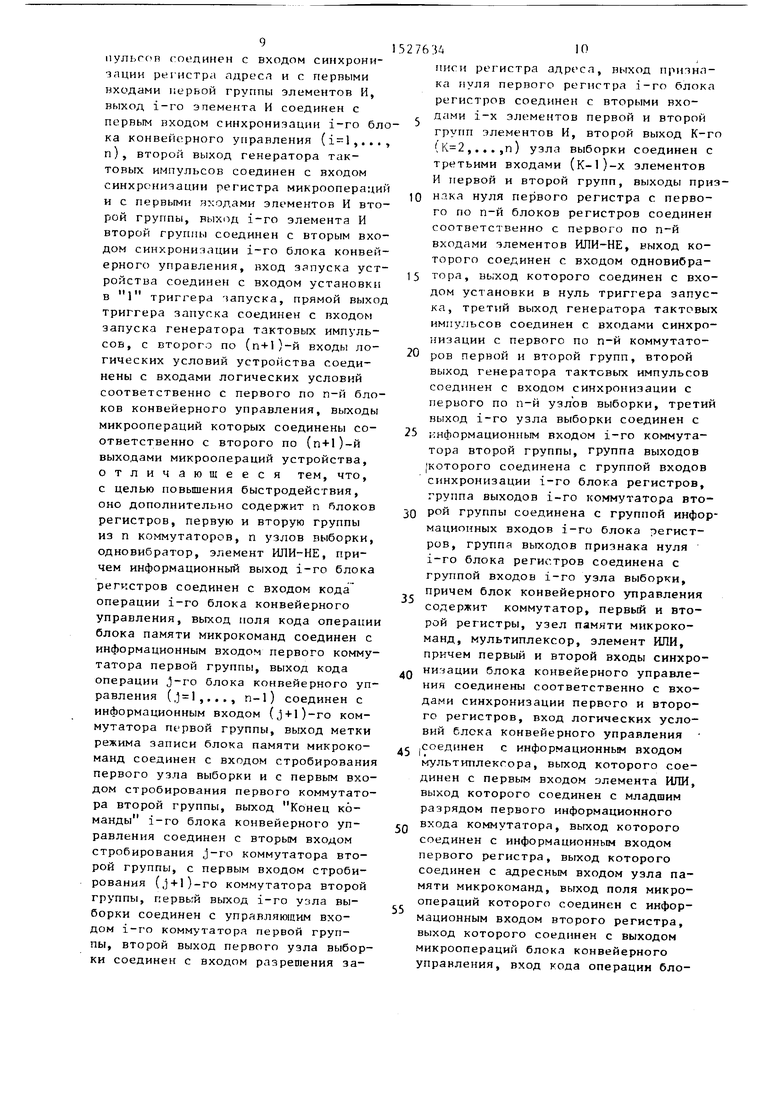

На фиг. 1 приведена функциональная схема устройства; тктфиг. 2 - схема блика конвейерного управления; на

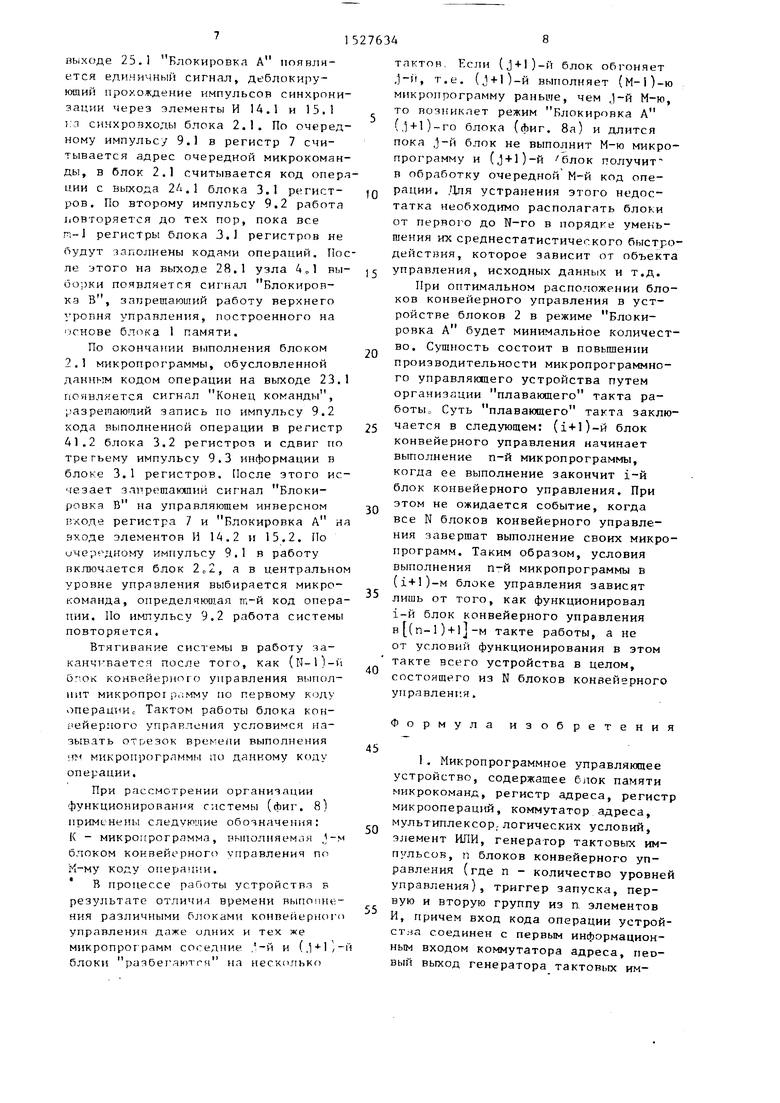

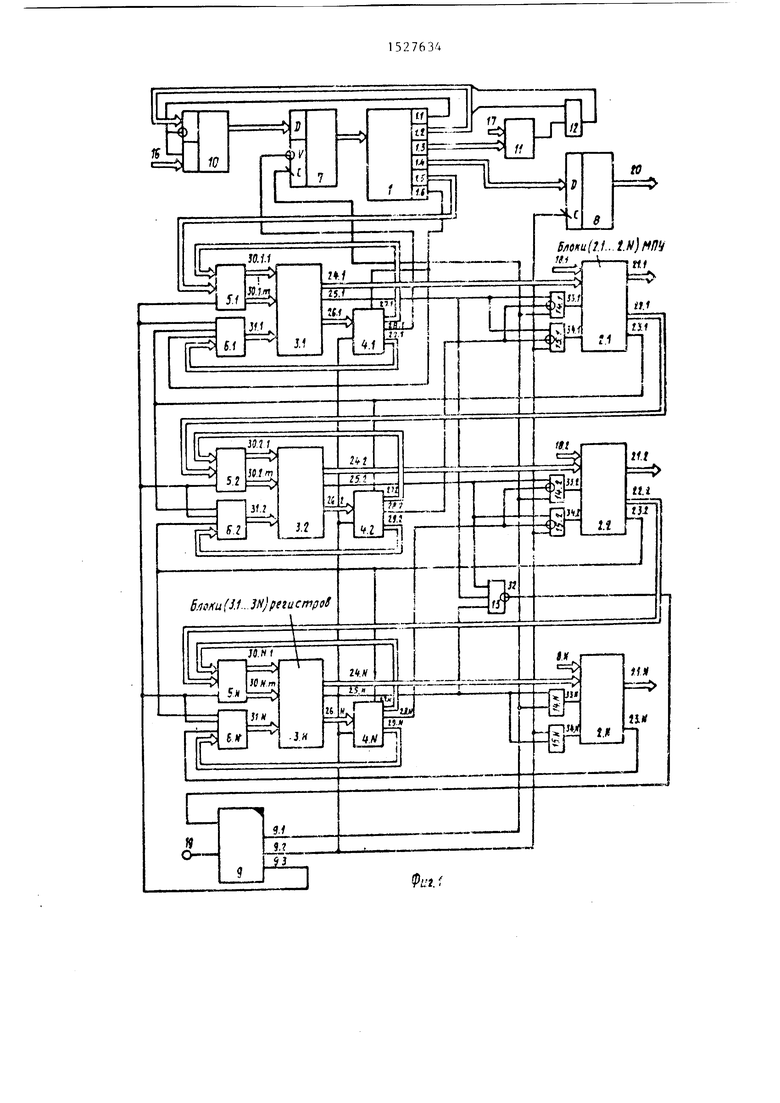

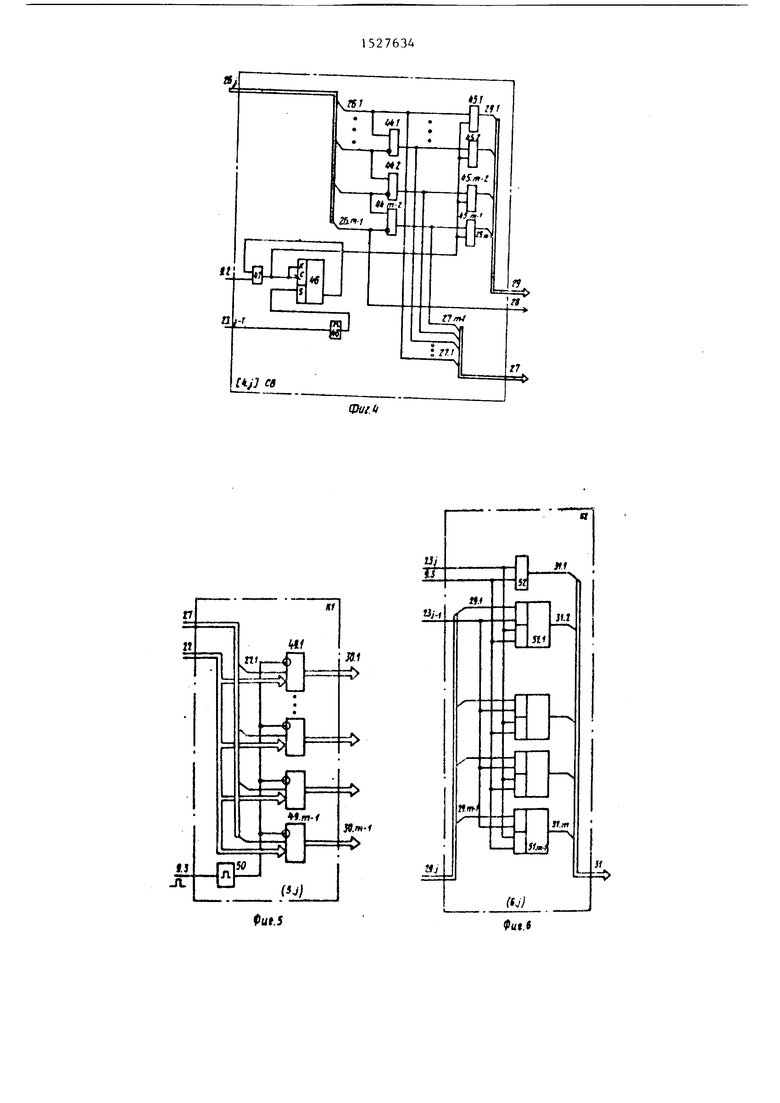

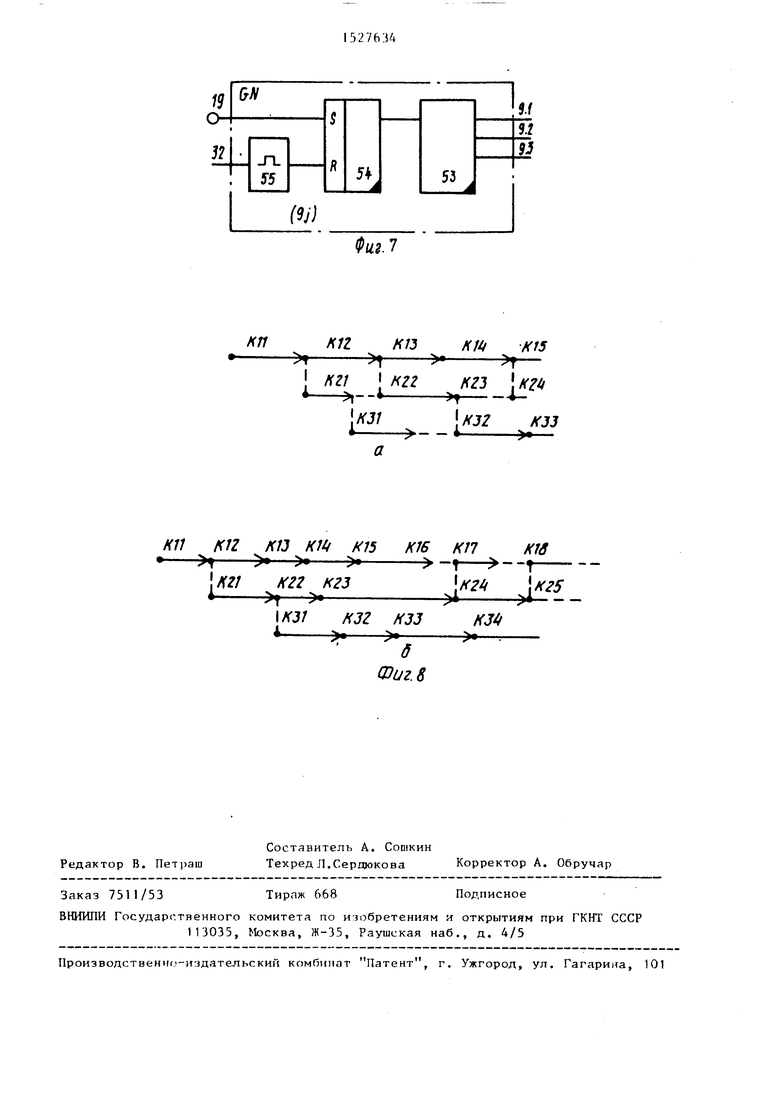

фиг. 3 - схема блока регистров; на фиг. 4 - схема узла выборки; на фиг. 5 и 6 - соответственно схемы первого и второго коммутаторов; на фиг. 7 - схема блока синхронизации; на фиг. 8 - вариант выполнения команд устройства.

Фугп циональная схема устройства содержит блок I памяти, блоки 2,1... 2.N конвейерного управления, блоки 3.1...3.N регистров, узлы 4.1...4.N

выборки, первую 5.1...5.N и вторую 6.1...6.N группы коммутаторов, регистр 7 адреса, регистр 8 микроопераций, блок 9 синхронизации, коммутатор 10 адреса, мультиплексор 11, элемент ИЛИ 12, элемент {-ШИ-НЕ 13, первую 14,1...14.N и вторую 15.1... 15oN группы элементов И, вход 16 кода микропрограмм, первый вход 17 логических условий, группу входов 8.1ос.18.г1 логических условий блоков 2.1..,2.N конвейерного управления, вход 19 пуска устройства, первый выход 20 микроопераций,группы выходов 21.1...2,,N конвейерных микроопераций, выходы 22 . 1 . с,. 22 .N-1 кода операции и выходы 23.1...23;N микрооперации Конец команд.ы блоков 2.1,,.2.N конвейерного управле- ния, группы выходов 24.1е..24.N кода операции, выходы 25 . 1 ... 25 .N признака нуля первого регистра - Блокировка А и 26.1.0.26.N признака нуля остальных регистров сигналов заня- гости блоков 3.1.C.3.N регистров, первые выходы 27.1,oo27.N узла выборки - рыбора регистра, вторые выходы 28,,1...28.N узла выборки - Блокировка в и третьи входы 29.1... 29.N узла выборки - управления синхронизацией, группу выходов 30,1,.. 30.N записи первых коммутаторов 5.1..o5.N, группу выходов 31.1..с 31.N управления вторых коммутаторов 6.1 ос6,11, выход 32 элемента ИЛИ-НЕ 13, группы выходов 33.1o..33.N и 34.1.0.34.N первой 14.1...14.N и второй 15ol...l5.N групп элементов И соответственно.

Каждый блок 2.1,..2oN конвейерного управления (фиг. 2) содержит узел 35 памяти микрокоманд с полями 35.1 кода логических условий, 35.2 адреса следующей микрокоманды, выход которого является одновременно выходом 22 кода операции, 35.3 кода микрокоманды, и 35.4 микрооперации Конеп команды, регистр 36 адреса, регистр 37 микрокоманды, коммутатор 38 адреса, мультиплексор 39 элемент ИПИ 40, вход 18 логических условий, вход 24 кода операции, пер йый 33 и второй 34 синхровходы, выходы 21 микроопераций, 22 кода опе

рации и 23 сигнала микрооперации Конец команды,

Кажды блок 3, 1 . , .3,N регястроп (фиг, З) содержит группу из r:i pernc i

5 0 5

0

0

5

0

5

5

ров 4 I . 1 . . . 4 1 ,rn, группу блоков элементов Ш1И 42 . 1 .. .42 .п-1 , группу элементов ИЛИ 43.1...43,т, группу информационных входов 30.1...ЗО.т-1, группу входов 31 синхронизации, информационные выходы 24, выход 25 признака нуля первог о регистра Блокировка А и группу выходон 26 признаков нуля блока рет истров.

Каждый узел 4,1...4.N выборки (фиг, 4) содержит первую 44.1... 44.т-2 и вторую 45.1. . .45.in-l группы элементов И, триггер 46, элемент И 47, одновибратор 48, вход 9.2 синхроимпульса, вход 23 сигнала микрооперации Конец команды, вход 26 сигналов состояния блоков регистров, выход 27 выбора регистра, выход 28 сигнала Блокировка в, выход 29 управления синхронизацией .

Каждый коммутатор 5.1...5.N (фиг. 5) содержит группу блоков элементов И 49.1 . ..49.т-1 и формирователь 50 импульсов.

Каждый коммутатор 6.1.,.6.N (фиг. 6) содержит группу элементов И-ИЛИ 51.1...51.т-1 и элемент И 52.

Блок 9 синхронизации (фиг. 7) содержит генератор 53 тактовых импульсов, триггер 54 пуска и формирователь 55 импульсов:,

Вход 19 соединен с 5-входом триггера 54, вход 32 соединен с входом формирователя 55 импульсов, выход которого соединен с входом триггера 54, прямой выход триггера 54 соединен с управляющим входом генератора 53, выходы KOTOpoi o являются выходами 9.1-9.3 блока синхронизации.

На фиг. 8 использованы обозначения, введенные на фиг, 1-7.

Блок 1 памяти предназначен для хранения микрокоманд, которые считываются ло тактовым импульсам, пос- туг1аюп№м на синхровход регистра 8 микрокоманд. Блок 1 памяти имеет шесть полей: 1,1 микрокоманды Конец микропрограммы, 1.2 адреса следующей микрокоманды, 1.3 кода логических условий, 1,4 операционной части микрокоманды, 1,5 кода операции, 1,6 управляющей метки,

Блок 2 конвейерного управления предназначен для организании микропрограммного управления в i-м канале управления и функционирует следуюг тим образом.

По первому синхроимпульсу, поступающему Via вход 33, в регистр 36 ал, реса через коммутатор 38 по разрешающему (единичному) сигналу микрокоманды Конец команды, поступающему с выхода поля 35.4 блока 35 памяти микрокоманд, заносится код операции, поступающий на вход 24. По принятому коду операции на выходе узла 35 памяти формируется соответствующая данному коду операции микрокоманда, т.е. код операции выступает как адрес первой микрокоманды выполняемой микропрограммы. По второму тактовому импульсу, поступающему на вход 34, в регистр 37 микрокоманд считывается операционная часть микрокоманды, которая поступает на выход 21, являющийся одновременно выходом устройства. По очередному первому тактовому импульсу в регистр 36 адреса записывается адрес очередной микрокоманды, поступающей на его вход с выхода поля 35.2 блока 35 памяти через коммутатор 38 по разрешающему (нулевому) сигналу микрооперации Конец команды. По второму тактовому импульсу работа повторяется. Исключение составляет реализация микрокоманды ветвления (условного перехода)

Коммутатор 10 предназначен для ввода в систему кода микропрограммы с входа 16 или адреса очередной микрокоманды с выхода поля 1.2 блока 1 памяти.

Мультиплексор 11 предназначен для выделения значения проверяемого логического условия, поступающего на одну из групп входов 17 в соответствии ,с кодом логических условий, поступающим на управляющий вход мультиплексора с выхода поля 1.3 блока 1 памяти.

Элемент ИЛИ 12 служит для модификации младшего разряда адреса микрокоманды при реализации условного перехода микропрограммы.

Элемент ИЛИ-НЕ 13 предназначен для выделения сигнала остановки блока 9 синхронизации после появления сигналов Блокировка А всех блоков 3.1...3.N регистров.

Группы элементов И 14.1...14.N предназначены для управления подачей синхроимпульсов на входы блоков конвейерного управления в соответствии со значениями сигналов Блоки

27634

роика А i-ro блока регистров и Клокировка в (i-l)-rc блока регистров.

5 Устройство работает следующим образом.

В исходном состоянии все элементы обнулены (цепи установки исход- ног о состояния не показаны). С груп- 10 пы входов 16 на коммутатор 10 поступает начальный адрес микропрограммы. После прихода сигнала Пуск с входа 19 блока 9 синхронизации начинает генерироаать последовательности син- 5 Х1)иимпульсов. По тактовому импульсу 21 при разрешающем единичном сигнале с выхода поля 1.1 блока 1 памяти и нулевом с выхода 28.1 узла выборки код операции записывается в ре- гистр 7 (во всех остальных микрокомандах, кроме конечной, на выходе поля I.1 присутствует нулевой сигнал). С его выхода код операции поступает на вход блока 1 памяти. С выхода поля 1.5 код операции поступает на информационный вход первого коммутатора 5„1, адрес следующей микрокоманды с выхода поля 1.2 поступает на второй информационный вход комму- 30 татора 10, сигнал управляющей метки с выхода поля 1.6 поступает на первые управляющие входы узла 4.1 и второго коммутатора 6.1, разрешая запись кода операции в свободный 35 регистр блока З,, регистров. Операционная часть микрокоманды поступает с выхода поля 1.4 на информационный вход регистра 8,

Так как в исходном состоянии 40 блок 3.1 регистров обнулен, то по сигналам кода состояния, поступающим с выхода 26 о 1 блока регистров на вход узла выборки, он вырабатывает управляющие сигналы, обеспечивающие выббр 45 коммутаторами 5.1 и 6.1 для записи кода операции регистр 41.2 блока 3.1 регистров. На выходе 23.1 блока 2.1 присутствует сигнал микрооперации Конец команды, разрешающей 50 сдвиг информации. По второму тактовому 11мпульсу в выбранный регистр 41.2 заносится код операции, а в регистр 8 считывается операционная часть микрокоманды.

ij5 По третьему ттктовому импульсу 9..3 производится сдвиг информации в блоке 3.1 регистров, после чего на его выходе 24.1 появляется код выполняемой операции, При этом на

выходе 25.1 Блокировка А появляется единичный сигнал, деблокирующий прохождение импульсов синхронизации через элементы И 14.1 и 15.1 }:з синхровходы блока 2.1. По очередному импульсу 9.1 в регистр 7 считывается адрес очередной микрокоманды, в блок 2.1 считывается код операции с выхода 2. блока 3.1 регистров. По второму импульсу 9.2 работа повторяется до тех пор, пока все Г1-1 регистры блока 3.1 регистров не будут заполнены кодами операций. После этого на выходе 28.1 узла 4„1 вы- бо рки появляется сигнал Блокировка в, запрешаюший работу верхнего уровня управления, построенного на jcHOBe блока 1 памяти.

По окончании выполнения блоком 2.1 микропрограммы, обусловленной даннь м кодом операции на выходе 23. появляется сигнал Конец команды, разрешающий запись по импульсу 9.2 кода выполненной операции в регистр 41.2 блока 3.2 регистров и сдвиг по третьему импульсу 9,3 информации в блоке 3.1 регистров. После этого исчезает эапретаюший сигнал Блокировка в на управляющем инверсном входе регистра 7 и Блокировка А н входе элементов И 14.2 и 15.2. По очередному импульсу 9.1 в работу включается блок 2о2, а в центрально уровне управления выбирается микрокоманда, определчюптая т-й код операции. По импульсу 9.2 работа системы повторяется.

Втягивание системы в работу заканчивается после того, как (N-l)-n GJ-IOK конвейерного управления выполнит микропрог ПО первому коду операции Тактом работы блока конвейерного управления условимся называть отрезок времени выполнения н( микропрограммы по данному коду операции.

При рассмотрении организации функционирования системы (фиг, 8) применены следующие обозначения: К - микропрограмма, выполняемая J-M блоком конвеЙ1 рного vпpaвлeния по К-му коду операции.

В процессе работы устройства Б результате отличил времени выпоине- ния различными блоками конвейерного управления даже одних и тех же микропрог рамм соседние , -й и (,1--1)блоки разбе1 ак)тся на несколько

5

0

5

0

5

0

5

0

тактов. Если (Jtl)-й блок обгоняет .-й, т.е. ( + 1)-й выполняет (М-1)-ю . микропрограмму раньше, чем ,1-й М-ю, то возникает режим Блокировка А (j+l)-ro блока (фиг. 8а) и длится пока J-й блок не выполнит М-ю микропрограмму и (J+l)-й /блок получит в обработку очередной М-й код операции. Для устранения этого недостатка необходимо располагать блоки от nepBoi o до N-ro в порядке уменьшения их среднестатистического быстродействия, которое зависит от объекта управления, исходных данных и т,д.

При оптимальном расположении блоков конвейерного управления в устройстве блоков 2 в режиме Блокировка А будет минимальное количество. Сущность состоит в повышении производительности микропрограммного управляющего устройства путем организации плавающего такта работы с, Суть плавающего такта заключается в следующем: (х + О-й блок конвейерного управления начинает выполнение п-й микропрограммы, когда ее выполнение закончит i-й блок конвейерного управления. При этом не ожидается событие, когда все N блоков конвейерного управления завершат выполнение своих микропрограмм. Таким образом, условия выполнения п-й микропрограммы в (i+l)-M блоке управления зависят лишь от того, как функционировал i-й блок конвейерного управления в(п-1) такте работы, а не от условий функционирования в этом такте всего устройства в целом, состоящего из N блоков конвейерного управления.

Формула изобретения

I. Микропрограммное управляющее устройство, содержащее блок памяти микрокоманд, регистр адреса, регистр микроопераций, коммутатор адреса, мультиплексор.логических условий, элемент ИЛИ, генератор тактовых импульсов, п блоков конвейерного управления (где п - количество уровней управления), триггер запуска, первую и вторую группу из п. элементов И, причем вход кода операции устрой- ст.ча соединен с первым информационным входом коммутатора адреса, пео- вый выход генератора тактовых импульгоп соединен с входом синхронизации регистра адреся и с первыми входами первой группы элементов И, выход i-ro элемента И соединен с первым входом синхронизации i-ro бл ка конвейерного управления (,... п), второй выход генератора тактовых импульсов соединен с входом синхронизации регистра микроопераци и с первыми иходами элементов И второй группы, выход i-ro элемента И второй группы соединен с вторым входом синхронизации i-ro блока конвейерного управления, вход запуска устройства соединен с входом установки в 1 триггера чапуска, прямой выхо триггера запуска соединен с входом запуска генератора тактовых импульсов, с второго по (п+1)-й входы логических условий устройства соединены с входами логических условий соответственно с первого по п-и блоков конвейерного управления, выходы микроопераций которых соединены соответственно с второго по (п+1)-й выходами микроопераций устройства, отличающееся тем, что, с целью повышения быстродействия, оно дополнительно содержит п блоков регистров, первую и вторую группы из п коммутаторов, п узлов выборки, одновибратор, элемент ИЛИ-НЕ, причем информационный выход i-ro блока

регистров соединен с входом кода операции i-ro блока конвейерного управления, выход поля кода операции блока памяти микрокоманд соединен с информационным входом первого коммутатора первой группы, выход кода операции J-ro блока конвейерного управления (,j l,.,., n-l) соединен с информационным входом (j+l)-ro коммутатора первой группы, выход метки режима записи блока памяти микрокоманд соединен с входом стробирования первого узла выборки и с первым входом стробирования первого коммутатора второй группы, выход Конец команды i-ro блока конвейерного управления соединен с вторым входом стробирования J-ro коммутатора второй группы, с первым входом стробирования (j+l)-ro коммутатора второй группы, первь;й выход i-ro узла выборки соединен с управляющим входом i-ro коммутатора первой группы, второй выход первого узла выборки соединен с входом разре01ения за,

152763410

писи регистра адреса, выход признака нуля первого регистра i-ro блока регистров соединен с вторыми вхо5

дами 1-х элементов первой и второй

групп элементов И, второй выход К-го

() узла выборки соединен с

третьими входами (К-1)-х элементов И первой и второй групп, выходы приз- 10 нака нуля первого регистра с первого по п-й блоков регистров соединен соответственно с первого по п-й входами элементов ИЛИ-НЕ, выход которого соединен с входом одновибра- 15 тора, выход которого соединен с входом установки в нуль триггера запуска, третий выход генератора тактовых импульсов соединен с входами синхро- иизации с первого по п-й коммутато- 0 ров первой и второй групп, второй выход генератора тактовых импульсов соединен с входом синхронизации с первого по п-й узлов выборки, третий выход i-ro узла выборки соединен с 25 информационным входом i-ro коммутатора второй группы, группа выходов которого соединена с группой входов синхронизации i-ro блока регистров, группа выходов i-ro коммутатора вто- 30 рой группы соединена с группой информационных входов i-ro блока регистров, группа выходов признака нуля i-ro блока регистров соединена с группой входов i-ro узла выборки, причем блок конвейерного управления содержит коммутатор, первый и второй регистры, узел памяти микрокоманд, мультиплексор, элемент ИЛИ, причем первый и второй входы синхро- .0 ничации блока конвейерного управления соединены соответственно с входами синхронизации первого и второго регистров, вход логических условий блока конвейерного управления . соединен с информационным входом мультиплексора, выход которого соединен с первым входом элемента ИЛИ, выход которого соединен с младшим разрядом первого информационного Q входа коммутатора, выход которого соединен с информационным входом первого регистра, выход которого соединен с адресным входом узла памяти микрокоманд, выход поля микроопераций которого соединен с информационным входом второго регистра, выход которого соединен с выходом микроопераций блока конвейерного управления, вход кода операции бло35

55

к а кои пей г рн о г с упрпвления соединен с n lOiUt .M (И.фс рмациоиным рходпм коммутатор;;, ныход г. Конец Kor-i.-iu- ды yTiui г;амУ1т, микрокоманд coe/UiHen с. yir,a iiinioiiiT .i иходом коммутатора и с. пыуодол комянды (1лока кон- иейериог о у1 ранления, старшие ды рыхода ночя адреса уяла памяти :-и Крокоманд соединены со старшими ра зряд. чмг первог-о информационного входа кс. -1ут.1тор,а и с т hrxoдo ; кода сшерадин блока коиЕ еГ ерног о управления, MiiivTi nfi разряд 1.ыходаио; Я адре- с-;; у Л.1 и,|мятк микроонеранин С( с TiTop r.M ч:{одом э:том(нта ИЛИ, 31,1ход пог я логи ескмх условий узля. памяти мнкро:тт:ераии 1 соединен с yiifjaririH- KiuiHM «ходом муль 1 инлексора, причем б.чок регистров содержит с нергзого по г.-й peiKc vphi, с первого по (т-2,;-й учлы элементов 11ПИ, с первого по щ-й элементы ИЛИ, причем группа входов синхронизации блока регистров соединена с входами син- хронизацип с liepnoro по т-й регистров, Н1,ход t-ro регистра (t -1 , . . . ,Г:) соединен с t-ro элемента Ш1И, с иервсгс lio ()-й входь группы . нформзиио 1 ьп-: входов бдока регнст- ;юв сооди;те; ;- соответственно с пер- вьпчи яходчг- г: г первого по (m-Z) элементов Ш1{, выходы к торых соединены соЛ: ветственно с И;:форма- циoнны :и :- ХОдами с второго по (ш-Ореги.строл, ()й вход группы инфор мационнь х J.ходов блока регистров соединен с информационным входом ri-i o регистра, второго регистра соединен с ниформационкым входом первого регистра, выход которого соединен с ИНфОрМ. ДИОННЬР выходом OjiOKo

pcTiiCTpoi ,, выход первого элемента IlTIli соединен с выходом цриткпка му- лй первого регистра блока регистров, выходь г второго по m-f: элементов ЯПИ соединен группой .в признака нуля блока регистров, nHfJiopMa- ционный выход 1-го регнстра (Т -З,... ш) соединег. с вторым нходом (л-2)-го узлл 3j-; -i M JBTOB ИПИ, кроме тело, утсл выборки содержич ТК-триггер, одно- ви&ратор, элемент И, первую и вторую гругнтп) элементов И, причем } ,ход стро бирования узла выборки соединен с входс:м одиоиьбратора, выход которого соединен с входом установки в единицу ТК-тоигтера, вых1:5Д которого соединен с iU pBMM входом элемент И,

1П1ХОД )го соединен с вход|-м cviHxpcuunaHVHi I К-тригггчп , с К-вхо- дом К-1-ри гг ера и с нерв1,|пи входами лем1Ч1тов И BTopoi i 1 руппы, вход син- хрои1-;зации узда выборки соединен с вторым вхг)дом элемента И, группа входг)в учла выборки соединена с пер- вьпии входами элементов И первой группы, первый вход группы входов узда выборки соединен с вторым входом первого элемента И второй группы и с первым рпзрядог первого выхода узла рь борки, с второго по т-й входы

5 группы входов узла выборки соединены с инверсными входами с второго по т,-й эле,менто1 И, выходы к(;торых соединены с остальными разрядами пер- вог О выхода узла выборки и с вторыми

0 входами с второго, по (т+П-й элементов И второй группы, выходы элементов И второй группы являются третьим выходом узла выборки, вторым выходом KOTopoi o является т-й вход

5 группы входов узла выборки.

2. Устройство по п. 1, о т л и - ч а ю п е е с я тем, что коммутатор цервой группы содержит одновиб- ратор и 1руппу блоков элементов И,

0 причем вход синхронизации коммутатора соедушеи с входом одновибратора, выход которого соединен с первым входом блоков элементов И группы, выходы которых подключены к группе выходов :ом - утатора, управляющий вход коммутатора поразрядно подключен к вторым входам блока элементов И группы, информационный вход коммутатора подключен к остальным входам каждого

Блока элементов И, 0

3. Устройство по п. 1, о т л и - ч а ю щ е е с я тем, что коммутатор Бторой группы содержит элемент

5 И, т руг:пу элементов И-ИЛИ, причем

нход синхронизации коммутатора соединен с первым входом элемента И и первыми входами элементов И-ИЛИ группы, первый стробирующий вход коммуQ татора соединен с вторым входом элемента ь и вторыми входами элементов И-ИЛИ группы, второй стробирующий вход коммутатора соединен с третьими входами элементов И-ИЛИ группы, инг формацион11ый вход коммутатора соединен поразрядно с четвертыми входами .лементов И-ИЛИ группы, выходы элементов И и элементов И-ИЛИ группы образуют выход коммутатора.

5

IS

ю

ФИ а

to

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1282121A1 |

| Адаптивная система обработки данных | 1984 |

|

SU1267429A1 |

| Мультимикропрограммное устройство управления с контролем | 1985 |

|

SU1272333A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1471190A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1381506A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Конвейерная система для программного управления | 1989 |

|

SU1665340A1 |

Изобретение относится к вычислительной технике, может применяться в устройстве обработки данных с конвейерным выполнением микропрограмм. Целью изобретения является повышение быстродействия микропрограммного управляющего устройства путем организации "плавающего" такта работы при конвейерном выполнении микропрограмм. Цель достигается введением группы блоков регистров, группы узлов выбора, первой и второй групп коммутаторов. Сущность состоит в организации "плавающего" такта работы, заключающегося в том, что (I+1)-й блок конвейерного управления начинает выполнение N-й микропрограммы, когда ее выполнение закончит I-й блок конвейерного управления. При этом не ожидается событие, когда все N блоков конвейерного управления завершат выполнение своих микропрограмм. Таким образом, условия выполнения N-й микропрограммы в (I+1)-м блоке конвейерного управления явно зависит лишь от того, как функционировал I-й блок конвейерного управления в [(N-1)+I]-м такте работы, а не от условий функционирования в этом такте всего устройства в целом, состоящего из N блоков конвейерного управления. 2 з.п. ф-лы, 8 ил.

Ui

Jf.f

J5.f

(1.

с

ff

If

5,2

зш

1

191 т

3f.

d

г.г

.w/r (}.1... 3N)peiu с т pot

«Mm lil

5f#

V,

К

n o-

JJL

JJ

-i

5лш(.1...г.и}миу

--trO

r

iff

vb H

af

iki

/лг

if/

T

Hi

777 Zf

)

.31t

)t

JW

г.г

tt.i

ГИ

ь

И

С1Л

Тл

&иМ

J.#

tqpl

q/M

Ч-Т

f./

Ji

«

(Риг. г

KS.i (Si)

Ш

Фиг. 3

26

нп

л/z A-/J Kf HIS

КП «n /f/J Klfi Ю5

иг//

l/rj/ /rj H33H3

Фиг.7

KJS

s.

д Фиг. 8

| Микропрограммное устройство управления | 1976 |

|

SU596947A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Электронная промьппленность, 1978, № 6, с | |||

| Способ смешанной растительной и животной проклейки бумаги | 1922 |

|

SU49A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1471190A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-12-07—Публикация

1987-04-27—Подача