с входом запуска и выходом ошибки блока ввода информации, инверсный выход первого триггера блока управления соединен с входом начальных установок генератора случайных чисел, прямой выход первого триггера блока управления соединен с первым информационным входом блока индикации и первым входом элемента И, второй вход которого соединен с выходом генератора импульсов, выход элемента И соединен с тактовым входом генератора случайных чисел и управляющим входом блока сравнения, выход которого соединен с первыми входами всех элементов И группы, управляющим входом первого дешифратора и единичными входами второго и пятого триггеров блока управления, нулевой вход второго триггера блока управления объединен с входами начальных установок регистра, блока индикации и блока памяти, первая группа информационных выходов которого соединена .с управляющей группой входов коммутатора и группой информационных входов первого дешифратора , выход которого соединен с информационным входом регистра, выход регистра и вторая группа информационных выходов блока памяти соединены с группой информационных входов второго дешифратора, управляющий вход которого соединен с выходом конца выборки блока памяти, вторыми входами третьего элемента ИЛИ и пятого элемента И блока управления и входом элемента НЕ блока управления.

выход восьмого элемента ИЛИ блока управления соединен с вторым информационным входом блока индикации, выход шестого элемента ИЛИ блока управления соединен с первым входом шестого элемента И блока управления, третьим информационным входом блока индикации и входом элемента НЕ, выход которого соединен с вторыми входами элементов И группы, третьи входы которых соединены с соответствующими информационными выходами группы генератора случайных чисел и информационными входами группы коммутатора, первая и вторая группы входов-выходов которого соединены соответственно с группами входов-выходов контролируемого блока и эталонных блоков замены группы, тактовый вход коммутатора соединен с выходом щестого элемента И блока управления и входом обращения блока памяти, выход генератора импульсов блока управления соединен с вторым входом щестого элемента И блока управления, четвертый информационный вход блока индикации соединен с выходом ошибки блока ввода информации, выходы элементов И группы и группа выходов второго дешифратора соединены соответственно с первой и второй группами информационных входов блока индикации, адресный информационный и управляющий выходы блока ввода информации соединены соответственно с адресным информационным и управляющим входами блока памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1981 |

|

SU1037259A1 |

| Устройство для психологических исследований | 1989 |

|

SU1683684A1 |

| Устройство для тренировки памяти обучаемого | 1988 |

|

SU1520574A1 |

| Устройство для контроля считываемой информации | 1984 |

|

SU1180903A1 |

| Устройство для построения диагностического теста и диагностирования комбинационных схем | 1983 |

|

SU1160420A2 |

| Устройство для профессионального отбора операторов | 1990 |

|

SU1778768A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство для профессионального отбора операторов | 1990 |

|

SU1714649A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| Устройство для контроля блоков оперативной памяти | 1986 |

|

SU1358003A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДИСКРЕТНОЙ АППАРАТУРЫ С БЛОЧНОЙ СТРУКТУРОЙ, содержащее генератор импульсов, генератор случайных чисел, блок сравнения, эталонный блок, блок управления, содержащий три элемента задержки, причем информационная группа выходов генератора случайных чисел соединена с группой входов эталонного блока, выход которого соединен с первым информационным входом блока сравнения, второй информационный вход которого соединен с выходом контролируемого блока, отличающееся тем, что, с целью повышения диагностической способности устройства, в него введены блок ввода информации, блок памяти, два дешифратора, элемент И, элемент НЕ, блок индикации, регистр, группа элементов И, коммутатор, группа эталонных блоков замены, в блок управления введены пять триггеров, восемь элементов ИЛИ, щесть элементов И, элемент НЕ, генератор импульсов, счетчик, дешифратор, кнопка сброса, кнопка пуска, кнопка включения ввода информации, кнопка включения блока памяти, причем в блоке управления первый вход первого элемента ИЛИ через контакт кнопки пуска соединен с шиной единичного потенциала, выход первого элемента ИЛИ соединен с единичным входом первого триггера, нулевой вход которого соединен с выходом второго элемента ИЛИ, первый вход которого объединен с первыми входами третьего и четвертого элементов И нулевым входом второго триггера и через контакты кнопки сброса соединен с щиной единичного потенциала, выход третьего элемента ИЛИ соединен с нулевым входом третьего триггера, входом счетчика и первым входом пятого элемента ИЛИ, выход которого соединен с нулевым входом четвертого триггера, единичный вход которого через контакты кнопки включения ввода информации соединен с шиной единичного потенциала, выход счетчика соединен с входом дешифратора, выходы которого соединены с входами шестого элемента ИЛИ и входами седьмого элемента ИЛИ, выход которого соединен с первым входом первого элемента И, выход которого через первый элемент задержки соединен с вторым входом первого элемента ИЛИ, выход четвертого элемента ИЛИ соединен с нулевым входом пятого триггера, прямой выход которого соединен с первым входом второго элемента И, выход которого соединен с первым входом третьего W элемента И, выход которого соединен со счетным входом счетчика, второй вход третьего элемента И соединен с прямым выходом третьего триггера, единичный вход которого через контакты кнопки включения блока памяти соединен с шиной единичного потенциала, прямой и инверсный выходы второго триггера соединены соответственно с вторым входом первого элемента И и пера вым входом четвертого элемента И, выход 00 которого соединен с первым входом восьмого ( элемента ИЛИ, второй вход которого соединен с выходом пятого элемента И, выход сд ьо элемента НЕ через второй элемент задержки соединен с третьим входом первого элемента И, выход конца работы генератора случайных чисел соединен с вторыми входами второго и четвертого элементов И блока управления, вторым входом второго элемента ИЛИ блока управления, первым входом пятого элемента И блока управления и входом третьего элемента задержки блока управления, выход которого соединен с вторым входом четвертого элемента ИЛИ блока управления, прямой выход четвертого триггера и второй вход пятого элемента ИЛИ блока управления соединены соответственно

Изобретение относится к автоматике, контрольно-измерительной и вычислительной технике и может быть использовано для контроля дискретной аппаратуры блочной структуры, имеющей в своем составе комбинационные и последовательностные логические схемы.

Цель изобретения - повышение диагностической способности устройства.

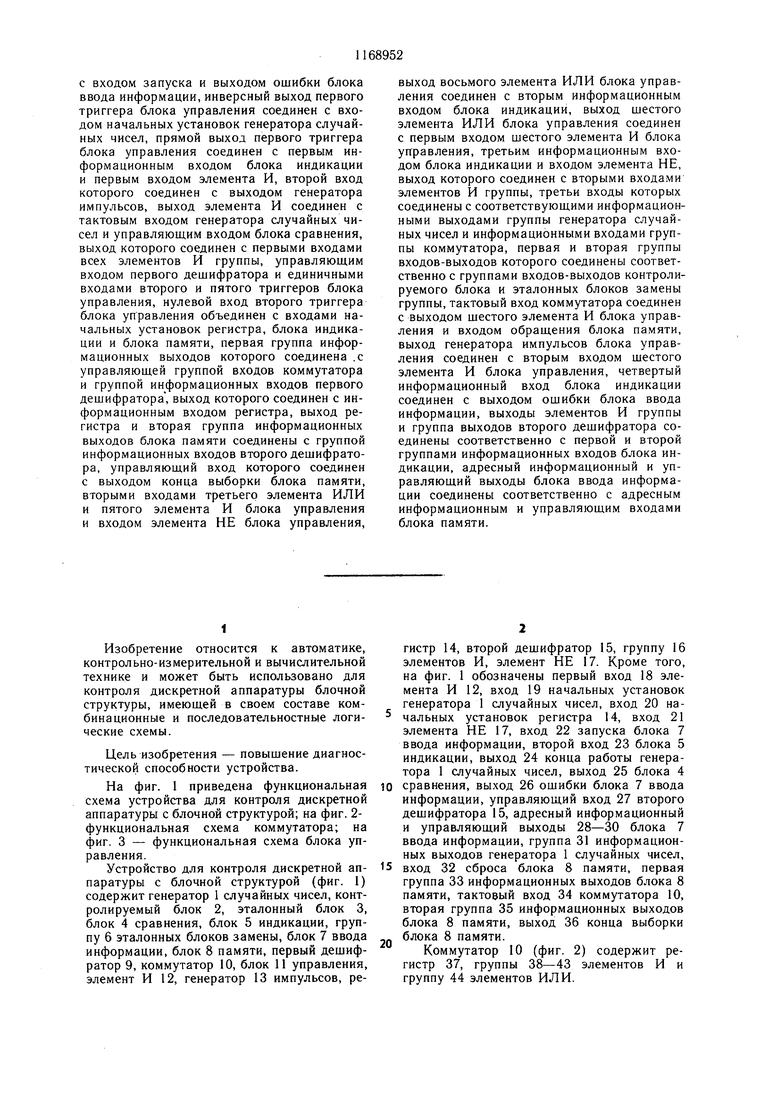

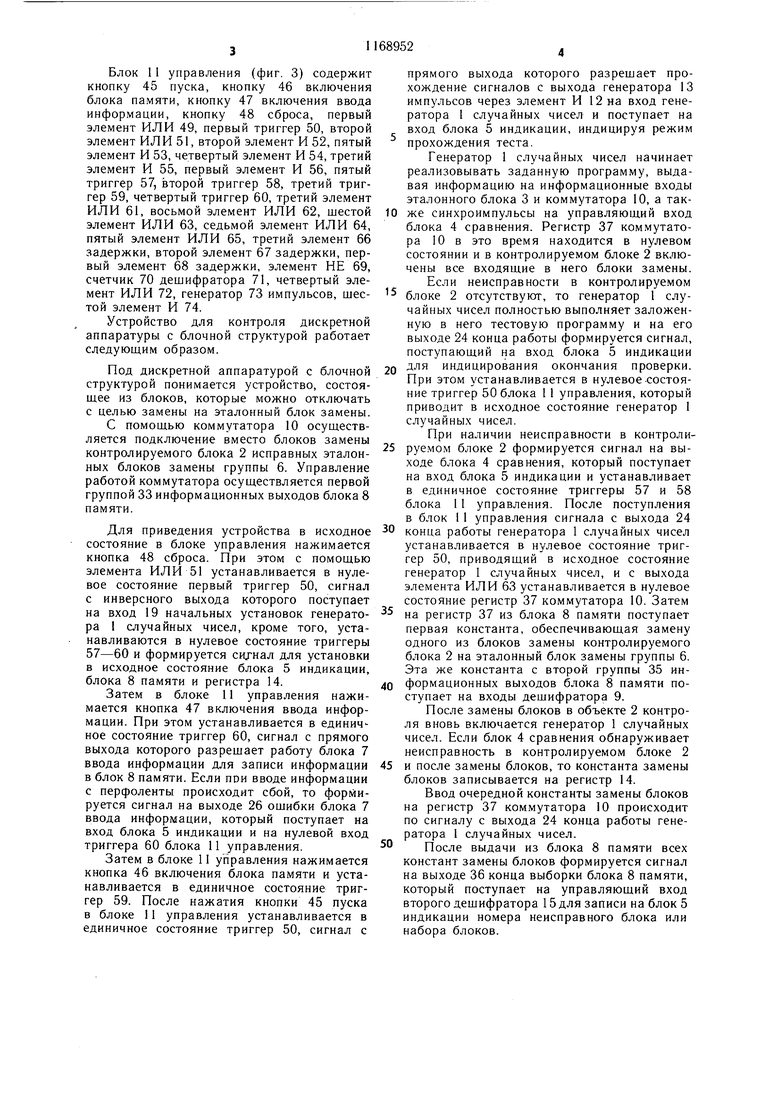

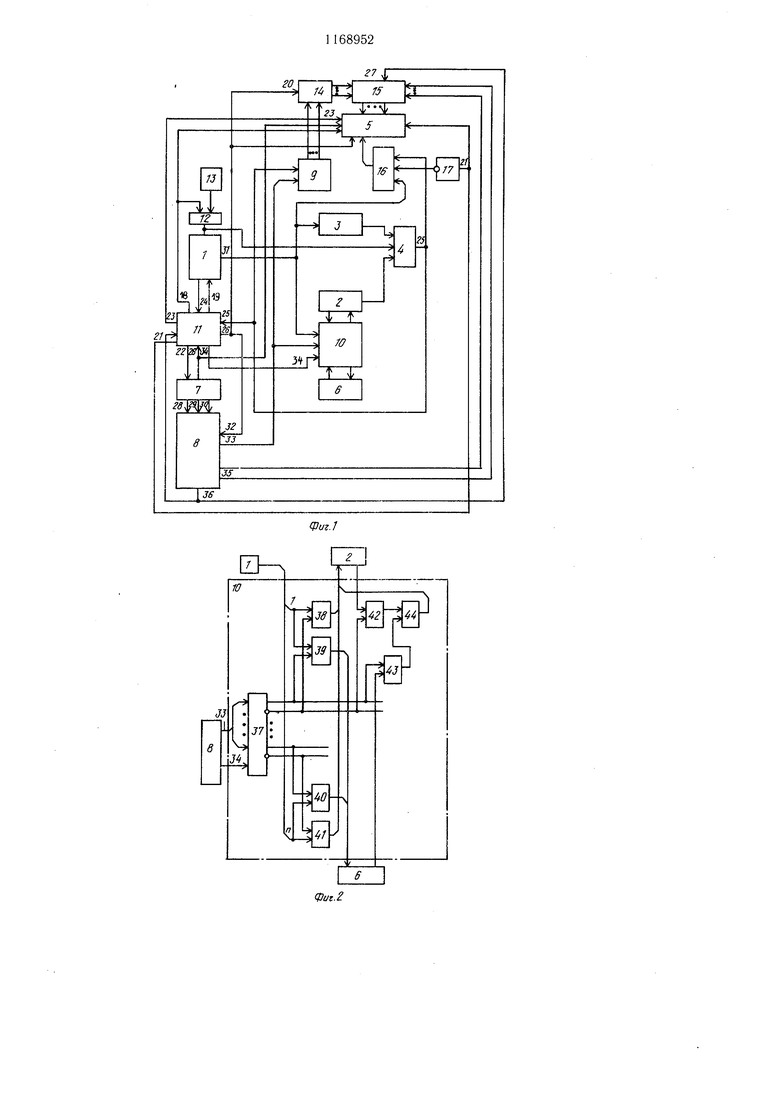

На фиг. 1 приведена функциональная схема устройства для контроля дискретной аппаратуры с блочной структурой; на фиг. 2функциональная схема коммутатора; на фиг. 3 - функциональная схема блока управления.

Устройство для контроля дискретной аппаратуры с блочной структурой (фиг. 1) содержит генератор 1 случайных чисел, контролируемый блок 2, эталонный блок 3, блок 4 сравнения, блок 5 индикации, группу 6 эталонных блоков замены, блок 7 ввода информации, блок 8 памяти, первый дешифратор 9, коммутатор 10, блок 11 управления, элемент И 12, генератор 13 импульсов, регистр 14, второй дешифратор 15, группу 16 элементов И, элемент НЕ 17. Кроме того, на фиг. I обозначены первый вход 18 элемента И 12, вход 19 начальных установок генератора 1 случайных чисел, вход 20 на чальвых установок регистра 14, вход 21 элемента НЕ 17, вход 22 запуска блока 7 ввода информации, второй вход 23 блока 5 индикации, выход 24 конца работы генератора 1 случайных чисел, выход 25 блока 4

0 сравнения, выход 26 ошибки блока 7 ввода информации, управляющий вход 27 второго дешифратора 15, адресный информационный и управляющий выходы 28-30 блока 7 ввода информации, группа 31 информационных выходов генератора 1 случайных чисел,

5 вход 32 сброса блока 8 памяти, первая группа 33 информационных выходов блока 8 памяти, тактовый вход 34 коммутатора 10, вторая группа 35 информационных выходов блока 8 памяти, выход 36 конца выборки

блока 8 памяти.

Коммутатор 10 (фиг. 2) содержит регистр 37, группы 38--43 элементов И и группу 44 элементов ИЛИ.

Блок 11 управления (фиг. 3) содержит кнопку 45 пуска, кнопку 46 включения блока памяти, кнопку 47 включения ввода информации, кнопку 48 сброса, первый элемент ИЛИ 49, первый триггер 50, второй элемент ИЛИ 51, второй элемент И 52, пятый элемент И 53, четвертый элемент И 54, третий элемент И 55, первый элемент И 56, пятый триггер 57, второй триггер 58, третий триггер 59, четвертый триггер 60, третий элемент ИЛИ 61, восьмой элемент ИЛИ 62, шестой элемент ИЛИ 63, седьмой элемент ИЛИ 64, пятый элемент ИЛИ 65, третий элемент 66 задержки, второй элемент 67 задержки, первый элемент 68 задержки, элемент НЕ 69, счетчик 70 дешифратора 71, четвертый элемент ИЛИ 72, генератор 73 импульсов, шестой элемент И 74.

Устройство для контроля дискретной аппаратуры с блочной структурой работает следуюшим образом.

Под дискретной аппаратурой с блочной структурой понимается устройство, состояшее из блоков, которые можно отключать с целью замены на эталонный блок замены.

С помощью коммутатора 10 осуществляется подключение вместо блоков замены контролируемого блока 2 исправных эталонных блоков замены группы 6. Управление работой коммутатора осуществляется первой группой 33 информационных выходов блока 8 памяти.

Для приведения устройства в исходное состояние в блоке управления нажимается кнопка 48 сброса. При этом с помощью элемента ИЛИ 51 устанавливается в нулевое состояние первый триггер 50, сигнал с инверсного выхода которого поступает на вход 19 начальных установок генератора 1 случайных чисел, кроме того, устанавливаются в нулевое состояние триггеры 57-60 и формируется сигнал для установки в исходное состояние блока 5 индикации, блока 8 памяти и регистра 14.

Затем в блоке 11 управления нажимается кнопка 47 включения ввода информации. При этом устанавливается в единичное состояние триггер 60, сигнал с прямого выхода которого разрешает работу блока 7 ввода информации для записи информации в блок 8 памяти. Если пои вводе информации с перфоленты происходит сбой, то формируется сигнал на выходе 26 ощибки блока 7 ввода информации, который поступает на вход блока 5 индикации и на нулевой вход триггера 60 блока 11 управления.

Затем в блоке II управления нажимается кнопка 46 включения блока памяти и устанавливается в единичное состояние триггер 59. После нажатия кнопки 45 пуска в блоке 11 управления устанавливается в единичное состояние триггер 50, сигнал с

прямого выхода которого разрешает прохождение сигналов с выхода генератора 13 импульсов через элемент И 12 на вход генератора 1 случайных чисел и поступает на вход блока 5 индикации, индицируя режим прохождения теста.

Генератор 1 случайных чисел начинает реализовывать заданную программу, выдавая информацию на информационные входы эталонного блока 3 и коммутатора 10, а также синхроимпульсы на управляющий вход блока 4 сравнения. Регистр 37 коммутатора 10 в это время находится в нулевом состоянии и в контролируемом блоке 2 включены все входящие в него блоки замены. Если неисправности в контролируемом

блоке 2 отсутствуют, то генератор 1 случайных чисел полностью выполняет заложенную в него тестовую программу и на его выходе 24 конца работы формируется сигнал, поступающий на вход блока 5 индикации

0 для индицирования окончания проверки. При этом устанавливается в нулевое-состояние триггер 50 блока 1 1 управления, который приводит в исходное состояние генератор 1 случайных чисел.

При наличии неисправности в контролируемом блоке 2 формируется сигнал на выходе блока 4 сравнения, который поступает на вход блока 5 индикации и устанавливает в единичное состояние триггеры 57 и 58 блока 11 управления. После поступления в блок 11 управления сигнала с выхода 24

0 конца работы генератора 1 случайных чисел устанавливается в нулевое состояние триггер 50, приводящий в исходное состояние генератор 1 случайных чисел, и с выхода элемента ИЛИ 63 устанавливается в нулевое состояние регистр 37 коммутатора 10. Затем

на регистр 37 из блока 8 памяти поступает первая константа, обеспечивающая замену одного из блоков замены контролируемого блока 2 на эталонный блок замены группы 6. Эта же константа с второй группы 35 информационных выходов блока 8 памяти поступает на входы дешифратора 9.

После замены блоков в объекте 2 контроля вновь включается генератор 1 случайных чисел. Если блок 4 сравнения обнаруживает неисправность в контролируемом блоке 2

5 и после замены блоков, то константа замены блоков записывается на регистр 14.

Ввод очередной константы замены блоков на регистр 37 коммутатора 10 происходит по сигналу с выхода 24 конца работы генератора 1 случайных чисел.

После выдачи из блока 8 памяти всех констант замены блоков формируется сигнал на выходе 36 конца выборки блока 8 памяти, который поступает на управляющий вход второго дешифратора 15 для записи на блок 5 индикации номера неисправного блока или набора блоков.

| Устройство для поиска неисправностей бесповоротных комбинационных схем | 1974 |

|

SU526834A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 3614608, кл | |||

| Телефонный аппарат, отзывающийся только на входящие токи | 1921 |

|

SU324A1 |

Авторы

Даты

1985-07-23—Публикация

1983-12-19—Подача