го элемента И и входом первого элемента НЕ, отличающееся тем, что, с цепью повышения быстродействия, оно содержит два дешифратора, пять счетчиков, элемент НЕ, триггер, шесть элементов РШИ, семь элементов И, схему сравнения, а блок управления содержит два триггера, кнопку пуска, три элемента ИЛИ, группу элементов И, регистр, причем выходы формирователей импульсов соединены с информационными входами второго дешифратора, первый выход которого соединен с первыми входами шестого, седьмого, восьмого и девятого элементов ИЛИ, п-й выход второго дешифратора (где п - число информационных входов устройства) соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом второго триггера, единичный вход которого соединен с вторым входом десятого элемента ИЛИ и подключен к кнопке пуска, выход первого элемента ИЛИ соединен с нулевым входом вгорого триггера и первым входом одинадцатого элемента ИЛИ, выход второго триггера - с вторым информационным входом блока индикаци и первым входом третьего элемента И, второй вход которого со.единен с выходом первого элемента НЕ, выход третьего элемента И соединен с единичным входом первого триггера, второй вход десятого элемента ИЛИ подключен к кнопке сброса, выход десятого элемента ИЛИ соединен с входом сброса третьего регистра и нулевым входом третьего триггера, выход которого соединен с третьим входом первого элемента ИЛИ, выходы второго регистра соединены с первой группой информационных входов блока индикации и с первыми входами соответствующих элементов И первой группы, вторые входы элементов И первой группы соединены с выходом одинадцатого элемента ИЛИ и единичным входом третьег триггера, выход первого элемента ИЛИ соединен с вторыми входами шестого и седьмого элементов ИЛИ и первым входом двенадцатого элемента ИЛИ, счетный вход второго счетчика соединен с выходом формирователя синхросигнала, вторым входом двенадцатого элемента ИЛИ и со счетным входом третьего счетчика, выход двенадцатого элемента ИЛИ соединен со счетным входом четвертого счетчика, выход переполнения которого соединен с входом второго элемента НЕ, первьм входом тринадцатого элемента ИЛИ и третьим входом шестого элемента ИЛИ, выход второго элемента НЕ соединен с первым входом четвертого элемента И, выход которого соединен с входом сброса четвертого счетчика и первыми входами пятого, шестого и седьмого элементов И, выходы которых соединены со счетными входами четвертого, пятого и шестого счетчиков соответственно, входы сброса которых соединены с выходом восьмого элемента ИЛИ, третий вход которого соединен с выходом восьмого элемента И, выходы четвертого, пятого и шестого счетчиков соединены с первой, второй и третьей группами входов второй схемы сравнения, первый, втопой и третий входы третьего дешифратора соединены с вторыми входами пятого, шестого и седьмого элементов И соответственно, четвертый выход третьего дешифратора соединен -с первыми входами восьмого и девятого элементов И и входом разрешения второй схемы сравнения, выход Неравно которой соединен с вторым входом девятого элемента И, выход которого соединен с вторым входом тринадцатого элемента ИЛИ, четвертым входом шестого элемента ИЛИ и третьим информационным входом блока индикации, выход Равно второй схемы сравнения соединен с вторым входом восьмого элемента И, входы обнуления второго и третьего счетчиков соединены с выходами седьмого и восьмого элементов ИЛИ соответственно, второй выход генератора тактовых импульсов соединены с вторым входом третьего элемента И, третий вход которого соединен с выходом чет вертого триггера, единичный -вход которого соединен с выходом десятого элемента РШИ, нулевой вход четвертого триггера соединен с выходом шестого элемента ИЛИ, четвертый вход которого соединен с выходом девятого элемента И, четвертым информационным входом блока индикации, вторым входом тринадцатого элемента ИЛИ, выход которого соединен с первыми входами элементов И второй группы, вторые входы которых соединены с соответствующими выходами второго дешифратора, первый.

второй и третий входы одинадцатого элемента ИЛИ соединены с выходами второго элемента И, тринадцатого элемента ИЛИ и выходом девятого элемента И соответственно, выходы третьего регистра соединены с BToVoH

.группой информационных входов блока индикации, выходы второго и третьего счетчиков соединены с информационными входами второго и третьего регуляторов соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля считываемой информации | 1982 |

|

SU1056200A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для управления ленточным перфоратором | 1990 |

|

SU1837333A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1741137A1 |

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Устройство для контроля считывания и записи информации | 1986 |

|

SU1341644A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Устройство для передачи информации | 1989 |

|

SU1700571A1 |

| Устройство для поиска информации | 1988 |

|

SU1640713A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СЧИТЫВАЕМОЙ ИНФОРМАЦИИ, содержащее генератор тактовых импульсов, группу формирователей импульсов, формирователь синхросигнала, блок управления, содержащий кнопку сброса и первый элемент ИЛИ, блок контроля, содержаищй два регистра, первую схему сравнения, первый счетчик, первый дешифратор, пять элементов ИЛИ, два элемента И, коммутатор, первый триггер, первый элемент НЕ, блок индикации, причем информационные входы устройства соединены с соответствующими входами формирователей импульсов группы, синхровход устройства соединен с входом формирователя синхросигнала, выходы формирователей импульсов группы соединены с информационными входами первого и второго регистров, выходы которых соединены с первой и В1орой группами информационных входов первой схемы сравнения, первый выход генератора тактовых импульсов соединен с первым входом первого элемента И, второй вход которого соединен с выходом первого триггера, выход первого элемента И соединен со счетным входом первого счетчика, выходы которого соединены с информационными входами первого дешифратора, первый, второй и третий выходы которого соединены с первыми входами второго, третьего и четвертого элементов ИЛИ, четвертый, пятый и шестой выходы первого дешифратора соединены с вторыми входами второго, третьего и четвертого элементов ОТИ соответственно, выход второго элемента ИЛИс входом записи второго регистра, выходы третьего и четвертого элементов ИЛИ соединены с входом записи с первого регистра и входом разрешения первой схемы сравнения соответствен(Л С но, выходы второго регистра - с соответствующими информационными входами коммутатора, управляющий вход которого соединен с выходом Равно первой схемы сравнения и с первым входом пятого элемента ИЛИ, выход Неравно первой схемы сравне00 о со о со ния соединен с первым входом второго элемента И, второй вход которого соединен с шестым выходом первого дешифратора, выход второго элемента И соединен с вторым входом пятого элемента ИЛИ и первым информационным входом блока индикации, выход пятого элемента ИЛИ соединен с первым входом элемента ИЛИ, второй вход кото рого подключен к кнопке сброса, выход первого элемента ИЛИ соединен с нулевым входом первого триггера и входом сброса первого счетчика, информационные выходы коммутатора являются информационными выходами устройства, выход формирователя синхросигнала соединен с третьим входом перво

1

Изобретение относится к вычислительной технике и может найти применение в вычислительных, управляющих, информационных и контролирующих системах для контроля информации, считываемой с перфоленты.

Цель изобретения - повышение быстродействия.

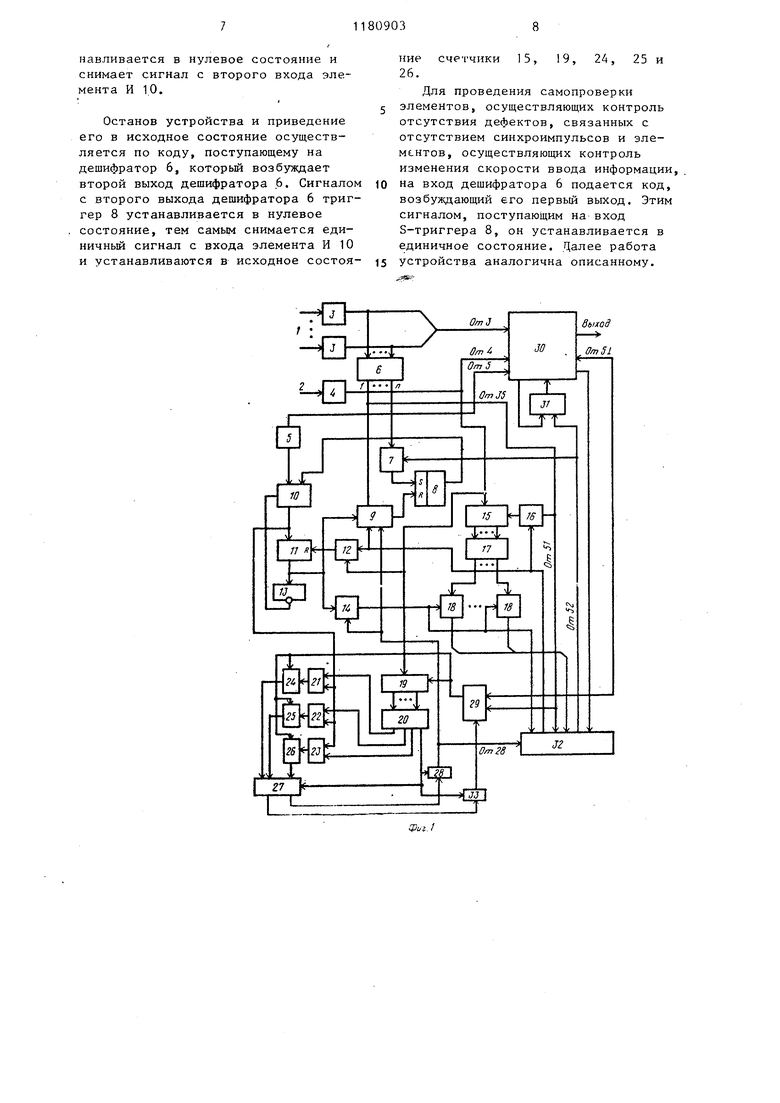

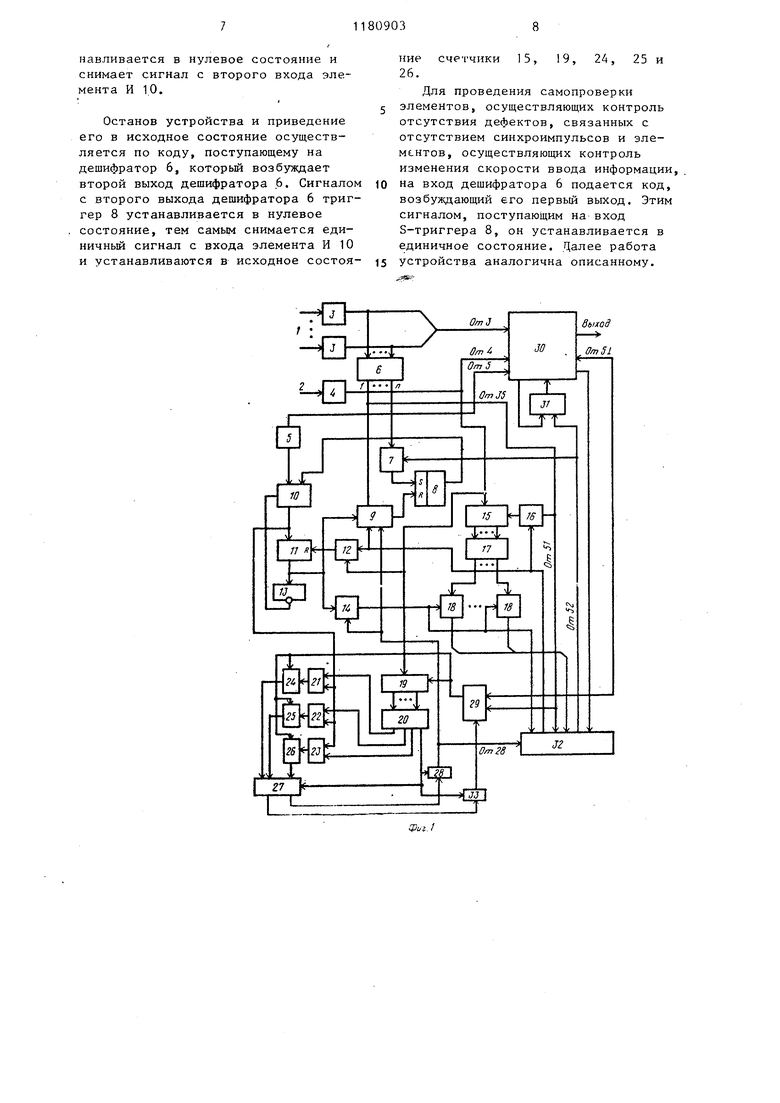

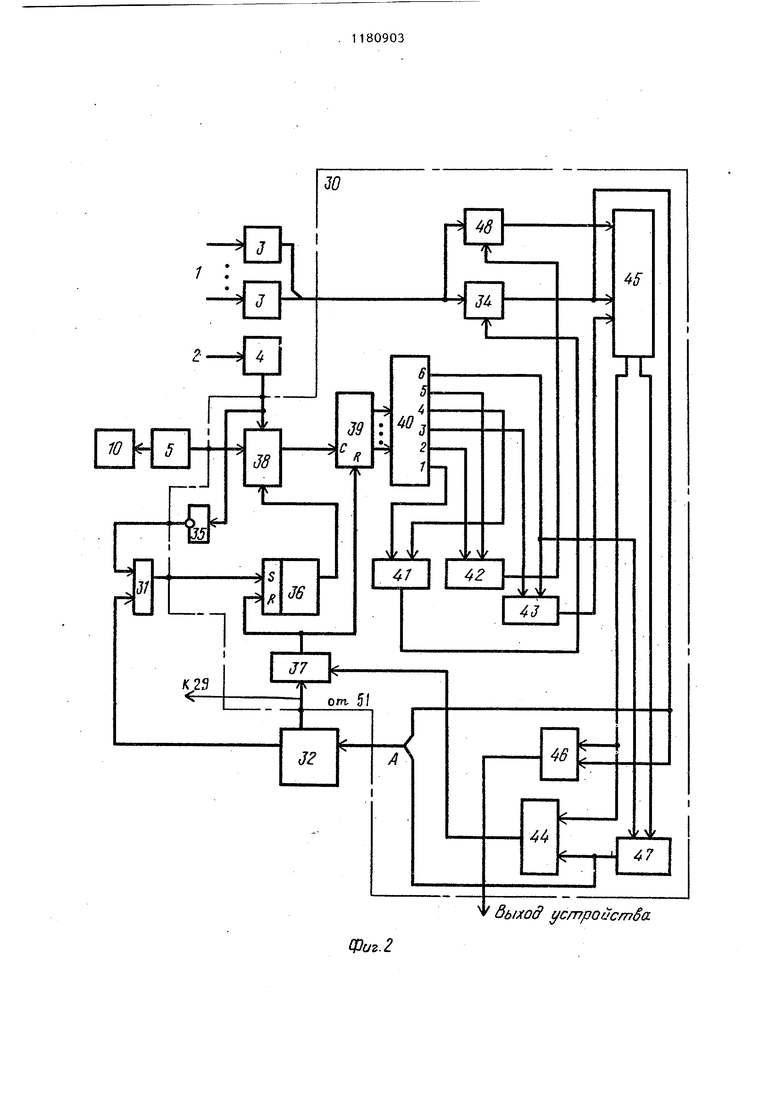

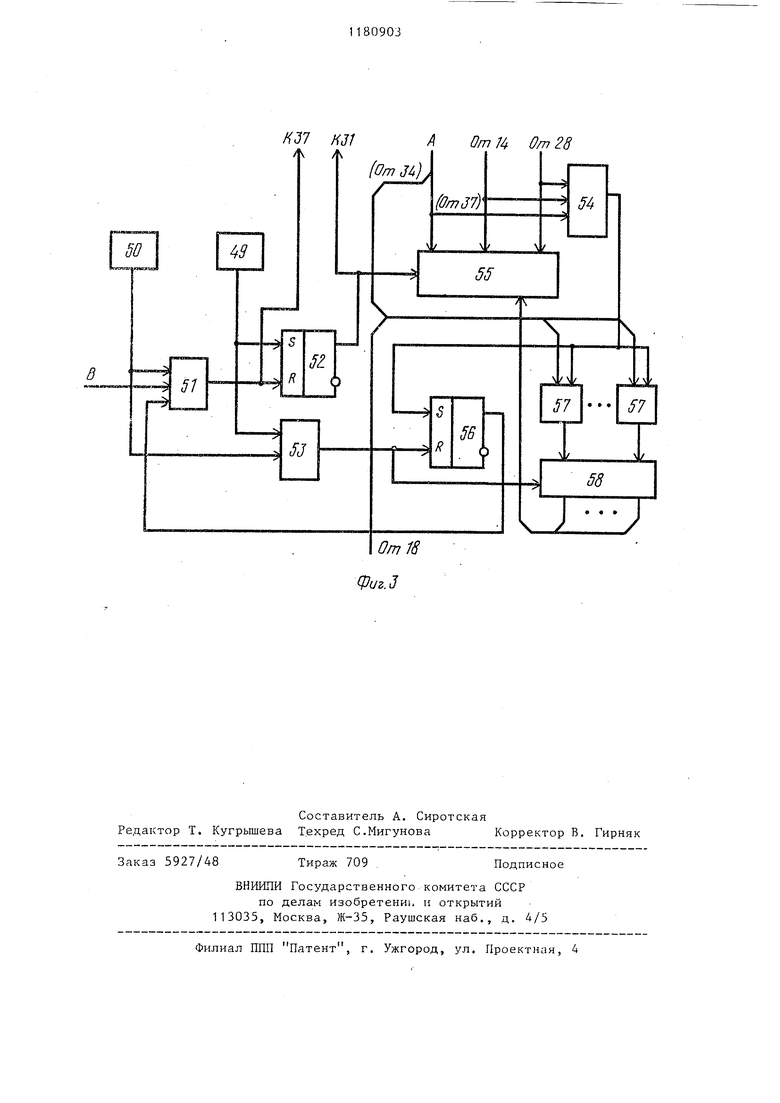

На фиг, 1 представлена блок-схема устройства; на фиг. 2 - схема блока контроля считываемой информации; на фиг. 3 - схема блока управления.

Устройство содержит информационные входы 1, вход 2 синхронизации, группу формирователей 3 импульсов, формирователь 4 синхроимпульсов, генератор 5 тактовых импульсов, дешифратор 6, элемент ИЛИ 7, триггер 8, элемент ИЛИ 9, элемент И 10, счетчик 11, элемент ИЛИ 12, элемент НЕ 13, элемент ИЛИ 14, счетчик 15, элемент ИЛИ 16, дешифратор 17, группу элементов И 18, счетчик 19, дешифратор 20, элемент И 21, элемент И 22, элемент И 23, счетчик 24, счетчик 25, счетчик 26, схему 27 сравнения, элемент И 28, элемент ИЛИ 29, блок 30 контроля считьгоаемой информации, элемент И 31, блок 32 управления, элемент И 33.

Блок 30 контроля считьшаемой инфомации содержит регистр 34, элемент НЕ 35, триггер 36, элемент ИЛИ 37, элемент И 38, счетчик 39, дешифратор 40, элементы ИЛИ 41-44, схему .45 сравнения, коммутатор 46, элемент И 47, регистр 48.

Блок 32 управления содержит переключатель 49 пуска, переключатель 50 сброса, элемент ИЛИ 51, триггер 52, элемент ИЛИ 53, элемент ИЛИ 54, блок 55 индикации, триггер 56, группу элементов И 57, регистр 58.

Блок 30 контроля считываемой информации работает следующим образом. До момента поступления информации и синхросигналов переключателем 50 сброса блока 32 управления в нулевое состояние приводится триггер 36 и счетчик 39 импульсов. Начальной фазой процесса считывания является пауза. При этом сигнал логического нуля, снимаемый с выхода формирователя 4 синхроимпульсов, инвертируется элементом НЕ 35, и при наличии сигнала на выходе пуска блока 32 управления через элемент И 31 устанавливает триггер 36 в единичное

состояние. С выхода триггера 36 снимается сигнал, подготавливающий элемент И 38 к открытию. При этом импульсы частоты f с выхода генератора 5 импульсов через элемент И 38 не проходят, так как на другом его входе в момент паузы присутствует сигнал уровня логического нуля, поступающий с выхода формирователя 4

5 синхроимпульсов. При поступлении с выхода формирователя 4 синхроимпульсов уровня логической единицы открывается элемент И 38 для прохождения импульсов генератора 5. Длительность импульсов генератора 5 тактовых импульсов рассчитывается таким образом, чтобы их вырабатывалось не менее шести в интервал действия синхроимпульса. Импульсы тактового

, генератора 5 через элемент И 38 поступают на счетный вход счетчика 39. Выходной код счетчика 39 дешифрируется с помощью дешифратора 40 таким образом, что после первого (четвертого) импульса генератора 5 тактовых импульсов возбуждается первый (четвертый) выход дешифратора 40, после второго (пятого) импульса генератор-г

5 импульсов - второй (пятый) выход дешифратора 40, после третьего (шестого) импульса генератора 5 импульсов - третий (шестой) выход дешифратора 40.

При возбуждении первого выхода дешифратора 40 сигнал уровня логической единицы через элемент ИЛИ 41 и через вход записи первого регистра 34 разрешает прием з регистр 34 через его входы байта информации. Затем при возбуждении второго выхода дешифратора 40 сигнал уровня логической единицы через элемент ИЛИ 42 и через вход записи второго регистра 48 разрешает прием в регистр 48 через его информационные входы этого байта информации. Далее при возбуждении третьего выхода дешифратора 40 сигнал уровня логической единицы через элемент ИЛИ 43 и через вход разрешения схемы 45 сравнения разрешает сравнение байтов, зафиксированных в регистрах 34 и 48. Если байты информации равны, то на выходе Равно схемы 45 сравнения вырабатывается импульс, который через управляющий вход коммутатора 46 разрешает передачу на информационные входы устройства байта информации с выходов регистра 34. Одновременно с сигналом Равно через вход элемента ИЛИ 44 и второй вход элемента ИЛИ 37 устанавливается в О триггер 36 и счетчик 39. Если при считывании информации на регистрах 34 и .48 окажутся различные коды, тогда вмзсто сигнала Равно на выходе схемы 45 сравнения будет выработан сигнал Не равно, который поступит на-первый вход второго элемента И 47, закрытый сигналом, присутствующим на его втором входе. При этом с выхода генератора 5 импульсов будут продолжать поступать импульсы через элемент ИЛИ 38 на счетчик 39, а на выходе дешифратора 40 возбудятся последовательно его четвертый, пятый и шестой выходы. В результате этого повторно осуществленыдействия записи байтов в регистры 34 и 48 и их сравнение на схеме 45 сравнения. При выработке сигнала Равно аналогично вышеописанному случаю произойдет передача правильного принятого байта на выход устройства через коммутатор 46 и установка устройства в исходное состояние для контроля очередного

байта информации. Ecjui вторично вырабатывается сигнал Не равно, то в результате его совпадения во времени с возбуждением шестого выхода дешифратора 40 на вход элемента И 47 проходит сигнал на блок 32 управлени совместно с информацией, которая неправильно считана (для регистрации отображения с целью локализации дефекта), т.е. работа блока соответствует работе известного устройства

Работа блока 32 управления начинается с нажатия переключателя 50 сброса. По команде Сброс приводитс в исходное состояние тригтер 52, регистр 58 и выдается сигнал элементу ИЛИ 37. При нажатии переключателя 49 пуска выдается команда для пуска устройства и для индикации на блок 55 индикации.

При появлении сигналов на входе А с выхода блока 30 в случае ошибки в считанной информации от элемента ИЛИ 14 в случае отсутствия синхросигнала, от элемента И 28 в случае изменения скорости ввода информации выдается сигнал на блок 55 индикации и на элемент ШШ 54. С выхода элемента ИЛИ 54 сигнал поступает на группы элементов И 57, разрешая запись инфомации в регистр 58 и на вход З-триг- гера 56,переходом которого в единичное состояние через элемент ИЛИ 51 выдается сигнал к элементу ИЛИ 37, и приводится в и.сходное состояние триггер 52, с выхода пуска сигнал снимается. При программировании программного сброса блока 32 управления подается сигнал на третий вход элемента ШШ 51 (В).

Устройство работает следуюш;им образом.

При нажатии переключателя 50 сброса в блоке 32 управления появляется сигнал на выходе элемента ИЛИ 51, которым приводятся в исходное состояние счетчики 11, 15, 19, 24, 25 и 26, триггер 8 и блок 30 контроля считываемой информации.

Пуск устройства осуществляется пр нажатии переключателя 49 пуска в блоке 32 управления. В этом случае с выхода пуска блока 32 управления сиг.-ал поступает на вход элемента ИЛИ 7 и на вход элемента И 31 для запуска блока 30 контроля счит1.шаемой информации.

Устройство осуществляется по информации, поступающей с выхода формирователя 3 группы, контроль считанной информации блоком 30, одновременно осуществляется контроль отсутствия дефсктов, связанных с отсутствием синхроимпульсов и изменения скорости ввода информации.

Контроль отсутствия дефектов, связанных с отсутствием синхроимпульсов, происходит следующим образом.

С выхода формирователя 4 синхроимпульсов сигналы одновременно поступают на вход элемента И 38j блока 30, на вход сброса счетчика 11 импульсов и на счетные входы счетчиков 15 и 19.

Выходным сигналом с элемента ИЛИ 7 устанавливается в единичное состояние триггер 8. Сигнал, снимаемый с выхода триггера 8, поступает на вход элемента И 10 а при наличии единичного сигнала на выходе элемента НЕ 13 разрешает прохождени

f с второго

импульсов частоты f, У

выхода генератора 5.импульсов. Частота следования импульсов f, выбирается, исходя из периода следования синхроимпульсов. Емкость счетчика 11 определяется исходя из того, что, если через промежуток времени С не поступит синхроимпульс с выхода формирователя 4 синхроимпульсов, то произойдет переполнение счетчика 1 1 импульсов. В этом случае снимается сигнал с третьего входа элемента И Ю, тем самым прекращается подача импульсов на счетчик 11. Сигналом переполнения, снимаемым с выхода счетчика И, устанавливается в нулевое состояние триггер 8. Триггер 8 снимает единичный сигнал с второго входа элемента И 10. С выхода счетчика 11 сигнал переполнения поступает на вторые входы элементов И 18 группь и на информационный вход блока 55 индикации. Счетчик 15 импульсов подсчитывает количество синхроимпульсов и в этом случае с помощью дешифратора 17 выдает информацию через элементы И 18 о месте дефекта на входы соответствующих элементов И 57 блока 32 управления. Если необходимо продолжить ввод информации, то в блоке 32 управления поочередно нажимаются переключатели 50 сброса и 49 пуска. В случае отсутствия дефекта счетчик 1 1 с приходом синхроимпульса сбрасывается в нулевое (исходное) состояние.

Одновременно устройство контролирует скорость ввода информации, которая должна быть постоянной. Контроль осуществляется следующим образом. Синхроимпульсы с выхода формирователя 4 поступают на счетный вход счетчика 19. С приходом первого импульса на Счетчик 19 возбуждается первый выход дешифратора 20. Единичный сигнал с первого выхода дешифратора 20 поступает на вход элемента И21, разрешая прохождение импульсов частоты fj с генератора 5 на счетчик 24. В счетчик 24 записывается количество импульсов, пропорциональное скорости поступления информации, так как частота считывания 2 постоянна. При записи второго импульса в счетчик 19 возбуждается второй выход у дешифратора 20, тем самым обеспечивается запись импульсов в счетчик 25. При возбуждении третьего выхода в дешифраторе 20 обеспечивается запись количества импульсов, пропорционального скорости поступления информации в счетчик 26. При записи четвертого импульса в счетчик 19 возбуждается четвертый выход с дешифратора 20. Сигнал с четвертого выхода дешифратора поступает на вход разрешения схемы 27 сравнения, разрешая поразрядное сравнение информации, записанное в счетчиках 24-26, и одновременно сигнал с четвертого выхода дешифратора поступает на первый вход элементов И 23 и 33. В случае, если информация во всех трех счетчиках 24-26 совпадает, то с первого выхода схемы 27 сравнения через элементы И 33 и ИЛИ 29 вьщается сигнал на приведение счетчиков 19, 24, 25 и 26 в нулевое состояние, и далее контроль скорости ввода в информацию производится аналогично.

Если информация, записанная в счечиках 24-26, не совпадает, то с выхода Не равно схемы 27 сравнения при возбуждении четвертого выхода в дешифраторе 20 через элемент И 28 выдается сигнал на элемент ИЛИ 54 и информационный вход блока индикации, на элементы И 18 группы, с выхода которых на блок 32 управления вьщается информация о месте дефекта, на вход R-триггера. Триггер 8 устанавливается в нулевое состояние и снимает сигнал с второго входа элемента И 10.

Останов устройства и приведение его в исходное состояние осуществляется по коду, поступающему на дещифратор 6, которьй возбуждает второй выход дешифратора .6. Сигналом с второго выхода дешифратора 6 триггер 8 устанавливается в нулевое состояние, тем самым снимается единичный сигнал с входа элемента И 10 и устанавливаются в исходное состоясчетчики 15, 19, 24, 25 и

ние 26.

Для проведения самопроверки элементов, осуществляющих контроль отсутствия дефектов, связанных с отсутствием синхроимпульсов и элементов, осуществляющих контроль изменения скорости ввода информации,

на вход дешифратора 6 подается код, возбуждающий его первый выход. Этим сигналом, поступающим на вход S-триггера 8, он устанавливается в единичное состояние. Далее работа

устройства аналогична описанному.

выход

-Ч

-п1

1

Ц)иг.2 /rJ7 /rj; /h /I От /4 77 5 } 0m 18 Фиг.З )

| Устройство для счытывания информации | 1973 |

|

SU471594A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля считываемой информации | 1982 |

|

SU1056200A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-23—Публикация

1984-04-11—Подача