ответственно с второй группой входов имитатора неисправностей, вторая груп па выходов блока управления имитацией неисправностей соединена с второй группой входов блока индикации, третья группа входов которого соединена - с третьей группой выходов блока управ ления имитацией неисправностей, четвертая группа выходов которого соеди нена с четвертой группой входов блока индикации, пятая группа входов которого соединена с пятой группой выходов блока управления имитацией неисправностей, оТ л и чающееся тем, что, с целью расширения функциональных возможностей путем определения минимизированного проверяющего теста, в устройство введены блок формирования импульсов считывания, блок памяти, две группы элементов И, блок определения теста, дешифратор, причем группа входов дешифратора соединена с группой выходов блока формирователей сигналов, выходы дешифратора соединены соответственно с первыми входами элементов И первой груп.пы, вторые входы которых соединены с вторым выходом блока управления имитацией неисправностей, первый вход которого соединен f. выходом второго блока сравнения, с третьими входами элементов И первой группы, с управляющим входом блока памяти, первая группа информационных Входов которого соединена с группой выходов второго счетчика, выход которого соединен с первым входом блоЁга формирования импульсов считывания, второй вход которого соединен с выходом блока памяти, с вторым входом блока управления имитацией неисправностей, третья группа входов которого соединена соответственно с первой группой выходов блока определения теста, вторая группа выходов которого соединена с второй группой информационных входов бпо ка памяти, группа выходов которого со единена с первой группой входов блока определения теста, вторая группа входов которого соединена с первой груп.пой выходов блока формирования импуль сов считывания, с группой управляющих входов блока памяти, вторая группа информационных входов которого соединена соответственно с выходами элементов И первой группы, соответственно с информационными входами регистра, управляющие входы которого соединены с третьим выходом блока упр)авления имитацией неисправностей, четвер159 тая группа входов которого соед 1нена соответственно с выходами регистра, с первыми входами элементов И второй группы, вторые входы которых соединены соответственно с группой выхо.дов эталонного узла, выходы элементов И второй группы соединены соответственно с пятой группой входов блока управления имитацией неисправностей, выход блока определения теста .соединен с третьим входом блока формирования импульсов считывания, вторая группа выходов которого соединена с третьей группой входов блока определения теста. 2. Устройство по п. 1, о т л и чающееся тем, что блок управления имитацией неисправностей содержит узел запуска, счетчик, переключатель, элемент ИЛИ, четыре регистра, триггер, три элемента И, группу элементов И, элемент НЕ, причем первый вход первой группы входов блока соединен с первым входом узла запуска, второй вход которого соединен с выходом первого элемента И и является первым выходом пятой группы выходОв блоки, второй вход первой rpjtnпы входов которого соединен со счетным входом счетчика, установочный вход которого соединен с выходом переключателя, с третьим входом узла запуска с нулевыми входами первого, второго, третьего и четвертого регист:ров, с нулевым входом триггера и является третьим выходом блока, первый вход которого соединен с первыми входами элементов И группы, с первым входом первого элемента И, второй вход которого соединен с выходом элемента НЕ, вход которого соединен с выходом элемента ИЛИ и является первым выходом блока, второй выход которого соединен с выходом узла запуска, с вторыми входами элементов И группы, третьи входы которых являются соответственно второй группой .входов блока, второй вход которого соединен с первым входом второго элемента И, второй вход которого соединен с выходом переполнения счетчика, с четвертым входОм узла запуска, с первым входом третьего элементаИ, группа входов которого соединена соответственно с инверсивными выходами первого регистра, единичные входы которого соединены соответственно с выходами элементов И группы, третья группа входов блока соединена соответственно с единичными

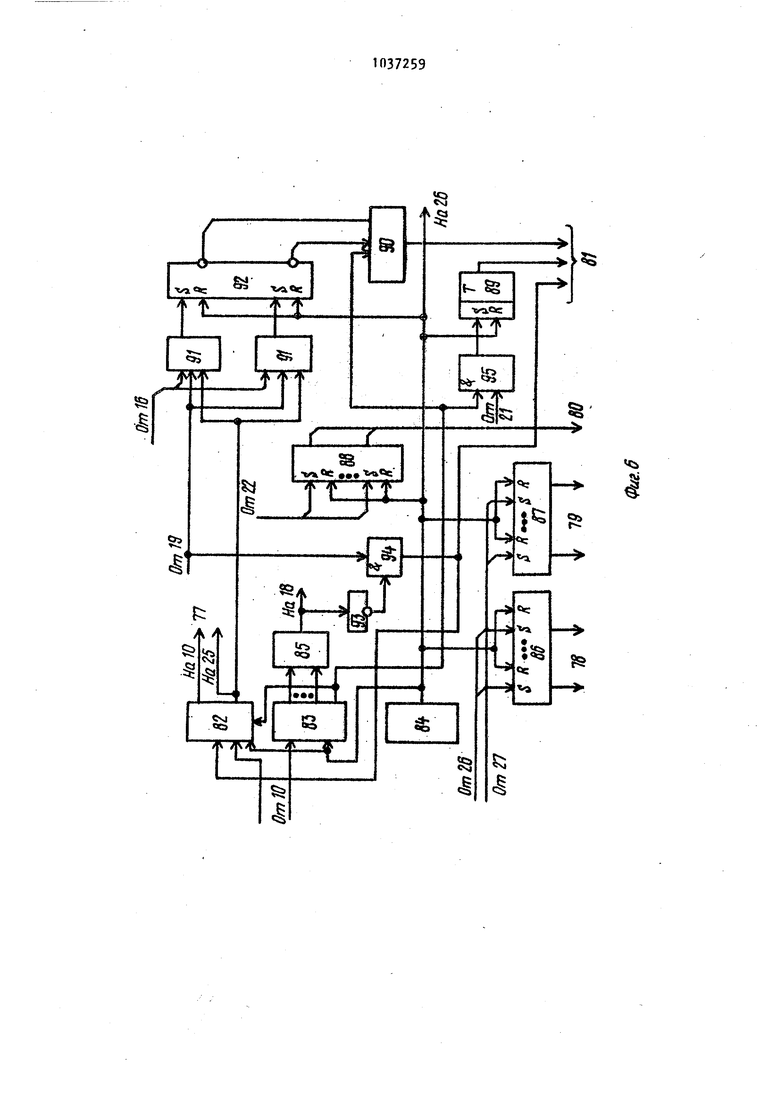

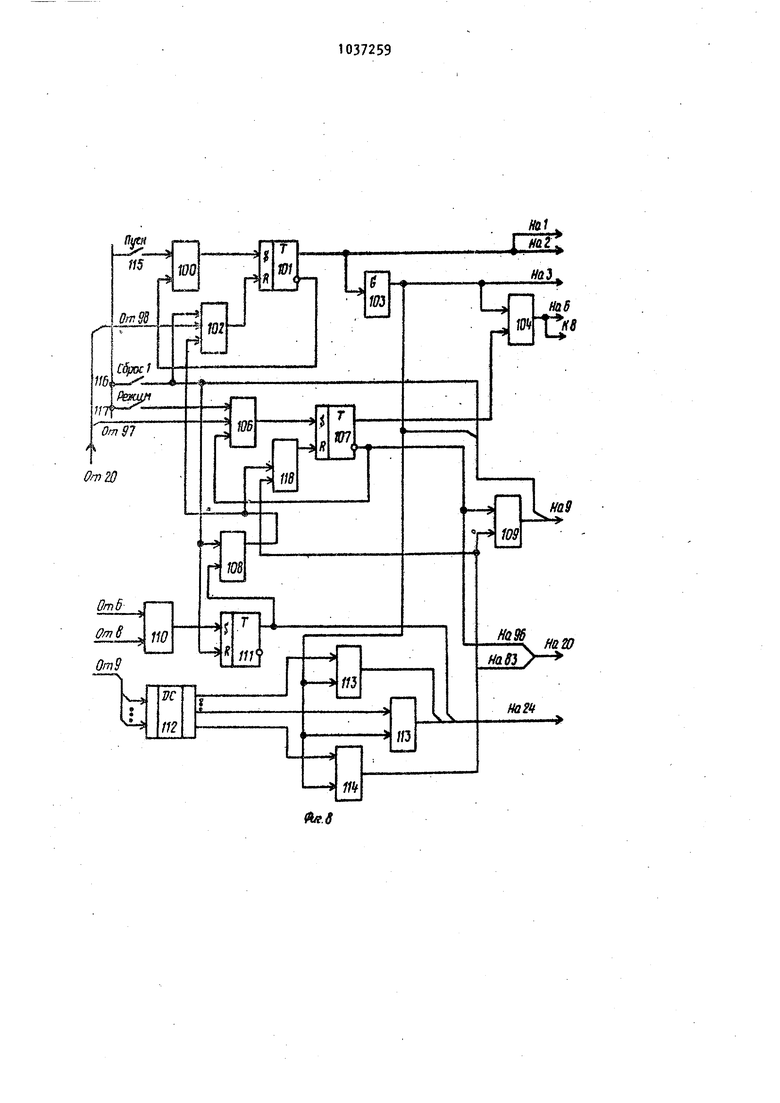

входами второго регистра, выходы которого являются четвертой группой выходов блока, четвертая и пятая группы входов которого соединены соответственно с единичными входами третьего, и четвертого регистров, выходы которых являются соответственно второй и третьей группами выходов блока, второй выход пятой группы выходов которого соединен с .выходом триггера, единичный вход которого соединен с выходом второго элемента И,третий выход пятой группы выходов блока соединен с выходом третьего элемента И, группа выходов узла.Запуска является .первой группой выходов блока.

3. Устройство по ПП.1 и., о т л ичающее ся тем, что узел запуска содержит элемент И, элемент ИЛИ триггер, переключатель, причем выход переключателя соединен с первым входом элемента И, второй вход которого является первым входом узла, второй вход которого соединен с первым входом элемента ИЛИ, второй вход которого является третьим входом узла, четвертый вход.которого соединен с третьим входом элемента ИЛИ, выход которого соединен с нулевым входом триггера и является первым выходом группы выходов узла, второй выход первой группы выходов которого соединен с is HBepcным выходом триггера, с третьим входом элемента И, выход которого соединен с единичным входом триггера, прямой выход которого является выходом узла.

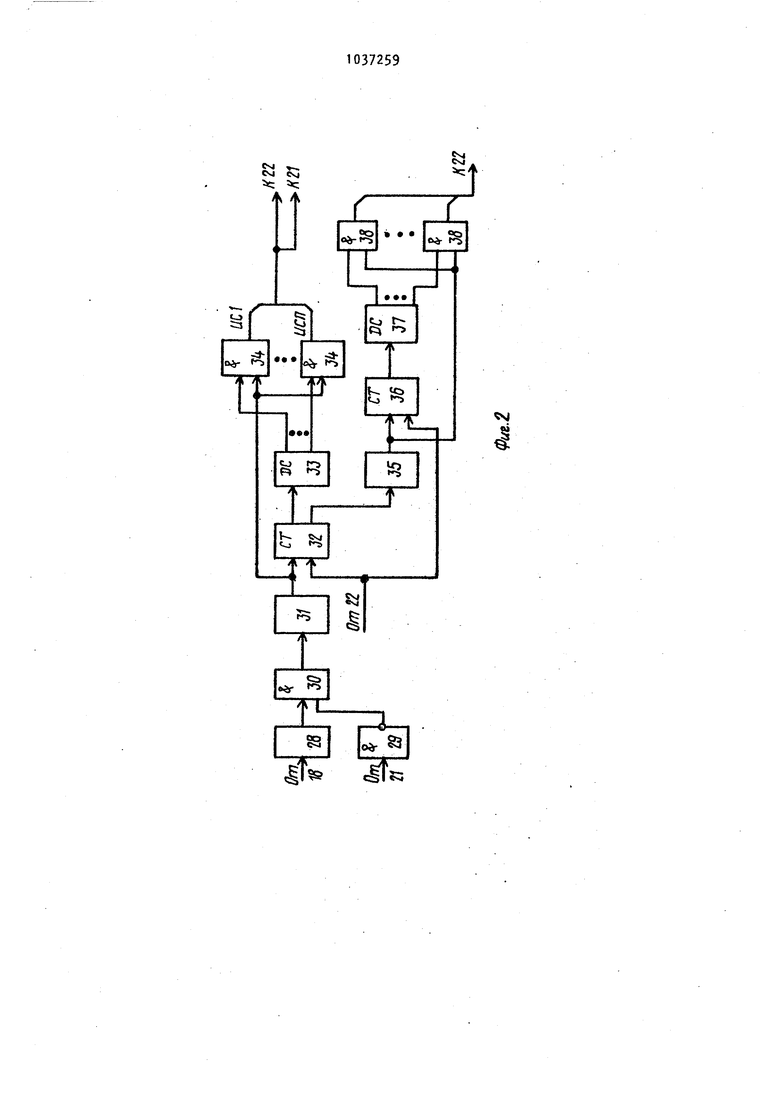

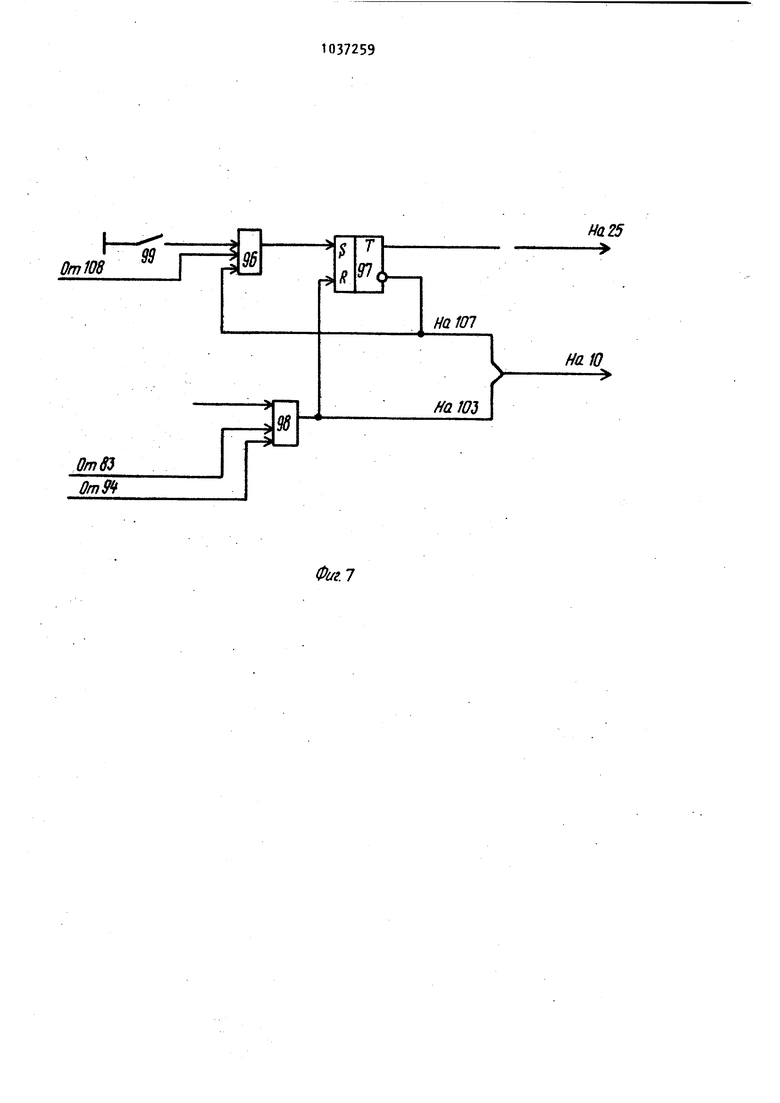

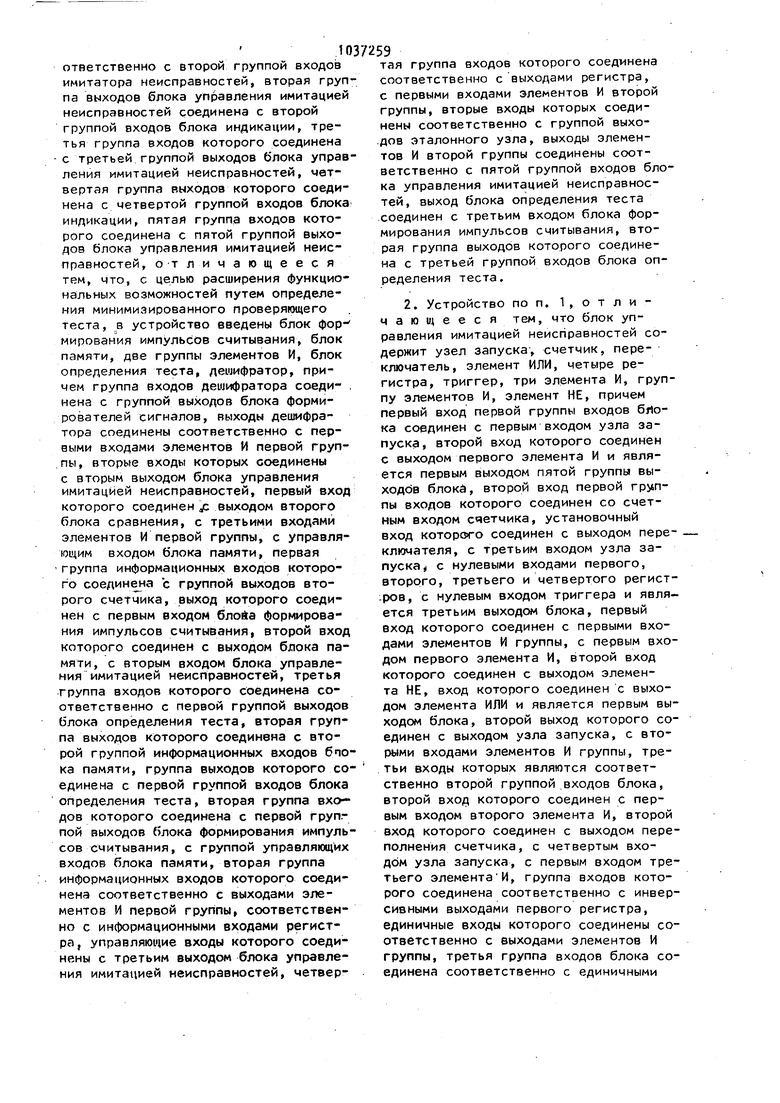

Устройство по п. 1, о т л и чающееся тем, что блок формирования импульсов считывания содержит элемент.задержки, элемент НЕ, элемент И, два генератора тактовых импульсов, два счетчика, два дешифр-лтора, две группы элементов И, причем первый вход блока соединен с входом элемента задержки, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом элемента НЕ, вход которого является вторым входом блока, выход элемента И соединен с управляющим входом первого генератора тактовых импульсов выход которого соединен со счетным входом первого счетчика, с первыми входами элементов И первой группы, вторые входы которых соединены соответственно с выходами первого дешифратора, входы которого соединены q выходами разрядов счетчика, выход переполнения которого соединен с управляюи им входом второго генератора тактовых импульсов, выход которого соединен со счетным входом второго счетчика, с первыми входами элементов И второй группы, вторые входы которых соединены соответственно с выходами второго дешифратора, входы которого соединены с выходами разрядов второго счетчика, вход сброса которого соединен с входом сброса первого счетчика и является третьим входом блока, выходы элементов И первой и второй групп является соответ-. ственно выходами первой и второй групп блока.

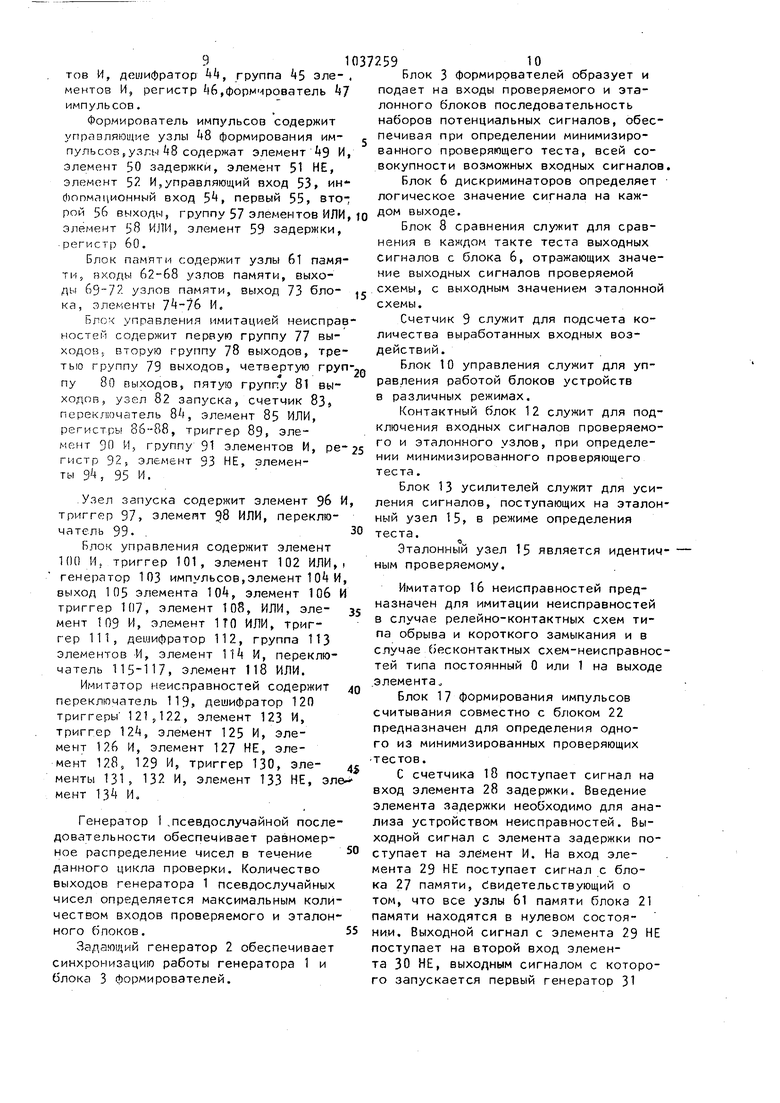

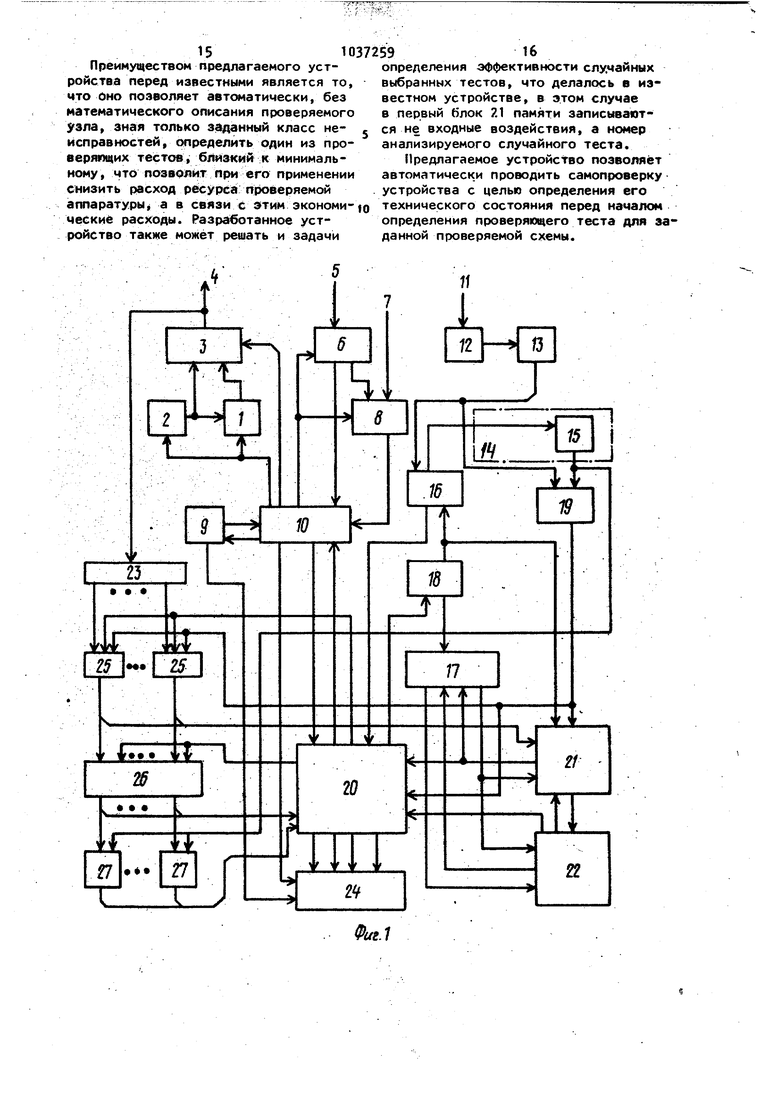

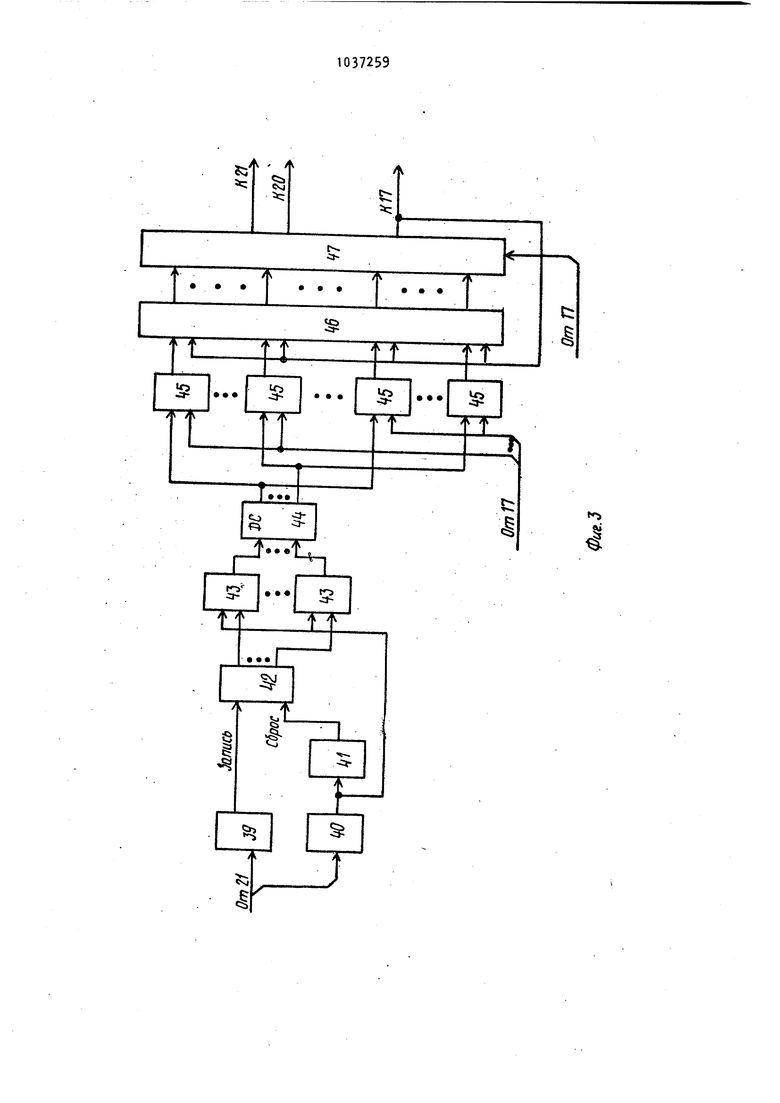

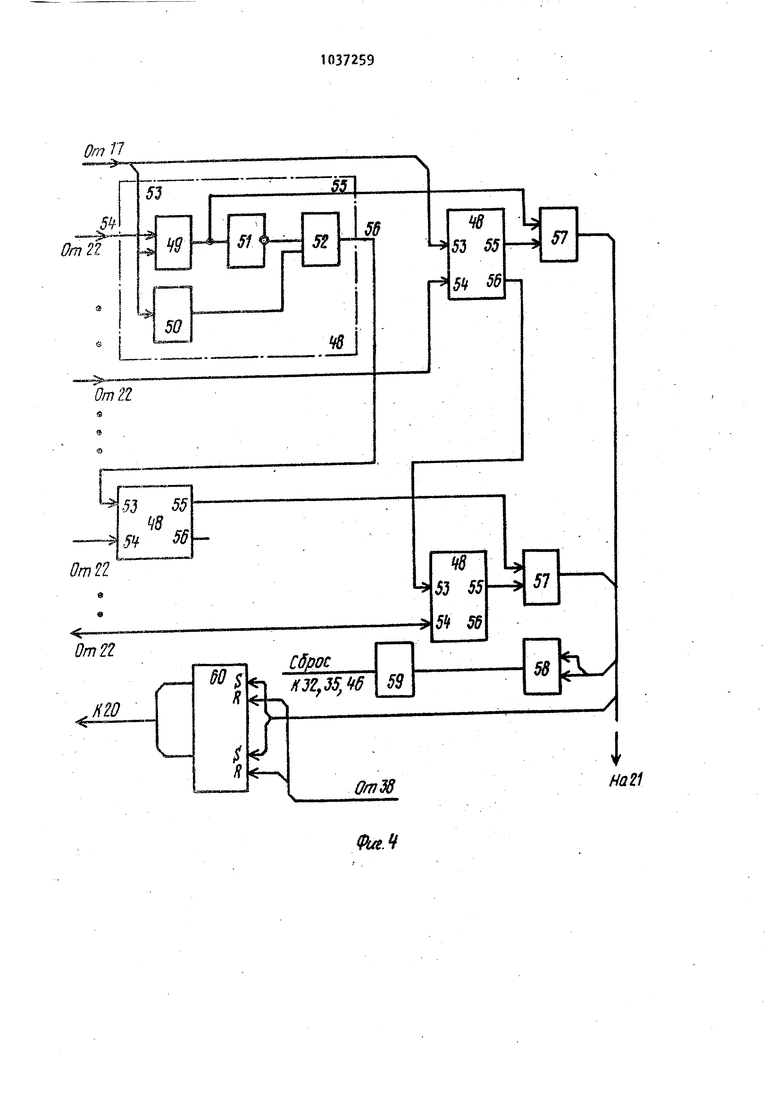

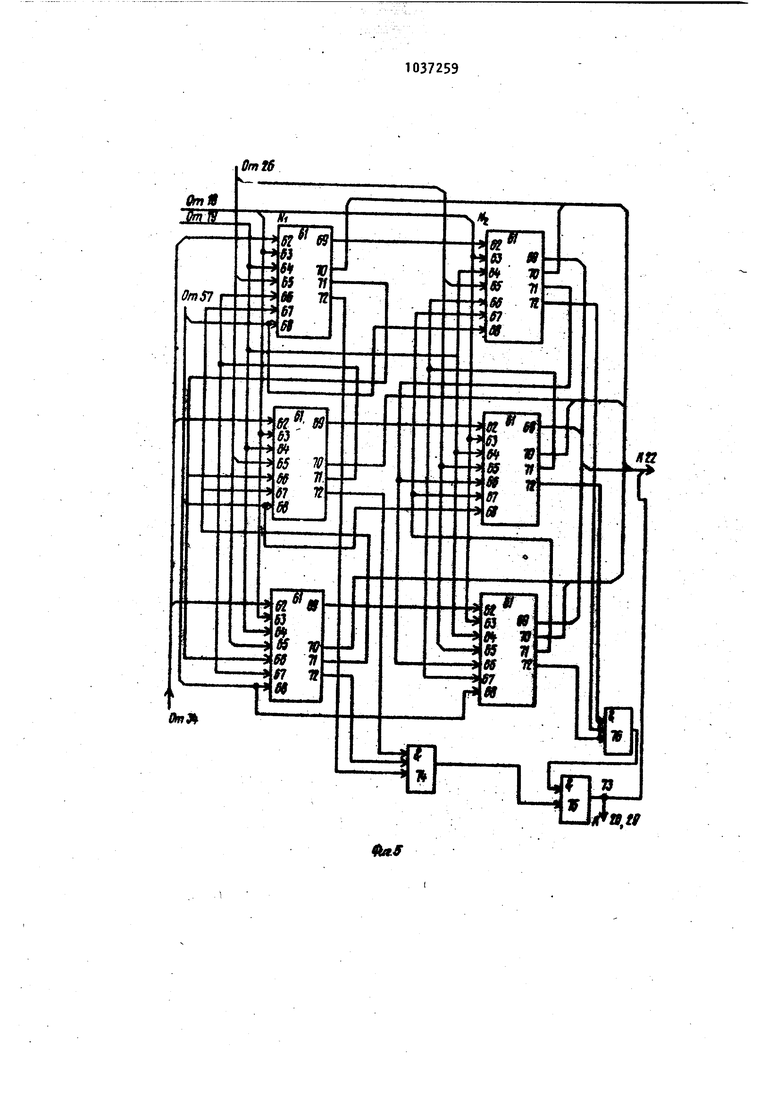

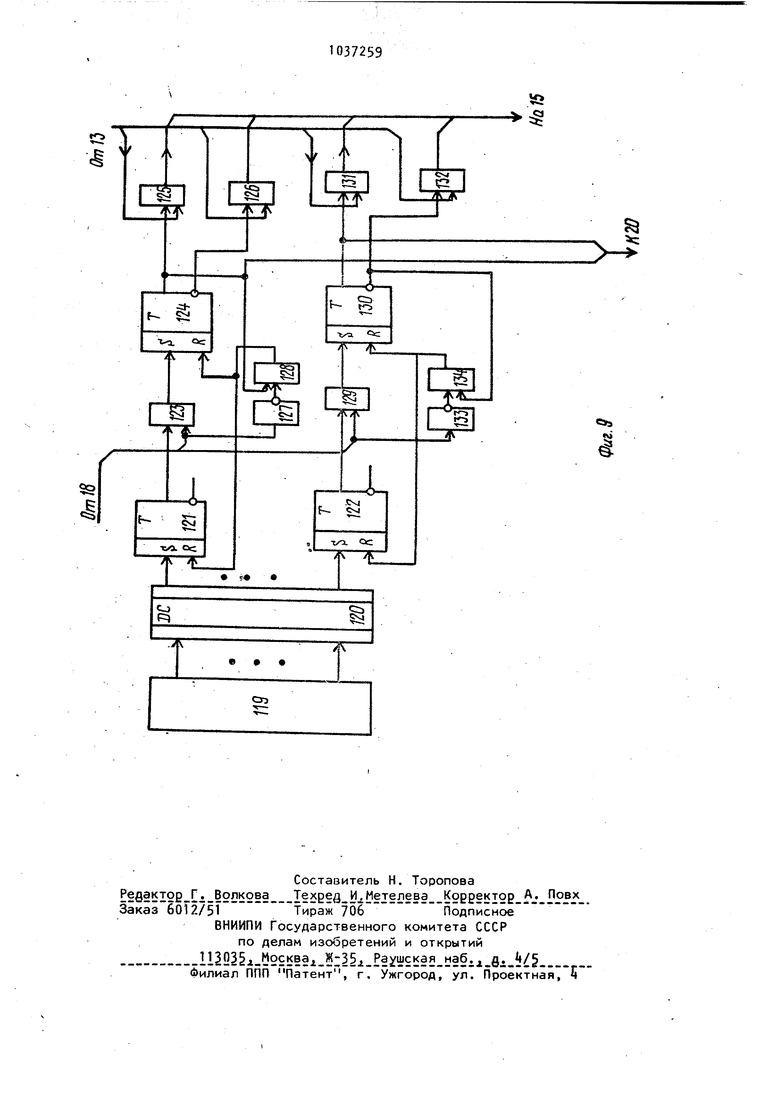

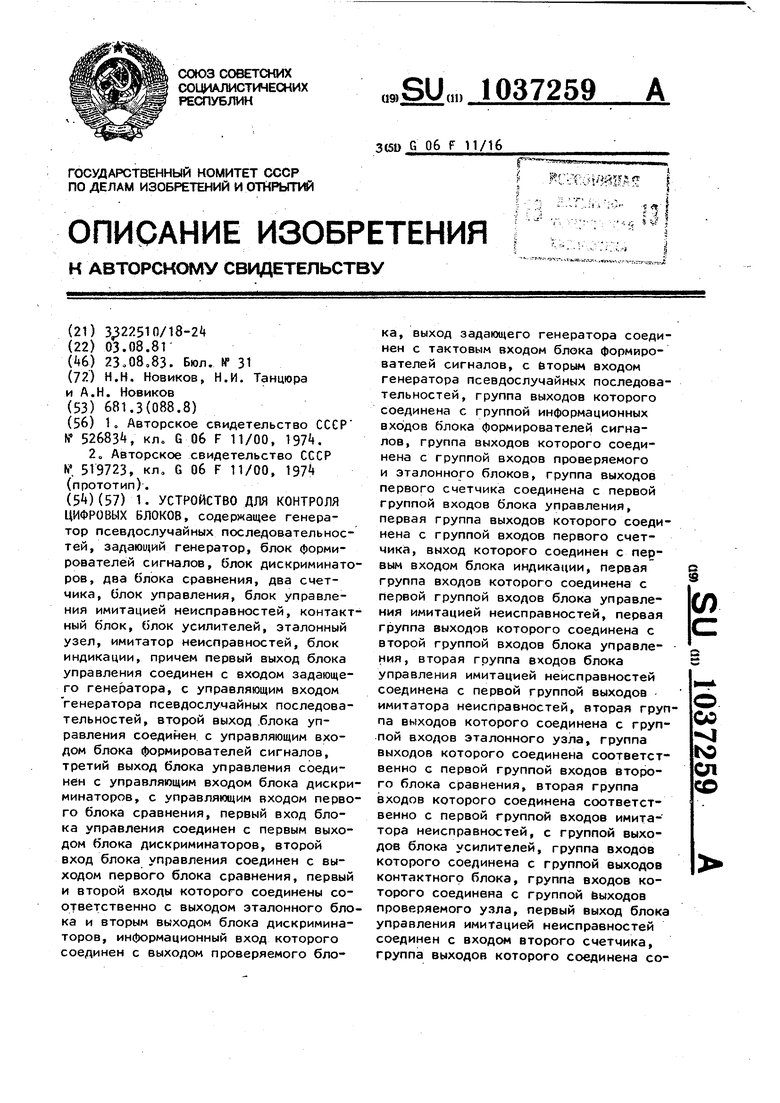

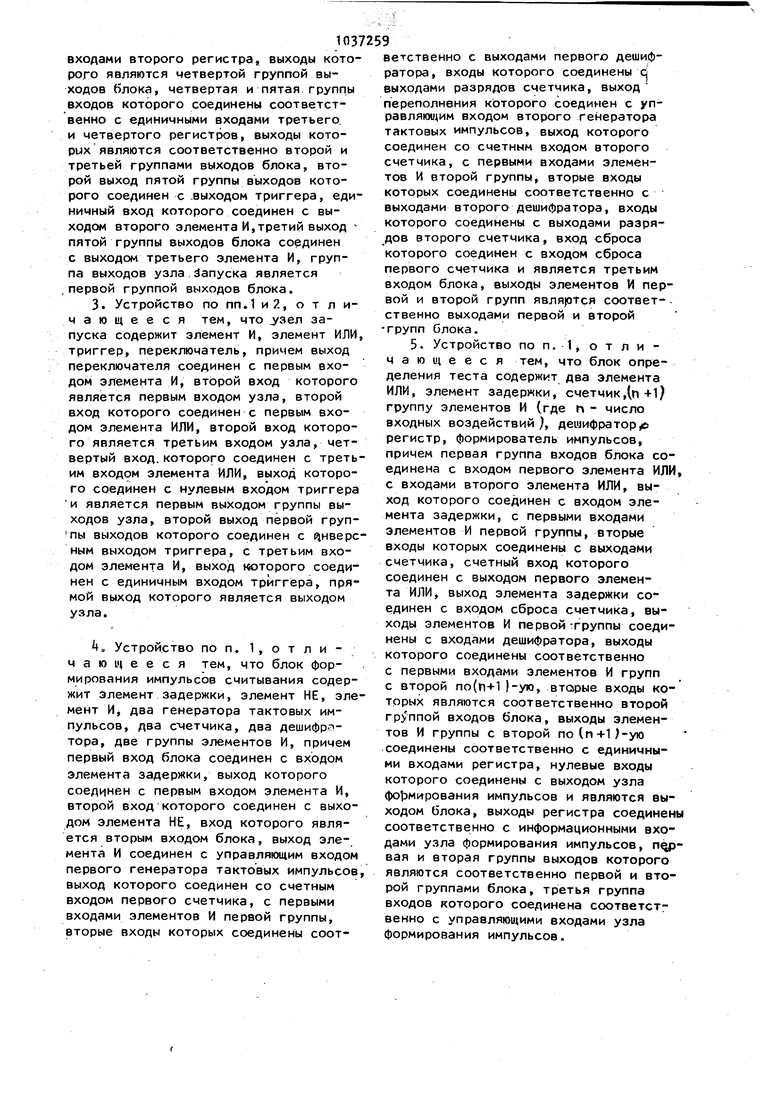

5. Устройство поп,1,отличающееся тем, что блок определения теста содержит два элемента ИЛИ, элемент задержки, счетчик,(п +1) группу элементов И (где п - число входных воздействий ), дешифратору регистр, формирователь импульсов, причем первая группа входов блока соединена с входом первого элемента ИЛИ с входами второго элемента ИЛИ, выход которого соединен с входом элемента задержки, с первыми входами элементов И первой группы, вторые входы которых соединены с выходами счетчика, счетный вход которого соединен с выходом первого элемента ИЛИ, выход элемента задержки соединен с входом сброса счетчика, выходы элементов И первой :группы соединены с входами дешифратора, выходы которого соединены соответственно с первыми входами элементов И групп с второй по(п+1)-ую, вторые входы которых являются соответственно второй группой входов блока, выходы элементов И группы с второй по (n+l )-ую соединены соответственно с единичными входами регистра, нулевые входы которого соединены с выходом узла фо эмирования импульсов и являются выходом блока, выходы регистра соединен соответственно с информационными входами узла формирования импульсов, и вторая группы выходов которого являются соответственно первой и второй группами блока, третья группа входов которого соединена соответственно с управляющими входами узла формирования импульсов. Изобретение относится к автоматике и вычислительной технике и может быть использовано для определения пр веряюи(их тесТов сложных комбинационных схем. Известно устройство для контроля и поиска неисправностей комбинационных схем, содержащее источник питания, (5лок фиксации неисправностей, коммутатор переменных логических фун ций, коммутатор переменных инверсных логических функций, коммутирующие эл менты, которые через электронные клю чи, управляюише входы которых через элементы ИЛИ соединены с входами шагового коммутатора и с выходными шинами другой группы данного коммутато ра, соединяющиеся с входными в другом включенном положении тех же коммутир щих элементов с управляющими входами диагностируемой схемы. Нагрузкой диагностируемой схемы является блок фиксации неисправностей, входы которого через коммутирующие элементы. коммутатора конъюнкций подключены к . одноименным входам шагового коммутатора, в каждом положении которого источник питания подключен к одной из входных шин одного матричного коммутатора совместно со всеми входными шинами и входами всех элементов ИЛИ другого коммутатора р J. Недостатком указанного устройства является невозможность его применения для контроля сложных комбинационных схем. Наиболее близким по технической сущности к предложенному является устройство для контроля цифровых модулей и проверки качества тестов, CO держащее генератор псевдослучайных последовательностей, блок дискримина торов, первый блок сравнения, контак ный блок, блок усилителей, сменную плату с эталонной интегральной схемой, два имитатора неисправностей, счетчик тактов, основной блок управления, счетчик неисправностей, второй и третий блоки сравнения, регистр длины теста, регистр и дополнительный блок управления, причем первый выход основного блока управления соединен со входом генератора синхронизации и с одноименными входами генератора псевдослучайных последовательностей, блока формирователей ,блока дискриминаторов и первого блока сравнения.первый вход - с одноименным выходом бло ка дискриминаторов, а второй вход с выходом первого блока сравнения, первый и второй входы которого соединены с шиной выходных сигналов эталонного модуля и вторым выходом блока дискриминаторов соответственно, второй выход блока дискриминаторов соединен с шиной выходных сигналов контролируемого модуля, первый выход генератора синхронизации соединен с вторым входом блока формирователей, второй выход - с одноименным входом генератора псевдослучайных последовательностей, выход которого соединен с третьим входом блока формирователей, выход которого соединен с шиной входных сигналов контролируемого и эталонного модулей. Первый выход дополнительного блока управления соединен с одноименным входом регистра длины теста и третьим входом основного блока управления, второй и третий выходы - со входами счетчика неисправностей и регистра, результата соответственно, первый вход - с выходом второго блока сравнения и третьим выходом основного блока управления, второй вход - с первыми входами первого и второго имитаторов неисправностей и выходом счетчика неисправностей, третий вход - с выходом регистра результата, а четвертый вход - с выходом третьего блока сравнения, первый вход которого соединен с выходом блока усилителей и вторым входом первого имитатора неисправностей, а второй - вход - с выходом второго имитатора неисправностей, второй вход которого соединен с выходом эталонной схемы сменной платы, вход которой соединен с выходом эталонной схемы сменной платы, вход которой соединен с выходом первого имитатора неисправностей, вход блока усилителей соединен с выходом контактного блока, вход которого соединен с шиной входных и выходных сигналов интегральных схем модуля, выход регистра длины теста соединен с первым входом второго блока сравнения, второй вход которого соединен с одноименным входом регистра длины теста и первым выходом счетчика тактов, второй вход и первый вход которого соединен с четвертым входом и вторым выходом основного блока управления соответственно, дополнительные входы - выходы счетчика тактов, регистра длины теста, регистра результата, дополнительного основного блоков управления соедийены с шиной сигналов индикации и пу та управления С 21Недостатком известного устройства является невозможность его применения для логического определения одного из минимальных проверяющих тестов или близкого к нему для проверяемого блока, так как в устройстве анализируются только случайно выбранные тесты, а сами тесты не определяются., . Целью изобретения является расширение функциональных возможностей пу тем определения минимизированного проверяющего теста. Поставленная цель достигается тем что в устройство для контроля цифровых блоков содержащее генератор псевдослучайных последовательностей, задающий генератор, блок формировате лей сигналов, блок дискриминаторов, два блока сравнения, два счетчика, блок управления, блок управления ими тацией неисправностей, контактный блок, блок усилителе, эталонный узел, имитатор неисправностей, блок индикации, причем первый выход блока управления соединен с входом задающе го генератора, с управляющим входом генератора псевдослучайных последова тельностей, второй выход блока управ ления соединен с управляющим входом блока формирователей сигналов,третий выход блока управления соединен управляющим входом блока дискриминаторов, с управляющим входом первого блока сравнения, первый вход блока управления соединен с первым выходом блока дискриминаторов, второй вход блока управления соединен с выходом первого блока сравнения, первый и второй входы которого соеду1нены соответственно с выходом эталонного блока и вторым- выходом блока дискриминаторов ииформационный вход которо го соединен с выходом проверяемого блока, выхрА задающего генератора со единен с тактовым входом блока форми рователей сигналов, с вторым входом генераторе псевдослучайных последова тельностей, группа выходов которого соединена с группой информационных входов блока формирователей сигналов группа выходов которого соединена с группой входов проверяемого и эталон ного блоков, группа выходов первого счетчика соединена с первой группой входов блока управления, первая груп па выходов которого соединена с груп пой входов первого счетчика , выход которого соединен с первым входом блока индикации, первая группа входов которого соединена с второй группой выходов блока управления, третья группа выходов которого соединена с первой группой входов блока управления имитацией неисправностей, первая группа выходов которого соединена с второй группой входом блока управления, вторая группа входов блока управления имитацией неисправностей соединена с первой группой выходов имитатора неисправностей, вторая группа выходов которого соединена с группой входов эталонного узла, группа выходов которого со- . единена соответственно с первой группой входов второго блока сравнения, вторая группа входов которого соединена соответственно с первой группой входов имитатора .неисправностей, с группой выходов блока усилителей, группа входов которого соединена с группой выходов контактного блока, группа входов которого соединена с группой выходов проверяемого узла, первый выход блока управления имитацией неисправностей соединен с входом второго счетчика, группа выходов которого соединена соответственно с второй группой входов. kmHTaTOpa неисправностей, вторая группа выходов блока управления имитацией неисправностей соединена с второй группой входов блока индикации, третья группа входов которого соединена с третьей группой выходов блока управления имитацией неисправностей, четвертая группа выходов которого соединена с четвертой группой входов бло- ка индикации, пятая группа входов которого соединена с пятой группой выходов блока управления имитацией неисправностей, введены блок формирования импульсов считывания, блок памяти, две группы элементов И, блок определения теста, дешифратор, причем группа входов дешифратора соединена с группой выходов блока формирователей сигналов, выходы дешифратора соединены соответственно с первыми входами элементов И первой- группы, вторые входы которых соединены с вторым выходом блока управления имитацией неисправностей, первый вход которого соединен с выходом второго блока сравнения, с третьими входами элементов И первой группы, с упрввляS10ющим входом блока памяти, первая труп па информационных входов которого соединена с группой выходов второго счетчика, выход которого, соединен с первым входом блока формирования имч пульсов считывания,второй вход которого соединен с выходом блока памяти, с вторым входом блока управления имитацией неисправностей, третья группа входов которого соединена соответственно с первой группой выходов блока определения теста, вторая группа выходов которого соединена с второй группой информационных входов блока памяти, группа выходов которого соединена с первой группой входов блока определения теста, вторая группа входов которого соединена с первой группой выходов блока формирования импульсов считывания, с труппой управляющих входов блока памяти, вторая группа информационных входов которого соединена соответственно с выходами элементов И первой группы соответственно с информационными входами регистра, управляющие входы которого соединены с третьим выходомблока управления имитацией неисправностей, четвертая группа входов которого соединена соответственно с вы ходами регистра, с первыми входами элементов И второй группы, вторые вхо ды которых соединены соответственно с группой выходов эталонного узла, вы ходы элементов И второй группы соединены соответственно с пятой группой входов блока управления имитацией не исправностей, выход блока определени теста соединен с третьим входом блока формирования импульсов считывания вторая группа выходов -которого соеди нена с третьей группой входов блока определения теста. Блок управления имитацией неисправ ностей содержит узел запуска, счетчи переключатель, элемент ИЛИ, четыре регистра, триггер, три элемента И, группу элементов И, элемент НЕ, причем первый вход первой группы входов блока соединен с первым входом узла запуска, второй вход которого соединён с выходом первого элемента И и я ляется первым выходом пятой группы выходов блока, второй вход первой группы входов которого соединен со счетным входом счетчика, установочный вход которого соединен t выходом переключателя, с третьим входом узла запуска, с нулевыми входами первого. 9 трет1 его и метвертрго реторого, гистров, с нулевым входом триггера и является третьим выходом блока, первый вход которого соединен с первыми входами элементов И группы, с первым входом первого элемента И, второй вход которого соединен t выходом элемента НЕ, вход которого соединен с выходом элемента ИЛИ и является первым входом блока, второй выход которого соединен с выходом узла запуска, с вторыми -входами элемен-. тов И группы, третьи входы которых являются соответственно второй группой входов блока, второй вход которого соединен с первым входом второго элемента И, второй вход которого соединен с выходом переполнения счетчика, с четвертым входом узла запуске, с первым входом третьего элемента И, группа входов которого соединена соответственно с инверсивными выходами первого регистра, единичные входы которого соединены соответственно с выходами элементов И группы, треть группа входов блока соединена соответственно с единичными входами второго регистра, выходы которого являются четвертой группой выходов блока, четвертая и пятая группы входов которого соединены соответственно с единичными входами третьего и четвертого регистров, выходы которых являются соответственно второй и третьей группами выходов блока, второй выход; пятой группы выходов которого соединен С выходом триггера, единичный вход которого соединен с выходим второго элемента И, третий выход пятой группы выходов блока соединен с выходом третьего элемента И, группа выходов узла запуска является первой группой выходов блока, Узел запуска содержит элемент И, элемент ИЛИ, триггер, переключатель, причем выход переключателя соединен с первым входом элемента И, второй вход которого является первым входом узла, второй вход которого соединен с первым входом элемента ИЛИ, второй вход которого является третьим входом узла, четвертый вход которого соединен с третьим входом элемента ИЛИ, выход которого соединен с нулевым входом триггера и является первым.выходом группы выходов узла, второй выход первой группы выходов которого соединен с инверсным выходом триггера, с-третьим входом элемента И, выход которого соединен с единичным входом триггера, прямой выход которого является выходом узла (1ричем блок формирования импульсов-считывания содержит элемент задержки, элемент НЕ, элемент И, два генератора тактовых импульсов, два счетчика, два дешифратора, две группы элементов И, причем первый вход б/тока соединен с входом элемента задержки, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом элемента НЕ, вход которого является вторым входом блока, выход элемента соединен с управлякедим входом первого генератора тактовых импульсов, вы ход которого соединен со счетным вхо дом первого счетчика, с первыми входами элементов И первой группы, вторые входы которых соединены соответственно с выходами первого дешифрато ра, входы которого соединены с выходами разрядов счетчика, выход переполнения которого соединен с управля ющим входом второго генератора такто вых импульсов, выход которого соединен со счетным входом второго счетчи ка , с первыми входами элементов И второй группы, вторые входы которых соединены соответственно с выходами второго дешифратора, входы которого соединены с выходами разрядов второго счетчика, вход сброса которого соединен с входом сброса первого сче чика и является третьим входомблока выходы элементов И первой и второй групп являются соответственно выхода ми первой и второй групп блока. Кроме того, блок определения тест Jcoдepжит два элемента ИЛИ, элемент з держки, счетчик (п -t-l ) группу элементов И, Чгде п - число входных воздействий , дешифратор, регистр, формирователь импульсов, причем первая группа входов блока соединена с входами первого элемента ИЛИ, с входами второго элемента ИЛИ, выход которого соединен с входом элемента задержки, с первыми входами элементов первой группы, вторые входы которых соединены с выходами счетчика, счетный вход которого соединен с выходом первого элемента ИЛИ, выход элемента задержки соединен с входом сброса счетчика, выходы элементов И первой группы соединены с входами дешифратора, выходы которого соединены соответственно с первыми входами элементов И групп с второй по (п+1)-ую, вторые входы которых являются соответственно второй группой входов блока, выходы элемеитов И группы с второй no{h+1) -ую соединены соответственно с единичными входами регистра, нулевые входы которого соединены с выходом узла формирования импульсов и являются выходом блока, выходы регистра соединены соответственно с информационными входами уз ла формирования импульсов, первая и вторая группы выходов которого являются соответственно первой и второй группами блока, третья группа входов которого соединена соответственно с управляющими входами узла формирования импульсов. На фиг. 1 представлена структурная схема предлагаемог;о устройства; на фиг. 2 - блок формирования импульсов считывания; на фиг. 3 - блок определения теста; на фиг. k - формирователь импульсов;на фигi 5 - блок памяти; на фиг, 6 - схема блока управления имитацией неисправностей; на фиг. 7 - узел запуска; на фиг. 8 схема блока управления; на фиг. 9 имитатор неисправностей .. Устройство содержит генератор 1 псевдослучайных последовательностей, задающий 2 генератор, блок 3 формирователей сигналов, выход 4 блока формирования сигналов, вход 5 блока дискриминаторов, блок 6 дискриминаторов, первый вход 7 блока 8 сравнения, счетчик 9 блок 10 управления, группа Т1 входов контактного блока, контактный блок 12, блок 13 усилителей, сменная плата 1, эталонный узел 15, имитатор 16 неисправностей, блок 17 формирования импульсов считывания, счетчик 18, блок 19 сравнения,блок 20 управления имитацией неиспр авностей, блок 21 памяти, блок 22 определения теста, дешифратор 23 блок 2k индикации, группа 25 элементов И, регистр 26, группа 27 элементов И. Блок формирования импульсов считывания содержит элемент 28 задержки,элемент 29 НЕ, элемент НЕ 30, генератор 31 тактовых импульсов, счетчик 32, дешифратор 33 группа 3 элементов И, генератор 35 тактовых импульсов, счетчик 36, дешифратор 37 группа 38 элементов И. Блок определения теста содержит элементы 39 0 ИЛИ, элемент задержки, счетчик k2, группа k3 элемен9тов и, дешифратор k, группа 5 элементов И, регистр i(6,формирователь 4 импульсов. Формирователь импульсов содержит управляющие узлы k8 формирования импульсоЕ 5узлы 8 содержат элемент 9 И элемент 50 задержки, элемент 51 НЕ, элемент И,управляющий вход 53 ин (1)опма1 ионный вход 5 первый 55, вто рой 56 выходы, группу 57 элементов ИЛ элемент в ИЛИ, элемент 59 задержки, регистр 60. Блок памяти содержит узлы 61 памя ти, входы б2--68 узлов памяти, выходы узлов памяти, выход 73 блока, злементьг Jh-jd И. Блоч управления имитацией неиспра ностей содержит первую группу 77 выходов, вторую группу 78 выходов, тре тью группу 79 выходов, четвертую rpy пу 80 выходов, пятую группу 81 выходов, узел 82 запуска, счетчик 83 переключатель 8f, элемент 85 ИЛИ, регистры 86-88, триггер 89j элемент 90 И, группу 91 элементов И, ре гистр 92. элемент 93 НЕ, элементы , 95 И. Узел запуска содержит элемент 9б триггер 97, элемент 8 ИЛИ, переключатель 99. . Блок управления содержит элемент 10(1 И, триггер 101, элемент 102 ИЛИ, генератор 103 импульсов,элемент 10 И выход 105 элемента 10, элемент 106 триггер 107, элемент 108, ИЛИ, элемент 109 И, элемент 1ТО ИЛИ, триггер 111, дешифратор 112, группа 113 элементов 11, элемент k И, переключатель 115-117, элемент 118 ИЛИ. Имитатор неисправностей содержит переключатель 119j дешифратор 120 триггеры 121,122, элемент 123 И, триггер 12А, элемент 125 И, элемент 126 И, элемент 127 НЕ, элемент 128, 129 И, триггер 130, элементы 13Ь 13. И, элемент 133 НЕ, мент 13 И, Генератор 1,псевдослучайной после довательности обеспечивает равномерное распределение чисел в течение данного цикла проверки. Количество выходов генератора 1 псевдослучайных чисел определяется максимальным коли чеством входов проверяемого и эталонного блоков. Задающий генератор 2 обеспечивает синхронизацию работы генератора 1 и блока 3 формирователей. 25910 Блок 3 формирователей образует и подает на входы проверяемого и эталонного блоков последовательность наборов потенциальных сигналов, обеспечивая при определении минимизированного проверяющего теста, всей совокупности возможных входных сигналов. Блок 6 дискриминаторов определяет логическое значение сигнала на выходе. Блок 8 сравнения служит для сравнения в каждом такте теста выходных сигналов с блока 6, отражающих значение выходных сигналов проверяемой схемы, с выходным значением эталонной схемы. Счетчик 9 служит для подсчета количества выработанных входных воздействий. Блок 10 управления служит для управления работой блоков устройств в различных режимах. Контактный блок 12 служит для подключения входных сигналов проверяемого и эталонного узлов, при определении минимизированного проверяющего теста. Блок 13 усилителей служит для усиления сигналов, поступающих на эталонный узел 15, в режиме определения теста. Эталонный узел 15 является идентич- - ным проверяемому. Имитатор 16 неисправностей предназначен для имитации неисправностей в случае релейно-контактных схем типа обрыва и короткого замыкания и в случае бесконтактных схем-неисправностей типа постоянный О или 1 на выходе .элемента о Блок 17 формирования импульсов считывания совместно с блоком 22 предназначен для определения одного из минимизированных проверяющих тестов. С счетчика 18 поступает сигнал на вход элемента 28 задержки. Введение элемента задержки необходимо для анализа устройством неисправностей. Выходной сигнал с элемента задержки поступает на элемент И. На вход элемента 29 НЕ поступает сигнал с блока 27 памяти, Свидетельствующий о том, что все узлы 61 памяти блока 21 памяти находятся в нулевом состоянии. Выходной сигнал с элемента 29 НЕ поступает на второй вход элемента 30 НЕ, выходным сигналом с которого запускается первый генератор 31 тактовых импульсов. Импульсы с первого генератора 31 тактовых импульсов поступают на счетный вход счетчика 32, заполняя его. Выходные импульсы со счетчика 32 поступают на вход дешифратора 33. В соответствии с поступившей на вход кодовой комбинацией на выходе дешифратора 33 возбудится одна извыходных шин. Выходной сигнал с дешифратора 33 поступает на вход группы элементов 3 И. Количество элементов 3 И в группе определяется количеством выходов в дешифраторе 33. На второй вход группы З элементов И поступает сигнал с генератора 31 тактовых импульсов, обеспечивая синхронизацию выдачи сигналов импульсов, обеспечивая синх ронизацию выдачи сигналов с дешифратора 33. Выходные сигналы группы 3 элементов И являются импульсами считывания, а также они являются управляющими входными сигналами для группы tS элементов И блока 22 определения теста. Как только на выходе счет чика 32 импульсов появится последняя комбинация, то этим сигналом запускается второй генератор 35 тактовых импульсов. Частота его импульсов выбирается такой, чтобы в период следования между импульсами частоты генератора 31 опросить все разряды регистра 46 блока 22 определения теста. С выхода второго генератора 35 тактовых импульсов сигналы поступают на счетный вход счетчика Зб импульсов о Выходные сигналы со счетчика 36 поступают на дешифратор 37, выходные сигналы с которого поступают на входы группы 38 элементов И. На управляющие входы этих элементов поступают и 4пyльcы с генератора 35 так товых импульсов, обеспечивая синхронизацию выдачи.результатов дешифратора 37. Выходные импульсы группы 38 элементов И поступают на формирователь Ц7 блока 22 определения теста. Сброс счетчиков 32 и 36 осуществляет ся ПО команде с формирователя kj бло ка 22. Останов счетчика 36 произойдет после сброса первого счетчика 32 Блок 17 прекратит свою работу после того, как блок 21 памяти выдает сигнал на элемент 29 НЕ, о том что все узлы памяти блока 21 находятся в нулевом состоянии (т.ео записана нулевая информация). Узел 82 блока 20 обеспечивает выдачу команды на запуск устройства режиме определения теста, тем саым выдавая управляющие команды на локи 10 и 2, а также выдает управляющую команду на группу 2 элеентов И. Блок 21 памяти предназначен для хранения номеров входных воздействий, на которых проявляется заданная неисправность. Объем блока 21 определяется максимальным количеством входнь1х воздействий проверяемых узлов и количеством возможных неисравностей. Устройство работает следующим образом. В его работе предусмотрено два режима: первый режим - режим контроля, второй режим - режим определения минимизированных тестов для комбинационных схем. При использовании устройства в первом режиме, входы проверяемого блока и эталонного подключаются параллельно к блоку 3 формирователей входных сигналов. После ручного запуска блока 10 управления этот блок приводит в исходное состояние все остальные блоки, а затем включает генераторы 1 и 2. Паследовательности сигналов, вырабатываемые этими генераторами, поступают на блок 3 формирователей входных сигналов, которые образуют и подают на входы проверяемого и эталонного блоков последовательность наборов потенциальных сигналов. После установки на входах блоков набора потенциалов, соответствующих текущему такту теста, блок 10 увеличивает на единицу содержимое счетчика 9. Сигналы на выходах проверяемого блока в каждом такте теста анализируются блоком 6 дискриминаторов, ко-, торые определяют логическое значе-. ние сигнала на каждом выходе. Выходные сигналы блока 6 дешифраторов, отражающие значения выходов проверяемого блока, сравниваются в каждом такте теста блоком 8 сравнения с выходными сигналами эталонного блока При обнаружении неравенства блок 8 выдает соответствующий сиг нал в блок 10 управления, который включает генераторы 1 и 2, останавливая тем самым тест, и сигнализируя ( в блоке индикации )о неисправности проверяемого блока. Аналогичная реакция блока 10 имеет место по сигналу блока 6 при отклонении потенциала хотя бы на одном выходе проверяемой схемы за пределы допусков для 1 и О. В обоих случаях счетчик 9 фиксирует номер такта теста, в котором обнаружена неисправность проверяемого блока. При работе устройства во втором режиме, т.е. при определении одного из минимизированных проверяющих тактов, по команде с блока 20 управления выдается команда на приведение блоков устройства в исходное состояние и проведение самопроверки устрой ства. После проведения самопроверки блок 20 управления выдает команду поступающую в сметчик 18 и с него в блок 16 имитации неисправностей. Блок 16 выдает команду о введении первой неисправности в узел 15. С бл ка 18 сигнал одновременно поступает ив блок 21 о введении этой неиспра ности в узел 15. поступающий с блока 16 имитации в блок 20. Если эта н исправность не будет проявляться хотя бы на одном из всех возможных входных наборов, то номер этой неисправности запоминается в блоке 20 и выносится на индикацию в блок с блока 20. I По команде с блока 10 генераторы и . с помощью блока 3 формируют все возможные входные воздействия. Сигна лы с выхода блока 3 одновременно поступают на дешифраторов. С выхода дешифратора .3 импульсы поступают на вход группы 25 элементов И, подготавливая их к открытию. При наличии команды с блока 20, которая выдается только во втором режиме и несовпадении выходной функции узла 15 и проверяемого, входные последовательности поступают на блок 2 памяти и регистр 26 С регистра 26 информация о номере входного воздействия, на которой фиксируется неисправность, поступает в блок 20, и эта же информация поступает на группу 27 элементов И. Выходная информация группы 27 элементов И, соответствующая эталонному значению выходной функ ции, поступает в блок 20. Блок 19 будет выдавать выходной сигнал только тогда, когда будет фиксироваться отличие выходной функции проверяемого узла от выходной функции эталонного узла 15, с выхода блока 19 сигнал поступает в блок 20, фиксируя факт наличия неисправности, в блок 21, раз решая запись единицы в ячейку памяти ЭТОГО блока; на элементы 25 И, обеспечиваюи ие фиксацию номера входного набора, на котором обнаружена неисправность. Информация о номере этого входного набора с выхода элементов 25 И поступает в блок 20 управления. После того как блок 3 вырабатывает все возможные входные- воздействия, с блока 10 в блок 20 поступает команда о введении новой- неисправности. Блок 20 выдает команду в счетчик 18, увеличивая его содержание на единицу и тем самым обеспечивая введение новой неисправности. Дальнейшая работа устройства будет аналогична. С введением последней неисправности, со счетчика 18 выдается команда на формирователь 17 импульсов считывания. В блоке 21 памяти в результате анализа неисправностей на всех возможных входных воздействиях образовался массив исходных данных для определения теста. С поступлением запускающего импульса на блок 17, он начинает формировать импульсы считывания, которые поступают в блок 21 и 22. С блока 21 памяти считывается информация о количестве неисправностей, определяемых на каждом входном наборе, эта информация в блоке 22 определения теста суммируется и выделяется входное воздействие, определяющее максимальное количество неисправностей „ Информация о номере входного воздействия, определяющего максимальное количество неисправностей, поступает с блока 22 в блоки 20 и 21. Поступившая информация обеспечивает обнуление ячеек памяти в блоке 21, которые соответствуют входному воздействию, определяющему максимальное количество неисправностей, и узлов 61 памяти тех входных воздействий, неисправности которых уже,определены входным воздействием, содержащим максимальное количество единиц. После, этого блоком 22 совместно с блоком 17 определяется следующее входное воздействие, содержащее максимальное количество единиц, только уже на новом массиве данных блока 21. Этот процесс будет продолжаться до тех пор, пока весь массив памяти блока 21 не станет нулевым, что послу«ит сигналом для прекращения процесса определения теста о Таким образом, в блоке 20 будут зафиксированы входные тестовые воздействия проверяющего теста и эталонные значения выходной функции. 10 Преимуществом предлагаемого устройства перед известными является то, что оно позволяет автсматически, без математического описания проверяемого узла, зная только заданный класс неисправностей, шределить один из проверяющих тестов, близкий к минимальному, что позвопйт при его применении снизить расход ресурса проверяемой аппаратуры а в связи с этим экономическиё расходы. Разработанное устройство также может ешать и задачи 59 определения эффективности случайных выбранных тестов, что делалось в известном устройстве, в этом случае в первый блок .1 памяти записываются не входные воздействия, а номер анализируемого случайного теста. Предлагаемое устройство позволяет автоматически проводить самопроверку устройства с целью определения его технического состояния перед началом определения проверяющего теста для за данной проверяемой схемы.

От П

,™:

li

57

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1981 |

|

SU1012263A1 |

| Устройство для контроля дискретной аппаратуры с блочной структурой | 1983 |

|

SU1168952A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1608672A1 |

| Устройство для контроля дискретных систем | 1983 |

|

SU1117640A1 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1278855A1 |

| Устройство для контроля цифровых блоков | 1983 |

|

SU1128267A1 |

| Устройство для имитации отказов дискретной аппаратуры | 1990 |

|

SU1815642A1 |

| Устройство для построения диагностического теста и диагностирования комбинационных схем | 1983 |

|

SU1160420A2 |

| Устройство для диагностирования логических блоков | 1986 |

|

SU1520518A1 |

| Тренажер оператора радиоэлектронной аппаратуры | 1989 |

|

SU1658193A1 |

50

,5J 55

8

Я б Сброс f( 6 ff/7

te.

Ни 25

J -

От 8 От9

НйЮ

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Регулируемое сопротивление | 1974 |

|

SU519723A1 |

Авторы

Даты

1983-08-23—Публикация

1981-08-03—Подача