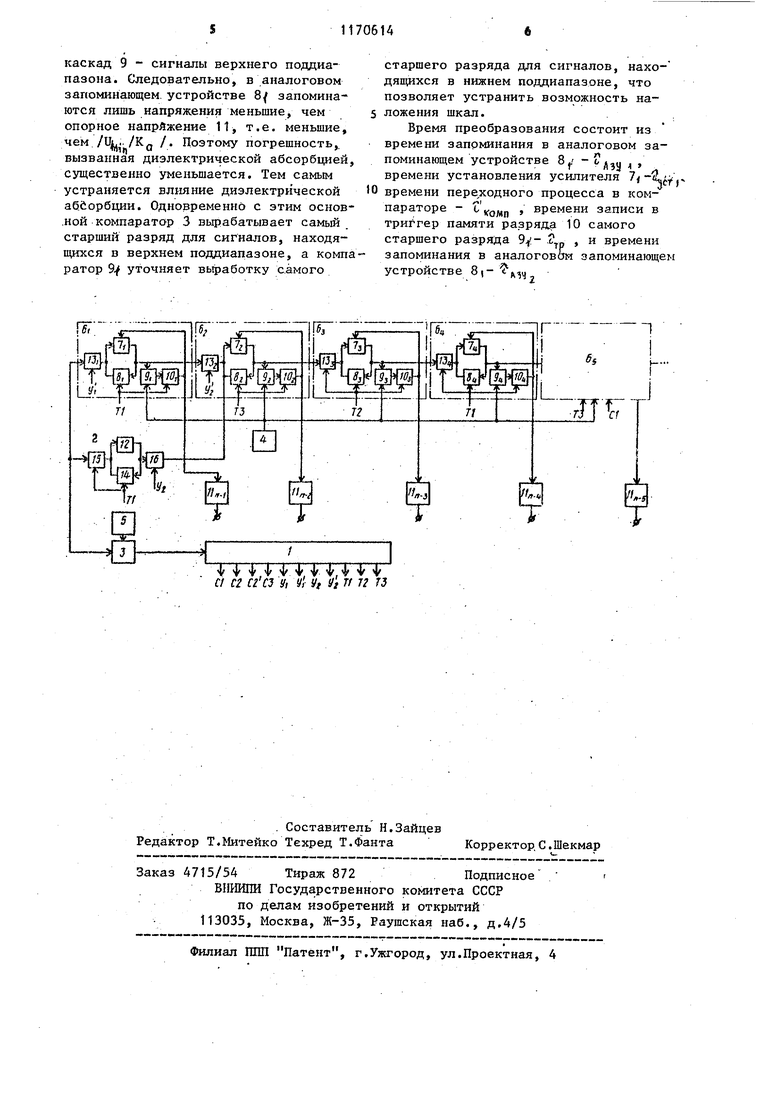

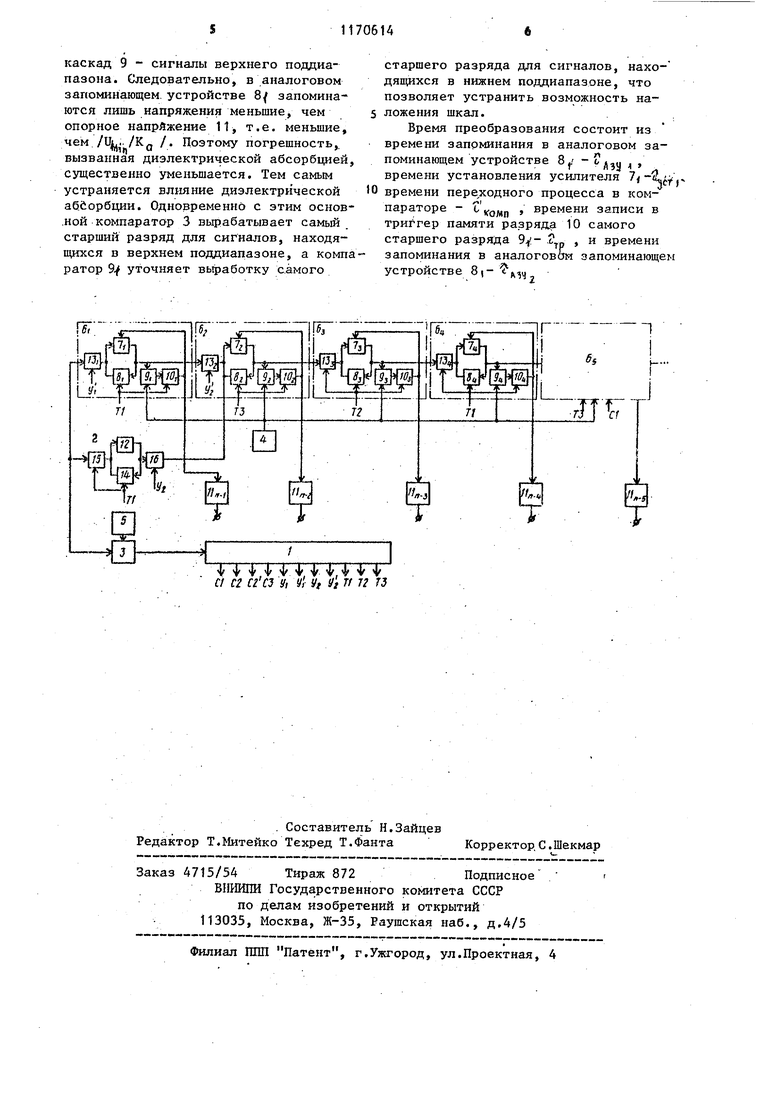

Изобретение относится к радиоэлек тронике и вычислительной технике и может быть использовано в быстродействующих преобразователях с логарифмической характеристикой. Цель изобретения - упрощение многоразрядного логарифмического аналого-цифрового преобразователя. На чертеже приведена функциональная схема многоразрядного логарифмического преобразователя. Многоразрядный логарифмический аналого-цифровой преобразователь содержит блок синхронизации 1, буферньш каскад 2, основной компаратор 3, первый 4 и второй 5 источники опорно го напряжения, формирователи разряда , усилители ., аналоговые запоминающие устройства 8y-8j,, компараторы 9,,-9, триггеры памяти , сдвиговые регистры 11,-1Т, , буферный усилитель 12, входные ключи 13,-13, буферное аналоговое запоминающее устройство 14, первый 15 и второй 16 ключи. Коэффициенты переда чи усилителей равны D ,D ,..., D соответственно. Первый источник опорного напряжения равен максимальному значению преобразуемого напряже ния и . Второй источник 5 опорного напряжения порогом основного компаратора 3, используемого для разбиения динамического диапазона на два поддиапазона. Такое разбиение предназначено для устранения влияния диэлектрической абсорбции конденсато ров, применяемых в аналоговых запоми нающих блоках 8,-8. Опорное напряже ние источника -5 выбирается меньше и . /К(),,г где и, минимальный преобразуемый сигнал, К - коэффициент ди :электрической абсорбции конденсаторов. Блок синхронизации 1 вырабатывает управляющие сигналы С1, С2, СЗ, У1, У2, Т1, Т2, ТЗ. Многбразрядный логарифмический аналого-цифровой преобразователь работает следующим образом. При появлении сигнала Т1 первый ключ 15 замыкается, аналоговое 8/j и буферное 14 аналоговое запоминающие устройства работают в режиме выборки напряжения, триггер памяти 10,j устанавливается в единичное состояние, вследствие чего усилитель 7 работает в режиме повторителя напряжения. В зависимости от состояния основного компаратора 3 по сигналам управления У1 И-У1 замыкается входной ключ 13 , если преобразуемый сигнал и„ меньше опорного напряжения источника 5 илиразмыкается первый ключ 15 в случае, когда Од не меньше опорного напряжения источника 5. В случае, когда Ujf не меньше опорного напряжения источника 5, преобрат зуемый сигнал Uy проходит через первый ключ 15 и буферный усилитель 12 и запоминается в буферном аналоговом запоминающем устройстве 14. При этом на вход усилителя 7 подан нулевой потенциал и напряжение в аналоговом запоминающем устройстве 8 равно нулю. После окончания сигнала управления Т1 первый ключ 15 и входной ключ 13 размыкаются, а буферное аналого ое запоминающее устройство 14 и аналоговое запоминающее устройство 8( переходят в режим хранения. При этом напряжения с выхода буферного аналогового зaпoмliнaющeгo устройства 14 и аналогового запоминающего устройства 8| поступают на входы буферного усилителя 12 и усилителя 7 соответственно, а триггер памяти 10 устанавливается в нулевое состояние, что приводит к работе усилитель 7 с коэффициентом передачи, равным единице. Так как U U /К„, то отX rtiQjr „т сутствует сигнал управления С/, предназначенный для записи состояния компаратора 9у в триггер памяти 10/ поэтому состояние триггера памяти 10/ остается неизменным. При появлении сигнала управления ТЗ происходит сдвиг в сдвиговом регистре 11|,., и запись состояния триггера памяти 10 в сдвиговый регистр 11jj. , замыкается второй ключ 16 при разомкнутом состоянии входного ключа 13j , аналоговое запоминающее устройство 8 рабо- . тает в режиме выборки, триггер памяти 10 устанавливается в единичное состояние,I что обусловливает работу усилителя Ту в режиме повторителя напряжения. В результате преобразуемый сигнал и , запомненный в буферном аналоговом запоминающем устройстве 14, проходит через буферный усилитель 12, второй ключ 16 и усилитель 7.J с коэффициентом передачи, равным в данный момент едигшце, и запоминается в аналоговом запоминающем устройстве Bg. После окончания сигнсша управления ТЗ размыкается 31 второй ключ 16, аналоговое запоминающее устройство 8 переходит в режим хранения. Триггер памяти 10 2 устанав ливается в нулевое состояние, что. обусловливает на единичный коэффициент передачи усилителя 7, напряжени запомненное в аналоговом запоминающем устройстве 8, подводится к вход усилителя 7. По сигналу управления Т1 формирователь разряда 6 и буферньш каскад 2 возвращаются в исходное состояние для выборки следукщего зна чения преобразуемого сигнала. управления блока синхрони зации 1 для формирователя разряда 6 совпадают с сигналами управления для каскада формирователя разряда 6,., а для формирователя разряда 6 у- - с сиг налами управления формирователя разряда 6i и так далее. . В случае, когда Uj меньше опорног напряжения источника 5 происходит пр цедура, аналогичная предьщущему случаю, лишь с отличием, состоящим в том, что входной ключ 13f .замыкается для запоминания преобразуемого сигна ла Uj( в аналоговом запоминающем устройстве 8,/ при подаче соответствующих сигналов управления.. В данном случае после окончания сигнала управ ления Т1 на выходе усилителя устанавливается напряжение ( /2 U,U,D , которое сравнивается компаратором 9f с опорным напряжением первого источника опорного напряжения 4, равным тах Р подаче сигнала управлени С2 в триггер памяти разряда 10 запоминается состояние компаратора 9 которое равно , при (и.. D ) S и . ill , при (.и, Б результате коэффициент передачи усилителя 7(/ устанавливается по состоянию триггера памяти разряда 10, а выходное напряжение усилителя 7 равно с учетом О) и (2) J/2 /„ J/2 при (UyDpiUp,; Ux при () и. Таким образом, вьфабатызается самый старший разряд . В отличие от предыдущего случая замыкается, клю 47 при разошснутом состоянии второго U4 ключа 16, в результате в аналоговом запоминающем устройстве 8, хранится .выходное напряжение усш1ител« 7, , определяемое по (3). Для обоих случаев к входу ус1тителя 7н в момент подачи сигнала управления Т1 подводится напряжение, равное с учето11(3) Уп-//г U,U,D при этом на выходе усилителя 7л устанавливается напряжение f/2 . D которое аналогично первому формирова телю разрядов 6 сравнивается компаратором 83. с опорным напряжением 4. По сигналу управления СТ в триггер памяти разряда 10 запоминается состояние компаратора 9, равное 0, и, , Jo. 1 IJ1 l, при и„о(ж. После этого на вход ключа 4 п поступает напряжение, равное с учетом (4), (5) и (6) и.и /п-г/2- „-г/2 Таким образом, вырабатьшается второй разряд преобразователя. При подаче сигнала управления Т2 ключ 13, замыкается, триггер памяти разряда 9 устанавливается в единичное состояние, при этом усилитель 7 работает в режиме повторителя напряжения, а аналоговое запоминающее устройство 8j запоминает напряжение, определяемое по (7), и так далее. В дальнейшем происходит та же процедура, что и в формирователе разряда 6-, а в последующих каскадах - аналогично работе формирователя разряда 6. TiaK как объем сдвиговых регистров уменьшается на 1 в сторону младших разрядов и коэффициенты передачи управляемых усилителей установлены в соответствии с логарифмической шкалой, то на выходные клеммы преобразЬвателя одновременно поступает информация о коде одной выборки, соответ- ствующем логарифмической шкале. Из описа}П1ого видно, что основной компаратор 3 разбивает динамический диапазон преобразователя на два под- диапазона, вследствие чего в фориирователь самого старшего разряда 6 поступают лишь сигналы, находящиеся в нижнем поддиапазоне, а в буферный

каскад 9 - сигналы верхнего поддиапазона. Следовательно, в аналоговом запоминающем устройстве 8 запоминаются лишь напряжения меньшие, чем опорное напрйжение 11, т.е. меньшие, чем,/Ujf../Kg /. Поэтому погрешность,, вызванная диэлектрической абсорбцией, существенно уменьшается. Тем самым устраняется влияние диэлектрической абсорбции. Одновременно с этим основ.ной компаратар 3 вырабатывает самьй . старший разряд для сигналов, находящихся в верхнем поддиапазоне, а компаратор 9 уточняет вьфаботку самого

старшего разряда для сигналов, находящихся в нижнем поддиапазоне, что позволяет устранить возможность наложения шкал.

Время преобразования состоит из времени запоминания в аналоговом запоминающем устройстве 8.. - ,у , времени установления усилителя 7 времени пере ходного процесса в компараторе - с

, времени записи в

fOAin

триггер памяти разряда 10 самого старшего разряда 9.- „ , и времени запоминания в аналоговом запоминающем

л

устройстве 8)-

АЗЧ

| название | год | авторы | номер документа |

|---|---|---|---|

| Логарифмический аналого-цифровой преобразователь | 1979 |

|

SU790294A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1042036A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1996 |

|

RU2114501C1 |

| Устройство широкодиапазонного логарифмического аналого-цифрового преобразования | 1988 |

|

SU1571763A1 |

| Широкодиапазонный логарифмический аналого-цифровой преобразователь | 1988 |

|

SU1580557A1 |

| Устройство широкодиапазонного логарифмического аналого цифрового преобразования | 1980 |

|

SU900440A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1014137A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| ПРИЕМНИК ИМПУЛЬСНЫХ РАДИОСИГНАЛОВ И ИЗМЕРИТЕЛЬ УРОВНЯ ДЛЯ НЕГО | 1996 |

|

RU2097922C1 |

| Стробоскопический преобразователь | 1977 |

|

SU684453A1 |

МНОГОРАЗРЯДНЫЙ ЛОГАРИФМИЧЕС-, КИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий блок синхронизации, буфер- ный каскад, основной компаратор, два источника опорного напряжения и ifформирователей разряда, каждый из которых содержит последовательно соединенные усилитель и аналоговое запоминающее устройство, компаратор, выход которого подключен к информационному входу триггера памяти, выход которого соединен с входом управления коэффициентом передачи усилителя и информационным входом сдвигового регистра, первый вход компаратора подключен к выходу первого источника опорного напряжения, управляющий вход аналогового запоминающего устройства соединен с входом сброса триггера памяти и одним выходом блока синхронизации, буферный каскад содержит последовательно соединенные буферный усилитель и буферное аналоговое запоминаюп1ее устройство, управляюа ий вход которого соединен с управляющим входом аналогового запоми нающего устройства первого фop шpoвa теля разряда, первый вход основного компаратора соединен с выходом второго источника опорного напряжения, о т л и ч а ю щ и j{ с я тем, что, с целью упрощения, в кавдый формирователь разряда введен входной ключ, выход которого соединен с вьпсодом аналогового запоминающего устройства; и входом усилителя, выход последнего соединен с вторым входом компаратора и входом входного ключа последующего формирователя разряда, в буферный W каскад преобразователя введены два ключа, выход первого if3 них соединен с выходом буферного аналогового запоминающего устройства и входом буферного усилителя, выход, которого через другой ключ соединен с входом усилителя второго формирователя разряда, вход преобразователя подключен к входу входного ключа первого фopми о рователя разряда, входу первого ключе О) буферного каскада и второму входу ocf новного компаратора, подключенного ( ВЫХОДОМ к входу запуска блока синхронизации, другие выходы блока синхронизации подключены к соответствую1цим управляющим входам входных ключей первого и второго формирователей разряда и управляиндему входу второго ключа буферного каскада, выходы одвит говых регистров являются.разрядными выходами преобразователя.

V Ф Ф, V i Ф. V V. Ф V V

С/ сг сгсз у, у , yt У iff 12 3

| Устройство для очистки полых изделий | 1985 |

|

SU1290057A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Логарифмический аналого-цифровой преобразователь | 1979 |

|

SU790294A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-07-30—Публикация

1983-02-11—Подача