1

Изобретение относится к информационно-измерительной технике и может быть использовано в преобразователях напряжения в код. с логарифмической функцией преобразования.5

Известен преобразователь, содержащий блок управления два канала последовательно соединенных усилителей , входы которых соединены с источником преобразуемых напряжений, и аналого- 0. вых запоминающих устройств, выходы последних через компараторы подключены к триггерам памяти разрядов , выходы которых подключены к сдвиговым регистрам, объем которых уменьшается 15 на единицу с уменьшением веса разрдда, выходы последних разрядов сдвиговых регистров подсоединены к буферно-му регистру 13

Недостатком данного устройства яв-20 ляется малый динамический диапазон и невозможность получения логарифмического преобразования.

Цель изобретения - расширение функциональных возможностей, а также по- 25 вышение надежности устройства.

Поставленная цель достигается тем, ч;т6 в логарифмический аналого-цифровой преобразователь, содержащий блок управления два канала из П последова- 30

тельно соединенных усилителей и П аналоговых запоминаюших устройств, входы первых усилителей объединены и соединены с выходом источника преобразуемого напряжения, выходы каждого из п аналоговых запоминающих блоков подключены через компаратор ко входам триггеров памяти разрядов, соединенных с соответствующими входами п сдвиговых регистров каждого канала, введены дополнительный компаратор, триггер, сдвиговый регистр, 2(п -l) элементов И, (п -l) элементов ИЛИ,причем выходы триггеров памяти разрядов подключены к управляющему входу соответствующих усилителей, выход первого аналогового запоминающего блока второго канала подключен к дополнительному компаратору, выход которого через триггер памяти подключен к г разрядному дополнительному сдвиговому регистру, выход которого соединен с выходной клеммой старшего разряда и с первым входом (П-1/ элементов И первой группы, а через инвертор с первым входом (п -1) элементов И второй группы, вторые входы (И -1) элементов И первой группы подключены к соответствующим выходам (п -1) сдвиговых регистров первого канала, вторые входы (п -1) .элементов И второй группы подключены к соответствующим выходам П сдвиговых регистров второго канала, выходы элементов И одного разряда подключены ко входам (П-1) элементов ИЛИ, выходы которых соединены с выходными клеммами преобразователя.

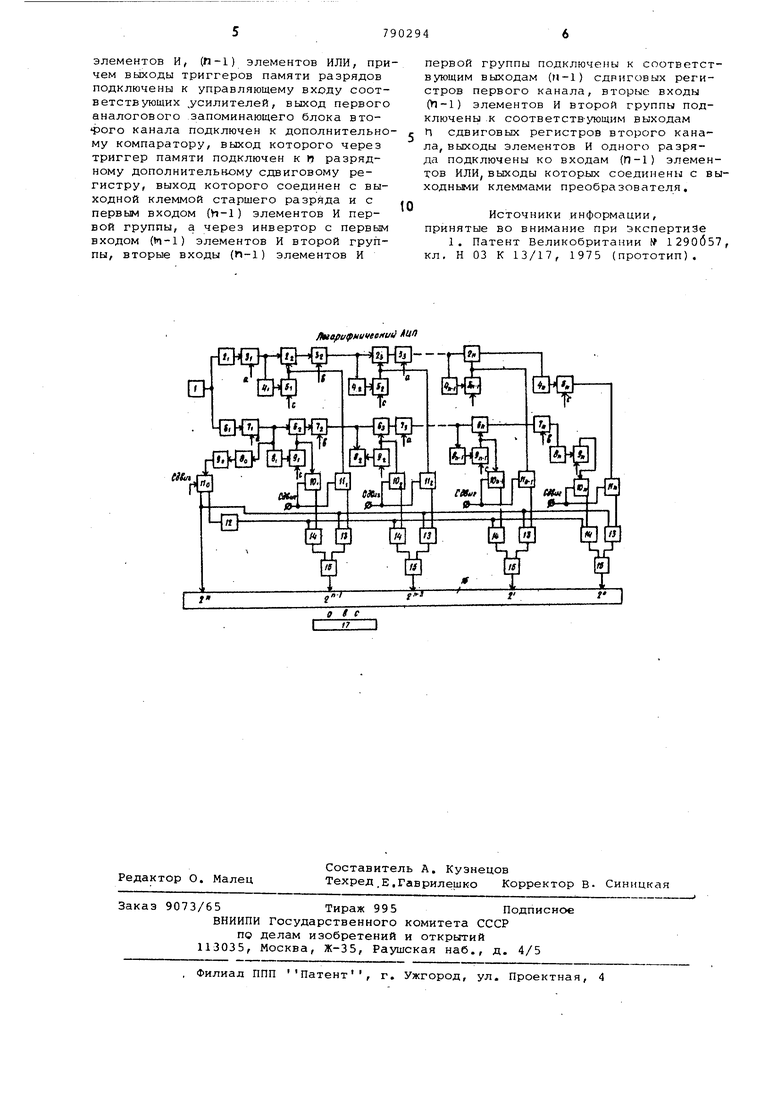

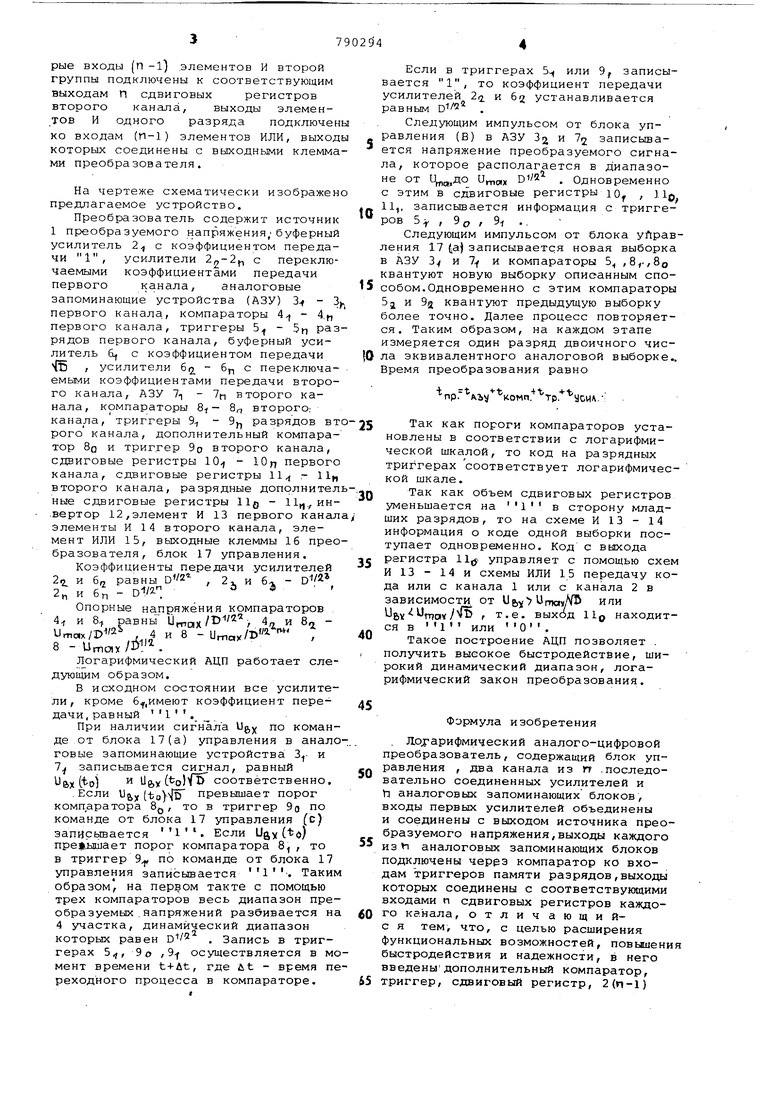

На чертеже схематически изображено предлагаемое устройство.

Преобразователь содержит источник 1 преобразуемого напряжения; буферный усилитель 2 с коэффициентом передачи 1, усилители с переключаемыми коэффициентами передачи первого канала, аналоговые запоминающие устройства (АЗУ) 3 - 3 первого канала, компараторы 4-j - 4.f, первого канала, триггеры 5 - 5п разрядов первого канала, буферный усилитель бь, с коэффициентом передачи (5 , усилители 6(2 - с переключаемыми коэффициентами передачи второго канала, АЗУ 7 - t второго канала, компараторы 8-г - 8 второго; канала, триггеры 9 - 9, разрядов второго канала, дополнительный компаратор SQ и триггер 9о второго канала, сдвиговые регистры 10 - 10 первого канала, сдвиговые регистры И - llj, второго канала, разрядные дополнительные сдвиговые регистры HQ - 11., ин-вертор 12,элемент И 13 первого канала элементы И 14 второго канала, элемент ИЛИ 15, выходные клеммы 16 преобразователя, блок 17 управления.

Коэффициенты передачи усилителей 22. и 6,2 Равны О /г- , 2j и 6 - 2, и 6п - D/2.,

Опорные напряжения компараторов . 4 и 8 равны ирппх/ и 8, , .,4 и 8 - ,x/D , 8 - Urnoix/В - .

Логарифмический АЦП работает следующим образом,

В исходном состоянии все усилители, кроме 6.у,имеют коэффициент передачи, равный 1.,,.

При наличии сигнала Ug,) по команде от блока 17(а) управления в анало говые запоминающие устройства 3. и 1 записывается сигнал, равный Uftxtto) и Uftv (tol T соответственно,

.Если Ug,y (to)llГ превышает порог комп аратора BQ , то в триггер 9о по команде от блока 17 управления (с) запйсьшается . Если (to) пре ышает порог компаратора 8 , то в триггер 9 по команде от блока 17 управления записывается . Таким образом, на пердом такте с помощью трех компараторов весь диапазон преобразуемых . напряжений разбивается на 4 участка, динамический диапазон которых равен D/ . Запись в триггерах 5, 9 о ,9 осуществляется в момент времени t+At, где fit - время переходного процесса в компараторе.

Если в триггерах 5 или 9, записывается 1, то коэффициент передачи усилителей 2/ и бд устанавливается равным D ,

Следующим импульсом от блока управления (В) в АЗУ 3 и 72 записьшается напряжение преобразуемого сигнаа, которое располагается в диапазоне от Ц„а,до UfTicxx , Одновременно с этим в сдвиговые регистры ю , 11д 11,, записывается информация с триггеров 5 , 9о , 9i ..

Следующим импульсом от блока уЛравения 17 ta)записывается новая выборка АЗУ ЗУ и 7у и компараторы 5 ,8,. ,8о вантуют новую выборку описанным способом.Одновременно с этим компараторы 5j и 9а квантуют предыдущую выборку более точно. Далее процесс повторяется. Таким образом, на каждом этапе измеряется один разряд двоичного числа эквивалентного аналоговой выборке,. Время преобразования равно

прГ АЬУ/ КОМП...:

Так как пороги компараторов установлены в соответствии с логарифмической шкалой, то код на разрядных триггерах соответствует логарифмической шкале,

Так как объем сдвиговых регистров уменьшается на i в сторону младших разрядов, то на схеме И 13 - 14 информация о коде одной выборки поступает одновременно. Код с вьахода

регистра ll,j управляет с помощью схем И 13 - 14 и схемы ИЛИ 15 передачу кода или с канала 1 или с канала 2 в зависимости от UE,Y UrTtciyN5 ипи Ujix mav/ f т.е, выход lip находится в Ч или О ,

Такое построение АЦП позволяет . получить высокое быстродействие, широкий динамический диапазон, логарифмический закон преобразования.

Формула изобретения

. Л.о;гарифмический аналого-цифровой преобразователь, содержащий блок управления , два канала из П .последовательно соединенных усилителей и Ь аналоговых запоминающих блоков, входы первых усилителей объединены и соединены с выходом источника преобразуемого напряжения,выходы каждого

5 из и аналоговых запоминающих блоков подключены через компаратор ко входам триггеров памяти разрядов,выходы которых соединены с соответствующими входами п сдвиговых регистров каждого канала, отличающийс я тем, что, с целью расширения функциональных возможностей, повыиения быстродействия и надежности, в него введеныдополнительный компаратор,

5 триггер, сдвиговый регистр, 2(п-1)

элементов И, (П-1) элементов ИЛИ, причем выходы триггеров памяти разрядов подключены к управляющему входу соответствующих .усилителей, выход первого аналогового запоминающего блока втофого канала подключен к дополнительному компаратору, выход которого через триггер памяти подключен к п разрядному дополнительному сдвиговому регистру, выход которого соединен с выходной клеммой старшего разряда и с первым входом (h-l) элементов И первой группы, а через инвертор с первым входом (tn-1) элементов И второй группы, вторые входы (П-1) элементов И

первой группы подключены к соответствующим выходам (П-1) сдвиговых регистров первого канала, вторые входы (1-1) элементов И второй группы подключены .к соответств-ующим выходам h сдвиговых регистров второго канала, вЕзКоды элементов И одного разряда подключены ко входам (П-1) элементов ИЛИ, выходы котор-ых соединены с выходньми клеммами преобразователя.

0

Источники информации, принятые во внимание при Экспертизе

1. Патент Великобритании № 1290б57, кл, Н 03 К 13/17, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоразрядный логарифмический аналого-цифровой преобразователь | 1983 |

|

SU1170614A1 |

| Калибратор переменного напряжения | 1983 |

|

SU1115031A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1042036A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство широкодиапазонного логарифмического аналого-цифрового преобразования | 1988 |

|

SU1571763A1 |

| Цифроаналоговый генератор телевизионного сигнала | 1989 |

|

SU1654978A1 |

| Множительно-делительное устройство | 1980 |

|

SU949662A1 |

| УСТРОЙСТВО СЧИТЫВАНИЯ С ВРЕМЕННОЙ ЗАДЕРЖКОЙ И НАКОПЛЕНИЕМ СИГНАЛОВ С МНОГОЭЛЕМЕНТНЫХ ФОТОПРИЕМНИКОВ ИНФРАКРАСНОГО ИЗЛУЧЕНИЯ | 2012 |

|

RU2498456C1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Цифроаналоговый преобразователь с автокалибровкой | 1989 |

|

SU1683176A1 |

/taapuifHuvienuii Лич

IP

I 1

Л«НМ

Авторы

Даты

1980-12-23—Публикация

1979-02-22—Подача