Ј

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1981 |

|

SU1109872A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1068838A1 |

| Цифровой фазовый детектор | 1980 |

|

SU1352615A1 |

| Цифровой фазовый детектор | 1980 |

|

SU875303A1 |

| Цифровой фазовый детектор | 1980 |

|

SU898588A1 |

| Способ цифрового фазового детектирования импульсных последовательностей на неравных частотах и устройство для его осуществления | 1979 |

|

SU879738A1 |

| Цифровой синтезатор частот | 1991 |

|

SU1803977A1 |

| Цифровой фазовый детектор | 1980 |

|

SU892654A1 |

| Цифровой фазовый детектор | 1982 |

|

SU1064421A1 |

| Устройство приема телеметрической информации | 1989 |

|

SU1735883A1 |

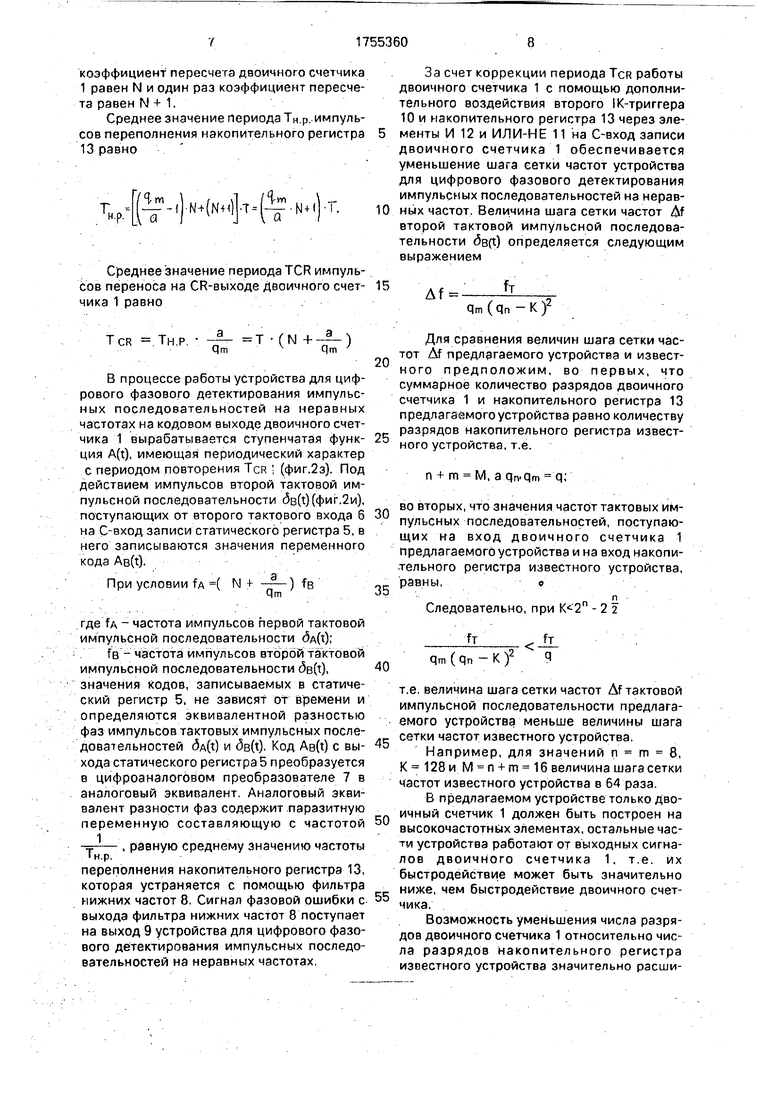

Сущность изобретения: устройство содержит двоичный счетчик 1, статический регистр 5, цифроаналоговый преобразователь б, фильтр нижних частот 8, два УК-триггера 3 и 10, элемент И 12, элемент ИЛИ-НЕ 11. накопительный регистр 13, два информационных входа 4 и 14, два тактовых входа 2 и 6.2-1-3-11-1,3-10-3,10-13,10-12-11.14- 13-12,6-5,4-1-5-7-8. В устройстве счетная импульсная последоватеТгьяость поступает на вход двоичного счетчика 1, задержки переносов которого меньше задержки накопительного регистра известного устройства, т.к. накопительный регистр 13 выполнен в виде последовательного соединения сумматора и статического регистра. Уменьшение задержки переносов в двоичном счетчике 1 приводит к расширению диапазона рабочих частот импульсных посяедовательностей. 2 ил.

-ч

OJ

ел ы о о

фи 1

Изобретение относится радиотехнике и может быть использовано для получения сигналов рассогласования в системах АПЧ, для формирования сетки стабильных частот в приемно-передающей и измерительной аппаратуре.

Известно устройство для цифрового фазового детектирования на неравных частотах, содержащее , формирователи импульсных последовательностей, блок привязки импульсов входного сигнала и последовательно соединенные двоичный счетчик, статический регистр и цифроанало- говый преобразователь (ЦАП).

Недостатком этого устройства является большая величина шага сетки частот входного сигнала, которая определяется частотой опорного сигнала.

Наиболее близким по технической сущности и достигаемому результату является устройство, содержащее накопительный регистр, ЦАП, триггер и фильтр нижних частот.

Недостатком известного устройства является ограничение возможности выбора шага сетки частот Af импульсной последо- вательности входного сигнала, так как величина шага сетки частот зависит от емкости q накопительного регистра и определяется следующим выражением

.

где ft - частота тактовой импульсной последовательности, поступающей на вход нако- пительного регистра;

q 2м - емкость накопительного регистра (м - число разрядов накопительного регистра).

Возможность увеличения емкости q на- копительного регистра ограничена задержками операций поразрядного суммирования и переносов результатов суммирования из разряда в разряд в накопительном регистре. Задержки оказывают- ся значительными, так как на информационный вход накопительного регистра могут поступать многоразрядные числа (до 16 и более разрядов).

Указанные недостатки вызывают значи- тельное уменьшение диапазона рабочих частот известного устройства.

Цель изобретения - расширение диапазона рабочих частот.

Поставленная цель достигается тем, что в устройство для цифрового детектирования импульсных последовательностей на неравных частотах, содержащее накопительный регистр, информационный вход которого является первым информационным входом устройства для цифрового фазового детектирования импульсных последовательностей на неравных частотах, первый IK-триггер и последовательно соединенные цифроаналоговый преобразователь и фильтр нижних частот, выход которого является выходом устройства для цифрового фа- зового детектирования импульсных последовательностей на неравных частотах, дополнительно введены двоичный счетчик, информационный вход которого является вторым информационным входом устройства для цифрового фазового детектирования импульсных последовательностей на неравных частотах, статический регистр, включенный между разрядными выходами двоичного счетчика и информационными входами цифроаналогового преобразователя, второй IK-триггер, элемент И и элемент ИЛИ-НЕ, включенные последовательно между прямым выходом первого IK- триггера и С-входом записи двоичного счетчика, при этом прямой выход первого IK-триггера подключен к другому входу элемента ИЛИ-НЕ, инверсный выход - к К-вхо- ду второго IK-триггера, прямой выход которого соединен с К-входом первого IK- триггера и тактовым входом накопительного регистра, а инверсный выход - с 1-входом и инверсным R-входом первого IK-триггера, выход переполнения накопительного регистра подключен к другому входу элемента И, CR-выход переноса двоичного счетчика - к С-входу синхронизации первого IK-триггера, а счетный Т-вход двоичного счетчика объединены с С-входом синхронизации второго IK-триггера и является первым тактовым входом устройства для цифрового фазового детектирования импульсных последовательностей на неравных частотах, вторым тактовым входом которого является вход записи статического регистра.

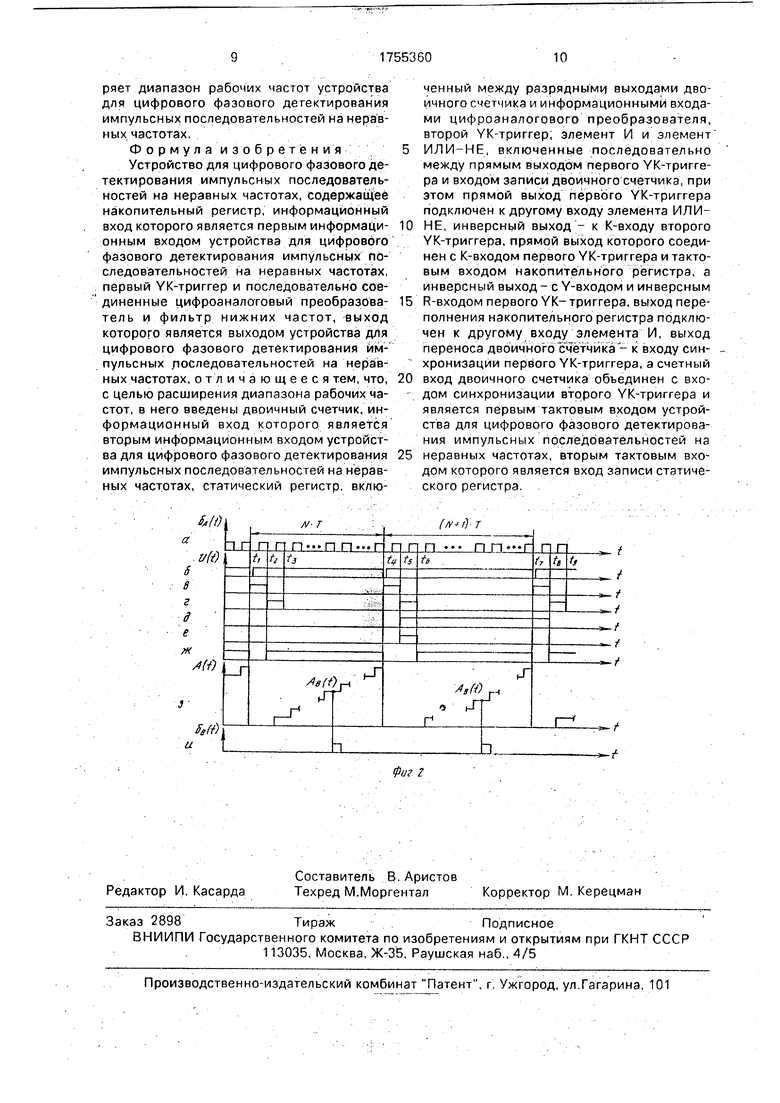

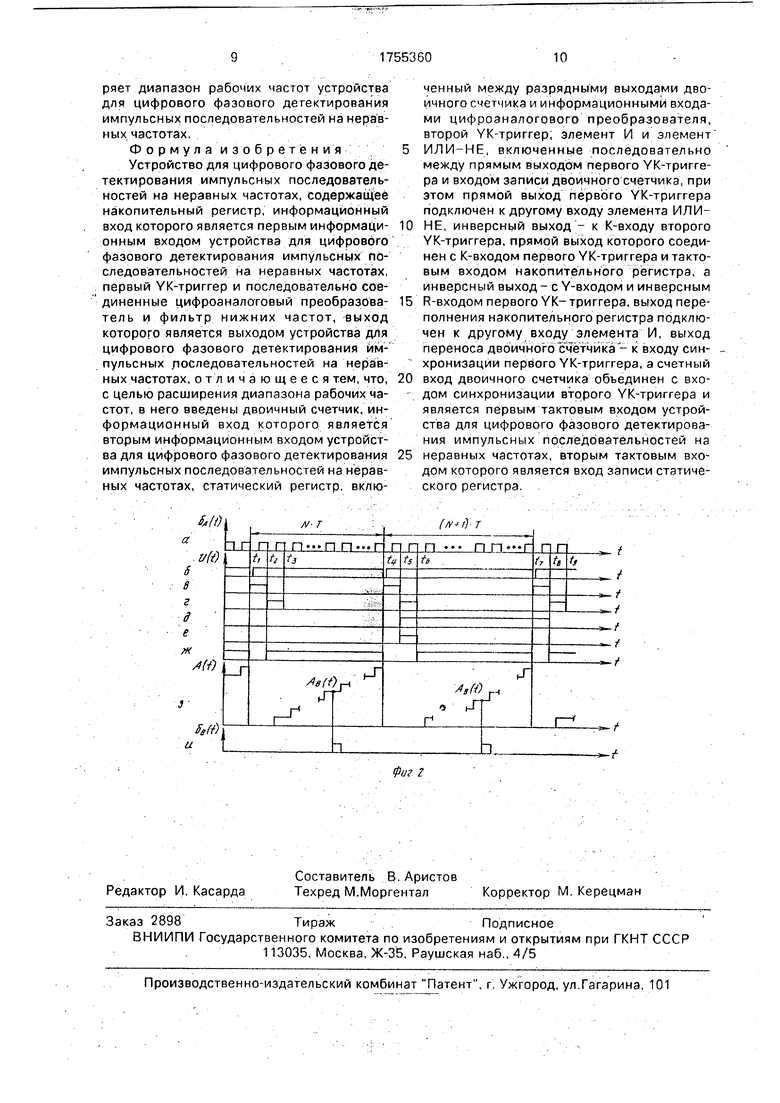

На фиг 1 изображена структурная электрическая схема устройства для цифрового фазового детектирования импульсных последовательностей на неравных частотах; на фиг,2 - временные диаграммы, поясняющие работу, устройства.

Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах (фиг.1) содержит двоичный счетчик 1, первый тактовый вход 2, первый IK-триггер З, второй информационный вход 4 статический регистр 5, второй тактовый вход 6, цифроаналоговый преобразователь 7, фильтр нижних частот 8, выход устройства 9, второй IK-триггер 10, элемент ИЛИ-НЕ 11, элемент И 12,

накопительный регистр 13, первый информационный вход 14.

Устройство для цифрового фазового детектирования работает следующим образом.

При поступлении двоичного кода К от информационного входа 4 и поступлении тактовой импульсной последовательности (5д(т.) от первого входа 2 (фиг.2а) соответственно на D-входы и счетный Т-вход двоим- ного счетчика 1 производится счетчика 1 производится их пересчет в режиме сложения. После пересчета N qn - К (где qn 2П - емкость двоичного счетчика 1; п - число разрядов двоичного счетчика 1) импульсов выходные разряды двоичного счетчика 1 устанавливаются в 1 и в момент времени ti на его CR-выходе переноса появляется - О (фиг.2б), который, воздействуя на С-вход синхронизации первого IK-триггера З, уста- навливает его прямой выход в 1 (фиг,2в). Эта 1 воздействует через элемент ИЛИ- НЕ 11 на С-вход записи двоичного счетчика 1, осуществляя запись двоичного кода К в двоичный счетчик 1.

С приходом заднего фронта следующего импульса тактовой импульсной последовательности 5д(т) в момент времени ta производится установка прямого выхода второго IK-триггерэ 10 в 1 (фиг.2г), а ин- версного - в О. Нулевой уровень инверсного выхода второго 1К-триггера 10, воздействуя на инверсный R-вход и 1-вход первого IK-триггера 3, устанавливает его прямой выход О, прекращая запись парал- лельного кода К в двоичный счетчик 1, и разрешает пересчет импульсов тактовой импульсной последовательности 5д(1), поступающих на Т-вход двоичного счетчика 1. Единичный уровень прямого выхода второ- го IK-триггера 10 в момент времени t2 поступает на тактовый вход накопительного регистра 13, имеющего емкость dm 2m (где m - число разрядов накопительного регистра 13). Содержание накопительного регист- ра 13 увеличивается с каждым тактом на величину а, поступающего от первого информационного входа 14.

С приходом заднего фронта следующего импульса тактовой импульсной последе- вательности 5л(т) в момент времени т,з производится выключение второго IK-триггера 10 (фиг.2г), т.е. на его прямом выходе появляется О, а на инверсном выходе - 1.

На интервале ti, осуществляется пересчет импульсов тактовой импульсной последовательности 3д(т). Длительность интервала ti, t« равна NT, где Т - период

тактовой импульсной последовательности A(t}; N - количество импульсов тактовой импульсной последовательности 5д(г.) на интервале t/, ц.

Если очередное значение QI, записываемое в накопительный регистр 13, равно или превышает его емкость, равную qm, он переполняется и коэффициентом пересчета становится равным N + 1 на время одного цикла заполнение двоичного счетчика 1.

Так, например, после пересчета импульсов тактовой импульсной последовательности 3д(т.) производится последовательное включение первого IK-триггера З (фиг.2в) в момент времени ц, затем второго IK-триггера 10 (фиг.2г) в момент времени ty, единичный уровень которого, воздействуя на тактовый вход накопительного регистра 13, вызывает его переполнение и появление 1 на его выходе (фиг.2д). При этом в результате совпадения единичных уровней прямого выхода второго tK-триггера 10 и выхода накопительного регистра 13 на интервале ts, te происходят формирование 1 на выходе элемента И 12 (фиг.2е) и увеличение длительности отрицательного импульса на С- входе записи двойч Шго с чТзтчйГка 1 (фиг.2ж) на время, равное периоду Т. Длительность интервала t4, равна (N + 1) Т.с

После пересчета N + 1 импульсов вновь производится последовательно включение в момент времени т первого IK-триггера З (фиг.2в), а в момент времени ts - второго IK-триггера 10 (фиг.2г), выходной единичный уровень которого, воздействуя на тактовый вход накопительного регистра 13, вызывает занесение в накопительный регистр 13 значения Qi qi + a qm. В этом случае число QI, записываемое в накопительный регистр 13, не вызывает его переполнения и на его выходе устанавливается в О (фиг.2д) С приходом заднего фронта следующего импульса тактовой импульсной последовательности 5д(т) в момент времени происходит выключение второго IK-триггера 10 (фиг.2г), т.е. на его прямом выходе появляется О, а на инверсном - 1.

При выполнении накопительного регистра 13 в момент времени ts (фиг.2д) в него фактически записывается число, равное ql Qi - qm, т.е. оно меньше относительно предыдущего значения, равного QI - а, на величину qm - а. Дальнейшее изменение кода в накопительном регистре 13 происходит, начиная со значения qi.

Таким образом в среднем за время одного периода импульсов переполнения накопительного регистра 13 ( -- - 1 ) раз

Э

коэффициент пересче га двоичного счетчика 1 равен N и один раз коэффициент пересчета равен N + 1.

Среднее значение периода Ти р импульсов переполнения накопительного регистра 13 равно

v(m- KH4 ИтСреднее значение периода TCR импульсов переноса на CR-выходе двоичного счетчика 1 равно

TCR Тн Р

а т -(N +-Ј)

qmvPm

В процессе работы устройства для цифрового фазового детектирования импульсных последовательностей на неравных частотах на кодовом выходе двоичного счетчика 1 вырабатывается ступенчатая функция A(t), имеющая периодический характер с периодом повторения TCR ; (фиг.2з). Под действием импульсов второй тактовой импульсной последовательности с5в)(фиг.2и), поступающих от второго тактового входа б на С-вход записи статического регистра 5, в него записываются значения переменного кода Ae(t).

а

При условии fА ( N+ ) fe

Qm

где ТА - частота импульсов первой тактовой импульсной последовательности 5д(т.);

fe - частота импульсов второй тактовой импульсной последовательности 5в(т), значения кодов, записываемых в статический регистр 5, не зависят от времени и определяются эквивалентной разностью фаз импульсов тактовых импульсных последовательностей 5д(т.) и 5в(х). Код Ав(г) с выхода статического регистра 5 преобразуется в цифроаналоговом преобразователе 7 в аналоговый эквивалент Аналоговый эквивалент разности фаз содержит паразитную переменную составляющую с частотой

1 , равную среднему значению частоты

I н р

переполнения накопительного регистра 13, которая устраняется с помощью фильтра нижних частот 8. Сигнал фазовой ошибки с выхода фильтра нижних частот 8 поступает на выход 9 устройства для цифрового фазового детектирования импульсных последовательностей на неравных частотах,

За счет коррекции периода TCR работы двоичного счетчика 1 с помощью дополнительного воздействия второго 1К-триггера 10 и накопительного регистра 13 через элементы И 12 и ИЛИ-НЕ 11 на С-вход записи двоичного счетчика 1 обеспечивается уменьшение шага сетки частот устройства для цифрового фазового детектирования импульсных последовательностей на неравных частот. Величина шага сетки частот Af второй тактовой импульсной последовательности deft) определяется следующим выражением

Af Qm ( Qn К )Z

Для сравнения величин шага сетки частот Af предлагаемого устройства и известного предположим, во первых, что суммарное количество разрядов двоичного счетчика 1 и накопительного регистра 13 предлагаемого устройства равно количеству разрядов накопительного регистра известного устройства, т.е.

n + m M, a q;

во вторых, что значения частот тактовых импульсных последовательностей, поступающих на вход двоичного счетчика 1 предлагаемого устройства и на вход накопительного регистра известного устройства, равны,о

- Следовательно, при - 2 2

fr

40

qm ( qn - К Y

JL q

5

т.е. величина шага сетки частот Af тактовой импульсной последовательности предлагаемого устройства меньше величины шага ,. сетки частот известного устройства.

Например, для значений n m 8, К 128 и M n + m 16 величина шага сетки частот известного устройства в 64 раза.

В предлагаемом устройстве только дво- Q ичный счетчик 1 должен быть построен на высокочастотных элементах, остальные части устройства работают от выходных сигналов двоичного счетчика 1, те. их быстродействие может быть значительно ниже, чем быстродействие двоичного счетчика.

Возможность уменьшения числа разрядов двоичного счетчика 1 относительно числа разрядов накопительного регистра известного устройства значительно расширяет диапазон рабочих частот устройства для цифрового фазового детектирования импульсных последовательностей на неравных частотах

Формулаизобретения

Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах, содержащее накопительный регистр, информационный вход которого является первым информаци- онным входом устройства для цифрового фазового детектирования импульсных последовательностей на неравных частотах, первый YK-триггер и последовательно сое- диненные цифроаналоговый преобразова- тель и фильтр нижних частот, выход которого является выходом устройства для цифрового фазового детектирования импульсных гюследовательностей на неравных частотах, отличающееся тем, что, с целью расширения диапазона рабочих частот, в него введены двоичный счетчик, информационный вход которого является вторым информационным входом устройства для цифрового фазового детектирования импульсных последовательностей на неравных частотах, статический регистр, вклюа

5 В г 3 е ж

u(i)

ченный между разрядными выходами двоичного счетчика и информационными входами цифроэналогового преобразователя, второй YK-триггер, элемент И и элемент ИЛИ-НЕ, включенные последовательно между прямым выходом первого YK-тригге- ра и входом записи двоичного счетчика, при этом прямой выход первого YK-триггера подключен к другому входу элемента ИЛИ- НЕ, инверсный выход - к К-входу второго YK-триггера, прямой выход которого соединен с К-входом первого YK-триггера и тактовым входом накопительного регистра, а инверсный выход - с Y-входом и инверсным R-входом первого YK-триггера, выход переполнения накопительного регистра подключен к другому входу элемента И, выход переноса двоичного счетчика - к входу синхронизации первого YK-триггера, а счетный вход двоичного счетчика объединен с входом синхронизации второго YK-триггера и является первым тактовым входом устройства для цифрового фазового детектирования импульсных последовательностей на неравных частотах, вторым тактовым входом которого является вход записи статического регистра

| Фазовый дискриминатор | 1982 |

|

SU1095349A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для цифрового фазового детектирования импульсных последовательностей на неравных частотах | 1981 |

|

SU1109872A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

Авторы

Даты

1992-08-15—Публикация

1990-09-10—Подача