чисел соединены с выходом счетчика эталонных чисел, а выходы - с входами третьей и четвертой групп ключей, выход второго регистра периода соединен с входом первого дешифратора, вьгходом соединенного с входом первого генератора опорных импульсов, первый вход блока управления соединен с вторым выходом блока вычитания, второй вход - с выходом первого компаратора кодов, третий вход - с выходом второго компаратора кодов, четвертый вход - с третьим входом устройства, пятый вход - с четвертым входом устройства, шестой входс пятым входом устройства, первый выход - с управляющими входами tiepBoго регистра периода и первого регистра чисел, второй выход -.с управляющими входами второго регистра периода и второго регистра числа, третий выход - с управляющим входом блока вычитания и первым входом счетчика эталонных чисел, четвертый выход - с вторым входом элемента ИЖ, пятый выход - с управляющими входами буферного регистра и регистра длительности, шестой выход - с управляющим входом регистра остатка, седьмой выход - с первым входом блока ввода и управляющими входами первой и четвертой групп ключей, восьмой выход - с вторым входом блока ввода и управляющими входами второй и третьей групп ключей, девятый . выход - с вторым выходом устройства и вторым входом формирователя входного сигнала, десятый выход - с .вторым входомсчетчика эталонных чисел, одиннадцатый выход - с входом установки регистра остатка в исходное состояние, установочный выход с установочными входами регистров длительности, чисел, периода, буферного регистра, блока вычитания и счетчиков импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматической фокусировки телевизионной камеры | 1984 |

|

SU1246412A1 |

| Устройство для формирования отрезка прямой линии на экране электронно-лучевой трубки | 1979 |

|

SU919163A1 |

| АНАЛОГО-ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1997 |

|

RU2123720C1 |

| Вероятностный преобразователь аналог-код | 1986 |

|

SU1363461A1 |

| Информационное устройство | 1987 |

|

SU1564066A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| Цифровой синтезатор речи | 1981 |

|

SU974404A1 |

| Способ измерения амплитудных значений электрических сигналов | 1986 |

|

SU1509751A1 |

| Система управления вибростендом | 1985 |

|

SU1305649A1 |

| Устройство для извлечения квадратного корня из напряжения | 1989 |

|

SU1721615A1 |

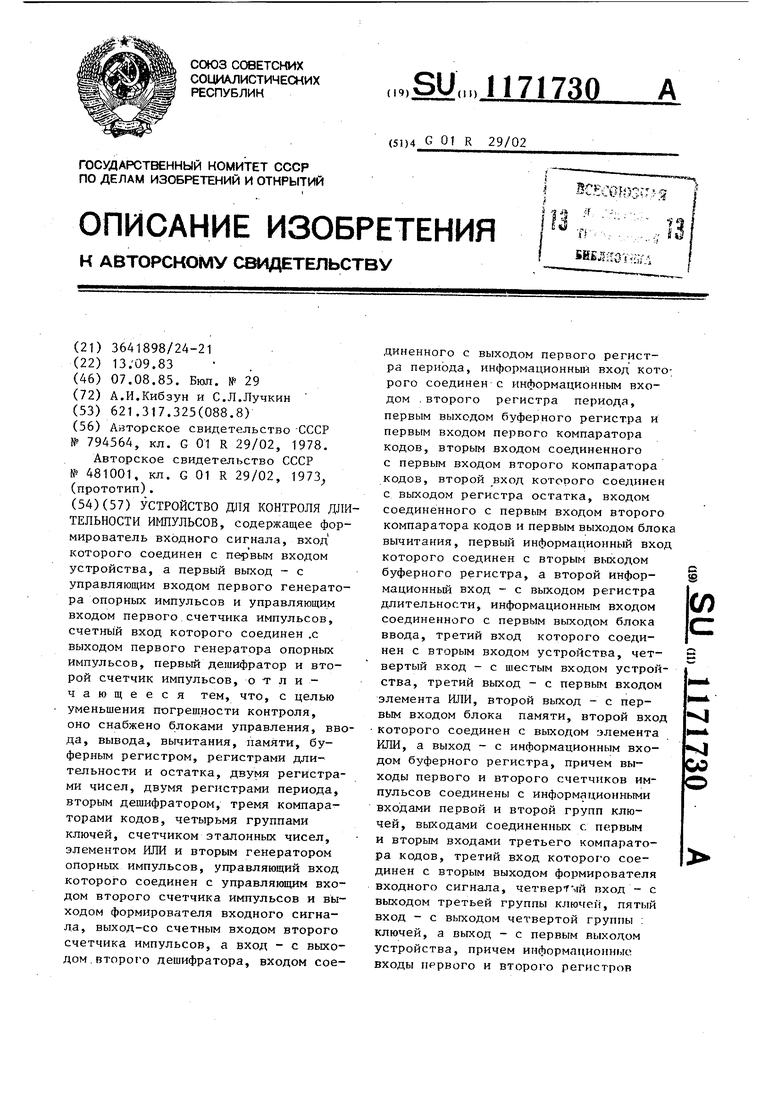

УСТРОЙСТВО ДНЯ КОНТРОЛЯ ДЛИТЕЛЬНОСТИ ИМПУЛЬСОВ, содержащее формирователь входного сигнала, вход которого соединен с первым входом устройства, а первый выход - с управляющим входом первого генератора опорных импульсов и управляющим входом первого счетчика импульсов, счетный вход которого соединен ,с выходом первого генератора опорных импульсов, первый дешифратор и второй счетчик импульсов, отличающееся тем, что, с целью уменьшения погрешности контроля, оно снабжено блоками управления, ввода, вывода, вычитания, памяти, буферным регистром, регистрами длительности и остатка, двумя регистрами чисел, двумя регистрами периода, вторым дешифратором, тремя компараторами кодов, четырьмя группами ключей, счетчиком эталонных чисел, элементом ИЛИ и вторым генератором опорных импульсов, управляющий вход которого соединен с управляющим входом второго счетчика импульсов и выходом формирователя входного сигнала, выход-СО счетным входом второго счетчика импульсов, а вход - с выходом, второго дешифратора, входом соединенного с выходом первого регистра периода, информационный вход которого соединен с информационным входом .второго регистра периода, первым выходом буферного регистра и первым входом первого компаратора кодов, вторым входом соединенного с первым входом второго компаратора кодов, второй вход которого соединен с выходом регистра остатка, входом соединенного с первым входом второго компаратора кодов и первым выходом блока вычитания, первый информационный вход которого соединен с вторым выходом буферного регистра, а второй инфорS мационный вход - с выходом регистра (Л длительности, информационным входом соединенного с первым выходом блока ввода, третий вход которого соединен с вторым входом устройства, четвертый вход - с шестым входом устройства, третий выход - с первым входом элемента ИЛИ, второй выход - с первым входом блока памяти, второй вход которого соединен с выходом элемента sj ШШ, а выход - с информационным вхоСО дом буферного регистра, причем выходы первого и второго счетчиков импульсов соединены с информационными входами первой и второй групп ключей, выходами соединенных с первым и вторым входами третьего компаратора кодов, третий вход которого соединен с вторым выходом формирователя входного сигнала, четвер-Г-. пход - с выходом третьей группы ключей, вход - с выходом четвертой группы : ключей, а выход - с первым выходом устройства, причем информационнью входы первого и второго регистров

1

Изобретение относится к электроизмерительной технике и может быть использовано в системах контроля параметров иэменяющихся во времени сигналов.

Целью изобретения является умень шеиие погрешности контроля. .

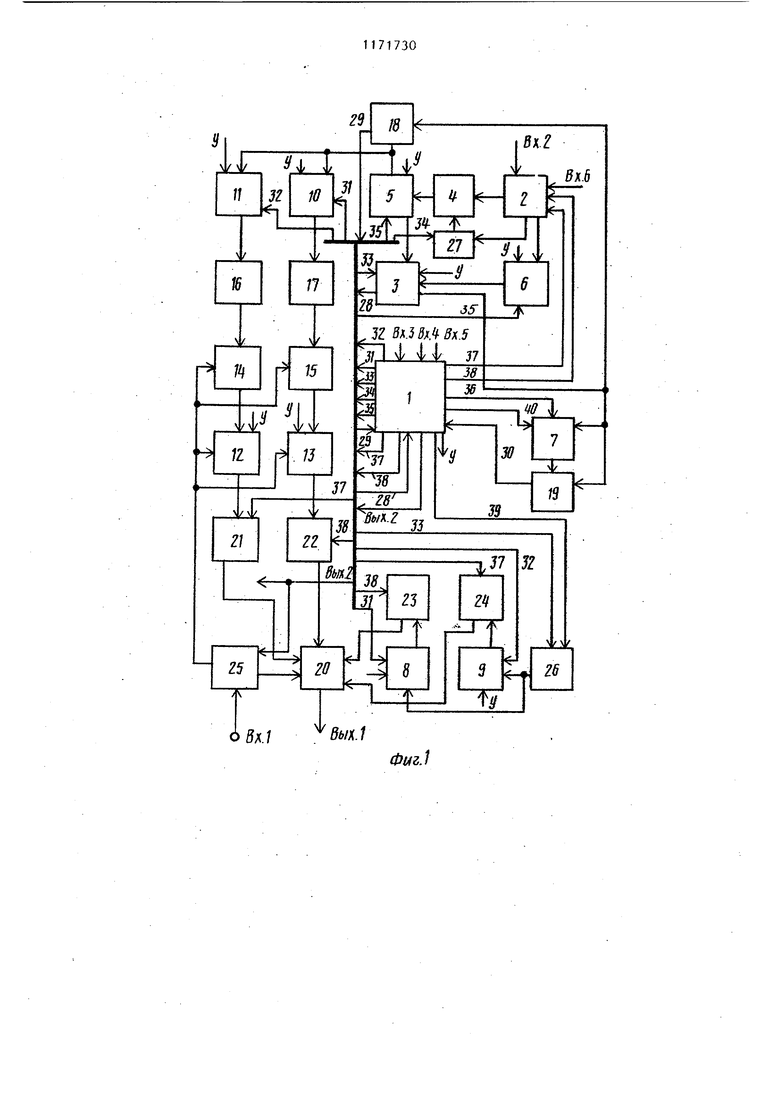

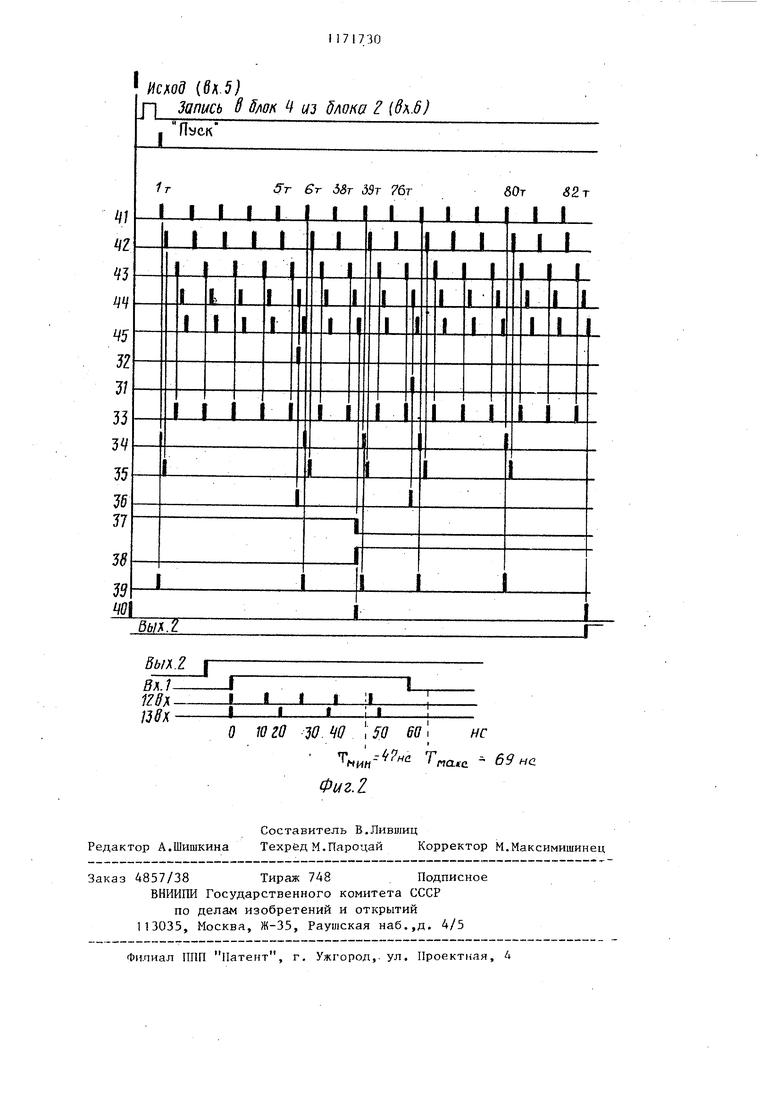

На фиг.1 изображена структурная электрическая схема предлагаемого устройства на фиг.2 - временные. диаграммы.

Устройство состоит из блока 1 управления, блока 2 ввода, блока 3 вычитания, блока 4 памяти, буферног регистра 5, регистра 6 длительности регистра 7- остатка, первого и второго регистров 8 и 9 чисел, первого и второго регистров 10 и 11 периода, первого и второго счетчика 12 и 13 импульсов, первого и второго генера торов 14 и 15 опорных импульсов, первого и второго дешифраторов 16 и 17, первого, второго и третьего компараторов 18-20 кодов, первой, второй, третьей и четвертой групп21-24 ключей, формирователя 25

входного сигнала, счетчика 26 эталонных чисел и элемента ИЛИ 27,

Вход формирователя 25 входного сигнала соединен с первым входом устройства, а первый выход - с управляющим входом первого генератора 14 опорных импульсов и управляющим входом первого счетчика 12 импульсов счетный вход которого соединен с выходом первого генератора 14 опорных импульсов. Управляющий вход второго генератора 15 опорных импульсов соединен с управляющим вхрдом. второго счетчика 13 импульсов и выходом формирователя 25 входного сигнала, выход - со счетньм входом второго счетчика 13 импульсов, а вход - с выходом второго дешифратора 17, входом соединенного с выходом первого, регистра 10 периода. Информационный вход регистра 10 периода соединен с информационным входом второго регистра 11 периода, первым выходом буферного регистра 5 и первым входом первого компаратора 18 кодов, вторым входом соединенного с первым

входом второго компаратора 19 кодов, второй вход которого соединен с выходом регистра 7 остатка, входом соединенного с первым входом второго компаратора 19 кодов и первым вькодо блока 3 вычитания. Первый информационный вход блока 3 вычитания соединен с вторым выходом буферного регистра 5, а второй информационный вход - с выходом регистра 6 длительности, информационным входом соединенного с первым выходом блока 2 ввода, третий вход которого соединен с вторым входом устройства, четверты вход - с шестым входом устройства, . третий выход - с первым входом элемента ИЛИ 27, второй выход - с первы входом блока 4 памяти, второй вход которого соединен с выходом элемента ИЛИ 27, а выход - с информационным входом буферного регистра 5. Причем выходы первого и второго счетчиков 12 и 13 импульсов соединены с информационными входами первой и второй групп 21 и 22 ключей, выходами. соединенных с первым и вторым входами третьего компаратора 20 кодов, третий вход которого соединен с вторым выходом формирователя 25 входного сигнала, четвертьй вход - с вы- ходом третьей группы 23 ключей, пятый вход - с выходом четвертой группы 24 ключей, а выход - с первым выходом устройства. Информационные входы первого и второго регистров 8 и 9 чисел соединены с выходом счетчика 26 эталонных чисел, а вько- ды - с входами третьей и четвертой групп 23 и 24 ключей. Выход второго регистра 11 периода соединен с входом первого дешифратора 16, выходом соединенного с входом первого генератора 14 опорных импульсов. Первый вход блока 1 управления соединен шиной 28 с вторым выходом блока 3 вычитания, второй вход шиной 29 - с выходо первого компаратора 18 кодов, третий вход шиной 30 - с выходом в торсго компаратора 19 кодов, четвертый вход - с третьим входом устройства, пятый вход - с четвертым входом устройства, шестой вход - с пятым входом устройства, первый выход шиной

31- с управляющими входами первого регистра 10 периода и первого регистра 8 числа, второй выход шиной

32- с управляющими входами второго регистра 11 периода и второго ре-

гистра 9 числа, третий выход шиной 33 - с управляющим входом блока 3 вычитания и первым входом счетчика -26 эталонных чисел, четвертый выход шиной 34 - с вторым входом элемента 27 ИЛИ, пятый выход шиной 35 - с управляющими входами буферного регистра 5 и регистра 6 длительности, шестой выход шиной 36 - с з равляющим входом регистра 7 остатка, седьмой вь1ход шиной 37 - с первым входом блока 2 ввода и управляющими входами первой и четвертой групп 21 и 24 ключей, восьмой выход шиной 38 - с вторым входом бдока 2 ввода и управляющими входами второй и третьей групп 22 и 23 ключей, девятый выход - с вторым выходом устройства и вторым входом формирователя 25 входного сигнала, десятьй выход шиной 39 - с вторьм входом счетчика 26 эталонных чисел, одиннадцатый выход шиной 40 - с входом установки регистра 7 остатка в исходное состояние, установочный выход - с установочными входами регистров 6-11 длительности, чисел, периода, буферн го регистра 5 блока 3 вычитания и счетчиков 12 и 13 импульсов,

Устройство работает следующим образом.

На шестой вход блока 1 управления подается сигнал установки в ис-; ходное состояние. На выходе блока 1 вырабатывается команда У установки триггеров, счетчиков, регистров в исходное состояние.

В исходном состоянии счетчик 12 устанавливается за один дискрет до переполнения,

В регистр 7 записывают максимально возможное число. Остальные эле-менты устанавливаются в нулевое состояние.

На пятый вход блока 1 управления подается команда режима, В режиме В, когда, например, заданы-максимальная уставка длительности Т 69 не

МО КС

и минимальная уставка длительности Т 47 НС, с 1 по 38 такты блоком Т на шину 37 выдается сигнал, поступающий затем на первый вхо блока ,2, Затем по команде, подаваемой на четвертый вход блока 2, в блок 4 памяти вводятся поступающие на третий вход блока 2 исходные данные, которые представляют собой коды длительности периодов импульсов Т, Т;, которые могут .вырабатывать генераторы 14 и 15, Через блок 2 в .регистр 6 по команде на шине 37 заносится пре дельно допускаемое значение длительности контролируемого импульса Количество значений Т -«ми звачення зависят от диап конкретные зона, в котором предполагается проводить контроль,.и допускаемой погрешности Ь Контроля Пусть, например, устройство пред назначено для контроля импульсов, граничные значения Т , которых могут находиться в диапазоне 10100 НС, а погрешность не должна превышать 3 не. Задаются набором из 10-19 НС с десяти периодов Т дискретностью 1 не и подбираю.т такие значения для каждого заданного q.c i Д™ каждого Т, ко торые бы обеспечили минимальную воз можную погрешность контроля второго вВДа или , где 10 1(1) Г . ИО м«н- 1 Тмо,кс1 мин (2) in j npw , мин - - 7 для каждого заданного значения с, такое целое число эталонных импульсов и с таким перио дом следования, произведение которых (Т; N) имело бы минимальное от личие от Т . причем не превьшало бы его. Аналогично для Т..,.., находятс , гЛИН такие N; и Tj из одного и того же набора периодов, чтобы (Т- N ) лучшим образом приближалось к Т оставаясь больше его, По сигналу Пуск, подаваемому на четвертый вход блока t управления, устройство подготавливаётс51 к контролю. Блок 1 вьщает по шине 39 сигнал по которому счетчик 26 устанавливается в .нуль. По шине 34 блок 1 уста навливает адрес ячейки блока 4, в которую записан код первого значения Т,.., 10 НС, адрес устанавливаетс с начала такта 1 до начала такта 6, По шине 34 блок 1 также воздействует через элемент ИЛИ 27 на втор вход блока 4 и подготавливает его к чтению. Блок t вырабатывает тактовый импульс 41 и синхроимпульсы 4 44, По синхроимпульсу 42 на шину 32 вьщается команда чтения, по которой из блока 4 в регистр 5 записывается первое значение периода Т- 10 не, а из регистра 6 в блок 3 вычнтания записывается значение уставки Т 47 НС, ,.... По синхроимпульсу 43 блок 1 вьщает на шину 33 сигнал, поступающий на управляющий вход блока 3, в котором оеущеетвляется операция вычитания , 47-10 37, (Число Т; записывается в дополнительном коде и операция вычитания заменяется равнозначной операцией сложения), Синхроимпульс 43 поступает также на счетньй вход счетчика 26 по шине 33 и записывает в него 1, Выход блока 3 вычитания соединен с входами компараторов 18 и 19 и регистра 7 остатка. Компаратор 18 с;равнивает содержимое блока 3 и регистра 5, где хранитея значение периода Tj, и выдает сигнал на шину 29, как только содержимое блока 3 станет меньше содержимого регистра 5 - сигнал разрешения перезаписи в.регистр 5 следующе-, го значения ,компаратор 19 сравнивает содержимое блока 3 и регистра 7 остатка и вьщает сигнал на разре- . Мение перезаписи из блока 3 остатка в регистр 7, В первом такте сигнала на выходе компаратора 18 нет, так как содержимое блока 3 больше Т (), на выходе компаратора 19 сигнал также отеутетвует, так как 37 5 (число 5 записано по команде у в регистр 7), После второго такта в блоке 3 останется число 27 (37-10), В третьем и четвертом тактах -элементы продолжают работать также, как во втором. После прохождения синхроимпульса 43 в пятом такте в блоке 3 окажется число - 3(47-5-10), которое по модулю меньше Т, (3-110), а также меньше числа 5, записанного по команде У в регистр 7, Поэтому на выходах компараторов 18 и 19 появляются сигналы, вьщаваемые на шины 29 и 30, По. приходу синхроимпульса 44 в пятом такте блок 1 вьщает сигнал на шину 36, который . управляет записью в регистр 7 остатка из блока 3, а также при наличии сигнала на тине 29 (признак режима В) на шину 32 вьщается команда, которая поступает на управление регист71рами 9 и 11. При этом в регистр 9 из счетчика 26 переписывается число периодов Т(, которое уложилось (с перекрытием в данном случае) в интервале T..UU НС. В регистр 11 заносится текущее значение периода Т, 10 НС из регистра 5. По синхроимпульсу 45 в пятом так те команды не вырабатываются. В шестом такте блок 1 вырабатывает импульс,.который по шине 39 поступает на счетчик 26 и устанавливает его в О. По синхроимпульсу 42 в шестом такте из второй ячейки блока 4 памяти по команде на шине 35 в регистр 5 записывается новое значение Tj 11 НС (старое Т 10 не стирается) , из регистра 6 в блок 3 по команде с шины 35 заносится снова НС и снова происходит в течение пяти тактов вычитание из содержи мого блока 3 периода Т2 11 не, пока в блоке 3 не окажется отрицательный остаток 8, Но так как по модулю содержимое блока 3 больше числа 3 , записанного в регистр 7, то компаратор 19 не выдает разрешающий сигнал на шину .30, а следовательно, в данном такте сигналы на шинах 36 и 32 не сформируются и содержимое регистров 7, 9 и 11 не изменится. . Таким образом, в течение 38 тактов перебираются все десять значений Т от .10 до 19 НС, причем в регистрах 9, 7 и 11 смена информации происходит (за исключением первого такта, когда обязательно заносятся результаты вычитания, значение остатка, J эталонное число N, н значение периода Т,) только при условии, что содер жимое блока 3 отрицательно и по абсо лютной ве.личине меньше числа, находящегося в данном такте после синхро импульса 43 в регистре 7. После перебора всех значений Tjno . отношению к регистре 9 оказывается число N. ,,4. Причем код Т Ti з писан в регистре 11. В регистре 7 ок зывается число 3, которое подтвержда ет,что погрешность не превышает 3 не. После перебора всех десяти значений Т блок 1 вьщает сигналы на шины 38 и 40, по которым устройство переходи в режим подготовки к контролю относи тельно Т , а регистр 7 устанавливается в исходное состояние. Одновреме но с поступлением по шине 38 сигнала на вход блока 2 сигнал на шине 39 ус 0,8 танавливает счетчик 26 чисел в О, а адрес на шине 34 принимает следующее значение. По синхроимпульсу 42 в 39-м такте выдается на шину 35 сигнал записи из блока 4 памяти в регистры 5 и 6 соответственно чисел Т, 10 и T a|jf69 не, По синхроимпульсу 43 в блоке 3 происходит вычитание (Т,, ). По синхроимпульсам 44, 45 в 39-м такте сигналы не формируются. Аналогично протекает процесс в 40-43 тактах. В 44-м такте после синхроимпульса 43 (вычитание) в блоке 3 окажется число 9 Т,10 (69-6-10) и компаратор 18 выдает сигнал на шину 29. В 45-м такте в регистр 5 записывается число 11, из регистра 6 в блок 3 число 69. В 45-50 тактах число 11 последовательно вычитается из содержимого блока 3. В 50-м такте после синхроимпульса 43 в блоке 3 оказывается число и 3 11 (69-6-11). По командам компараторов 18 и 19 блок 1 выдает команды на шины 36 и 31, в регистр 7 переписывается число 3, в регистр 10 - число 11, в регистр 8 - число 6. I До 76-го такта содержимое этих регистров не изменяется, так как содержимое блока 3, будучи меньше чисе.л 12, 13, 14, 15, 16, записываемых в регистр 5, все же будет превьш1ать число 3 в регистре 7. В 76-м такте после вычитания из содержимого блока 3 числа T-., там останется число I ; 3 и 1 17, поэтому в регистры 7, 10 и 8 запишутся соответственно числа 1, 17 и 4, которые и останутся там до конца режима подготовки по 82 тактам. В 82-м такте режим подготовки заканчивается. По синхроимпульсу 44 выра-. батьшается сигнал на девятом выходе блока 1, который сигнализируется об окончании режима подготовки. Устройство переходит в режим ожидания измерения. При этом в регистре 11 записано число 12, в регистре 9 число 4, в регистре 8 - также 4, в регистре 10 - число 17. На вход формирователя 25 с-девятого выхода блока 1 поступ ает сигнал разрешения. Сигнал с выходов регистров 10 и 11 воздецствует на дешифраторы 16 и 17, которые задают необходимую длительность периодов импульсов генераторов. В рассматриваемом случае генератор 14 подготавлива9ется к работе с длительностью перио да .12 НС, а генератор 15 17 не. С приходом контролируемого импульса на первый вход формирователя 25, последний по переднему фронту импульса запускает генераторы 14 и 15 и открывает счетные входы счет чиков 12 и 13. Выходные сигналы счетчиков/через группы ключей 21 и 22 поступают на первый и второй входы компаратора 20, который выпол нен двухканальным. На третий и четвертьй входы компаратора 2Q поступают сигналы с выходов регистров 8 и 9 через группы ключей 23 и 24, управляемые сигнала признака режима, поступающими с блока управления по шинам 37, 38. Счетные импульсы для счетчиков 12 и 13 (12 вх 13 вх. на фиг.2) формирзпотсй по началу периода. По зйднему фронту контролируемого импульса входы счет чиков 12 и 13 блокируются, генераторы 14 и 15 выключаются и на компаратор 20 подается сигнал вьщачи результата контроля. Результаты контроля формируются по следующим правилам (относительно допустимости погрешности второго вида): для режима А если Ц $ Т - Годен, Брак, переходе к состоянию устройства N Годен, Брак (N - соде жимое счетчика 13 после заднего фро та контролируемого импульса, N - с держимое регистра 8 после окончания режима подготовки, t - длительност контролируемого импульса); для режима Б, если t 9 ден, t,( Брак, или х Кэ Годен, - Брак (NJ - соде жимое счетчика 12 после заднего фро та контролируемого импульса, Ng - с 010 держимое регистра 9 после окончания режима подготовки) -, для режима В, если t. Годен, Т.. х wate t т t- ж J- kAHU J -Jt N;6Nx Ng, то сигнал Годен , , то сигнал Брак. Для рассматриваемого примера: 47 $69 НС - Годен, при этом . находится в норме, наЕСЛИ t, пример НС, на счетчик 12 поступает пять импульсов, но так как он был установлен в состояние максимального значения, первый счетный импульс вызывает его переполнение и устанавливает в состояние О, затем идет счет импульсов. В момент не входы счетчиков 12 и 13 закрываются, в данном случае в обоих счетчиках будет число 4, условие (3) соблюдается, компаратор 20 вырабатывает сигнал Годен, который поступает на Вьк.1. Если t 47,9 НС, то на счетчик 12 поступает четыре импульса, а записывается число 3, что отвечает условию (4), компаратор. 20 вырабатывает сигнал Брак. При этом между уставкой T..,. не и действительным значением t, соответствующим норме, но забракованным устройствам, имеется разность Д -0,9 не - методическая погрешность, присущая устройству. Будет забракован, и ,9 не, хотя на самом деле находится в норме, и здесь имеет место погрешность +0,9 НС.

| Устройство для контролядлиТЕльНОСТи иМпульСОВ | 1978 |

|

SU794564A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой измеритель длительности импульсов | 1973 |

|

SU481001A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-08-07—Публикация

1983-09-13—Подача