Изобретение относится к технике электрических измерений и может быть использовано при,построении приборов для измере11ия-.а&е9лютных отклонений частоты от. .ромина ьного значения, для измерения скафсов частоты, джиттера и скачквв Для слежения за периодом сигналов, для непрерывно. го измерения,интервалов времени. I Целью изобретения является расширение функциональных возможностей измерителя за счет непрерывного слежёния за.длительностью каждого периода .

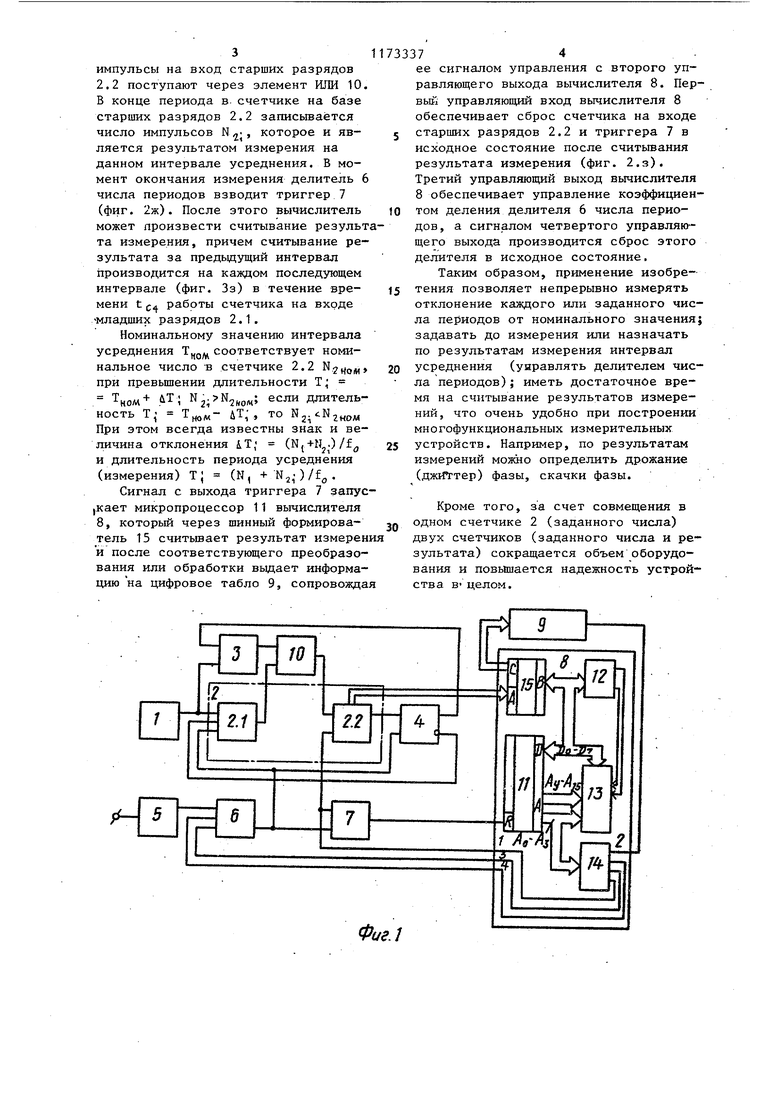

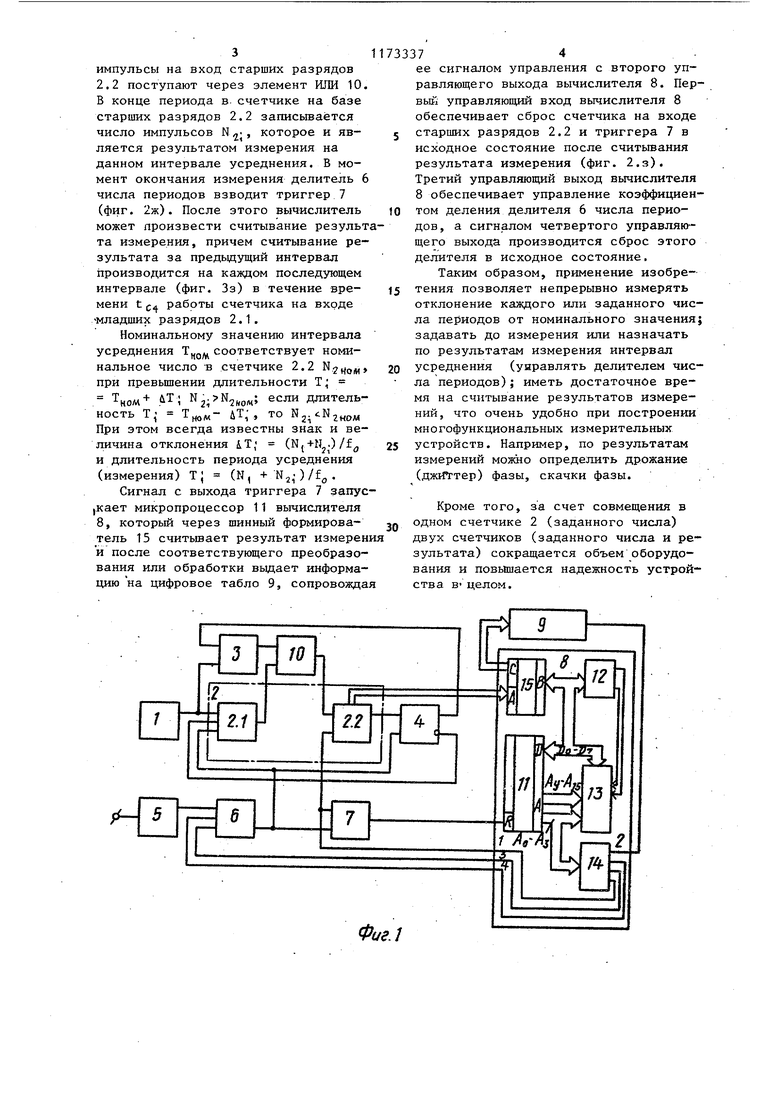

На фиг. 1 представлена схема устройства; на фиг.2 - временные диаграммы работы устройства.

Устройство содержит генератор 1 квантующих импульсов, счетчик 2, содержащий младшие 2.1 и старшие 2.2 разряды, элемент 3 совпадения, первый управляющий триггер 4, входной формирователь 5, делитель 6 числа периодов, второй управляющий триггер 7, вычислитель 8,, цифровое табло 9 и элемент ИЛИ 10,

Вычислитель 8 содержит микропроцессор 11,, регистр 12 управления, запоминающее устройство 13, формирователь 14 управляющих сигналов и шинньш формирователь 15.

В Устройстве для измерения периода сигналов (фиг.1) генератор 1 квантующих импульсов подключен к первому входу элемента 3 совпадения и к счетному входу счетчика 2, запрещающий вход и выход переноса которохо соединены соответственно с нулевым выходом и единичным входом первого управляющего триггера 4, входной формирователь 5 подключен через делитель 6 числа периодов к единичному входу второго управляющего триггера 7, первый вход элемента ИЛИ 10 подключен к выходу элемента совпадения 3, а второй вход и выход соединены соответственно с выходом младших разрядов 2.1 счетчика 2 и входом его старших разрядов 2.2, единичный выход первого управляющего триггера 4 соединен с вторым входом элемента 3 совпадения, а нулевой вход объединен со сбросовым входом младших разрядов 2.1 счетчика 2 и подключен к единичному входу второго управляюБ его триггера 7, нулевой вход и единичньй выход которого соединены соответственно с первым управляющим выходом и входом вычислителя 8, второй, третий и четвертый управляющие выходы которого подключены соответственно к управляющему входу цифрового табло 9, сбросовому и управляющему входам делителя 6 числа периодов, информационньй выход к цифровому табло 9, а информационные входы - к выходам старших разрядов 2.2 счетчика 2, сбросовый вход которых соединен с нулевым входом второго управляющего триггера 7.

Выч,ислитель 8 выполнен по традиционной схеме микроэвм на микропроцессоре. Микропроцессор 11 по шине данных соединен с запоминающим устройством 13, регистром 12 управления и шинным формирователем 15, вход которого подключен к выходу старших разрядов 2.2 счётчика 2, а выход к входу цифрового табло 9, по шине адреса - с запоминающим устройством 13 и формирователем 14 управляющих сигналов, по входу - с единичным выходом второго управляющего триггера 7, выходы регистра 12 управления подключены к управляющим входам запоминающего устройства 13, а выходы формирователя 14 управляюыщх сигналов явл5потся первым четвертым управляющими выходами вычислителя 8.

Работа устройства поясняется временными диаграммами на фиг.2. Входной сигнал (фиг.2а), подлежащий измерению, проходит через входной формирователь 5, которью выделяет нульпереходы на каждом периоде сигнала (фиг. 26). Если необходимо измерить длительность каждого периода, то этот сигнал является выходом делителя 6 числа периодов, который регулярно производит сброс младших разрядов 2.1 счетчика 2. Если же в делителе 6 записано заданное число периодов К, то сигнал на фиг.2 б это выход делителя. I

После сброса счетчик 2 ведет подсчет числа квантующих импульсов от генератора 1, пока не подсчитает число импульсов, равное N , (N,) мл K(N) ст (фиг. 2 в,г). После этого с выхода триггера 4 разрешающий потенциал подается на вход элемента 3 совпадения, а запрещающий (фиг.2 д на соответствующий вход счетчика 2 (младшие разряды 2.1). Начинается подсчет числа квантующих импульсов старшими разрядами счетчика 2 (фиг.2 На первом и втором проходах счетные 3 импульсы на вход старших разрядов 2.2 поступают через элемент ИЛИ 10, В конце периода в счетчике на базе старших разрядов 2.2 записьгоаётся число импульсов N j, которое и является результатом измерения на данном интервале усреднения. В момент окончания измерения делитель 6 числа периодов взводит триггер 7 (фиг. 2ж). После этого вычислитель может произвести считывание результ та измерения, причем считывание результата за предыдущий интервал производится на каждом последующем интервале (фиг. Зз) в течение времени t с работы счетчика на входе младших разрядов 2.1. Номинальному значению интервала усреднения соответствует номинальное число в счетчике 2.2 N.JQ, при превьш1ении длительности Т Т„ом+ .,,,,,«; если длительком- ДТ;, то Nj. ность т, При этом всегда известны знак и величина отклонения iX,- ( и длительность периода усреднения (измерения) Т; (N, + Nj O/foСигнал с выхода триггера 7 запу ,кает микропроцессор 11 вычислителя 8, который через шинный формирователь 15 считьшает результат измере и после соответствующего преобразо вания или обработки вьщает информа цию на цифровое табло 9, сопровожд 7 ее сигналом управления с второго управляющего выхода вычислителя 8. Первый управляющий вход вычислителя 8 обеспечивает сброс счетчика на входе старших разрядов 2.2 и триггера 7 в исходное состояние после считьгеания результата измерения (фиг. 2.з). Третий управляющий выход вычислителя 8 обеспечивает управление коэффициентом деления делителя 6 числа периодов, а сигналом четвертого управляющего выхода производится сброс этого делителя в исходное состояние. Таким образом, применение изобретения позволяет непрерывно измерять отклонение каждого или заданного числа периодов от номинального значения; задавать до измерения или назначать по результатам измерения интервал усреднения (унравлять делителем числа периодов); иметь достаточное время на считывание результатов измерений, что очень удобно при построении многофункциональных измерительных устройств. Например, по результатам измерений можно определить дрожание () фазы, скачки фазы. Кроме того, за счет совмещения в одном счетчике 2 (заданного числа) двух счетчиков (заданного числа и результата) сокращается объем оборудования и повышается надежность устройства в-целом.

f

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой фазометр | 1988 |

|

SU1638654A1 |

| Цифровой фазометр | 1986 |

|

SU1323979A1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012130C1 |

| Аналого-цифровой преобразователь с частотным преобразованием | 1990 |

|

SU1725396A1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С ПРОМЕЖУТОЧНЫМ ПРЕОБРАЗОВАНИЕМ В ЧАСТОТУ | 1990 |

|

RU2007029C1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1388989A2 |

| Многоканальный аналого-цифровой преобразователь | 1980 |

|

SU993468A1 |

| МНОГОКАНАЛЬНЫЙ ИНФРАНИЖОЧАСТОТНЫЙ ЦИФРОВШ КОРРЕЛЯТОР | 1972 |

|

SU433486A1 |

| Устройство для измерения динамическихХАРАКТЕРиСТиК АНАлОгО-цифРОВыХ пРЕОбРАзО-ВАТЕлЕй | 1979 |

|

SU815897A1 |

УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПЕРИОДА СИГНАЛОВ, содержащее генератор квантующих 11мпульсов, подключенный к первому входу элемента совпадейия и к счетному входу счетчика, запрещающий вход и выход переноса которого соединены соответственно с нулевым выходом и единичным входом первого управляющего триггера, входной формирователь, подключенный через делитель числа периодов к единичному входу второго управляющего триггера и цифровое табло, отличающееся тем, что, с целью расширения функциональных возможностей, в него введены вычислитель и элемент ИЛИ, первый вход которого подключен к выходу элемента совпадения, а второй вход и выход соединены соответственно с выходом младших разрядов счетчика и входом его старших разрядов, единичный выход первого управляющего триггера соединен с вторым входом элемента совпадения, а нулевой вход объединен со сбросовым входом младших разрядов счетчика и подключен к единичному входу второго управляющего триггера, нулевой вход и единичный выход которого соединены соответственно с первым управляющим выходом и входом вычислителя, второй, третий и четвертый-управляющие выходы которого подключены соответственно к управляющему входу цифрового табло, сбросовому и управляющему входам делителя числа периодов, информационный выход - к цифровому табло, а информационные входы - к выходам старших разрядов счетчика, сбросовый вход которых соединен с нулевым входом второго управляющего триггера. СО СлЭ 00

| Устройство для измерения отклонениячАСТОТы OT НОМиНАльНОгО зНАчЕНия | 1978 |

|

SU834567A1 |

| Устройство для измерения абсолютно-гО ОТКлОНЕНия чАСТОТы | 1978 |

|

SU817599A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-08-15—Публикация

1983-04-20—Подача