Изобретение относится к вычислительной технике и предназначено для использования в быстродействующих цифровых устройствах, функционирующих в непозиционных системах счисления и реализующих различные немодульные операции.

Целью изобретения является расширение области применения за счет выполнения операции масштабирования в модулярном коде.

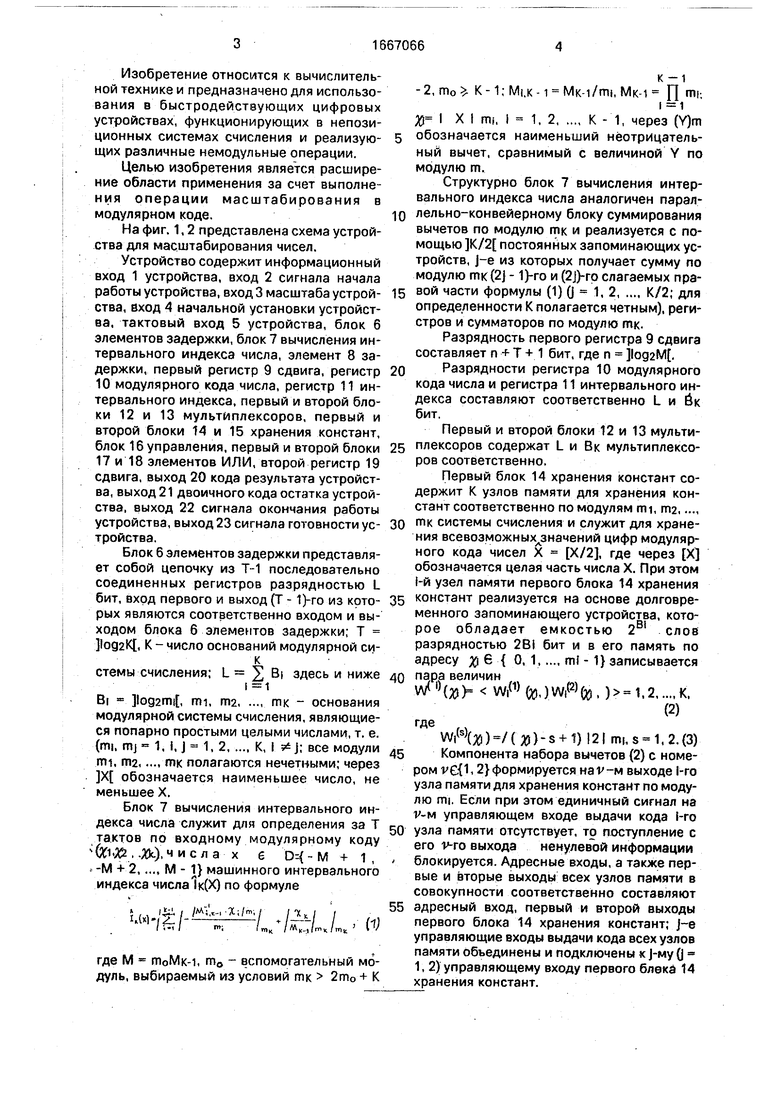

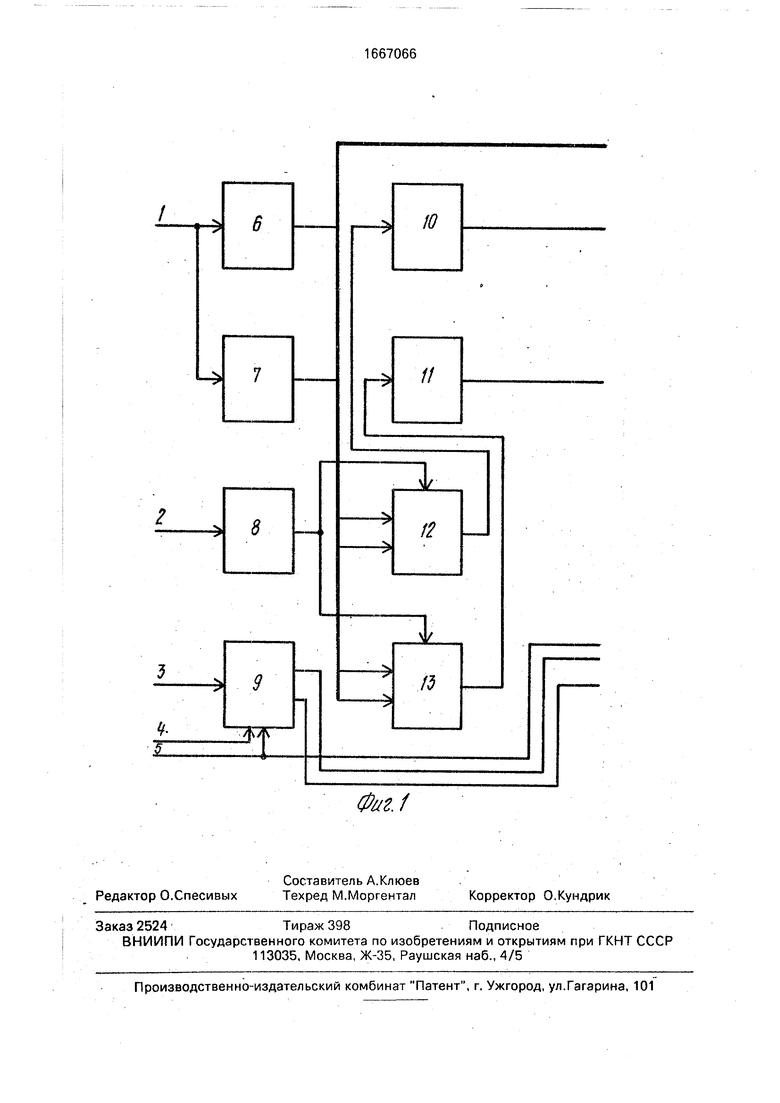

На фиг. 1,2 представлена схема устройства для масштабирования чисел.

Устройство содержит информационный вход 1 устройства, вход 2 сигнала начала работы устройства, вход 3 масштаба устройства, вход 4 начальной установки устройства, тактовый вход 5 устройства, блок 6 элементов задержки, блок 7 вычисления интервального индекса числа, элемент 8 задержки, первый регистр 9 сдвига, регистр 10 модулярного кода числа, регистр 11 интервального индекса, первый и второй блоки 12 и 13 мультиплексоров, первый и второй блоки 14 и 15 хранения констант, блок 16 управления, первый и второй блоки 17 и 18 элементов ИЛИ, второй регистр 19 сдвига, выход 20 кода результата устройства, выход 21 двоичного кода остатка устройства, выход 22 сигнала окончания работы устройства, выход 23 сигнала готовности устройства.

Блок 6 элементов задержки представляет собой цепочку из Т-1 последовательно соединенных регистров разрядностью L бит, вход первого и выход (Т - 1)-го из которых являются соответственно входом и выходом блока 6 элементов задержки; Т log2Kl. К - число оснований модулярной сик

стемы счисления; L Г В| здесь и ниже

i 1

Bi - log2Tii, mi, ma тк - основания

модулярной системы счисления, являющиеся попарно простыми целыми числами, т. е.

(mi, mj 1, I, j 1, 2 К, I J; все модули

mi, ГП2тк полагаются нечетными; через

Х обозначается наименьшее число, не меньшее X.

Блок 7 вычисления интервального индекса числа служит для определения за Т тактов по входному модулярному коду ч(#.# ...). ч и с л а х & D--{ - М + 1 , -М + 2, .... М - 1} машинного интервального индекса числа к(Х) по формуле

wfel- UZLL-to

где М - тоМк-1. т0 - вспомогательный модуль, выбираемый из условий тк 2т0 + К

к - 1 -2, т0 К-1; М|,к-1 Мк-1/mi, М«-1 П т .

l 1 й I X I mi, I 1. 2 К - 1, через (Y)m

обозначается наименьший неотрицательный вычет, сравнимый с величиной Y по модулю т.

Структурно блок 7 вычисления интервального индекса числа аналогичен параллельно-конвейерному блоку суммирования вычетов по модулю тк и реализуется с помощью К/2 постоянных запоминающих устройств, J-e из которых получает сумму по модулю тк (2J - 1)-го и (2j)-ro слагаемых правой части формулы (1) 0 1.2К/2; для

определенности К полагается четным), регистров и сумматоров по модулю тк.

Разрядность первого регистра 9 сдвига составляет п + Т + 1 бит, где n log2M.

Разрядности регистра 10 модулярного кода числа и регистра 11 интервального индекса составляют соответственно L и Вк бит.

Первый и второй блоки 12 и 13 мультиплексоров содержат L и Вк мультиплексоров соответственно.

Первый блок 14 хранения констант содержит К узлов памяти для хранения констант соответственно по модулям mi, 012

тк системы счисления и служит для хранения всевозможныхлзначений цифр модулярного кода чисел X Х/2, где через X обозначается целая часть числа X. При этом 1-й узел памяти первого блока 14 хранения

констант реализуется на основе долговременного запоминающего устройства, которое обладает емкостью 2 слов разрядностью 2BI бит и в его память по адресу #6 { 0. 1mi - 1} записывается

пара величин

( Wi(1)fo,)Wi%,)

1,2К,

(2)

где

Wi(s)(;0)/(;0)-s + 1)|2lmi..2.(3) Компонента набора вычетов (2) с номером vC{1.2} формируется Hav-м выходе 1-го узла памяти для хранения констант по модулю mi. Если при этом единичный сигнал на v-м управляющем входе выдачи кода 1-го узла памяти отсутствует, то поступление с его v-ro выхода ненулевой информации блокируется. Адресные входы, а также первые и вторые выходы всех узлов памяти в совокупности соответственно составляют адресный вход, первый и второй выходы первого блока 14 хранения констант; j-e управляющие входы выдачи кода всех узлов памяти объединены и подключены к j-му ( 1, 2) управляющему входу первого блока 14 хранения констант.

Второй блок 15 хранения констант служит для хранения значений нтервально индексной характеристики к(Х), где X Х/2,

X (#i , $№) произвольный элемент

рабочего диапазона D. Второй блок 15 хранения констант реализуется на основе дол- современного запоминающего устройства, обладающего емкостью 2В слов разрядностью р . Вк бит (р К + q, q К/2 + 1),.в

память которого по адресу fe{0, 1тк - 1}

записывается набор вычетов

) Л/к(1)(1), WK(2)(I)WK(p)(l) ,(4)

где

«l/m,, при t-1 ц I mK-m0-k«.Z /Л1-т)/г -4М/т« при и I ь mK-m0-k 2,1C

/(l-.I(,npM i H«-p,

и I ™«-™„ - + 2 ,(5)

()-MK)/2-t+ + t/ro«,npH t -(-H - р rr)K-m0-k«2

1(1) - интервальный индекс числа Г. Компонента набора вычетов (4) с номером v формируется на v -м выходе второго блока 15 хранения констант (Vfi{1, 2,..., р}). Если при этом единичный сигнал на v -м управляющем входе выдаче кода второго блока 15 хранения констант отсутствует, то поступление с его выхода ненулевой информации блокируется.

Блок 16управления реализован аналогично узлу анализа прототипа и по интервально-лзрду-

лярному коду (# , #%«. - 2 , 1 1к(Х))

числа XЈD вырабатывает требуемую последовательность управляющих сигналов. На выходах блока 16 управления с первого по (Р + 2)-й ежетактно генерируются соответственно буле- вы величины W, Ч, ai 02ор , определяемые соотношениями

Ч

Ы„

--U 5-1

5 }

Сч

ч/flt при t d 4- с{, -} у Si при -t q-H р

где

VI. -2(t I) и t-1-q, иди ec/uZlifj «-Й:« г(-,,1)иКа4,Ар

I 1l«1

(8)

о в остальных случаях (50

при этом 4J (л . к - 1 fc . J 1, 2К-1;

(X)/2. й.к-1 и mj. fl.-POmj. 1(Х) - интервальный индекс числа X, определяемый соотношением

f лл

Кх)Л еслм к)гпк-т0-к+г, (1кОО- гпк если IK(x); mK-m0 + K-2;

55

5

10

1C

20 25 30

35

40

45

50

55

7Vj+Wj(2, если (UjiK, четно ч /ф. + со j/ , если (U j, K-, .нечетно

j 1,2К-1; //j. Vilmj;

если 1 (1) четно, у V если 1 (1) нечетно,

а р.если дз. .

О, в противном случае;

,2k-1.

через X обозначается отрицание булевой величины X.

Первый блок 17 элементов ИЛИ содержит L двухвходовых элементов ИЛИ.

Второй блок 18 элементов ИЛИ содержит Вк р-входовых элементов ИЛИ.

Разрядность второго регистра 19 сдвига составляет п+1 бит.

Рассмотрим, как работает устройство для масштабирования чисел. По сигналу Густ 1, подаваемому с входа 4 устройства, первый регистр 9 сдвига обнуляется, тем самым устройство приводится в исходное рабочее состояние

В целях формирования управляющих сигналов на сигнальных выходах 22 и 23 устройства содержимое первого регистра 9 сдвига ежетактно сдвигается в сторону младших разрядов по сигналу Гт 1, подаваемому с тактового входа 5 устройства. При инициации в устройстве очередной операции содержимое первого регистра 9 сдвига логически складывается с подаваемым на его информационный вход двоичным кодом числа 2 + с входа 3 масштаба устройства, где I - номер требуемого масштаба, SI 21 (I

1,2 п + 1). В результате (Т + I - 1)-й

разряд первого регистра 9 сдвига устанавливается в единичное состояние.

На первом такте операции масштабирования модулярной код (#1 , xz .. , %к ) масштабируемого числа X с информационного входа 1 устройства передается в блок 6 элементов задержки, а также поступает в блок 7 вычисления интервального индекса числа, где в ходе очередных Т тактов, считая текущий, в соответствии с форм.(1) вычисляется машинный интервальный индекс к(Х) числа. Кроме этого, на первом такте управляющий сигнал Г- 1, подаваемый с входа 2 устройства, поступает в элемент 8 задержки.

На Т-м такте сигнал Г- 1 с выхода элемента 8 задержки подается на управляющие входы первого и второго блоков 12 и 13 мультиплексоров, поэтому появляющиеся в данном такте на выходах блока 6 элементов задержки и блока 7 вычисления интервального индекса числа модулярный код

(# , #№ ) и характеристика7к(Х) через

вторые информационные входы первого и второго блоков 12 и 13 мультиплексоров соответственно поступают в регистр 10 модулярного кода числа и регистр 11 интервального индекса.

На каждом из I последующих тактов операции масштабирования выполняются одни и те же действия. В ходе (Т + г + 1)-го такта (г 0,1I - 1)блок 16 управления по

модулярному коду (xv ,;pr юР и

машинному интервальному индексу 1к(Хг) числа Хг (при г 0 полагается Х0 X и

#° % , ,2К), подаваемым на его

первый и второй входы с выходов регистров 10 и 11 модулярного кода числа и интервального индекса соответственно, вырабатывает

сигналы КГ), ). Oir) ,...o$ off), определяемые соотношениями вида (6) - (8). Признаки ) и четности числа Хг с первого и второго выходов блока 16 управления подаются соответственно на первый и второй управляющие входы выдачи кода первого блока 14 хранения констант, на адресный вход которого из регистра 10 модулярного кода числа поступают цифры кода

(№,№(Р).Сигналы

от ,ojr ,..., с последних р выходов блока 16 управления подаются на соответствующие управляющие входы выдачи кода второго блока 15 хранения констант, а на его адресный вход из регистра 11 интервального индекса поступает интервально- индексная характеристика к(Хг). Если Хг

четно С W 1 и 0), то на первом выходе первого блока 14 хранения констант сформируется модулярный код

tf + 1,jЈ+1tf+1) w(l)(),wЈ1)

(#))wP(;JP) числа Xr+i - Xr/2

. (см. (2), (3)), а на втором выходе - кохЦО 0

0). Если же Хг является нечетным (Ч /г) О, Ч /г) 1), то код нуля формируется на первом выходе первого блока 14 хранения констант, а код числа Хг-м. совпадающий в данном случае с кодом ()(#r)) , Wi2

(jЈ) )W0 (г))Хсм.(2),(3))-навтором

выходе. В обоих случаях на выхбде первого блока 17 элементов ИЛИ будет получен модулярныйкод(г + 1).г + 1))) числа Хги. который через первый информационный вход первого блока 12 мультиплексоров, на управляющий вход которого подается сигнал Г 0, пересылается в регистр 10 модулярного кода числа. Что

касается сигналов оу , огг (J$ ,то как

видно из (7) и (8), лишь один из них принимает единичное значение. Пусть этот сигнал имеет номер v Тогда на выходах второго блока 15 хранения контакт формируется набор величин 0, 0О, N (к(Хг)), 00

-я из которых представляет собой машинный интервальный индекс числа Хг-н, т. е.

W)(K(Xr))K(Xi+i)(cM. (4), (5), при I 1к/Хг)). Характеристика 1к(Хг+1), пройдя через второй блок 1Й элементов ИЛИ и второй блок

5 13 мультиплексоров, поступает в регистр 11 интервального индекса.

Ежетактно содержимое второго регистра 19 сдвига по сигналу Гт 1, подаваемому с тактового входа 5 устройства, сдвигается

0 на один бит в сторону младших разрядов, после чего в его старший разряд записывается признак четности W/, генерируемый на втором выходе блока 16 управления. В

ц результате по окончании (Т + г + 1)-го такта операции в г+ 1 старших разрядах второго регистра 19 сдвига будет получен двоичный код величины

Rr + i t ччо-2 .

0i 0

представляющий собой остаток I X I 2г-н от

деления X на 2

Согласно изложенному по истечении (Т+

+ 2)-го такта на выходе первого блока 17 5 элементов ИЛИ сформируется модулярный

код ($. $ до ) искомого целочисленного приближения Х| Х/2 к дроби Х/2 , а в I старших разрядах второго регистра 19 сдвига - двоичный код остатка RI Х 21; при этом на выходе младшего разряда первого регистра 9 сдвига, а значит и на выходе 22 устройства появляется единичный сигнал, указывающий на то, что процесс масштабирования завершен.

Инициация новой операции в устройстве может быть осуществлена уже на 1-м такте текущей операции. Признаком готовности устройства к выполнению опе- р. рации служит единичный сигнал, генерируемый на выходе (Т+1)-го разряда первого регистра 9 сдвига, а соответственно и на выходе 23 устройства.

0

5

Формула изобретения

Устройство для масштабирования чисел, содержащее первый и второй регистры сдвига, регистр модулярного кода числа, регистр интервального индекса, первый и второй блоки хранения констант, первый и второй блоки мультиплексоров, блок управления, первый и второй блоки элементов ИЛИ, причем вход масштаба устройства и вход начальной установки устройства соединены соответственно с информационным входом и входом сброса первого регистра сдвига, вход разрешения сдвига которого соединен с тактовым входом устройства и с входом разрешения сдвига второго регистра сдви- га, выход которого является выходом двоичного кода остатка устройства, выход первого блока мультиплексоров соединен с входом регистра модулярного кода числа, выход которого соединен с адресным вхо- дом первого блока хранения констант и с первым входом блока управления, первый и второй выходы которого соединены с соответствующими входами разрешения выдачи первого блока хранения констант, первый и второй выходы которого соединены с соответствующими входами первого блока элементов ИЛИ. выход которого является выходом кода результата устройства, выход сигнала окончания работы которого соеди- нен с выходом первого разряда первого регистра сдвига, выход второго блока мультиплексоров соединен с входом регистра интервального индекса, выход которого соединен с адресным входом второго блока хранения констант и с вторым входом блока

управления, второй выход которого соединен с информационным входом второго регистра сдвига. 1-й вход разрешения выдачи и 1-й выход второго блока хранения констант ( + q + 1:K- количество оснований; q - целая часть числа К/2) соединены соответственно с (I + 2)-м выходом блока управления и с 1-м входом второго блока элементов ИЛИ, выходы первого и второго блоков элементов ИЛИ соединены с первыми информационными входами первого и второго блоков мультиплексоров соответственно, отличающееся тем, что, с целью расширения области применения за счет выполнения операции масштабирования в модулярном коде, оно содержит блок элементов задержки, блок вычисления интервального индекса числа и элемент задержки, причем информационный вход устройства соединен с входами блока элементов задержки и блока вычисления интервального индекса числа, выходы которых соединены соответственно с вторыми информационными входами первого и второго блоков мультиплексоров, управляющие входы которых соединены с выходом элемента задержки, вход которого соединен с входом сигнала начала работы устройства, выход сигнала готовности которого соединен с выходом ( Iog2« + 1)-го разряда первого регистра сдвига.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления экспоненциальной функции в модулярной системе счисления | 1985 |

|

SU1317433A1 |

| Устройство для вычисления квадратного корня числа в модулярной системе счисления | 1985 |

|

SU1317434A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1986 |

|

SU1411742A1 |

| Арифметическое устройство в модулярной системе счисления | 1987 |

|

SU1432517A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1368878A1 |

| Устройство для умножения чисел | 1986 |

|

SU1325475A1 |

| Устройство для сложения чисел в модулярной системе счисления | 1986 |

|

SU1322278A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1352483A1 |

| Устройство для умножения комплексных чисел в модулярном коде | 1985 |

|

SU1330631A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1989 |

|

SU1667065A1 |

Изобретение относится к вычислительной технике и предназначено для использования в быстродействующих цифровых устройствах, функционирующих в непозиционных системах счисления и реализующих различные немодульные операции, такие как деление, умножение дробей, масштабирование, перевод чисел в двоичную систему счисления. Целью изобретения является расширение области применения за счет выполнения операции масштабирования в модулярном коде. Устройство содержит блок элементов задержки, блок вычисления интервального индекса числа, элемент задержки, первый и второй регистры сдвига, регистр модулярного кода числа, регистр интервального индекса, первый и второй блоки мультиплексоров, первый и второй блоки хранения констант, блок управления, первый и второй блоки элементов ИЛИ со связями. 1 ил.

| Устройство для преобразования непозиционного кода в позиционный код | 1987 |

|

SU1510097A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для масштабирования числа в интервально-модулярном коде | 1986 |

|

SU1305678A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-30—Публикация

1989-09-28—Подача