и шестые входы первых четырех се лекторов соединены с входом первой группы входов данных, первые входы второй и третьей групп вхо--дов данных которого соединены соответственно с вторыми и четвертыми входами первых четырех селекторов соответственно, выход первого селек тора подключен к первому и пятому входам пятого селектора, выход которого соединен с первым и пятым входами шестого селектора, выход седьмого селектора соединен с третьим и шестым уходами шестого селектора, выход второго селектора подключен к третьему и шестому входам пятого селектора выход третьего селектора подключен к первому и пятому входам седьмого селектора, выход четвертот-о селектора подключен к третьему и шестому входам седьмого селектора, второй и третий входы второй группы входов данных узла подключены к вторым входам пятого и седьмого селекторов и второму входу шестогб селектора соот ветственно, второй и третий входы третьей группы входов данных узла подключены к четвертым входам пятого и седьмого селекторов и четвертому входу шестого селектора соответственно, выходы всех селекторов являют ся группой выходов результата узла расчета функций, а узел коррекции содержит мультиплексор и два элемен- та 2И-ИЛИ, выходы которых являются выходами узла коррекции, первый и второй информационные входы которого подключены к первому и второму прямым и инверсным входам мультиплексора соответственно, вход разрешения которого является входом разрешения узла, а первый и второй выходы подключены к первым входам первого и второго элементов 2И-ИЛИ, вторые и третьи входы которых подключены к группе входов сигналов инвертирования узла, причем блок управления кор рекцией содержит узел инвертирования узел преобразования сигналов запрета селектор, элемент И и два мульти- плексора, выходы которых подключены к группе выходов сигнала инвертирования блока, узел инвертирования содержит три элемента И, элемент ИЛИ, два элемента сложения по модулю два и селектор, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом первого элементами, первый вход которого соединен с первым входом первого элемента сложения по модулю два, первым входом второго элемента И, первым и четвертым входами селектора, первым и четвертым входами селектора блока управления коррекцией и первым входом элемента И, первым входом группы входов задания функции блока, второй вход группы входов задания функции, которого соединен с вторым и пятым входами селектора блока, вторым входом второго элемента И, первым входо второго элемента сложения по модулю два, вторым входом второго элемента сложения по модулю два, первым входо третьего элемента И и вторым входом элемента И блока, третий вход группы входов задания функции блока управления коррекцией соединен с третьим входом селектора и третьим и шестым входами селектора блока,управления коррекцией, вторыми входами элементов сложения по модулю два и третьим входом элемента И, выход которого соединен с входом управления первого мультиплексора, выходы первого и второго элементов сложения по модулю два соединены с вторым входом третьего.и вторым входом первого элементов И соответственно, выходы первого, второго, третьего элементов-И и эле- мента ШМ узла инвертирования являются группой выходов разрешения блока управления коррекцией, а узел пре .образования сигналов запрета содержит шесть элементов И и коммутатор, первый, второй, третий и четвертый прямые информационные входы которого подключены к второму, первому, четвертому и третьему входам группы входов управления расчетом функций блока управления коррекцией и к первому, второму входам первого и второго элементов И соответственно,первый, второй, третий и четвертый инверсные информационные входы коммутатора подключены к первому входу группы входов управления расчетом функций блока, выходу первого элемента И, третьему входу группы входов управления расчетом функций , блока и выходу второго элемента И соответственно, выходы первого и второго элементов И соединены с вто)ммк входами третьего и пятого элементов И соответственно, пятый вход группы входов управления расчетом функции

блока соединен с первыми входами элементов И и с третьего по шестой с уп равляющим входом коммутатора, вторые входы четвертого и шестого элементов И подключены к первому и третьему инверсным входам коммутатора, первый выход которого подключен к группе выходов разрешения блока и к информационным третьим входам первого и второго мультиплексоров блока управ ления, коррекцией, первые информационные входы которых подключены к выходу третьего элемента И, выход четвертого элемента И подключен к группе выходов разрешения блока управления коррекцией и к пятым информационным входам первого и второго мультиплексоров блока управления коррекцией,вторые информационные входы которых со117

18

единены с выходом пятого элемента И, выход шестого элемента И соединен с шестыми информационными входами пер вого и второго мультиплексоров блока управления коррекцией, четвертые информационные входы которых соединены с третьим выходом коммутатора уэла преобразования сигналов запрета, второй выход которого соединен с группой выходов разрешения блока управления коррекцией и с седьмыми информационными входами первого и второго мультиплексоров блока управления коррек,цией, восьмые информационные входы ко торых соединены с четвертым выходом коммутатора узла преобразования сигналов запрета, управляющий вход второго мультиплексора подключен к выходу элемента И блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический модуль | 1987 |

|

SU1425649A1 |

| Многофункциональный логический модуль | 1983 |

|

SU1164693A1 |

| Генератор систем функций Аристова | 1989 |

|

SU1746373A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| РАСШИРИТЕЛЬ ИНТЕРФЕЙСА "КАНАЛ ОБЩЕГО ПОЛЬЗОВАНИЯ" | 2009 |

|

RU2402805C1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

| Система коммутации | 1986 |

|

SU1403071A1 |

| Система коммутации | 1986 |

|

SU1410047A1 |

| Устройство для передачи информации в системе телесигнализации | 1987 |

|

SU1509968A1 |

| Генератор согласованных систем базисных функций Аристова | 1989 |

|

SU1746374A1 |

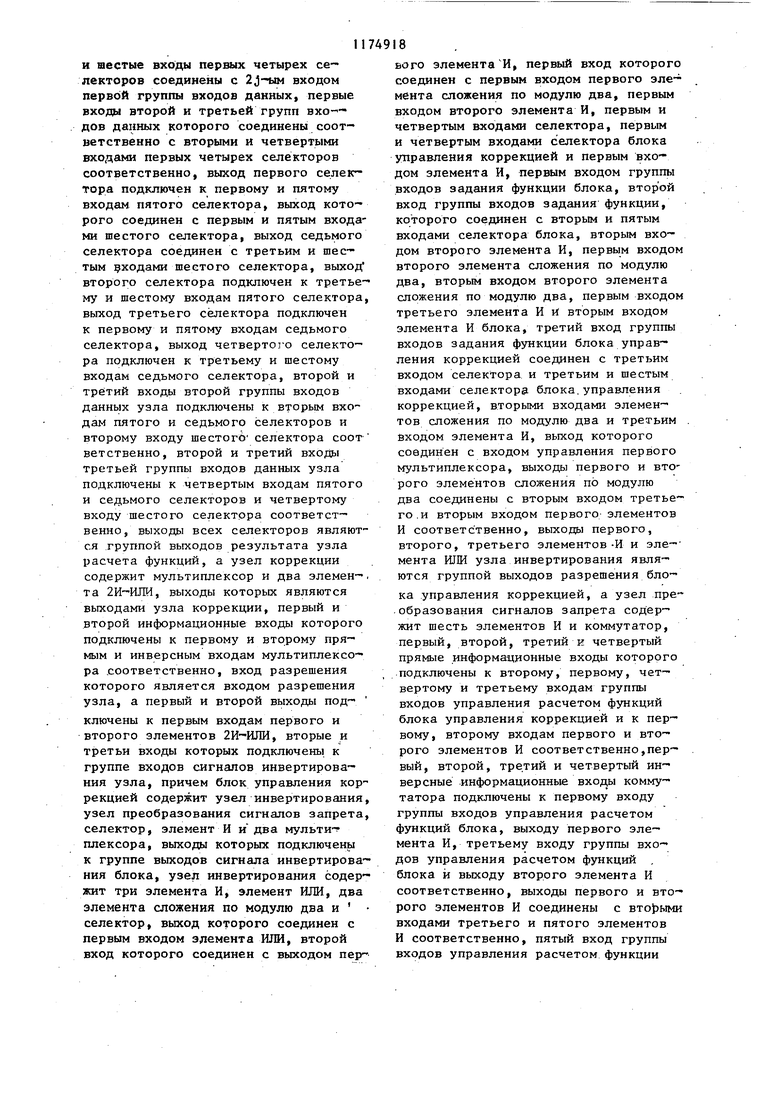

МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ, содержащий первый коммутатор данных, первый и .второй информационные входы которого являются группой информационных входов модуля, выход коммутатора подключен к первому входу данных узла расчета функций, группа выходов результата которого соединена с группой информационных входов мультиплексора, группа выходов которого подключена к группе информационных входов первого регистра, отлич ающийся тем, что, с цепью повышения производительности, модуль дополнительно содержит, второй коммутатор данных, .второй и третий регистры, элемент задержки, узел маскирования, узлы коррекции и блок уггравления коррекцией, группа входов управления расчетом функций и группа входов заданий функции которого соеди иены с группой выходов второго регист ра, вход синхронизации которого является синхровходом модуля, группа входов управления расчетом функции и группа входов задания функции которого подключены к информационных входов второго регистра, группа ад«ресных входов модуля соединена с информационным входом второго коммутатора, вход запуска модуля соединен с управляющим входом первого и второго коммутаторов данных, входом разрешения записи первого регистра и через элемент задержки - с входом разрешения записи третьего регистра, группа информационных входов которого объеди нена с группой информационныз входов первого регистра, синхровход которого соединен с синхровходом третьего регистра, с синхровходом модуля и синхровходом узла маскирования, группа входов которого подключена к группе входов задания функции блока управления коррекцией, группа выходов разре- § шения которого подключена к входам разрешения узлов коррекции соответст(Л венно , первый и второй информационные входы каждого i-ro узла коррекции (,..., 4) соединены с выходами разрядов первого и третьего регистров соответственно, выходы узлов коррекции являются первой группой выходов модуля, выход узла маскирования ляется второй группой выходов модуля, и со группа выходов сигналов инвертирования блока управления коррекцией под-, ключена к группе входов инвертирова00 ния каждого узла коррекции, группа управляющих входов мультиплексора подключена к группе, входов задания функции модуля, группы прямых и ин- ве;рсных выходов второго коммутатора данных подключены к второй и третьей группам входов данных узла расчета . функций соответственно, причем узел расчета функций содержит семь селекторов, первые и пятые входы nej)вых четырех селекторов соединены с

1

Изобретение относится .к области вычислительной техники и может быть использовано в качестве специализированного вычислительного устройства в системах автоматического проектиро-.5 вания логических объектов при проверке правильности схем логических объектов в процессе их разработки и при построении проверяемых тестов.

Целью изобретения является повы- 10 шение производительности модуля.

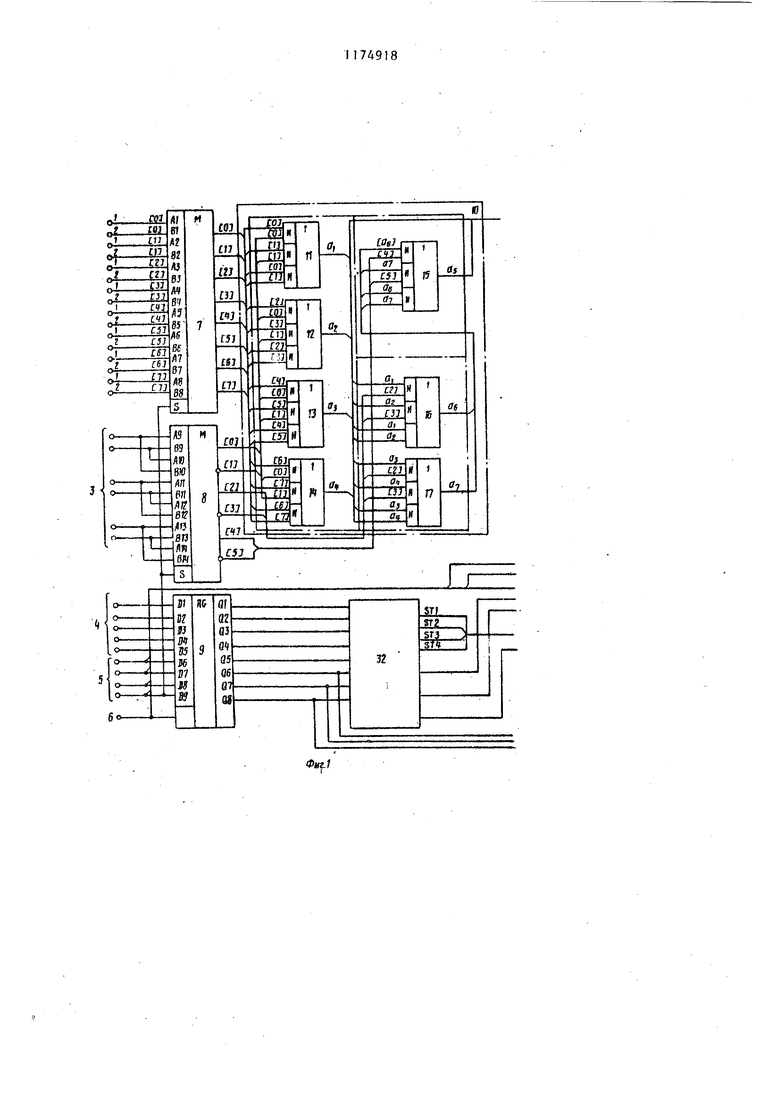

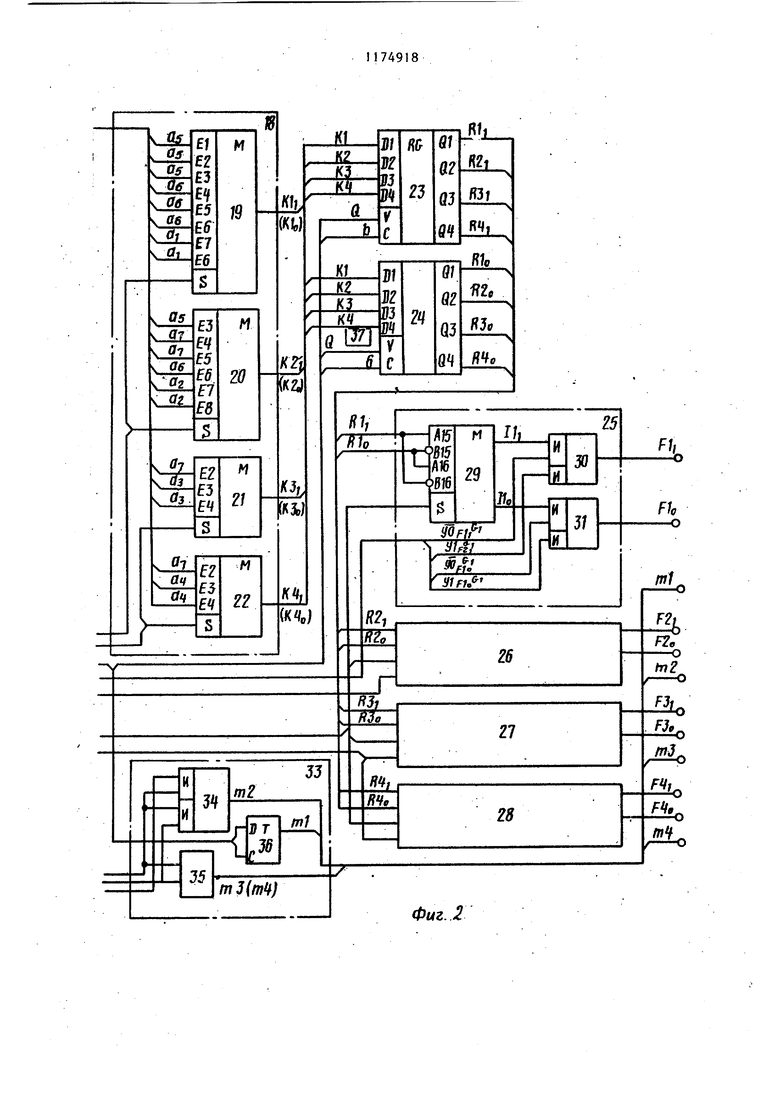

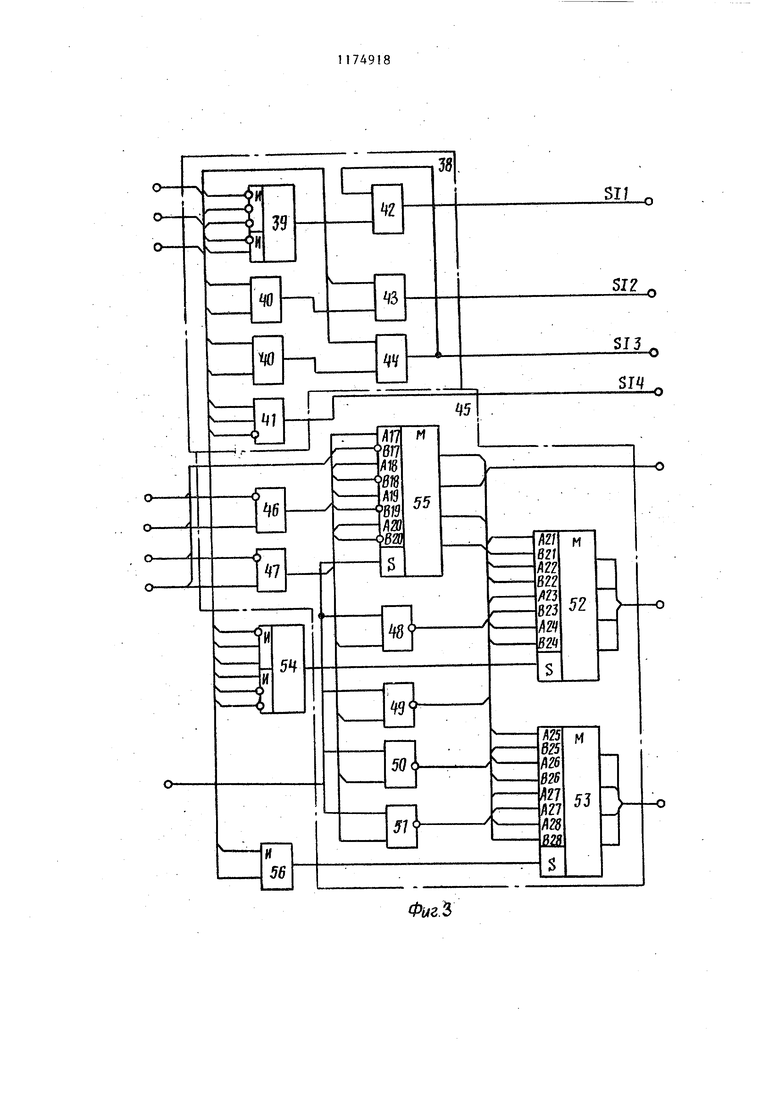

На фиг,1 и 2 изображена функциональная схема модуля; на фиг.З - схема блока управления коррекцией; на фиг,4 - временные диаграммы работы -15 модуля.

Модуль содержит группу информационных входов 1 модуля, группу адресных входов 2 модуля, группу входов 3 управления расчетом функции, 20 группу входов 4 задания функции, вход 5 запуска модуля, вход 6 синхронизации, первый и второй коммутаторы 7 и 8, регистр 9, узел 10 расчета функций, содержаший сеяектд- 25 ры 11-17, мультиплексор 18, содержащий мультиплексоры 19-22, регистры 23 и 24, узлы 25-28 коррекции, каж.дый из которых содержит мультиплексор 29, элементы И-ИЛИ 30 и 31, блок 32 управления коррекцией, узел 33

маскирования, содержащий элемент И-ИЛИ 34, элемент ИЛИ 35, триггер 36 а также элемент 37 задержки, В состав блока управления коррекцией входят узел 38 управления инвертирования, содержащий элемент И-ИЛИ 39, схемы 40 сложения по модулю два, элемент И 41, элемент ИЛИ 42, элементы И 43 и 44, а также узел 45 преобразования сигналов запрета, содержащий элементы И 46-51, мультиплексоры 52 и 53, селектор 54, мультиплексор 55 и элемент И 56,

Предлагаемое устройство предназначено для расчета выходных состояний интегральных схем (ИС) как с npse мыми, так и с инверсными выходами, выполняющих функции мультиплексоров из двух каналов в один, из четырех каналов в один и из восьми каналов в один и имеющих входы запрета, которые позволяют организовать в логических узлах, построенных на этих схемах, объединение выходов ИС,

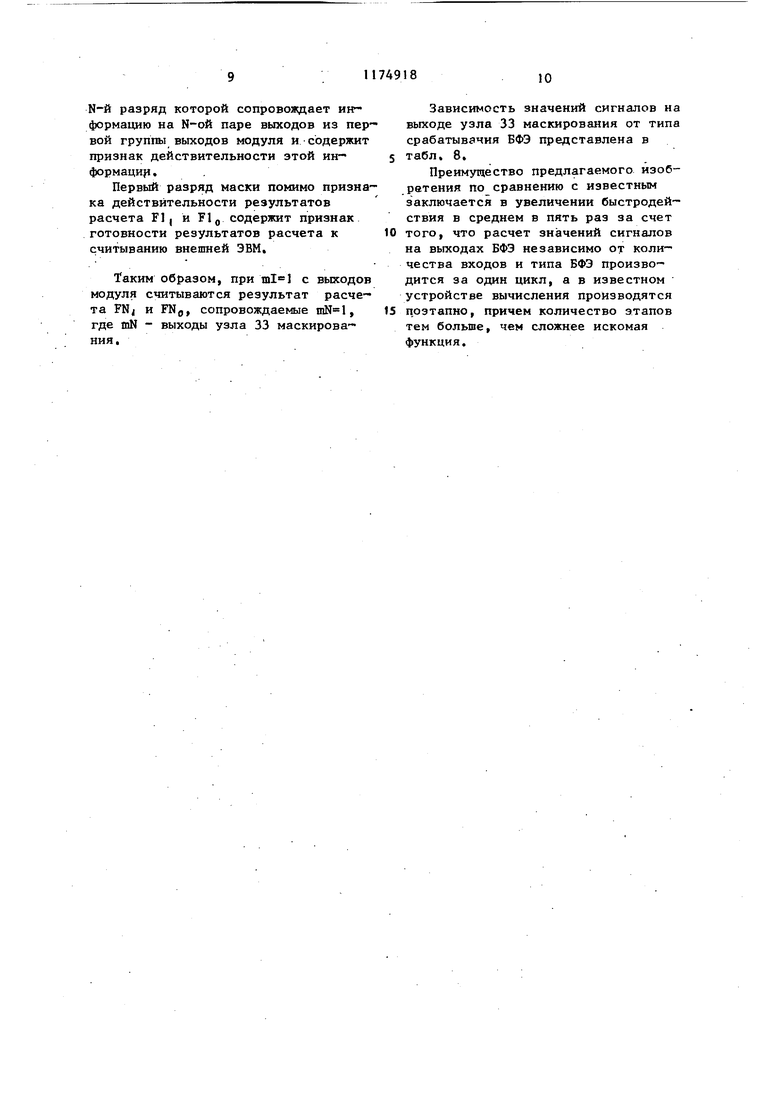

При подготовке к расчету в модуле ИС описываются в виде базовых функциональных элементов (БФЭ). Каждому типу БФЭ присвоен четырехразрядный двоичный номер -машинный номер (МН.), Разряды МН обозначаются ТО, Т1, Т2 и ТЗ, Соответствие МН БФЭ

31

типу его функционирования, т.е. ло-гическим функциям, вырабатываемым на выходах БФЭ, представлено в табл.К

Логические функции FN, где 1 N64 реализуемые БФЭ, в основном точно соответствуют логическим функциям мультиплексирующих ИС серий 100 и 533 с числом выходов . Разрядом ТО закодирован способ воздействия сигналов запрета на мультиплексорНые функции, вырабатываемые БФЭ, например, логический О в разряде ТО МН расчитываемого БФЭ означает, что при наличии сигнала запрета, равно OV

го логическому U, выходам логиБФЭ, БФЭ в МН

ческой 1 на выходах которого , обозначаются МПБФЭО и представляют ИС серии 100; логив разряде ТО МН рассчи- ческая тываемого БФЭ означает, что при наличии сигнала запрета, равного логической 1, выходам модуля присваив ются значения, соответствующие состоянию Z (высокоимпедансное состояние) на выходах БФЭ,БФЭ в МН которого , обозначаются МПБФЭ1 и представляют ИС серии 533, Расчет в модуле одного БФЭ производится по алгоритму Подача сигналов на входы модуля функций мультиплексоров, реализуемых данным БФЭ бе.з учета инверсии Учет инверсии этих функций Коррекция результатов расчета с учетом сигналов запрета Так как действие .сигналов запрет на результаты мультиплексирования в общем случае носит нелогический характер , то алгоритм условно мож но разделить на два этапа: I -логический -расчет функций собственно мультиплексоров , реализуемых данным БФэ(2Г|:зН и II -нелогический коррекция результатоврасчета с учетом сигналов запрета( б

749184

Расчет по алгоритму {П производится в многозначной логике: состояние сигнала при расчете БФЭ описывается двухразрядным двоичным кодом, обозначаемым в дальнейшем КП код представления сигнала, первый и второй разряды которого обозна аются AJ и А.,

Состояние сигнала А и КП сигнала А имеет следующее соответствие: Гй На первом этапе 71 алгоритма iV возникновение на линиях связи схемы той части схемы модуля, которая реализует этот этап, KIT сигнгша, соответствующего состоянию Z, невозможно, В реальных схемах входные шины не могут находиться в высокоимпедансном состоянии, а на внутренних линиях связи указанной части схемы модуля оно не может возникнуть как результат логических операций из-за нелогического характера состояния Z, На втором этапе 8 алгоритма .fl|j при наличии сигналов запрета сигналам на выходах модуля присваиваются значения, соответствуклцие состоянию,выходного сигнала БФЭ, равного логической 1 при расчете МПБ ФЭО и Z при расчете МПБФЭ,. Для того, чтобы пояснить принцип подхода к расчету функции мультиплексора, по алгоритму необходимо привести формулы из расчета по нему конъюнкции, дизъюнкции и отрицания : 1. Конъюнкция () - О О О 000 1 .1 1 11 Р( - А1,+А2, Г„ AU +А2, о о 3. Отрицание Так как любая функция ваемая на выходе любой И описана выражением, соде конъюнкции, дизъюнкции о ного, числа как прямых, т ных аргументов - сигнало ИС, то согласно и ю функции вида Р(, .А7 . Г2 где AN и Аи являются нез переменными, можно расчи мулам , (M,(A:il,,.,. ,АН.,1М«М 0 (М„(ГОо,.- AM.(Л или в соответстви с F, Ftft,jf-,,,,.,ftN,,ANo)i fu o lAI-ftloVM ANo.ftN ib В частности, расчет КП функций собственни мультиплексоров из двух каналов в один (,1), из четырех в один (,1) и из восьми в один ,1| ), реализуемых БФЭ перечисленных в таблице типов (где i - номер мультиплексорной функции в БФЭ), производится в соответствии с {9-14J по формулам I.М 8, ,0,D1,- S4o-s5.Slo +... +D8,-84,. S2,, J г. Л ,(,. S4,- S2,- Sl,+... +D8o. 84„. S2o.Sl. II.M 4,y : ,1, D1, S2o- Slot.. .+D4, -S2, -SI, ; . ,l,Dl S2 |;io+... SI,; г -7 ,,-S2o-Slo+,..+D8, -82,-SI, f- J ,.S2, 81,-f...-HD8o-82 -Slp. III.M 2,1 : ,l, Dl,-81, +D2, -SI,; ,l Dl./l, ,; ,2l, ВЗ,.81„ -bD4, -SI,; ,21„ D3. SI,+В4,-81„; (l7J ,3, D5, . +D6,. 51,; Mt2,3X В5„., +D6 -Slo; ,4, D7, +D8,-S1,; M5,,- SI, +D8,- 81,. В общем случае мультиплексируюа1ая функция в описании ,il , а разряды КП этой функции МП, ,iJ. Сопоставительный анализ формул дпя расчета ,I,H ,ij | 15-17J показывает, что целесообразно производить поочередный расчет по этим формулам на одном итом же оборудовании. На основании этого, а также в соответствии с Г7, 8 и 11, алгоритм-fl можно записать более подробно: Подача сигналов на входы модуляП Мультиплексирование входных сигналов, необходимых для расчета первых разрядов КП функций вида М j,i. . 19 Расчет первых разрядов функций вида MPj, по формулам Г|5-17 {20 Выбор результатов расчета,соответствующих типу функционирования расчитываемого БФЭf lj Мультиплексирование входных сигналов, необходимых для расчета вторых разрядов КП функций вида Mtj, Рйсчет вторых разрядов КП функций вида М j, поформулам(15-1 23

Выбор результатов расчета,COOT- ветствунядих типу функционирования расчитываемого

Составление КП результатов ; расчетаt j

Преобразование КП с учетом инвертирования в БФЭ результата мультиплексированияf j

Коррекция результатов расчета в 10 соответствии с сигналами запрета расчитываемого -БФЭГ27

Конец: 28i

Сигналы, поступающие на информационные 1, адресные 2 и управляю- is щие 3 входы модуля (первый шаг )8 алгоритма , представляют собой разряды КП, обозначаемые. D1 , Б,..,, D8,, D8, SI, , ...,S4, , 54, Gl., Gljj, G2 , G2-0, соответственно 20 информационных (D1-D8), адресных. (SI, S2, S4) сигналов и сигналов затпрета (Gl, G2) на входах расчитываемого БФЭ, Сигналы, поступающие на управляющие входы 4 задания функции 25 модуля, представляют собой разряды ТО - ТЗ МН БФЭ.

Последовательная передача данныхс входов 1, 2 модуля на входы узла 10 расчета функций осуществляется зо коммутаторами 7 и 8, управляемыми с-игналом ПС,

Причем при (второй шаг {l9( алгоритмау на входы узла 10 посту- пают сигналь .D1,-D8 I, S1,, Sl., S2, , ,, S2, 84,, S4p; при (пятый шаг {22 алгорит а) - сигналы D1, - D8o, Slo, SI, , S2o, S2, , S4o, S4,.

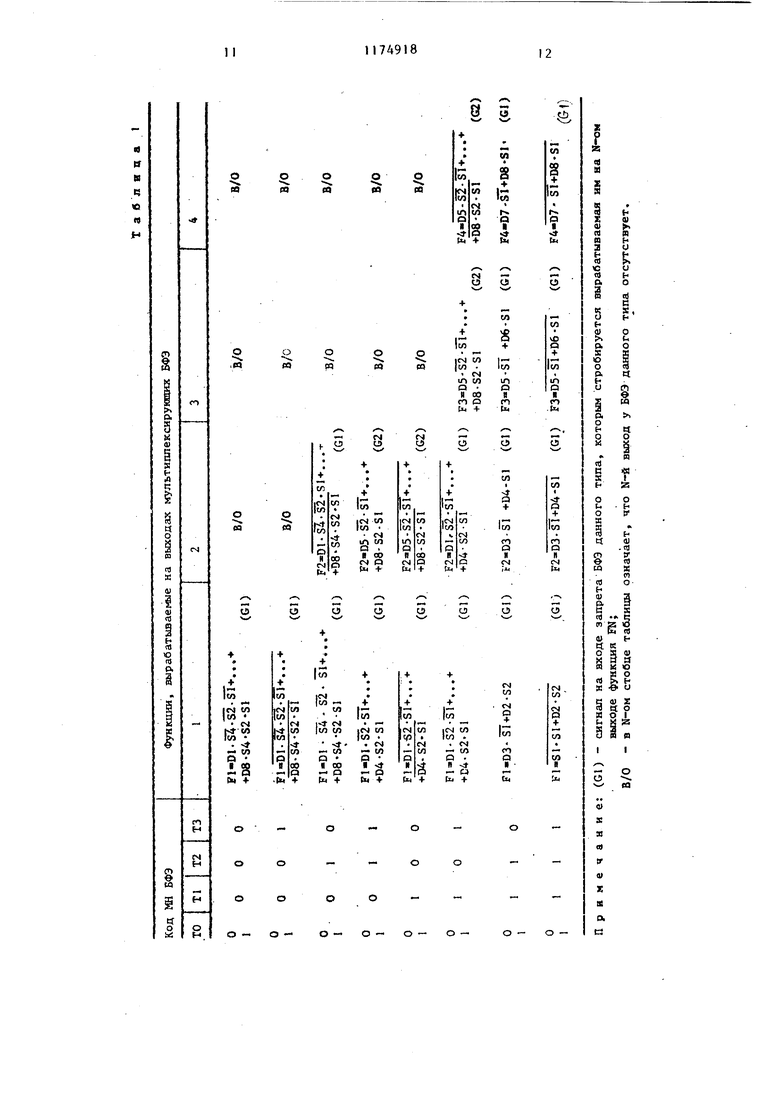

Узел 10 расчета реализует тре- тий 20. (при ) и шестой (23 (при , ) шаги алгоритма. На выхо . ах селекторов 11-17, входящих в его состав, вырабатываются функции, представленные в табл. 2. .

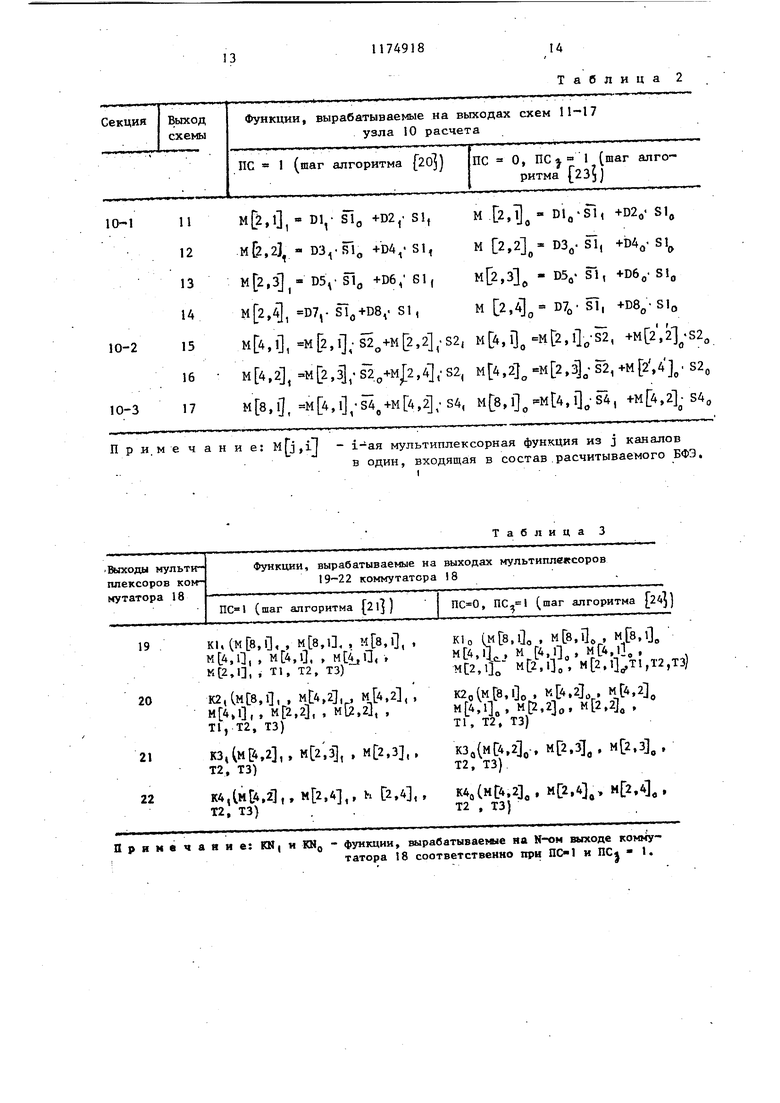

Мультиплексор 18 реализует чет- вертый {21 (при и седьмой (при , ПС 1 шаги алгоритма. ультиплексоры 19-22, входящие в его состав, вырабатывают на своих выхоах функции, представленные в табл,3. а регистры 23 и 24 при и ПС,1 соответсвенно принимаются с выходов мультиплексора 18 соответствующие результаты расчета представ-- 55 енные в табл, 4 (шаг {25 алгоритма.

Мультиплексоры 29 (фиг.1 и 2) узов 25-28 коррекции реализуют девятый шаг 26 алгоритма согласно (lT( в соответствии с формулами

IN,RN.. S1N+RN.-SIN ;

29

1X11 iJ Jk 1ч «

о RNj, SIN+RN - SIN,

IN

где RN и RNg; - сигналы на выходах соответственно 23 и 24 регистров;

SIN - сигнал на управляюще входе мультиплексора N-го из четырех узлов ко р ре кции.

Сигналы SIN вырабатываются узлом 38 управления инвертированием блока 32 в соответствии с табл. 5.

Коррекция результатов расчета в соответствии с сигналами запрета (десятый шаг (28j алгоритма) производится элементами И-ИЛИ 30 и 31 в соответстви с формулами

,-10FN/YlF«, ; г-з . ,.YO -bYl,, i где YOp,, У1,УОр,и Ylp

- сигидналы установки соответственно и 1 первого (FN) и второго (FN ) разрядов КП функции, вырабатываемой на N-dM выходе БФЭ; IN и IN - выходы соответственно первой и второй схем (2-1) И-2ИЛИ N-ro узла коррекци

Механизм действия сигнала запрета на значения разрядов КП выходной функции проилл1бстрирован формулами Yl ТО-GO -HO-G, 31 YOp, TO-G,- GO (32

+TOG,. G 33

YL

(34

TO G,

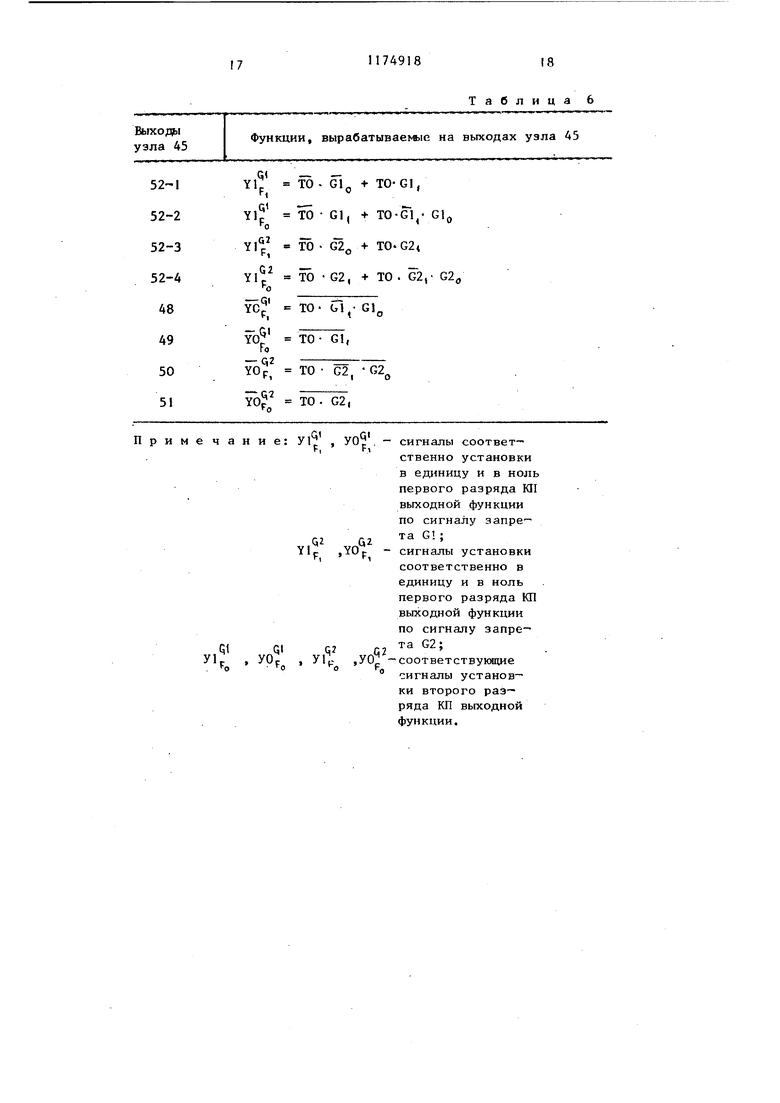

Подставляя в формулы З1-34 значения Glj,-Glp и G2,G2p, получим перечень выражений для преобразованных сигналов запрета, вырабатываемых на выходах узла 45 блока 32 (табл.6).

Так. как результаты мультиплексирования на одном и том же выходе различных типов БФЭ могут стробировать- ся различными сигналами запрета G1 и G2, то преобразованные сигналы запрета (табл.б) нуждаются в дополнительном распределении по выходам YOpf, ,

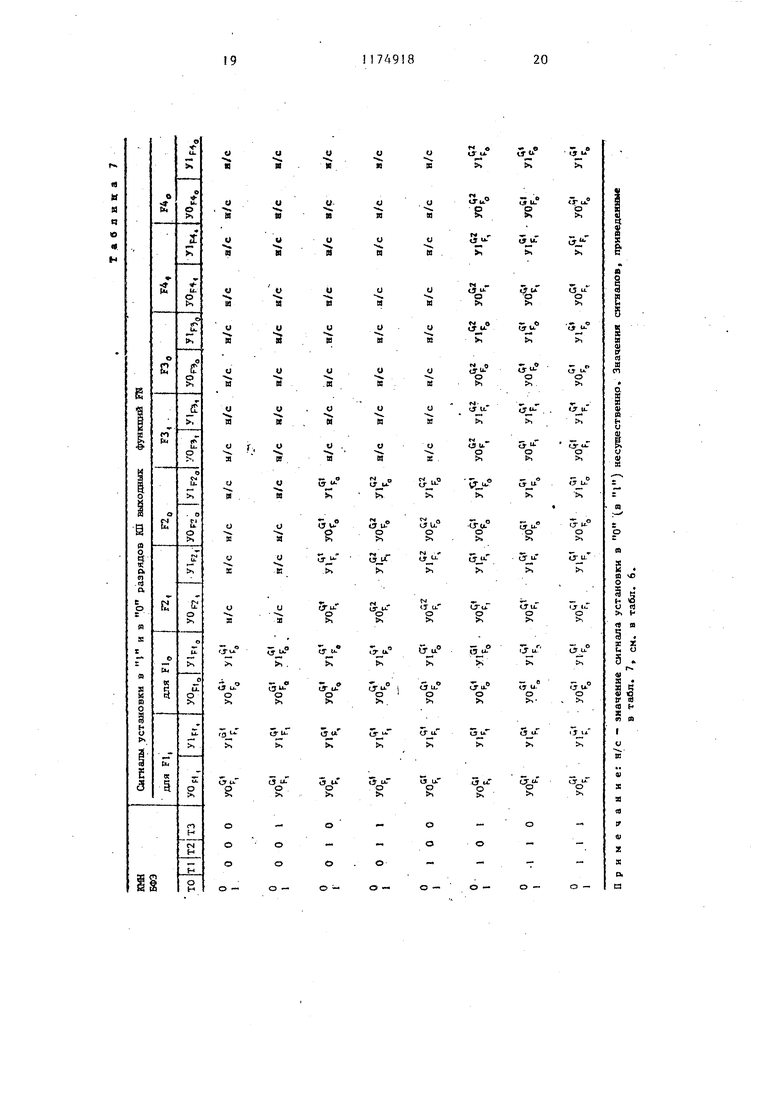

Y1

YO,

Р1 и Ylpfj узлов 25-28 корFN, рекции. Это распределение осуществляется мультиплексорами 53 и 55,Соответствие значений сигналов установки в О и в 1 значениям преобразованных сигналов запрета приведено в табл, 7.

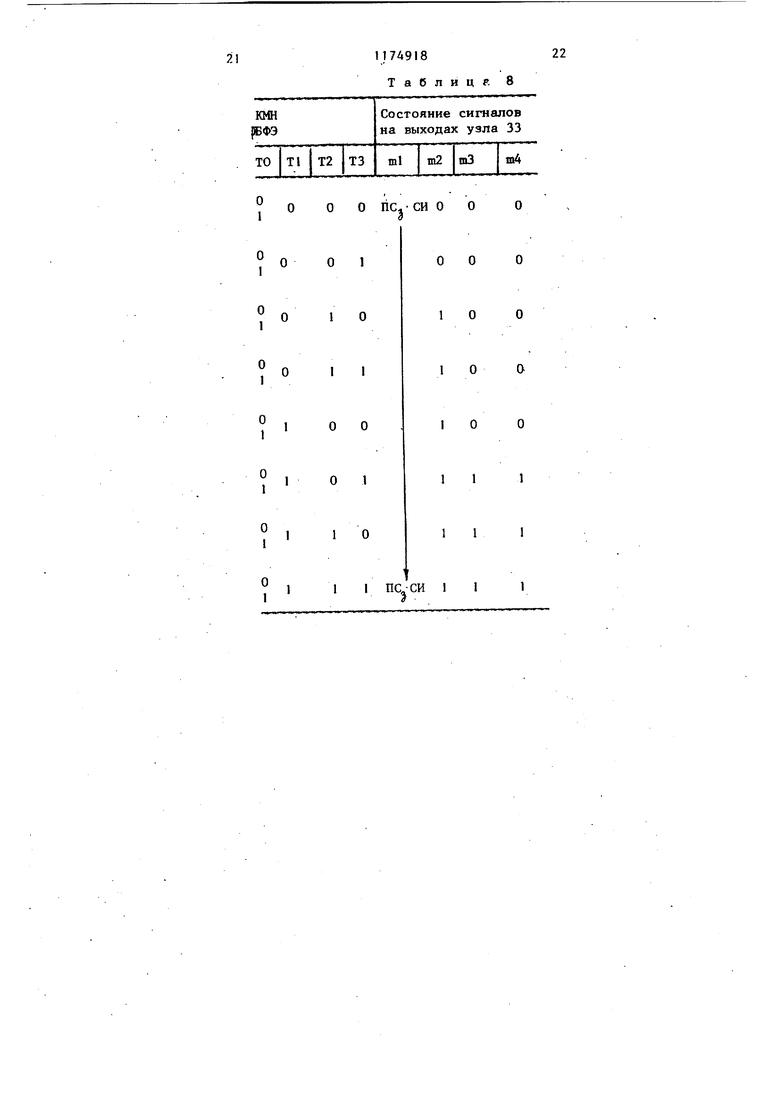

В состав устройства включен узел 33 маскирования. На его выходах формируется четырехразрядная маска.

N-й разряд которой сопровождает ингформацию на N-ой паре выходов из первой группы выходов модуля и содержит признак действительности этой ин- формации.

Первый разряд маски помимо признака действительности результатов расчета F1, и Fig содержит признак готовности результатов расчета к считыванию внешней ЭВМ.

Таким образом, при с выходов модуля считываются результат расчета FNji и FNfl, сопровождаемые , где fflN - выходы узла 33 маскирования.

Зависимость значений сигналов на выходе узла 33 маскирования от типа срабатывания БФЭ представлена в табл. 8.

Преимущество предлагаемого изобретения по сравнению с известным заключается в увеличении быстродействия в среднем в пять раз за счет того, что расчет значений сигналов на выходах БФЭ независимо от количества входов и типа БФЭ производится за один цикл, а в известном устройстве вычисления производятся цоэтапно, причем количество этапов тем больше, чем сложнее искомая функция.

,1, - D1,- Slg +D2,- SI,М Сг.Т - , -Ю2о- 81„

.23 - D3,.Bi +D4,. 8ЦМ 2,2 D3,. 81, 4-D4o.

, Sl +D6, 81,,3 - DS,- SI, +06,- Sl

,4, D7,- ,. SI ,M 2, D sT, +В8„- Sl

,l, ,,2,.S2,, Г|, , , ,,

,2, ,3l,-S2: +Mj;2,4,S2,.2 ,,.4. 52„

,1|, ,1,,2,. S4,, l . i S4, .21-84, При.мечание: ММ,11 К1.(,1, , ,1. , ,i, ,

К 4,1, , ,1. , , , КС2,1, , Т1, Т2, ТЗ)

,1,, МГ4,2, ,2,, ,. ,2, , Mb.zl, , Т1, Т2, ТЗ)

.2,, МС2,3, , ,3,, Т2, ТЗ)

K4,tMt;4,2, , ,4,, h 2,4, , Т2, ТЗ) Примечание: КН|И КЫ :

Таблица 2

Таблица 3

К1о UCB.lL , , , ,

«t.U. «Л.1о. С.1..

НС2, ,11„, .,T2,T

К2о №, Оо . К 4.2 М 4.2 ,, ,, ,2 , Т1, Т2, ТЗ)

КЗДМС4,.. .3 . .3, , Т2, ТЗ)

(нС4.2, МС2,4, .4, Т2 , ТЗ) i-ая мул ьтипле к сорная функция из j каналов в один, входящая в состав.расчитываемого БФЭ, функции, вырабатывае1«1е яа выходе комьсу- татора 18 соответственно при ПО1 и ПС I.

23 24

RN, - KN,-nC - СИ„

н/с П р и м е ч а н и е{ СИ н/с О

000

О О I

О 1 О

1 о

О 1 1

о

1 о О

1

о

О

1 О 1

1

О 1

О

1 1 О

О 1

I Примечание SIN

Таблица 4

Выходы заблокированы в состояНИИ RN J

SN. ,,

Таблица 5

н/с

н/с

н/.

н/с

н/сн/с

н/сн/с

н/с

н/с состояние сигнала на сннхровходе регистра, соот ветствующее переходу 1-0 п-го синхроимпульса; состояние выходов регистра несущественно. сигнал управления инверсией КП функции FN на N-OM выходе БФЭ; состояние управлйкщего сигнала несущественно.

римечание: , . - сигналы соответ.QZ

Yip ,YOp - сигналы установки

qi qi q q2 2; ip , ypp 1 yip ,yOp -соответствующие

Таблица 6 ственно установки в единицу и в ноль первого разряда KII выходной функции по сигналу запре-

та G ; соответственно в единицу и в ноль первого разряда КП выходной функции по сигналу запре сигналы установки второго разряда КП выходной функции.

21

22 Таблиц p. 8 as h 1Фиг. 2

Фиг.З

I 2

КНс ml

FH

Фиг. -V

| Авторское свидетельство СССР № 754427, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Программируемый многофункциональныйлОгичЕСКий МОдуль | 1979 |

|

SU851399A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1985-08-23—Публикация

1984-01-30—Подача