(54) ПРОГРАММИРУЕМЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ

t

Изобретение относится к вычислительной технике и может быть использовано в микропрограммных устройствах обработки логической информации, предназначенных для математических вычислений, контроля и управления сложными процессами.

Известен многофункциональный модуль для реализации булевых функций, содержащий логические элементы и триггеры Cll

Недостатком модуля является его сложность и ограниченное количество реализуемых булевых функций.

Наиболее близким к предлагаемому является многофункциональный модуль, реализующий булевые функции от любого числа аргументов, содержащий первый коммутатор, управляющие вхо-. ды которого соединены с управляющей ишиой, а информационные входы - с информационными входами модуля, дешифратор, входы которого соединен} с управляющей шиной модуля, триггер, выход которого соединен со входом коммутатора С2 .

Недостатками этого модуля являются его сложность и ограничения, накладываемые на класс реализуеколх булевых функций. Так операции проЛОГИЧЕСКИЙ МОДУЛЬ

межуточных вычислений происходят для числа аргументов не выше трех, и значения промежуточных функций злпоминаются на триггере. Результаты промежуточных вычислений с выхода логического блока и триггера поступают на соответствующие входы ко «мутатора в качестве аргументов для вычисления последующего промеtoжуточного результата или окончательного значения функции. В качестве примера рассмотрим процесс вычисления этим модулем функции

ts

«.VVVVV T-VVVV e ,В первом такте вычисляется функция

а Значение функции зап

запоАшнается

на триггере.

Во втором такте вычисляется 25 функция

Ч. «. в третьем - функция

Ч - л f«

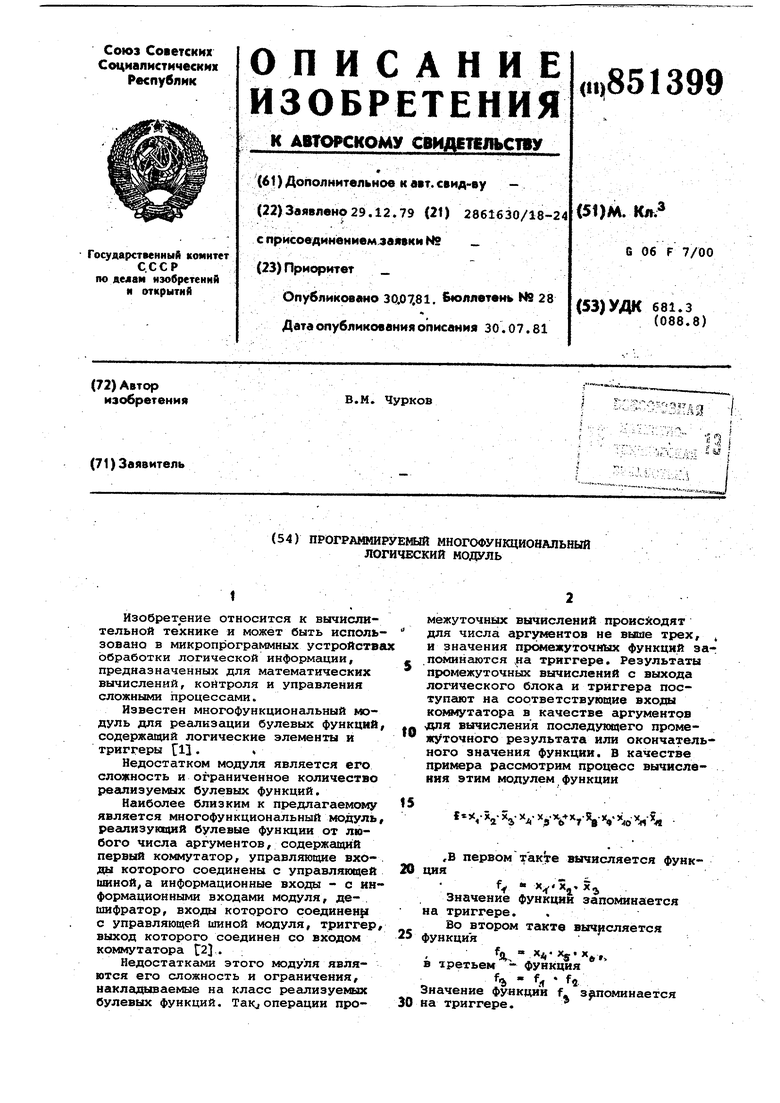

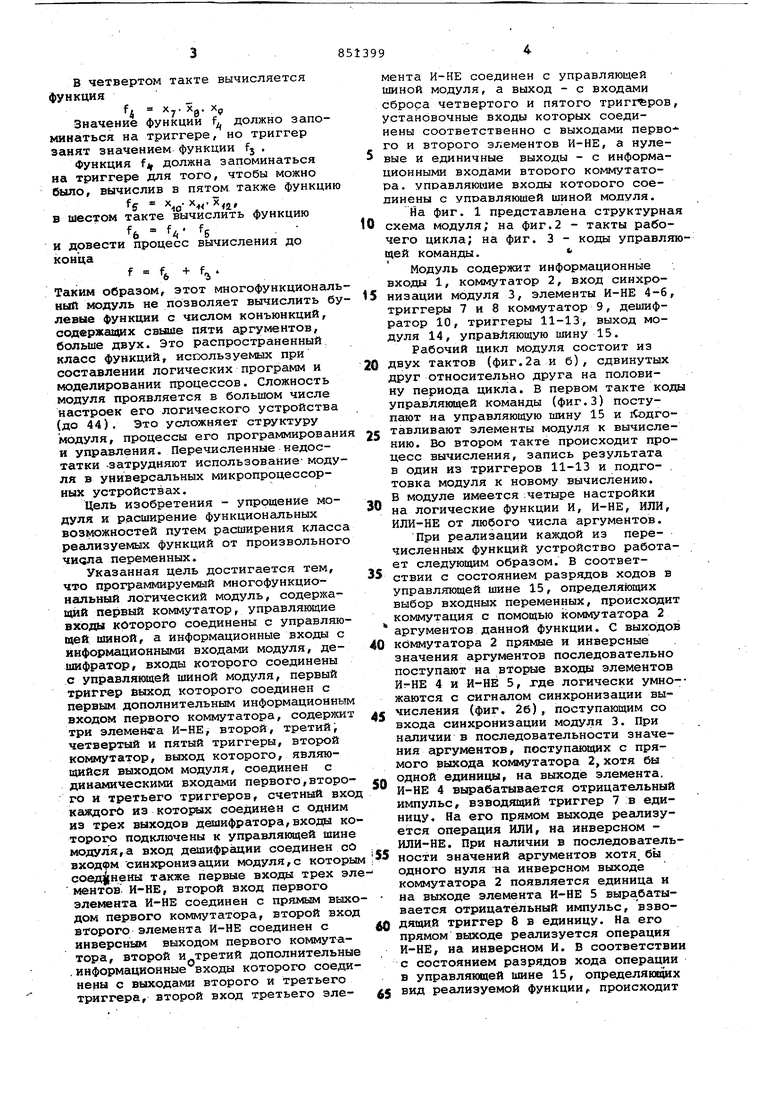

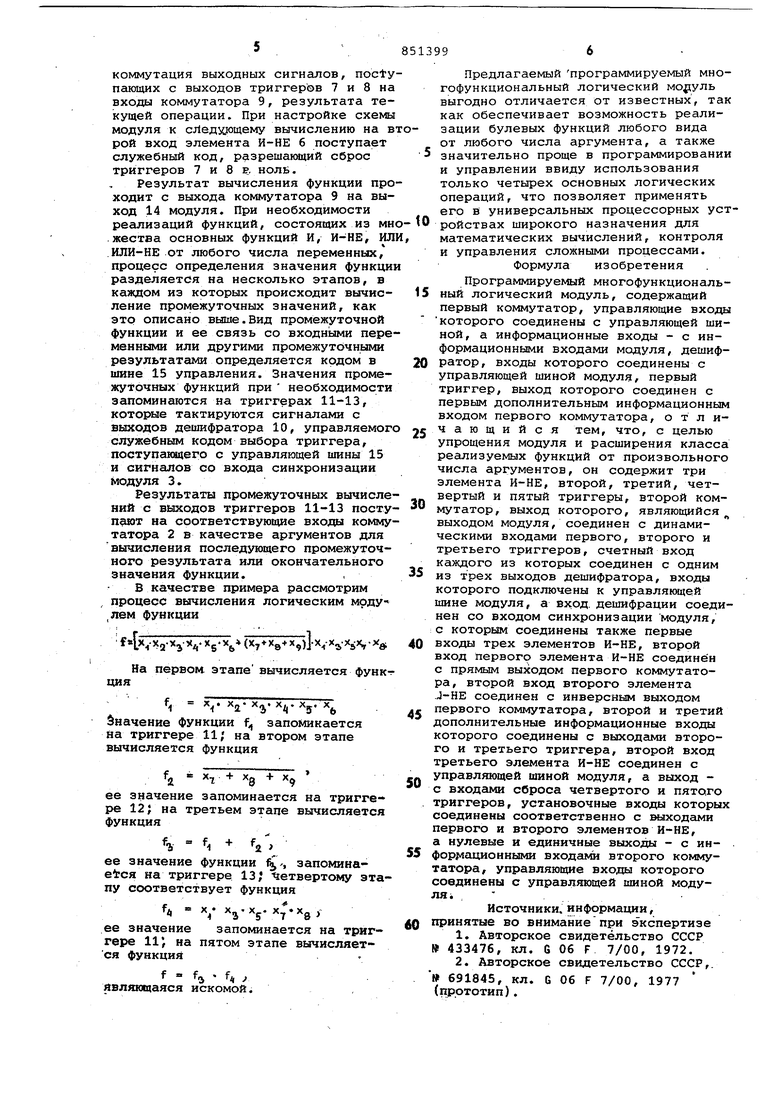

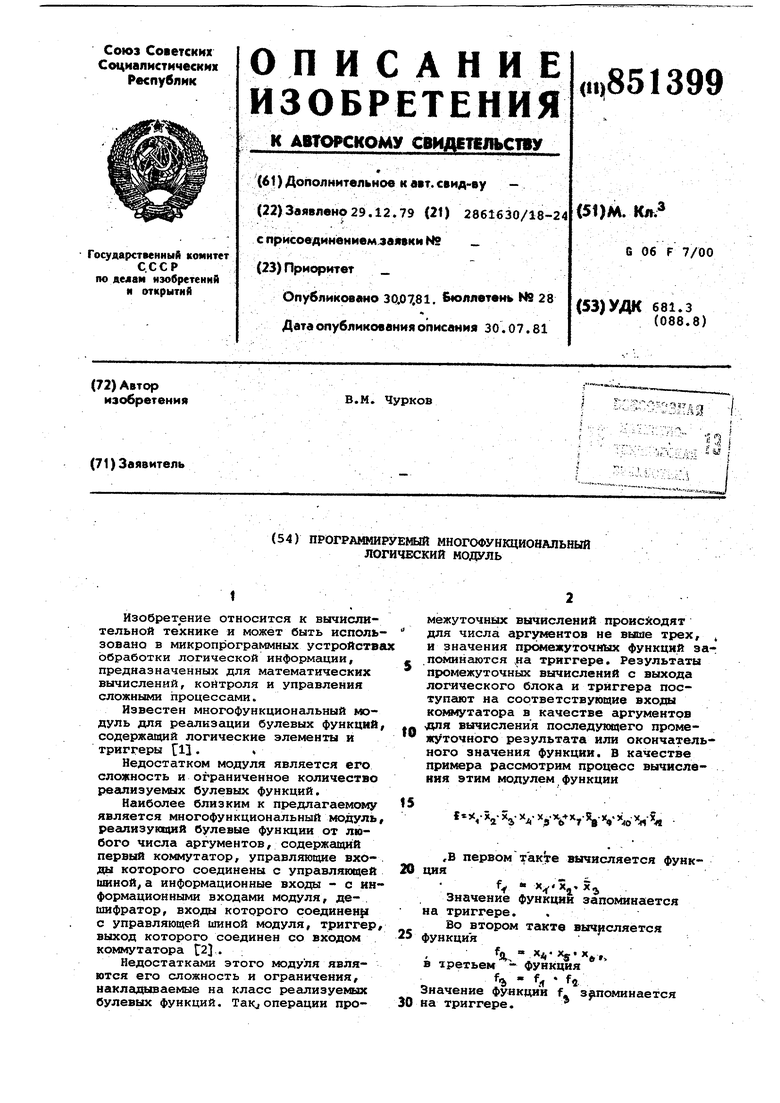

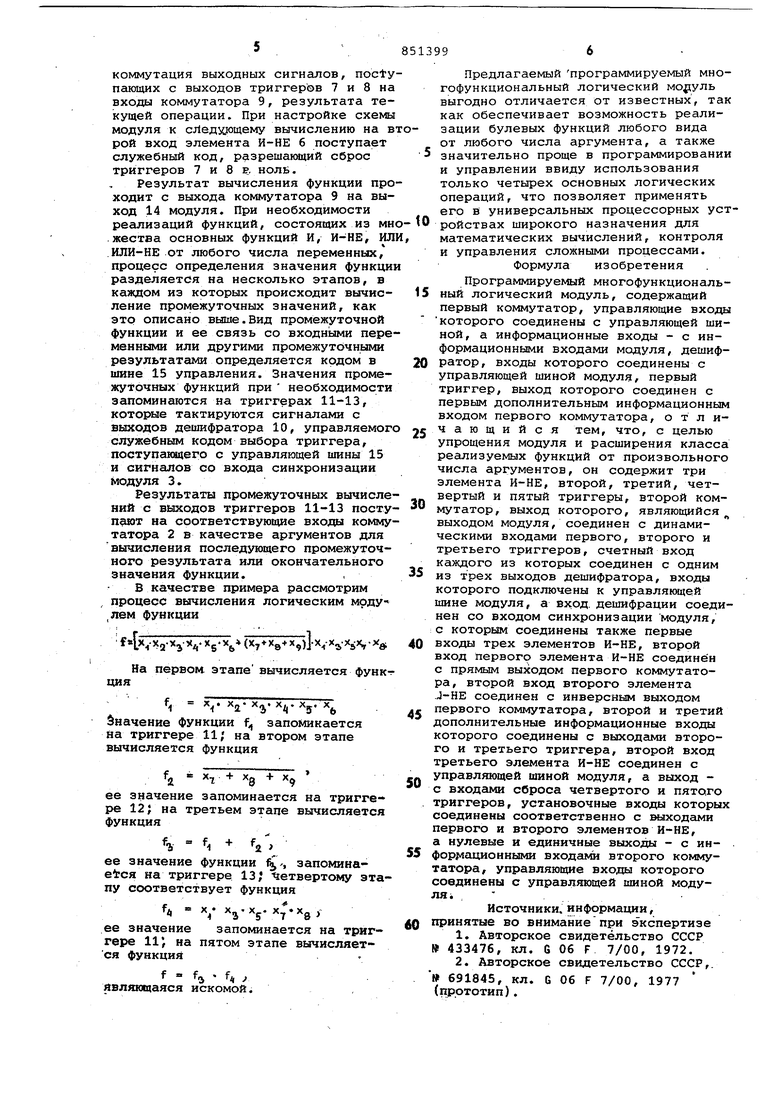

Значение функции f запоминается 30 на триггере, В четвертом такте вычисляется функция Ху. Хд. Хд Значение функций f должно запоминаться на триггере, но триггер занят значением функции fj . Функция f должна запоминаться на триггере для того, чтобы можно было, вычислив в пятом также функцию 5 о в шестом такте вычислить функцию и довести процесс вычисления до конца f f + Таким образом, этот многофункциональ ный модуль не позволяет вычислить бу левые функции с числом конъюнкций, содержа14их свыше пяти аргументов, больше двух. Это распространенный, класс функций, исгюльзуемых при составлении логических программ и моделировании процессов. Сложность модуля проявляется в большом числе настроек его логического устройства (до 44). Это усложняет структуру модуля, процессы его программировани и управления. Перечисленные недостатки -затрудняют использование- модуля в универсальных микропроцессорных устройствах. Цель изобретения - упрощение модуля и расширение функциональных возможностей путем расширения класса реализуемых функций от произвольного чидла переменных. Указанная цель достигается тем, что программируемый многофункциональный логический модуль, содержащий первый коммутатор, управляющие входы которого соединены с управляю щей шиной, а информационные входы с информационными входами модуля, дешифратор, входы которого соединены с управляющей шиной модуля, первый триггер выход которого соединен с первым дополнительным информационны входом первого коммутатора, содержи три элемена-а И-НЕ, второй, третий; четвертый и пятый триггеры, второй коммутатор, выход которого, являющийся выходом модуля, соединен с динамическими входами первого,второ го и третьего триггеров, счетный вхо каждого из которых соединен с одним из трех выходов дешифратора,входы к торого подключены к управляющей шин модуля,а вход дешифрации соединен с входфм синхронизации модуля,с котор (нены также первые входы трех э ментов И-НЕ, второй вход первого элемента И-НЕ соединен с прямым вых дом первого коммутатора, второй вхо второго элемента И-НЕ соединен с инверсным выходом первого коммутатора, второй и третий дополнительны .информационные входы которого соеди нены с выходами второго и третьего триггера, второй вход третьего элемента И-НЕ соединен с управляющей шиной модуля, а выход - с входами сброса четвертого и пятого триггеров, установочные входы которых соединены соответственно с выходами перво го и второго элементов И-НЕ, а нулевые и единичные выходы - с информационными входами ВТОРОГО коммутатора, управляющие входы которого соединены с управляющей шиной модуля. На фиг. 1 представлена структурная схема t/юдуля; на фиг.2 - такты рабочего цикла; на фиг. 3 - коды управляющей команды. Модуль содержит информационные входы 1, коммутатор 2, вход синхронизации модуля 3, элементы И-НЕ 4-6, триггеры 7 и 8 коммутатор 9, дешифратор 10, триггеры 11-13, выход модуля 14, управляющую шину 15. Рабочий цикл модуля состоит из двух тактов (фиг.2а и б), сдвинутых друг относительно друга на половину периода цикла. В первом такте коды управлякяцей команды (фиг.З) поступают на управляющую шину 15 и подготавливают элементы модуля к вычислению. Во втором такте происходит процесс вычисления, запись результата в один из триггеров 11-13 и подго- . товка модуля к новому вычислению. В модуле имеется ;четыре настройки на логические функции И, И-НЕ, ИЛИ, ИЛИ-НЕ от любого числа аргументов. При реализации каждой из перечисленных функций устройство работает следующим образом. В соответствии с состоянием разрядов ходов в управляющей шине 15, определяющих выбор входных переменных, происходит коммутация с помощью коммутатора 2 аргументов данной функции. С выходов коммутатора 2 прямые и инверсные значения аргументов последовательно поступают на вторые входы элементов И-НЕ 4 и И-НЁ 5, тде логически умно-жаются с сигналом синхронизации вычисления (фиг. 2б), поступающим со входа синхронизации модуля 3. При наличии в последовательности значения аргументов, поступающих с прямого выхода коналутатора 2, хотя бы одной единицы, на выходе элемента. И-НЕ 4 вырабатывается отрицательный импульс, взводящий триггер 7 в единицу. На его прямом выходе реализуется операция ИЛИ, на инверсном ИЛИ-НЕФ При наличии в последовательности значений аргументов хотя бы одного нуля на инверсном выходе коммутатора 2 появляется единица и на выходе элемента И-НЕ 5 вырабатывается отрицательный импульс, взводящий триггер 8 в единицу. На его прямом выходе реализуется операция И-НЕ, на инверсном И. В соответствии с состоянием разрядов хода операции в управляющей шине 15, определякяцих вид реализуемой функции, происходит коммутация выходных сигналов, nocty пающих с выходов триггеров 7 и 8 на входы коммутатора 9, результата текущей операции. При настройке схем модуля к сЛед уощему вычислению на рой вход элемента И-НЕ 6 поступает служебный код, разрешающий сброс триггеров 7 и 8 э. ноль. Результат вычисления функции про ходит с выхода коммутатора 9 на вы ход 14 модуля. При необходимости реализаций функций, состоящих из м .жества основных функций И, И-НЕ, ИЛ ИЛИ-НЕ от любого числа переменных, процесс определения значения функци разделяется на несколько этапов, в каждом из которых происходит вычисление промежуточных значений, как это описано выше.Вид промежуточной функции и ее связь со входными пере менными или другими промежуточными результатами определяется кодом в шине 15 управления. Значения промежуточных функций при необходимости запоминаются на триггерах 11-13, которые тактируются сигналами с выходов дешифратора 10, управляемог служебным кодом выбора триггера, поступающего с управляющей шины 15 и сигналов со входа синхронизации модуля 3. Результаты промежуточных вычисле ний с выходов триггеров 11-13 посту пдют на соответствующие входы комму татора 2 в качестве аргументов для вычисления последующего промежуточного результата или окончательного значения функции., В качестве примера рассмотрим процесс вычисления логическим моду ,лем функции (Х7 + Хв+Х,).,.,.Х. На первом этапе вычисляется функ Xj- x,j. . Xj. х Значение функции f запоминается йа триггере 11, на втором этапе вычисляется функция fy, 1 + В ) ее значение запоминается на триггере 12; на третьем этапе вычисляется функция fi - fa . ее значение функции f., запоминается на триггере 13/ tieTBepTOMy эта пу соответствует функция f X.J.XJ. Х.Хду ее значение запоминается на триг rape 11; на пятом этапе вычисляется функция f f 5 f л являющаяся искомой. Предлагаемый программируемый многофункциональный логический модуль выгодно отличается от известных, так как обеспечивает возможность реализации булевых функций любого вида от любого числа аргумента, а также значительно проще в программировании и управлении ввиду использования только четырех основных логических операций, что позволяет применять его в универсальных процессорных устройствах широкого назначения для математических вычислений, контроля и управления сложными процессами. Формула изобретения Программируемый многофункциональный логический модуль, содержащий первый коммутатор, управляющие входы которого соединены с управляющей шиной, а информационные входы - с информационными входами модуля, дешифратор, входы которого соединены с управляющей шиной модуля, первый триггер, выход которого соединен с первым дополнительным информационным входом первого коммутатора, отличающийся тем, что, с целью упрощения модуля и расширения класса реализуемых функций от произвольного числа аргументов, он содержит три элемента И-НЕ, второй, третий, четвертый и пятый триггеры, второй коммутатор, выход которого, являющийся выходом модуля, соединен с динамическими входами первого, второго и третьего триггеров, счетный вход каждого из которых соединен с одним из трех выходов дешифратора, входы которого подключены к управляющей шине модуля, а вход, дешифрации соединен со входом синхронизации модуля, с которым соединены также первые входы трех элементов И-НЕ, второй вход первого элемента И-НЕ соединён с прямым выходом первого коммутатора, второй вход второго элемента J-HE соединен с инверсным выходом первого коммутатора, второй и третий дополнительные информационные входы которого соединены с выходами второго и третьего триггера, второй вход третьего элемента И-НЕ соединен с управляницей шиной модуля, а выход с входами сброса четвертого и пятого триггеров, установочные входы которых соединены соответственно с выходами первого и второго элементов И-НЕ, а нулевые и единичные выходы - с инфор1лгщионными входги ш второго коммутатора, управляющие входы которого соединены с управляющей шиной модуЛЯ;Источники, информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 433476, кл. 6 Об F 7/00, 1972. 2. Авторское свидетельство СССР,. 691845, кл. G Об F 7/00, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный модуль | 1977 |

|

SU691845A1 |

| Многофункциональный логический модуль | 1989 |

|

SU1661752A1 |

| Устройство для вычисления булевых функций | 1988 |

|

SU1501033A1 |

| Устройство для реализации логических функций | 1981 |

|

SU1001080A1 |

| УСТРОЙСТВО ДЛЯ ПОСТРОЕНИЯ ПРОГРАММИРУЕМЫХ ЦИФРОВЫХ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2003 |

|

RU2254603C1 |

| УСТРОЙСТВО ДЛЯ ПОСТРОЕНИЯ ПРОГРАММИРУЕМЫХ ЦИФРОВЫХ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2004 |

|

RU2273042C2 |

| Устройство для моделирования конечных автоматов | 1980 |

|

SU955080A1 |

| Программируемый контроллер | 1987 |

|

SU1448338A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ, ЭЛЕКТРОННЫМИ КЛЮЧАМИ И СИГНАЛИЗАЦИЕЙ | 2001 |

|

RU2207612C2 |

| Устройство для построения программируемых цифровых микропроцессорных систем | 2015 |

|

RU2616153C2 |

а S

Ко9 аргупента

К09 операции

То л ml Т акт г

СлуяеУныи код

Авторы

Даты

1981-07-30—Публикация

1979-12-29—Подача