мирователя адреса модификатора адреса, первый выход формирователя адрес подключен к второму информационному входу регистра данных модификатора адреса, второй выход формирователя адреса модификатора адреса подключен к второму адресному входу регистра адреса накопителя имитируемых регист .ров и промежуточных результатов, тре тий адресный вход регистра адреса накопителя имитируемых регистров и промежуточных результатов объединен с первым входом дешифратора блока имитируемых регистров, выход регистр адреса накопителя имитируемых регист ров и промежуточных результатов подключен к адресному входу блока памяти накопителя имитируемых регистров и промежуточных результатов, выход регистра данньрс которого подключен к информационному входу блока памяти накопителя, второй информационный вход регистра данных которого подключен к выходу сумматора по модулю два блока имитируемых регистров, гру па входов сумматора по модулю два которого подключена к первой группе выходов буферного регистра блока ими тируемых регистров, управляющий вход буферного регистра которого соединен с выходом дешифратора блока имитируемых регистров, вход генератора тактовых импульсов является синхронизирующим входой многоразрядного генератора испытательных последовательностей, отличающийся быстродействия, введены блок управле ния, мультиплексор, схемы сравнения, конвейерный регистр и выходной ре- :. гистр, причем блок управления содержит два элемента ИЛИ, дешифратор команд, три элемента И,R5-триггер, два регистра и мультиплексор, причем группа входов первого элемента ИЛИ объединена с первой группой входов мультиплексора блока управления и яв ляется группой входов внешних данных режима работы многоразрядного генератора испытательных последовательностей, входы сброса первого и второ го регистров объединены с первым вхо дом первого элемента И блока управления и являются входом Пуск много.разрядного генератора испытательных последовательностей, синхронизирующие входы первого и второго регистров бло ка управления и конвейерного регистра объединены и подключены к выходу генератора тактовых Импульсов, первый выход первого элемента ИЛИ подключен к R-входу КЗ-триггера блока управления, второй выход первого элемента ИЛИ которого соединен .с вторым входом первого элемента И блока управления, выход первого элемента И которого подключен кS-входу RS-триггера блока управления, выход RS-триггера которого подключен к входу Пуск триггера мультиплексора блока управления, первые входы второго и третьего элементов И которого объединены с группой входов дешифратора команд блока управления, второй вход второго элемента И и третьего элемента И которого подключены к соответствующим выходам второго элемента ИЛИ блока управления, первый вход второго регистра блока управления объединен с группой входов дешифратора команд и второго элемента ИЛИ блока управления и является первым управляющим входом блока управления, подключенного к выходу блока памяти про-:грамм и к информационному входу конвейерного регистра, выходы дешифратора команд, входы-в осоды первого и второго регистров и выходы .второго и третьего элементов И блока управления подключены к соответствующим входам мультиплексора блока управления, кроме входа , который является вторым управляющим входом блока управления и подключен к выходу схемы сравнения модификатора адреса, первый и второй входы схемы сравнения модификатора адреса подключены соответственно к второму и третьему входам буферного регистра модификатора адреса и входу UQ мультиплексора, который является третьим управляющим входом блока управления, подключенным к выходу относительного адреса формирователя адреса моДИфикатора адреса, тактовый вход формирователя адреса которого соединен с первым выходом конвейерного регистра, второй и третий выходы которого подключены соответственно к первому входу дешифратора и первому входу схемы уравнения блока имитируемых регистров, второй вход схемы сравнения которого подключен к первому выходу буферного регистра блока имитируемых регистров, третий и четвертый выходы буферного регистра ко-

торого подключены соответственно к i ггервому и второму входам выходного регистра, информационный вход буферного регистра блока имитируемых регистров подключен к выходу мультиплексора накопителя имитируемых регистров и промежуточных результатов, первая группа входов мультиплексора которого подключена к выходу блока памяти накопителя имитируемых регистров и промежуточных результатов, вторая группа входов мультиплексора которого подключена к третьему и четвертому входам регистра данных накопителя имитируемых регистров и промежуточных результатов и к выходу схемы сравнения блока имитируемых регистров и третьему входу йыходного регистра, синхронизирую1ций вход которого подключен к первому выходу генератора тактовых тшпульсов, выход выходного регистра является выходом многоразрядного генератора испытательных по- следовател1зностей, третья группа выходов мультиплексора блока управления является третьим управляющим выходом блока управ41ения и подключена к управляющему входу блока памяти программ, четвертая группа выходов мультиплексора блока управленияявляется четвертым управляющим выходом блока управления и подключена к группе управляющих входов регистра данг ных, регистра адреса и к управляющим входам первого и второго блоков памяти модификатора адреса

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный генератор двоичных последовательностей | 1981 |

|

SU991397A1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1115054A1 |

| Устройство управления процессора | 1988 |

|

SU1670686A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Устройство для контроля блоков памяти | 1983 |

|

SU1092569A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

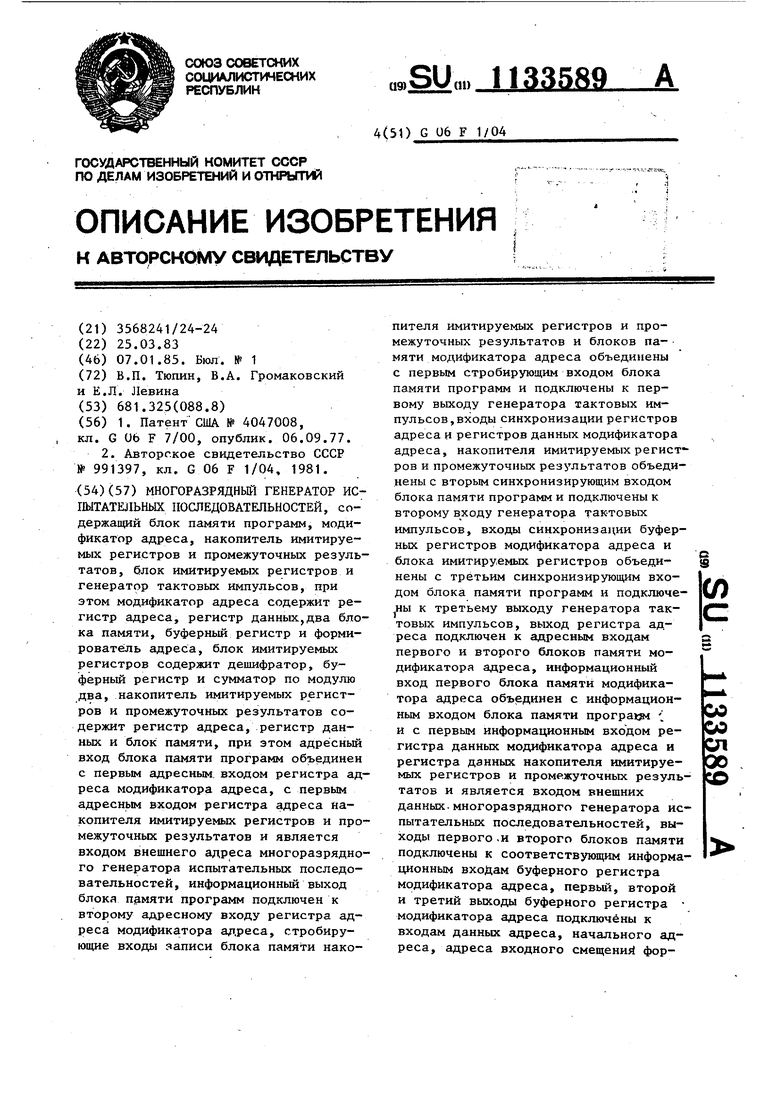

МНОГОРАЗРЯДНЫЙ ГЕНЕРАТОР ИСПЫТАТЕЛЬНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ, содержащий блок памяти программ, модификатор адреса, накопитель имитируемых регистров и промежуточных результатов, блок имитируемых регистров и генератор тактовых импульсов, при этом модификатор адреса содержит регистр адреса, регистр данных,два блока памяти, буферный регистр и формирователь адреса, блок имитируемых регистров содержит дешифратор, буферный регистр и сумматор по модулю два, накопитель имитируемых регистров и промежуточных результатов содержит регистр адреса, регистр данных и блок памяти, при этом адресный вход блока памяти программ объединен с первым адресным входом регистра адреса модификатора адреса, с первым адресным входом регистра адреса Накопителя имитируемых регистров и промежуточных результатов и является входом внешнего адреса многоразрядного генератора испытательных последовательностей, информационный выход блока памяти программ подключен к второму адресному входу регистра адреса модификатора a/i,peca, стробирующие входы записи блока памяти накопителя имитируемых регистров и промежуточных результатов и блоков памяти модификатора адреса объединены с первым стробирующим входом блока памяти программ и подключены к первому выходу генератора тактовых импульсов , входы синхронизации регистров адреса и регистров данных модификатора адреса, накопителя имитируемых регистров и промежуточных результатов объединены с вторым синхронизирующим входом блока памяти программ и подключены к второму входу генератора так-товых импульсов, входы синхронизации буферных регистров модификатора адреса и i блока имитируемых регистров объединены с третьим синхронизирующим вхо(Л дом блока памяти программ и подключе ны к третьему выходу генератора тактовых импульсов, выход регистра адреса подключен к адресным входам первого и второго блоков памяти модификатора адреса, информационный вход первого блока памяти модификатора адреса объединен с информационDO 00 СП ным входом блока памяти nporpa i , и с первым информационным входом регистра данных модификатора адреса и 00 регистра данных накопителя имитируемых регистров и промежуточных резуль ;о татов и является входом внешних данных.многоразрядного генератора испытательных последовательностей, выходы первого-и второго блоков памяти подключены к соответствунщим информационным входам буферного регистра модификатора адреса, первый, второй и третий выходы буферного регистра модификатора адреса подключены к входам данных адреса, начального адреса, адреса входного смещений фор

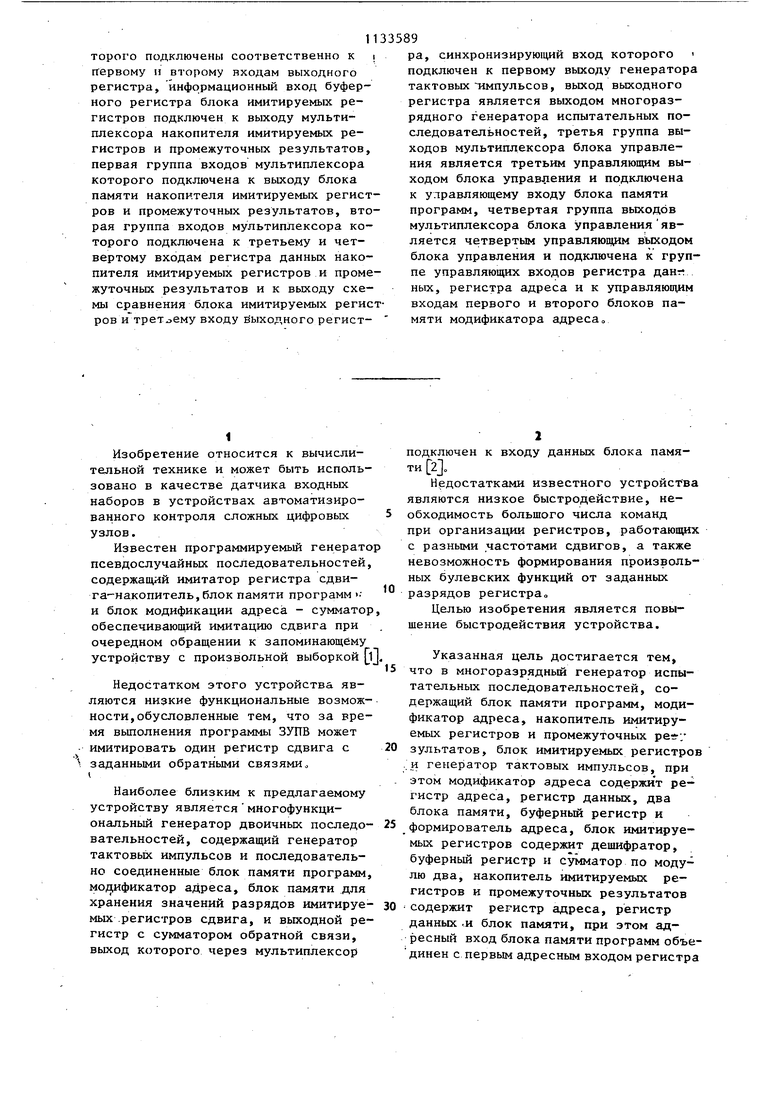

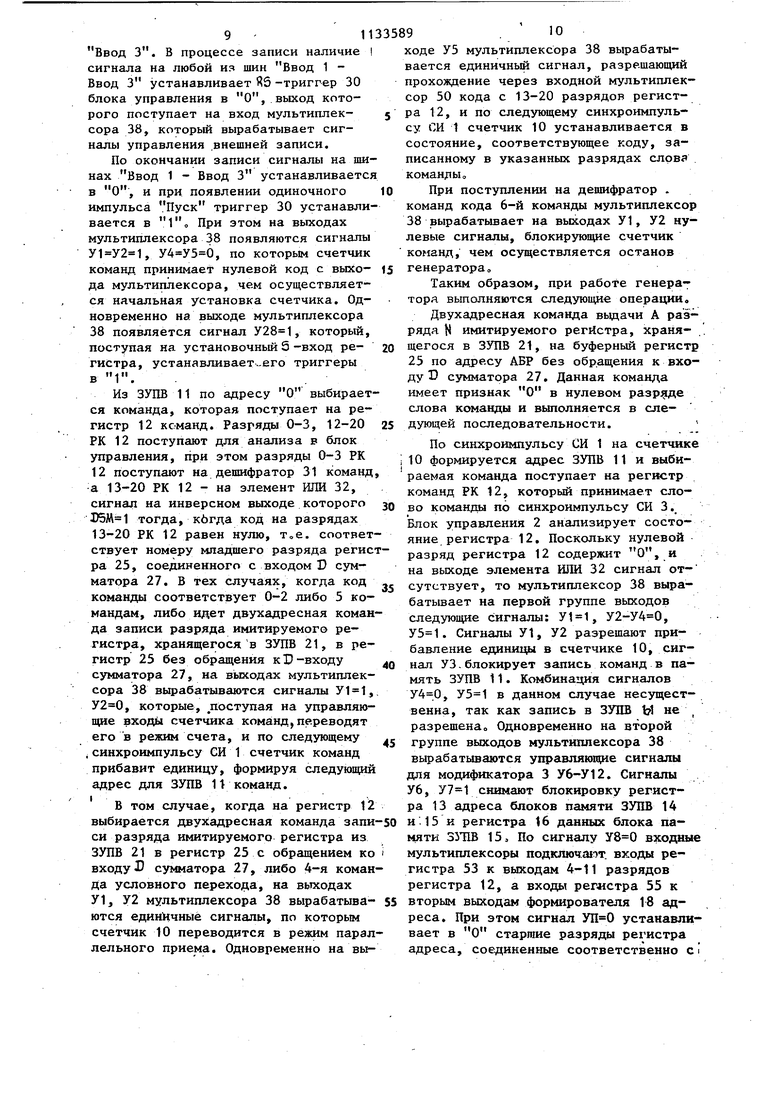

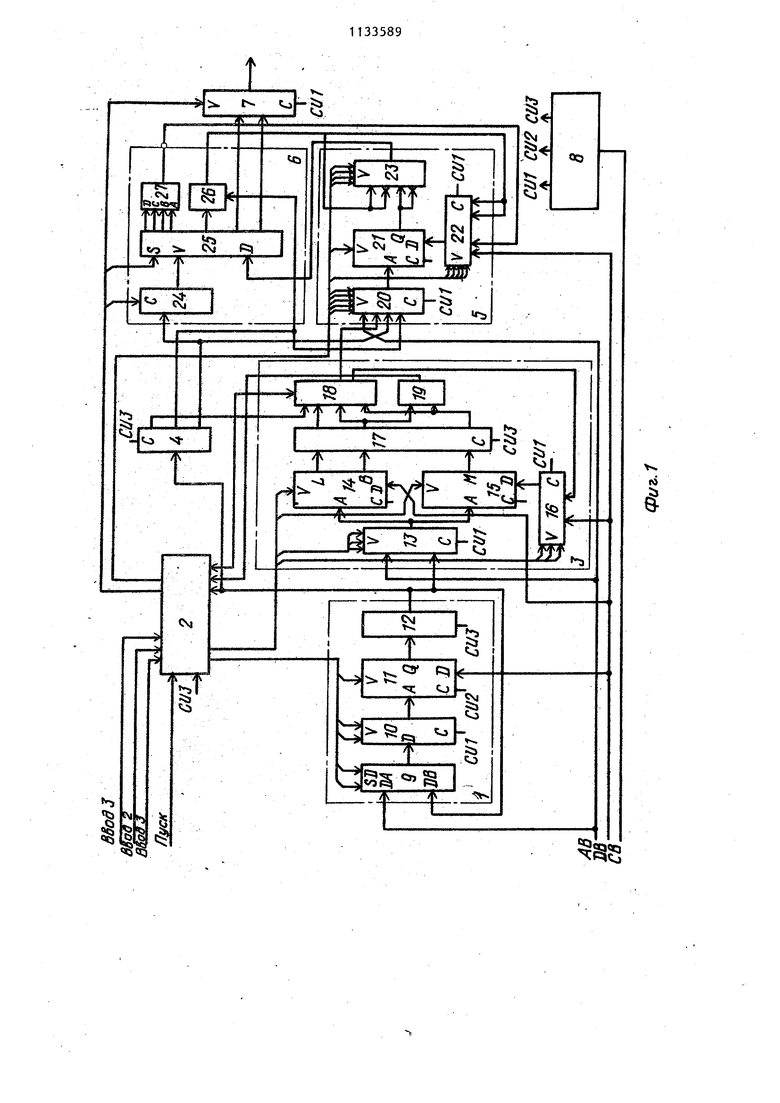

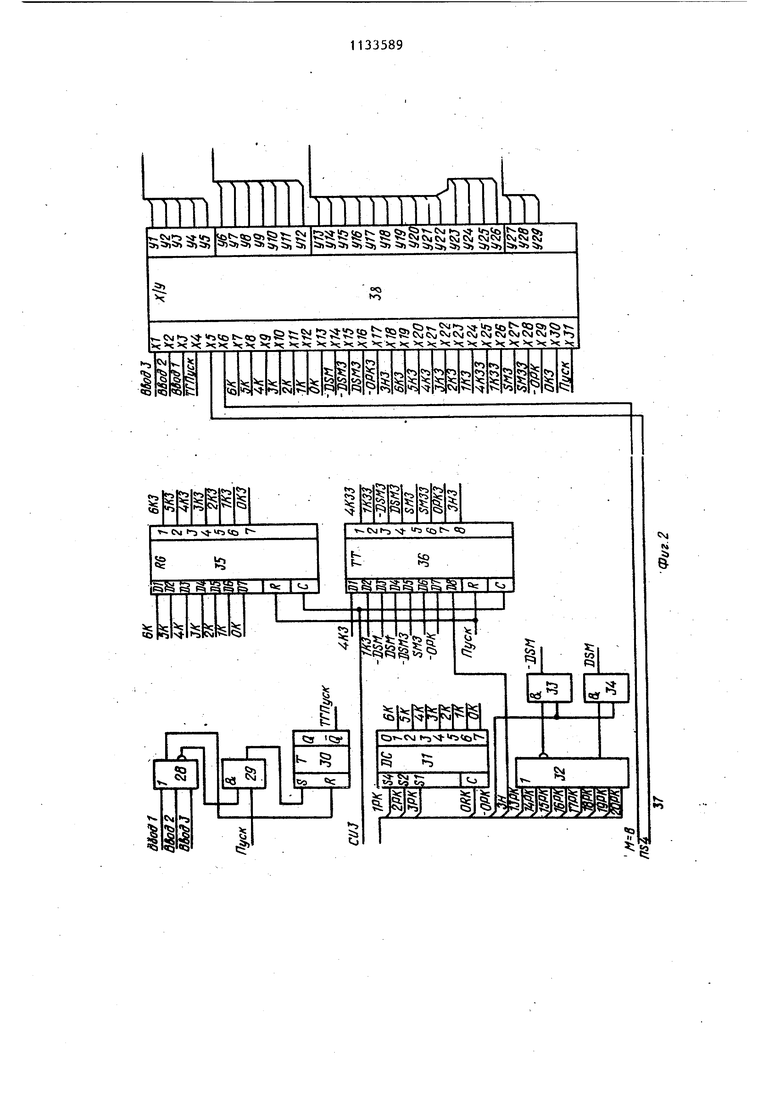

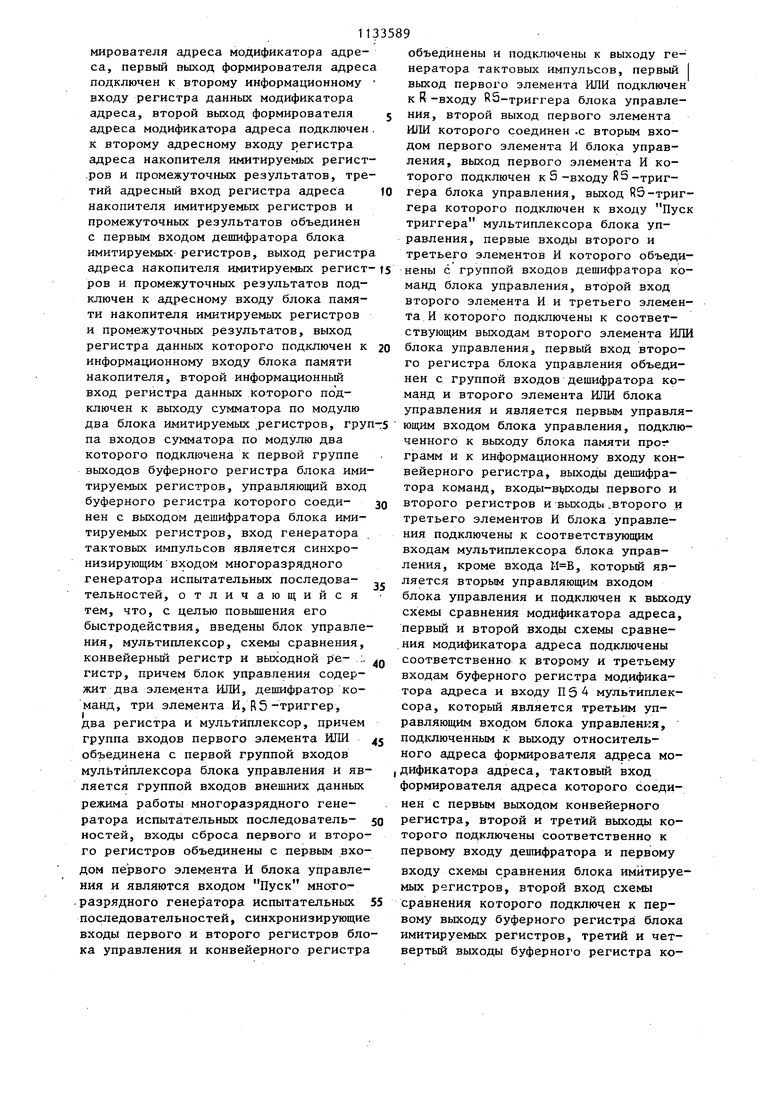

Изобретение относится к вычислительной технике и может быть использовано в качестве датчика входных наборов в устройствах автоматизированного контроля сложных цифровых узлов. Известен программируемый генерато псевдослучайных последовательностей содержащий имитатор регистра сдвига-накопитель,блок памяти программ и блок модификации адреса - сумматор обеспечивающий имитацрпо сдвига при очередном обращении к запоминающему устройству с произвольной выборкой Недостатком этого устройства являются низкие функциональные возможности, обусловленные тем, что за время вьшолнения Программы ЗУПВ может имитировать один регистр сдвига с заданными обратными связями о ( Наиболее близким к предлагаемому устройству являетсямногофункциональный генератор двоичных последовательностей, содержащий генератор тактовых импульсов и последовательно соединенные блок памяти программ мо ификатор адреса, блок памяти для хранения значений разрядов имитируемых .регистров сдвига, и выходной регистр с сумматором обратной связи, выход которого через мультиплексор подключен к входу данных блока памятиНедостатками известного устройства являются низкое быстродействие, необходимость большого числа команд при организации регистров, работающих с разными частотами сдвигов, а также невозможность формирования произвольных булевских функций от заданных разрядов регистрао Целью изобретения является повышение быстродействия устройства. Указанная цель достигается тем, что в многоразрядный генератор испытательных последовательностей, содержащий блок памяти программ, модификатор адреса, накопитель имитируемых регистров и промежуточных ре--/ зультатов, блок имитируемых регистров и генератор тактовых импульсов, при этом модификатор адреса содержит регистр адреса, регистр данных, два блока памяти, буферный регистр и формирователь адреса, блок имитируемых регистров содержит дешифратор, буферный регистр и сумматор по модулю два, накопитель имитируемых регистров и промежуточных результатов содержит регистр адреса, регистр данных .и блок памяти, при этом адресный вход блока памяти программ объединен с первым адресным входом регистра гдреса модификатора адреса, с первьм адресным входом регистра адреса накопителя имитируемых регистров и промежуточных результатов и является входом внешнего адреса многоразрядного генератора испытательных последовательностей, информационный вьгход блока памяти программ подключе к второму адресному входу регистра адреса модификатора адреса, стробиру ющие входы записи блока памяти накопителя имитируемых регистров и промежуточных результатов и блоков памяти модификатора адреса объединены с первым стробирующим входом блока памяти программ и подключены к первому выходу генератора тактовых импульсов, входы синхронизации регис ров адреса и регистров данных модификатора адреса, накопителя имитируемых регистров и промежуточных результатов объединены с вторым синхронизИРутащим входом блока памяти программ и подключены к второму выходу генератора тактовых импульсов, входы синхронизации буферных регистров модификатора адреса и блока имитируемых регистров объединены с третьим синхронизирующим входом блока памяти программ и подключены к третьему выходу генератора тактовых импульсов, выход регистра адреса модификатора адреса подключен к адресным входам первого и второго блоков памяти модификатора адреса, информационный вход первого блока памяти мо дификатора адреса объединен с информ ционным входом блока памяти программ и первым информационным входом регистра данных модификатора адреса и. регистра данных накопителя имитируемых регистров и промежуточных результатов и является входом внешних данных многоразрядного генератора f испытательных последовательностей, выходы первого и второго блоков памя ти подключены к соответствующим информационным входам буферного регист ра модификатора адреса, первьш, второй и третий выходы буферного регист ра модификатора адреса подключены к входам данных адреса, начального адреса, адреса входного смещения формирователя адреса модификатора адреса, первый выход формирователя адреса подключен к второму информаци онному входу регистра данных модификатора адреса, второй выход формирователя адреса модификатора адреса подключен к второму адресному входу регистра адреса накопителя имитируемых регистров и промежуточньос ре-, зультатов, .третий адресный вход регистра адреса накопителя имитируемых регистров и промежуточных результатов объединен с первым входом дешифратора блока имитируемых регистров, выход регистра адреса накопителя имитируемых регистров и промежутрчных результатов подключен к адресному входу блока памяти накопителя имитируе- . мых регистров и промежуточных результатов, выход регистра данных которого подключен к информационному входу блока памяти накопителя, второй ин,формационный вход регистра данных которого подключен к выходу сумматора по модулю два блока имитируемых регистров, группа входов сумматора по модулю два которого подключена к первой группе выходов буферного регистра блока имитируемых регистров, управляющий вход буферного регистра которого соединен с выходом .дешифратора блока имитируемых регистров, вход генератора тактовых импульсов является синхронизирующим входом многоразрядного генератора испытательных последовательностей, введены блок управления, мультиплексор, схемы сравнения, конвейерный регистр и выходной регистр, причём блок управления содержит два элемента ИЛИ, дешифратор команд, три элемента И,R5 триггер, два регистра и мультиплексор, причем группа входов первого элемента ИЛИ объединена с первой группой входов мультиплексора блока управления и является входами внешних данных режима работы многоразрядного генератора испытательных -последовательностей, входы сброса первого и второго регистров объединены с первым входом первого элемента И.блока управления и являются входом Пуск многоразрядного генератора испытательных последовательностей, синхронизирующие входы первого и второго регистров блока управления и конвейерного регистра объединены и подключены к третьему выходу генератора тактовых импульсов, первый выход первого элемента ИЛИ. подключен к R -вхоу R5-триггера блока управления, второй выход первого элемента ИЛИ которого соединен с вторым входом первого элемента И блока управления. S 113 выход первого элемента И которого подключен к 6-входу R5 -триггера блока управления, выход Й5-триггера которого подключен к вхаду Пуск триггера мультиплексора блока управления, первые входы вт орого и третьего элементов И которого объединены с группой входов дешифратора команд блока управления, вторые входы второ го элемента И и третьего элемента И которого подключены к соответству- ющим выходам второго элемента ИЛИ блока управления, первый вход второго регистра блока управления объединен с группой входов дешифратора команд и второго элемента ШШ блока управления и является первьм управляющим входом блока управления, подключенного к выходу блока памяти программ и 1 информационному входу конвейерного регистра, выходы дешифратора команд, входы-выходы .первого и второго регистров и выходы второго и третьего элементов И блока управления подключены к соответствующим входам мультиплексора блока управления, кроме входа , который является вторым управляющим входом бло ка управления- и подключен к выходу схемы сравнения модификатора адреса, первый и второй входы схемы сравнени модификатора адреса подключены соответственно к второму и третьему выходам буферного регистра модификатора адреса и входу П S 4 мультиплексора, которьш является третьим управляющим входом блока управления, подключенным к выходу относительного ад реса формирователя адреса модификатора адреса, тактовый вход формирова теля адреса которого соединен с первым выходом конвейерного регистра, второй и третий выходы которого под ключены соответственно к первому вх ду дешифратора и первому входу схеIмы сравнения блока имитируемых реги ров, второй вход схемы сравнения ко торого подключен к первому выходу буферного регистра блока имитируемы регистров, третий и четвертый выходы буферного регистра которого подключены соответственно к первому и второму входам выходного регистра, информационный вход буферного регис ра блока имитируе1Ф1х регистров - к выходу мультиплексора накопителя им тируемых регистров и промежуточных результатов, первая группа входов мультиплексора которого подключена к выходу блока памяти накопителя имитируемых регистров и промежуточных результатов, вторая группа входов мультиплексора которого подключена к третьему и четвертому входам регистра данных накопителя имитируемых регистров и промежуточных результатов и к выходу схемы сравнения блока имятируе№.1х регистров, управляющие входы мультиплексора, блока памяти, регистра адреса и регистра данных которого подключены к первой группе управляющих выходов мультиплексора блока управления, вторая группа вы- .ходов мультиплексора блока управле- . кия является вторым управляющим выходом блока управления и подключена к стробирующему входу дешифратора, единичному входу буферного регистра блока имитируемых регистров и третьему входу выходного регистра, синхронизирующий вход которого подключен к первому выходу генератора тактовых импульсов, выход выходного регистра является выходом многоразрядного генератора испытательных последовательностей, третья группа выходов мультиплексора блока управления является третьим управляющим выходом блока управления и подключена к управляющему входу блока памяти программ, четвертая группа выходов мультиплексора блока управления явля тся четвертым управляющим выходом управления и подключена к группе управляющих входов регистра данных, регистра адреса и к управляющим входам первого и второго блоков памяти модификатора адресао На фиг о 1 представлена структурная схема генератора; на фиг 2 структурная схема блока управления; на фиг. 3 - функциональная схема формирователя управляющих сигналов блока управления; на фиг. 4 - функциональная схема входного мультиплексора и счетчика адреса блока памяти программы; на фиг, 5 - функциональная схема регистров адреса и данных блоков памяти модификатора адреса; на фиг. 6- функциональная схема формирователя адреса; на фиг, 7 - функциональная схема накопителя имитируемых регистров с регистрами адреса и данных и выходным мультиплексором, Многоразрядный генератор со.стонт (фиг. 1) из блока 1 памяти программ,

блока 2 управления, модификатора 3 адреса, конвейерного регистра 4, наколителя 5 имитируемых регистров и промежуточньи результатов блока 6 имитируемых регистров, выходного ре- 5 гистра 7 и генератора 8 тактовых импульсов.

Блок 1 памяти программ содержит входной мультиплексор 9 адреса (из , двух направлений в одно), счетчик 10 Ю адреса, блок 11 памяти команд (ЗУПВ) и выходной регистр 12 команд.

Модификатор 3 адреса состоит из регистра 13 адреса и первого и второго блоков 14 и 15 памяти (ЗУПВ) и 15 регистра 16 данных, буферного регистра 17, формирователя 18 адреса и .схемы 19 сравнения.

Накопитель Ь имитируемых регистров содержит регистр 20 адреса, блок 20 21 памяти (ЗУПВ), регистр 22 данных с входными мультиплексорами, и мультиплексор 23 о

Блок 6 имитируемых регистров срдержйт .дешифратор 24 на N выходовrerj- 25 со стробированием, буферный регистр 25., состоящий из NDV-триггеров, управляющие входы которых V соединены с соответствующими выходами дешифратора, а информационные входы D 30 объединены и подключены к выходу Мультиплексора 23, схемы 26 сравнения двух В-разрядных кодов и четырехвхйдового сумматора 27 по модулю два.J5

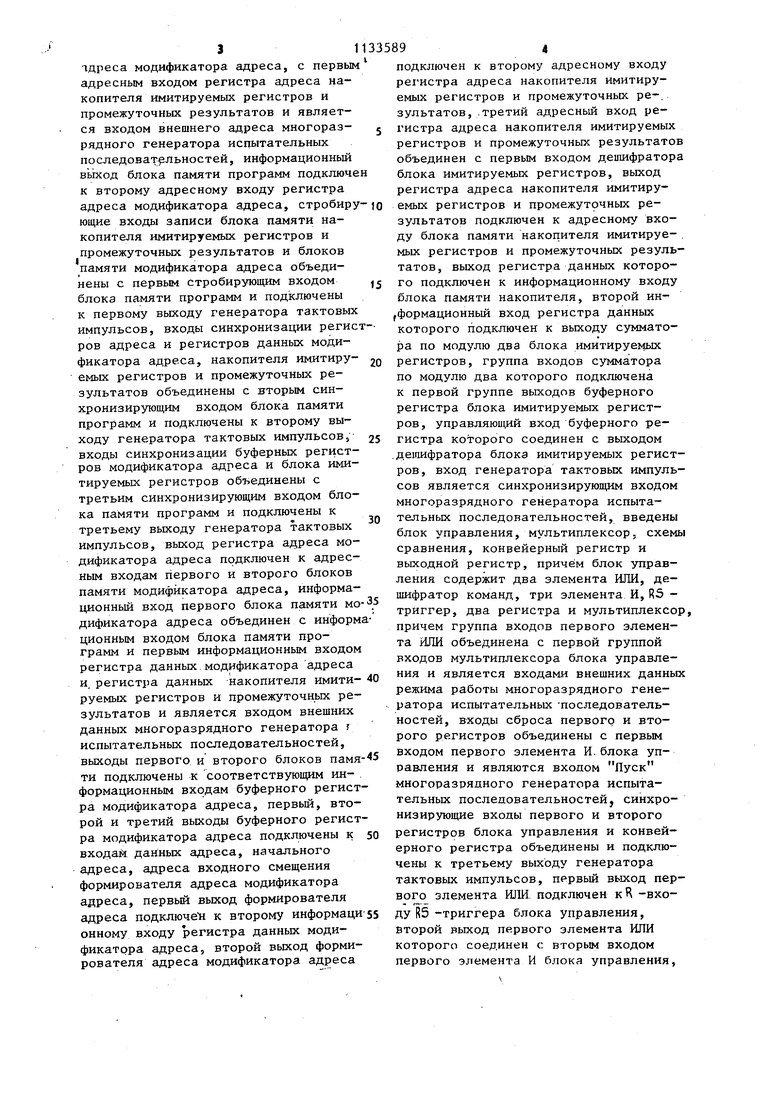

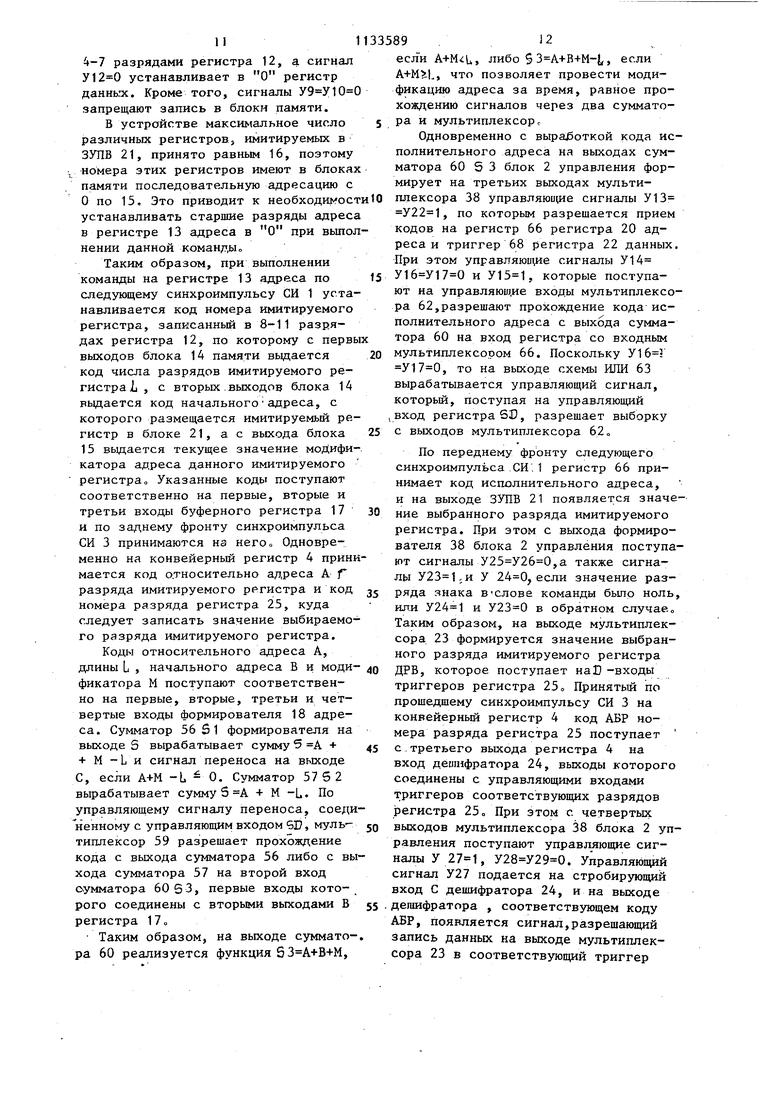

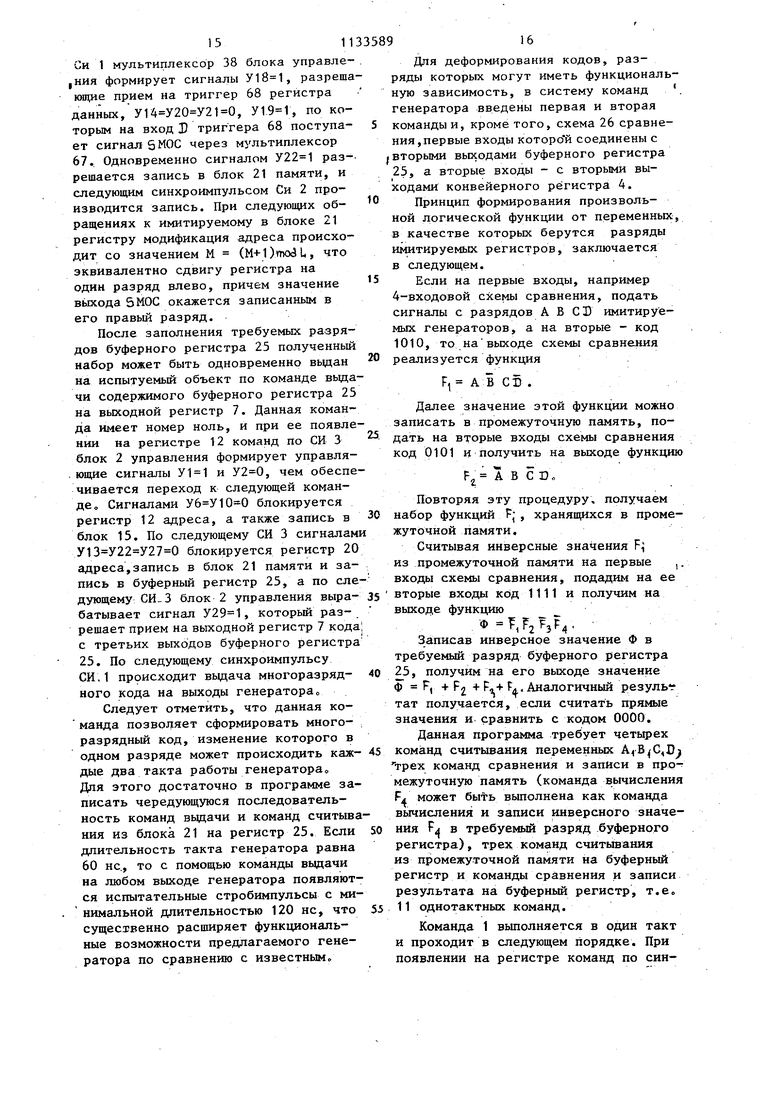

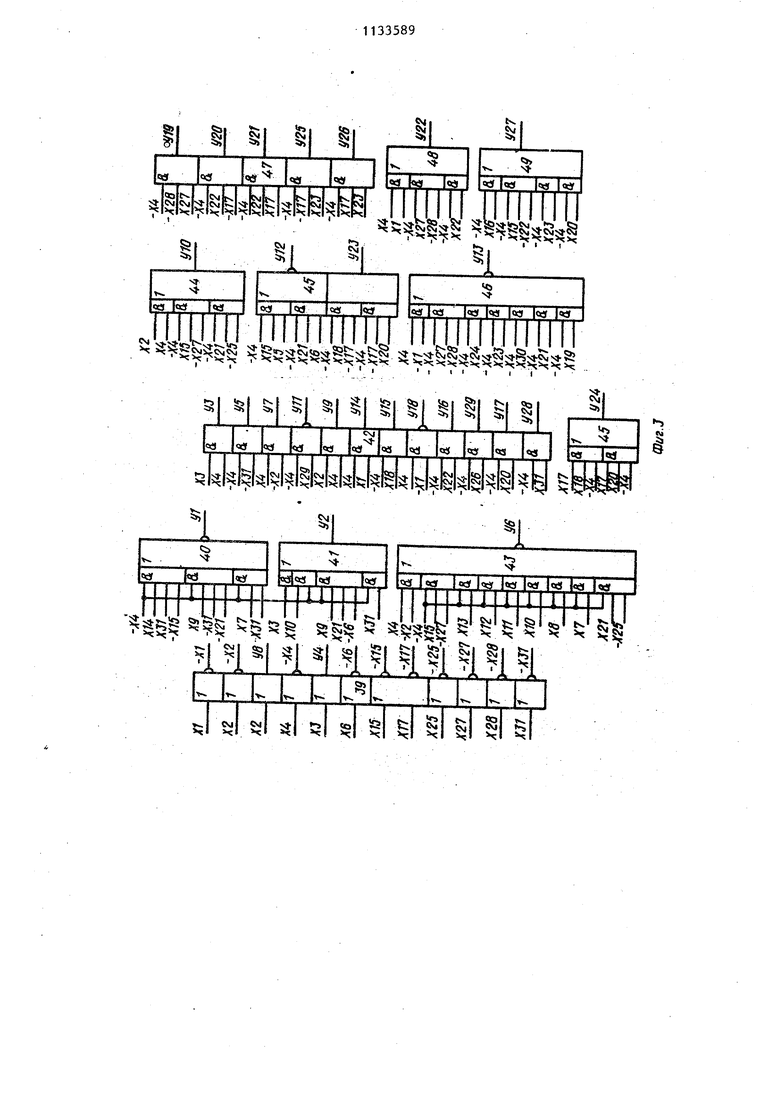

Блок управления (фиг 2) содержит элемент ИЛИ 28, элемент И 29, RS триггер 30, дешифратор 31 команд, элемент ИЛИ 32, являющийся дешифратором номера разряда регистра 25, соединенного с четвертым входом D сумматора 27 по модулю два, второй и третий двухвходовые элементы И 33 и 34, регистры 35 и 36, вход 37 и мультиплексор 38, который.содержит 45 (фиг о 3) инверторы 39, элементы ИШ1И 40 и 41, элемент И 42 и элементы И-ШШ 43-46, элемент И 47 и элементы И-Ш1И 48 и 49 двухвходовые„

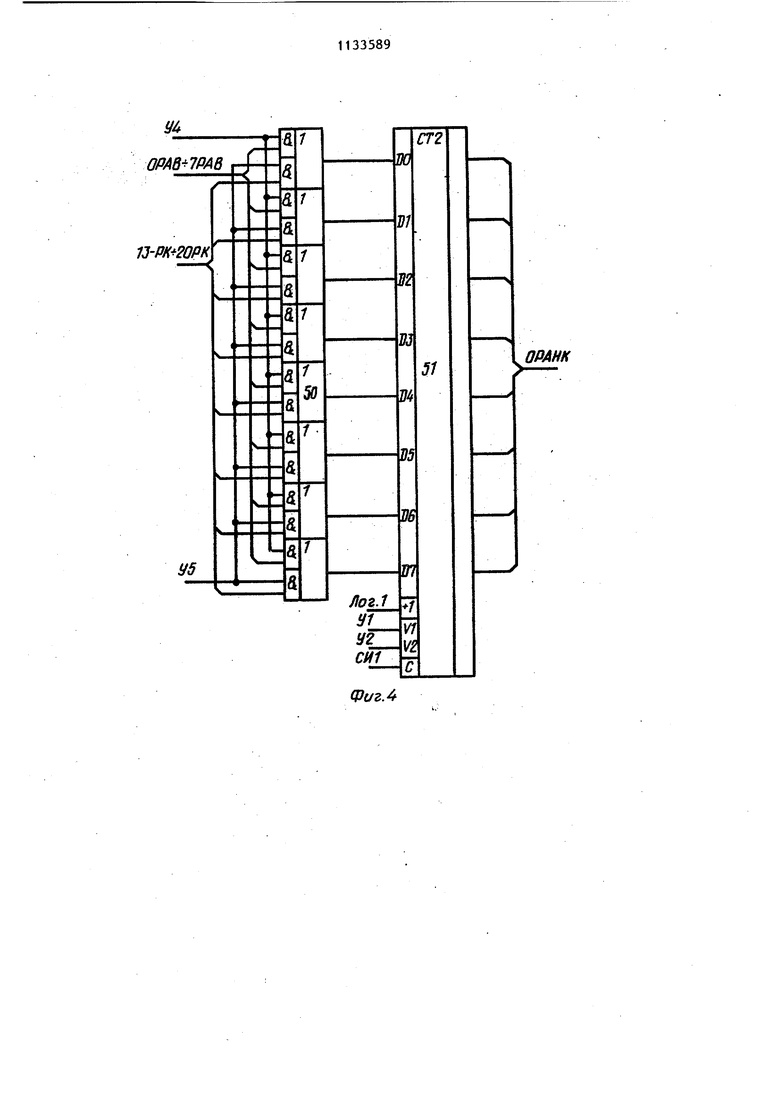

На фиг о 4 показан входной мульти- jg плексор 50 и счетчик 51 адреса.

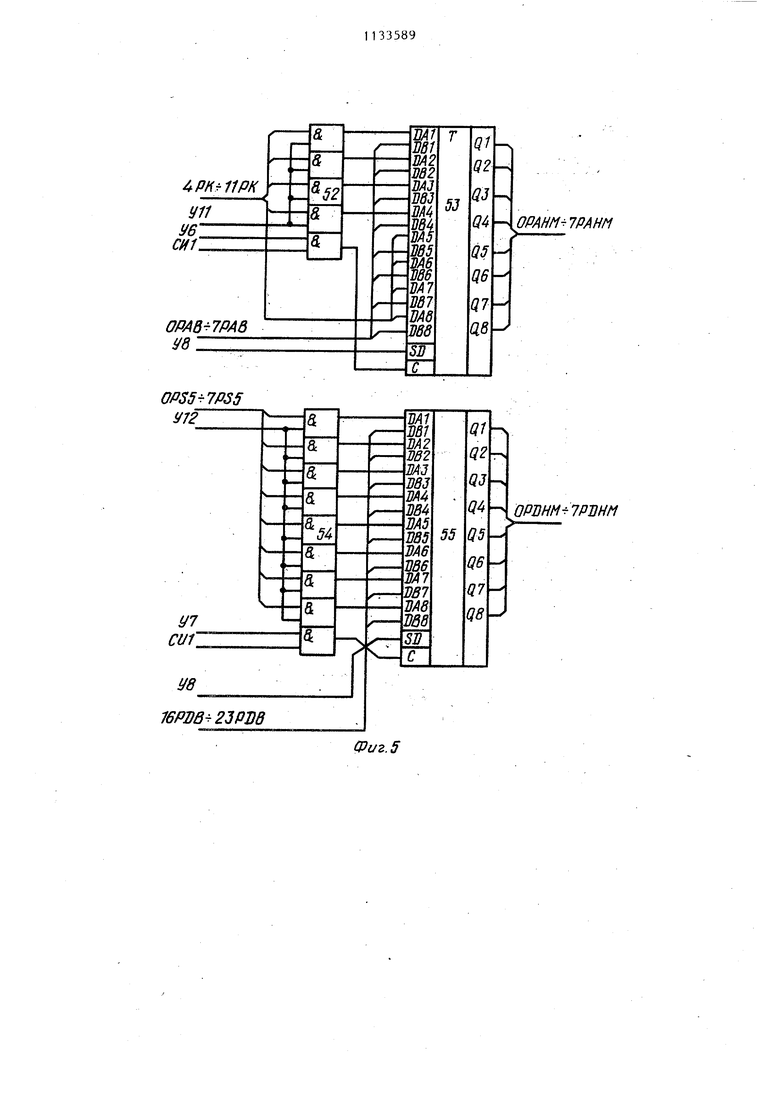

Регистры адреса -13 и данных 16 содержат (фиг. 5) двухвходовой элемент И 52 и регистры с входным мультиплексором 53, элемент И 54, мультиплек- 55 сор 55

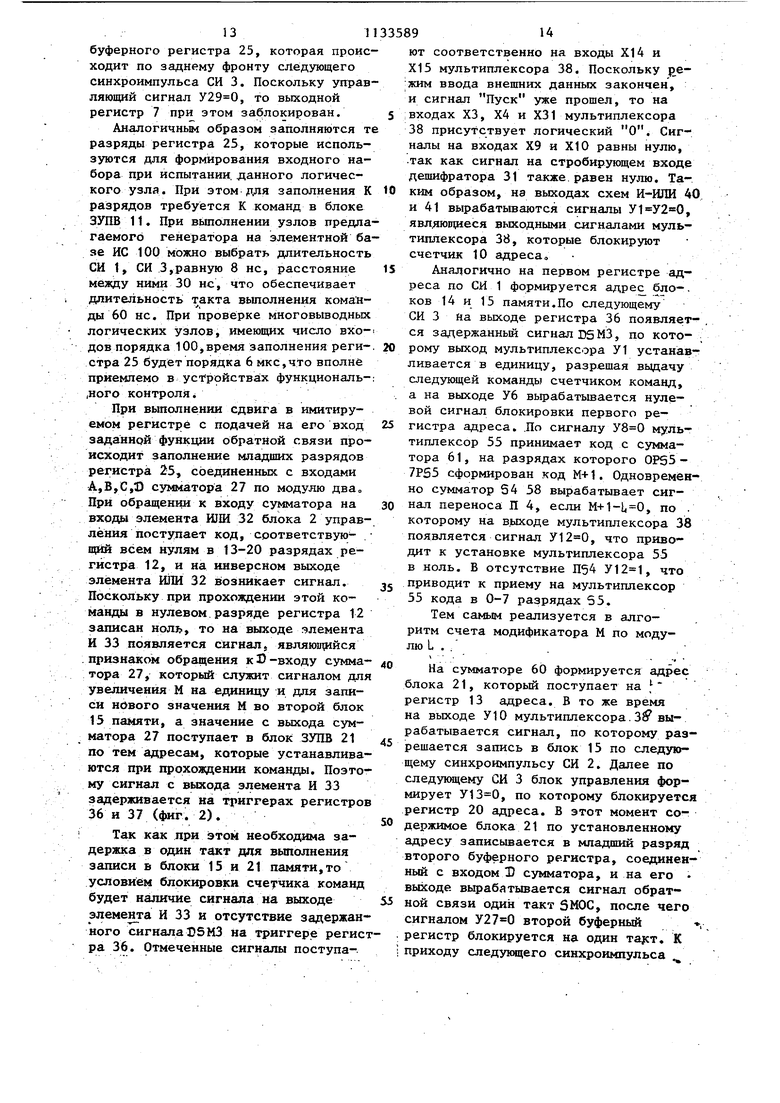

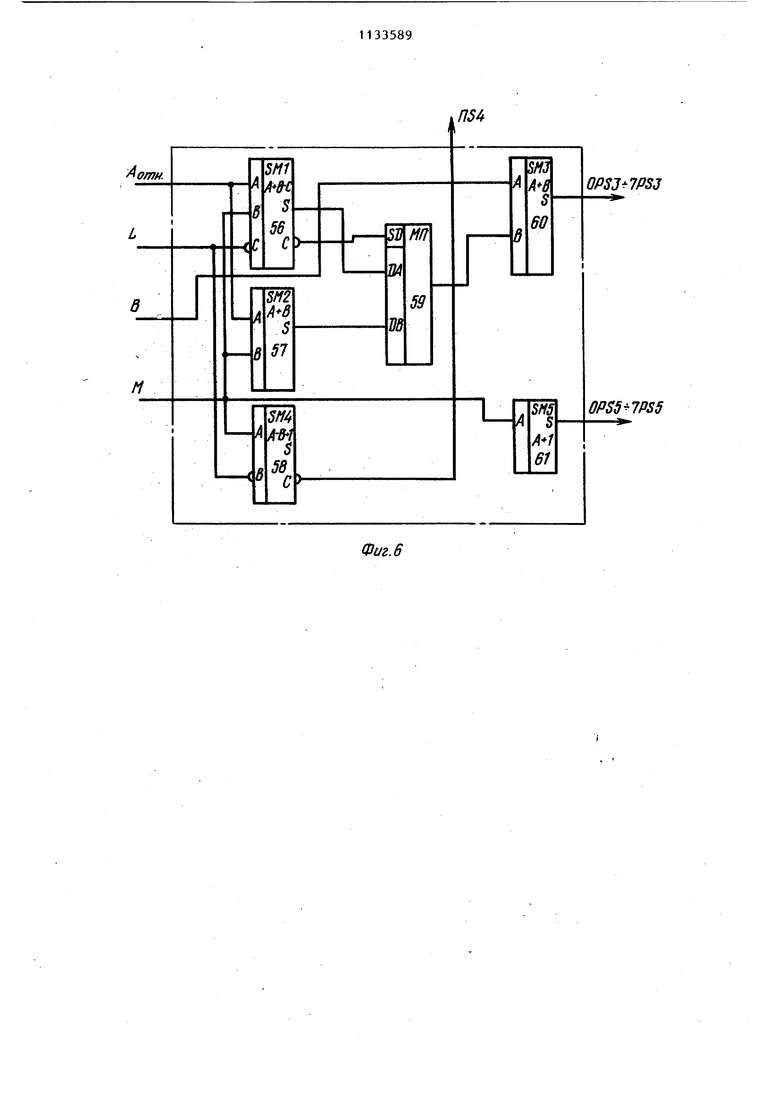

Формирователь адреса состоит (фиг, 6) из первого комбинационного

Iсумматора 56 на три входа, второго, ; третьего и четвертого двухвходовых сумматоров 57 и 58, мультиплексора 59, четвертого и пятого комбинационных сумматоров 60 и 61, осуществляющих сложение входного-кода с единицей о

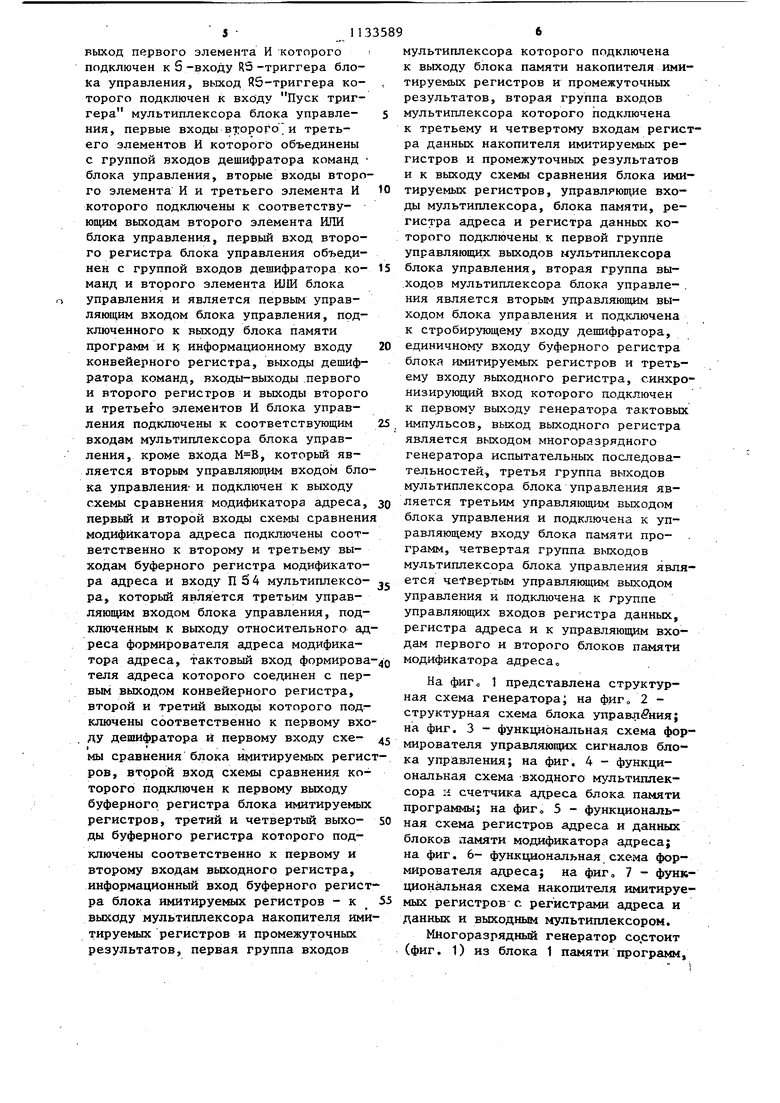

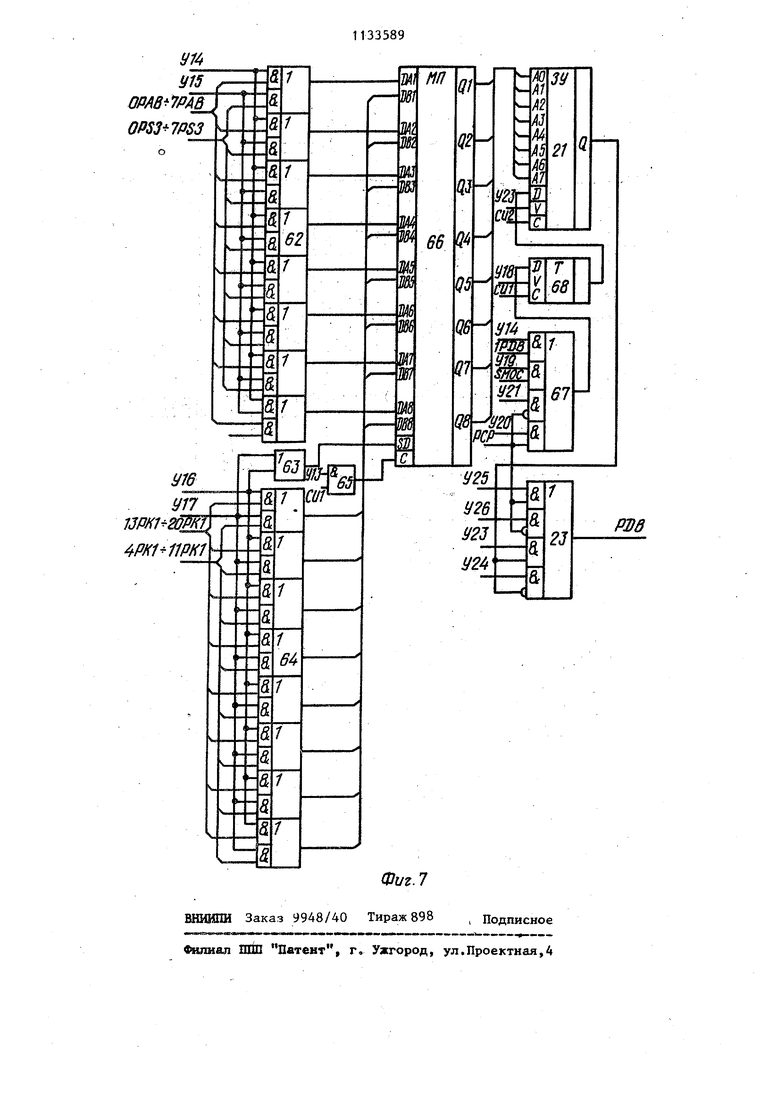

Регистры адреса и данных (фиг, 7) состоят из входного мультиплексора 62 из двух направлений в одно, элемента ИЛИ 63, мультиплексора 64, элемента И 65, регистра 66 адреса с входным мультиплексором, входного мультиплексора 67 данных из четырех направлений в одно и триггера 68 хранения данных.

Предлагаемое устройство работает следующим образом

Генератор имеет два режима работы ввод внешних данных и формирование на выходном регистре последовательности многоразрядных кодов

При вводе информации в ЗУПВ 11 по щине Ввод 1 в блок 2 управления подается сигнал, по которому блок управления формирует на первых выходах управляющие сигналы , , открывающие прохождение кода адреса на шине внешнего адреса АВ через мультиплексор 9 на входы параллельного приема счетчика 10. Одновременно по сигналам счетчик 10 переводится в режим параллельного приема и формирует адрес ЗУПВ 11, на., вход данных ко орого поступает код с шины внешних данных DB, а на вход управления - сигнал разрешения записи из блока 2. Генератор 8 тактовых импульсов вьщает трехфазную систему синхроимпульсов СИ1, СИ2 и СИЗ синхронно с внешними стробимпульсами, идущими по шине СВ. Код на шинах Ввод 1 - Ввод 3 АВ, ДВ, СВ. поступает с внешнего устройства или пульта управления (не показаны).

При записи в ЗУПВ 11 регистры 13, 16, 20, 22, 25 и 7 блокируются, а на управляюших входах ЗУПВ 14, 15 и 21 отсутствуют сигналы разрешения записи.

По окончании записи в ЗУПВ 11 сигнал Ввод 1 сни 4ается, подается сигнал Ввод 2 и происходит заполнение ЗУПВ 14 и 15. При этом блокируется зпись в ЗУПВ 11 и 21,- а также регистры 20, 22, 25 и 7 и счетчик команд. Аналогичным образом заполняется ЗУПВ 2.1 при поступлении сигнала 911 Ввод 3. В процессе записи наличие сигнала на любой из шин Ввод 1 Ввод 3 устанавливает Я5 -триггер 30 блока управления в О, выход которого поступает на вход мультиплексора 38, который вырабатывает сигналы управления .внешней записи. По окончании записи сигналы на шинах Ввод 1 - Ввод 3 устанавливается в О, и при появлении одиночного импульса Пуск триггер 30 устанавливается в 1, При этом на выходах мультиплексора 38 появляются сигналы , , по которым счетчик команд принимает нулевой код с выхода мультиплексора, чем осуществляется начальная установка счетчика. Одновременно на выходе мультиплексора 38 появляется сигнал , который, поступая на установочный 5-вход реустанавливает его триггеры гистра, в Из ЗУПВ 11 по адресу О выбирает ся команда, которая поступает на регистр 12 кс/манд. Разряды 0-3, 12-20 РК 12 поступают для анализа в блок управления, при этом разряды 0-3 РК 12 поступают на дешифратор 31 команд а 13-20 РК 12 - на элемент ИЛИ 32, сигнал на инверсном выходе которого тогда, кбгда код на разрядах 13-20 РК 12 равен нулю, т,е. соответ ствует номеру младшего разряда регис ра 25, соединенного с входом D сумматора 27. В тех случаях, когда код команды соответствует 0-2 либо 5 командам, либо идет двухадресная коман да записи разряда имитируемого регистра, хранящегосяв ЗУПВ 21, в регистр 25 без обращения к -входу сумматора 27, на выходах мультиплексора 38 вырабатываются сигналы , , которые, поступая на управляющие входы счетчика команд,переводят его в режим счета, и по следующему ,синхроимпульсу СИ 1 счетчик команд прибавит единицу, формируя следующий адрес для ЗУПВ 11 команд. В том случае, когда на регистр 12

выбирается двухадресная команда запи-50и, 15 и регистра 16 данных блока паси разряда имитируемого регистра измяти ЗЗТШ 15, По сигналу входшле ЗУПВ 21 в регистр 25 с обращением ко мультиплексоры подключ.а1:)т. входы ревходу U сумматора 27, либо 4-я коман-гистра 53 к выходам 4-11 разрядов Да условного перехода, на выходахрегистра 12, а входь регистра 55 к У1, У2 мультиплексора 38 вырабатыва- 55вторым выходам формирователя 18 адются единичные сигналы, по которым счетчик 10 переводится в режим параллельного приема. Одновременно на выреса. При этом сигнал устанавливает в О старшие разряды регистра адреса, соединенные соответственно ci 9 ходе У5 мультиплексора 38 вырабатывается единичный сигнал, разрешающий прохождение через входной мультиплексор 50 кода с 13-20 разрядов регистра 12, и по следующему синхроимпульсу СИ 1 счетчик 10 устанавливается в состояние, соответствующее коду, записанному в указанных разрядах слова команды. При поступлении на дешифратор . команд кода 6-й команды мультиплексор 38 вырабатьшает на выходах У1, У2 нулевые сигналы, блокирующие счетчик команд, чем осуществляется останов генератора. Таким образом, при работе генератора выполняются следующие операции. Двухадресная команда вьщачи А разряда Н имитируемого регистра, хранящегося в 35ППВ 21, на буферный регистр 25 по адресу АБР без обращения к входу D сумматора 27. Данная команда имеет признак О в нулевом разряде слова команды и выполняется в следующей последовательности. По синхроимпульсу СИ 1 на счетчике 10 формируется адрес ЗУПВ 11 и выбираемая команда поступает на регистр команд РК 12, который принимает слово команды по синхроимпульсу СИ 3. Блок управления 2 анализирует состояние регистра 12. Поскольку нулевой разряд регистра 12 содержит О, и на выходе элемента ШШ 32 сигнал отсутствует, то мультиплексор 38 вырабатывает иа первой группе выходов следующие сигналы: , У2-У4 0, . Сигналы У1, У2 разрешают прибавление единищл в счетчике 10, сигнал УЗ.блокирует запись команд в память ЗУПВ 11. Комбинация сигналов , в данном случае несущественна, так как запись в ЗУПВ Ь1 не разрешена Одновременно на второй группе выходов мультиплексора 38 вырабатываются управляющие сигналы для модификатора 3 У6-У12. Сигналы У6, снимают блокировку регистра 13 адреса блоков памяти ЗУПВ 14 4-7 разрядами регистра 12, а сигнал устанавливает в О регистр даяньж. Кроме того, сигналы запрещают запись в блоки памяти. В устройстве максимальное число различных регистров, имитируемых в ЗУПВ 21, принято равным 16, поэтому номера этих регистров имеют в блока памяти последовательную адресацию с 0 по 15, Это приводит к необходимос устанавливать старшие разряды адрес в регистре 13 адреса в О при выпо нении данной команды Таким образом, при выполнении команды на регистре 13 адреса по следующему синхроимпульсу СИ 1 уста навливается код номера имитируемого регистра, записанный в 8-11 разрядах регистра 12, по которому с перв выходов блока 14 памяти вьщается код числа разрядов имитируемого регистра L , с вторых.выходов блока 14 выдается код начальногоадреса, с которого размещается имитируемый ре гистр в блоке 21, ас выхода блока 15 выдается текущее значение моДифи катора адреса данного имитируемого регистра. Указанные коды поступают соответственно на первые, вторые и третьи входы буферного регистра 17 и по заднему фронту синхроимпульса СИ 3 принимаются на него Одновременно на конвейерный регистр 4 прин мается код относительно адреса А f разряда имитируемого регистра и код номера разряда регистра 25, куда следует записать значение выбираемо го разряда имитируемого регистра. Коды относительного адреса А, длины L , начального адреса В и моди фикатора М поступают соответственно на первые, вторые, третьи и четвертые входы формирователя 18 адреса. Сумматор 56 51 формирователя на выходе 5 вырабатывает сумму + + М -L и сигнал переноса на выходе С, если А+М -L - 0. Сумматор 5762 вырабатывает сумму + М -L. По управляющему сигналу переноса, соеди ненному с управляющим входом 5Г, мультиплексор 59 разрещает прохождение кода с выхода сумматора 56 либо с вы хода сумматора 57 на второй вход сумматора 6053, первые входы которого соединены с вторыми выходами В регистра 17о Таким образом, на выходе сумматора 60 реализуется функция 53 А+В+М, 8912 если , либо 5 3 A+B+M-if, если А+МЯ,, что позволяет провести модификацию адреса за время, равное прохождению сигналов через два сумматора и мультиплексор с Одновременно с выработкой кода исполнительного адреса на выходах сумматора 60 5 3 блок 2 управления формирует на третьих выходах мультиплексора 38 управляющие сигналы У13 , по которым разрещается прием кодов на регистр 66 регистра 20 адреса и триггер 68 регистра 22 данных. При этом управляющие сигналы У14 и , которые поступают на управляющие входы мультиплексора 62,разрешают прохождение кода исполнительного адреса с выхода сумматора 60 на вход регистра со входным мультиплексором 66. Поскольку У16 , то на выходе схемы ИЛИ 63 вырабатывается управляющий сигнал, который, поступая на управляющий вход регистра SD, разрешает выборку с выходов мультиплексора 62 По переднему фронту следующего синхроимпульса СИ.1 регистр 66 принимает код исполнительного адреса, и на выходе ЗУПВ 21 появляется значение выбранного разряда имитируемого регистра. При этом с выхода формирователя 38 блока 2 управления поступают сигналы ,а также сигналы ,и У значение разряда знака вСлове команды бьшо ноль, или и в обратном случае Таким образом, на выходе мультиплексора 23 формируется значение выбранного разряда имитируемого регистра ДРВ, которое поступает наС -входы триггеров регистра 25 Принятый по прошедшему синхроимпульсу СИ 3 на конвейерный регистр 4 код АБР номера разряда регистра 25 поступает с третьего выхода регистра 4 на вход дешифратора 24, выходы которого соединены с управляющими входами триггеров соответствующих разрядов регистра 25 При этом с четвертых выходов мультиплексора 38 блока 2 управления поступают управляющие сигналы У , . Управляющий сигнал У27 подается на стробирующий вход С дешифратора 24, и на выходе дешифратора , соответствующем коду БР, появляется сигнал,разрешающий запись данных на выходе мультиплексора 23 в соответствующий триггер буферного регистра 25, которая происходит по заднему фронту следующего синхроимпульса СИ 3. Поскольку управ ляющий сигнал , то выходной регистр 7 при этом заблокирован. Аналогичным образом заполняются т разряды регистра 25, которые используются для формирования входного набора при испытании, .данного логического узла. При этом для заполнения К разрядов требуется К команд в блоке ЗУПВ 11. При выполнении узлов предла гаемого генератора на элементной ба зе ИС 100 можно выбрать длительность СИ 1, СИ 3,равную 8 не, расстояние между ними 30 НС, что обеспечивает длительность такта выполнения команды 60 НС. При проверке многовыводных логических узлов, имеющих число входов порядка 100,время заполнения регистра 25 будет порядка 6 мкс,что вполне приемлемо в устройствах функциональ,ного контроля i При выполнении сдвига в имитируемом регистре с подачей на его вход заданной функции обратной связи происходит заполнение младших разрядов регистра 25, соединенных с входами А,ВуС,1Э сумматора 27 по модулю два При обращении к входу сумматора на входы элемента И1Ш 32 блока 2 управления поступает код, соответствующйй всем нулям в 13-20 разрядах регистра 12, и на инверсном выходе элемента ШШ 32 возникает сигнал. Поскольку при прохождении этой команды в нулевом разряде регистра 12 записан ноль, то на выходе элемента И 33 появляется сигнал, являющийся признаком обращения к D-входу сумматора 27, который служит сигналом для увеличения М на единицу и для записи нового значения М во второй блок 15 памяти, а значение с выхода сумматора 27 поступает в блок ЗУПВ 21 по тем адресам, которые устанавливаются при прохождении команды. Поэтому сигнал с выхода элемента И 33 задерживается на триггерах регистров 36 и 37 (фиг. 2). Так как при этом необходима задержка в один такт для выполнения записи в блоки 15 и 21 памяти,то условием блокировки команд будет наличие сигнала на выходе элемента И 33 и отсутствие задержанного сигналаВбМЗ на триггере регис ра 36. Отмеченные сигналы поступают соответственно на входы XI4 и Х15 мультиплексора 38. Поскольку ежим ввода внешних данных закончен, и сигнал Пуск уже прошел, то на входах ХЗ, Х4 и Х31 мультиплексора 38 присутствует логический О. Сигналы на входах Х9 и XIО равны нулю, .так как сигнал на стробирующем входе дешифратора 31 также равен нулю. Таким образом, на выходах схем И-ШШ 40 и 41 вырабатываются сигналы , являющиеся выходными сигналами мультиплексора 38, которые блокируют счетчик 10 адреса. Аналогично на первом регистре яд- раса по СИ 1 формируется адрес бло-. ков 14 и 15 памяти.По следующему СИ 3 На выходе регистра 36 появляется задержанный сигнал DSM3, по кото- , рому выход мультиплексора У1 устанавливается в единицу, разрешая выдачу следующей команды счетчиком команд, а на выходе У6 вьфабатывается нулевой сигнал блокировки первого регистра адреса. .По сигналу мультиплексор 55 принимает код с сумматора 61, на разрядах которого ОР557PS5 сформирован код М+1. Одновременно сумматор 54 58 вырабатывает сигнал переноса П 4, если , по . которому на в.ыходе мультиплексора 38 появляется сигнал , что приводит к установке мультиплексора 55 в ноль. В отсутствие П54 , что приводит к приему на мультиплексор 55 кода в 0-7 разрядах 55. Тем реализуется в алгоритм счета модификатора М по модулю L .. 1 - . .... На сумматоре 60 формируется адрес блока 21, которьш поступает на f регистр 13 адреса. В то же время на выходе У10 мультиплексора.3 вырабатывается сигнал, по которому разрешается запись в блок 15 по следующему синхроимпульсу СИ 2. Далее по следукнцему СИ 3 блок управления формирует , по которому блокируется регистр 20 адреса. В этот момент содержимое блока 21 по установленному адресу записывается в младший разряд второго буферного регистра, соединенный с входом) сумматора, и на его выходе вырабатывается сигнал обратной связи один такт Sмое, после чего сигналом второй буферный , регистр блокируется на один та|ст, К приходу следующего синхроимпульса 1511 Си 1 мультиплексор 38 блока управле,ния формирует сигналы , разреша ющие прием на триггер 68 регистра данных/ , , по которым на вход D триггера 68 поступает сигнал Sмое через мультиплексор 67.. Одновременно сигналом разрешается запись в блок 21 памяти, и следующим синхроимпульсом Си 2 производится запись. При следующих обращениях к имитируемому в блоке 21 регистру модификация адреса происходит со значением М (M+1),, что эквивалентно сдвигу регистра на один разряд влево, причем значение вькода 5мое окажется записанным в его правый разряд. После заполнения требуемых разрядов буферного регистра 25 полученный набор может быть одновременно выдан на испытуемьй объект по команде вьща чи содержимого буферного регистра 25 на выходной регистр 7. Данная команда имеет номер ноль, и при ее появле нии на регистре 12 команд по СИ 3 блок 2 управления формирует управля. ющие сигналы У1 1 и , чем обеспе чивается переход к следующей команде. Сигналами блокируется регистр 12 адреса, а также запись в блок 15. По следующему СИ 3 сигналам блокируется регистр 20 адреса,запись в блок 21 памяти и запись в буферный регистр 25, а по сле дующему СИ. 3 блок 2 управления вырабатывает сигнал , который разрешает прием на выходной регистр 7 кода с третьих выходов буферного регистра 25. По следующему синхроимпульсу СИ.1 происходит выдача мнохоразрядного кода на выходы генераторао Следует отметить, что данная команда позволяет сформировать многоразрядный код, изменение которого в одном разряде может происходить каждые два такта работы генератора Для этого достаточно в программе записать чередующуюся последовательность команд вьщачи и команд считыва ния из блока 21 на регистр 25. Если длительность такта генератора равна 60 НС., то с помощью команды выдачи на любом выходе генератора появляются испытательные стробимпульсы с минимальной длительностью 120 не, что существенно расширяет функциональные возможности предлагаемого генератора по сравнению с известным 9 Для деформирования кодов, разряды которых могут иметь функциональную зависимость, в систему команд . генератора введены первая и вторая команды и, кроме того, схема 26 сравнения,первые входы которой соединены с вторыми выходами буферного регистра 25, а вторые входы - с вторыми выходами конвейерного регистра 4. Принцип формирования произвольной логической функции от переменных, в качестве которых берутся разряды имитируемых регистров, заключается в следующем. Если на первые входы, например 4-входовой схемы сравнения, подать сигналы с разрядов А В СЗ) имитируемых генераторов, а на вторые - код 1010, то навыходе схемы сравнения реализуется функция F, А В С5 . Далее значение этой функции можно записать в промежуточную память, подать на вторые входы схемы сравнения код 0101 и получить на выходе функцию А В С О, Повторяя эту процедуру, получаем набор функций FJ, хранящихся в промежуточной памяти. Считывая инверсные значения F из промежуточной памяти на первые ,. входы схемы сравнения, подадим на ее вторые входы код 1111 и получим на выходе функцию . Ф Записав инверсное значение Ф в требуемый разряд буферного регистра 25, получим на его выходе значение Ф F, + F + F, Рд. Аналогичный резуль- тат получается, если считать прямые значения и сравнить с кодом 0000. Данная программа требует четырех команд считывания переменных трех команд сравнения и записи в промежуточную память (команда вычисления FX может быть выполнена как команда вычисления и записи инверсного значения FJ в требуемый разряд буферного регистра), трех команд считывания из промежуточной памяти на буферный регистр и команды сравнения и записи результата на буферньй регистр, т.е 11 однотактных команд. Команда 1 вьшолняется в один такт и проходит в следующем порядке. При появлении на регистре команд по сиихроимпульсу СИ 3 кода первой команд блок 2 управления на первых выходах мультиплексора 38 вырабатывает управляющие сигналы , , по которым счетчик 10 адреса устанавливается в режим счета, , чем блокируется запись в блок 11 памяти, значения сигналов и при этом несущественно для прохождения команд На второй группе выходов мультиплексора 38 вырабатываются сигналы управления модификатором 3 адреса , . По сигналу . блокируется регистр 13 адреса, а сигналами запрещается запись в блоки 14 и 15 памяти Остальные сигналы . У7, У8, У11 и У12 при этом несущественны. По следующему синхроимпульсу СИ 3 происходит передача содержимого регистра команд на конвейерный регистр 4„ Одновременно блок управления вырабатывает сигначы У13 0, , по которым блокируется регистр 20 адреса и запись в блок 21 памяти, и сигналы и , есл значения разряда знака , или и , если значение разряда знака , при этом Тем самым мультиплексор 23 рйзре-, шает прохождение прямрго либо инверсного результата сравнения на выходе схемы 26 сравнения на информационный вход второго буферного регистра 25, Одновременно на стробирующий вход дешифратора 24 приходит разрешающий сигнал , на. информационные входы - код с третьих выходов конвей ерного регистра 4, а на вторые входы схемы сравнения - код с вторых выходов регистра 4 Тем самым к моменту прихода следующего синхроимпульса СИ 3 на V -вхо соотве;тствующего триггера регистра 25 поступает разрешающий сигнал, а ,к HaD-вход - прямой либо инвертирован ный результат сравнения кода на первых входах схемы 26 с кодом на вторы выходах регистра 4. По заднему фронту СИ 3 результат записывается в выб раннь триггер регистра 25. Команда 2 выполняется в следующем порядке. После приема по заднему фронту СИ 3 команды на регистр 12 команд блок 2 управления сигналами , подготавливает счетчик команд к выборке следующей по порядку команды, а по блокируется запись в блок 11 памяти. Одновременно вырабатьшаются сигналы , по которым блокируется регистр 13 адреса и запись в блоки 14 и 15. По заднему фронту следующего СИ 3. содержимое регистра 12 принимается на регистр 4, а блок 2 управления вырабатывает , и , по которым регистр 20 адреса принимает код с третьих выходов регистра 4 о Одновременно на вторые входы схемы 26 сравнения поступает код с вторых выходов регистра 4, результат сравнения поступает на вход мультиплексора 67 регистра 22 данных, С выхода мультиплексора 38 блока 2 управления на управляющие входы триггера 68 приходит разрешающий сигнал , а на входы мультиплексора 67- сигналы и , если записывается прямое значение результата сравнения, и , - если инверсное. По следующему синхроимпульсу СИ 1 регистр 66 и триггер 68 принимают значение адреса и данных для блока 21. При этом на вход блока 21 поступает разрешающий сигнал , и по следующему синхроимпульсу СИ 2 происходит запись в блок 21 памяти. Вместе с тем , чем обеспечивается блокировка регистров 25 и 7. Третья и четвертая команды являются командами безусловного и условного перехода. Введение ихв состав команд генератора обеспечивает организацию циклов в программе, что позволяет существенно сэкономить память 11 команд при: имитации регистров, работающих с различными частотами сдвигов. Команда 3 выполняется следующим образом. При поступлении на регистр 12 команд кода команды по синхроимг.у I ,.L:4 A- fitffJ .AKAAA.IJ lli .ЯЛЛЛл. k СИ 3 на выходе мультиплексо 38 блока 2 управления вырабатываются управляющие сигналы и , которыми счетчик команд переводится в режим приема данных с выхода мультиплексора 9, а запись в память 11 команд блокируется, Управляющие сигналы и разрешают прохождение кода следующей команды с регистра команд на выход мультиплексора 50 (фиг. 4). Одновременно вырабатываются сигналы , блокирующие регистр 13 адреса и запись в блоки 14 и 15. По следующему СИЛ счетчик 10 адреса принимает код с регистра команд. По следующему СИ 3 вырабатываются сигналы 0, блокирующие регистр 20 адреса и запись в блок 21 памяти, а также , поступающий на С-вход дешифра тора 24, блокируя тем с:амым запись в регистр 25о По следующему СИ 3 сигналом запрещается прием на выходной регистр 7о Команда 4 выполняется в два такта поскольку необходимо время на форми-т рование условия перехода. При вводе данных в блок 14 по выбранному адресу записывается код конечного значений счетчика циклов В, а в блок 15 по тому же адресу - начальный нулево код счетчика циклов М 0„ Таким, образом, счетчиком циклов является слово с данным адресом в блоке 15. При поступлении на регистр 12 кода /команды по СИ 3 блок 2 управления вырабатывает и , чем блокирует счетчик 10 адреса и запись в блок 11. Одновременно формируются , , , . Сигналами У6 и У7 разрешается прием на регистр 53 регистра 13 адреса и мультиплексор 55 регистра 16 данных, йигналами У8, УНуИ У12 разрешается прохождени на триггера регистра 53 кода с 4-11 разрядов регистра команд, а на триггера регистра 55 - кода с выхода сумматора бЪ 5 0-7Р55, По следующему СИ 1 на регистр адреса принимается адрес слова в блоках 14 и 15, в котором записано конечное состояние счетчика циклов В и его текущее значение М. Эти данные поступают соответственно на второй и третий входы буферного регистра 17 и по заднему фронту следующего синхроимпульса СИ 3 запоминаются на нем. Одновремен но блок управлениявырабатывает сигналы , блокирующие регистр 20 адреса, запись в блок 21 и в регистр 25,и сигнал У ,разрешающий запись в блок 15.При этом на первых , входах схемы 19 сравнения находится код конечного состояния счетчика цик лов, а на вторых входах - код текущего значения Если эти коды совпадают (), то выходной сигналсхемы 19 сравнения, поступающий в блок 2 управления приводит к вьфаботке управляющих сигна лов У , У2 ОиУ12 0,так что по следую 1 920 щему СИ 1 счетчик 10 адреса прибавит единицу, а на мультиплексор 55 примется нулевой код В обратном случае () , , , , а на счетчик 10 адреса примется код с регистра 12, а на мультиплексор 55 код М + 1, сформированный на выходе сумматора 615 5. По следующему СИ 2 происходит запись нового значения счетчика циклов в блок 15 Команда 5 выполняет считывание из ЗУПВ 21 и запись выбранного значения на буфернь регистр 25, при этом модификация адреса, указанного в слове команды, не производится Данная команда совместно с первой и второй командами обеспечивает вычисление произвсшьных булевских функций от некоторого набора переменных, которыми являются разряды вторых выходов регистра 25 о Команда выполняется в следующем порядке о После приема команды по СИ 3 на регистр 12 блок управления формирует сигналы У1 1, и , чем разрешается переход к следующей по порядку команде и блокируется запись в блоке 11.Одновременно вырабатываются сигналы управления модификатором 3 , которые блокируют регистр 13 адреса и запись в блоки 14 и 15. По следующему СИ 3 конвейерный регистр 4 принимает содержимое регистра команд, а блок 2 управления формиРУ т сигналы , У14-У15 У16 0, tT л -г л -тт.. , При этом разрешается прием на регистр 66 регистра 20 адреса, элемент ШШ 63 вырабатывает на выходе уровень логической единицы, по которому входной мультиплексор регистра 66 разрешает прохолвдение кода с выходов мультиплексора 64, который в свою очередь обеспечивает прохождение кода с вторых выходов конвейер ° ° регистра 4 (4-11 разряды регистР команд). Одновременно вырабатываются .сигналы управления, если значение знакового разряда регистра команд равно О, то , , если наоборот, то У23.1, , , , , , Таким образом, по следующему СИ 1 на регистр 20 адреса принимается ад рее с вторых выходов регистра 4, запись в блок 21 блокируетсяо Мультиппексор 23 обеспечивает прохождение кода с выхода блока 21 на вход данных регистра 25, Дешифратор 24 по коду

на третьих выходах регистра 4 разрешает запись в соответствующий триггер регистра 25, и по следующему СИ 3 значение на выходе 21 с требуемым знаком записьшается в выбранный разряд регистра 25.

Команда 6 предназначена для останова генератора В сочетании с командами З..И 4 она может служить для останова генератора по достижению заданного числа тактов работы.При появлении этой команды на регистре команд блок 2 управления вырабатьшает управляющие сигналы, блокирующие последовательно по BpeMe ни счетчика 10 адреса и регистр 13 адреса. Далее вырабатывается блокировка записи в блоки памяти, блокировка второго регистра адреса, второго буферного регистра и выходного регистра. На этом генератор останавливает свою работуо

Таким образом, предлагаемый генератор обеспечивает формирование весьма широкого набора многоразрядных

последовательностей, которые могут быть использованы в качестве входных наборов при функциональном конт poJie практически любых логических узлов, выполненных как на ИС, так и БИС с числом выводов порядка 100. При этом дпительность такта в среднем составляет величину порядка 10 мкс, что позволяет подавать за время проверлИ несколько миллионов входных наборов, чем обеспечивается высокое качество контроля, полнота и достоверность. Довольно ограниченный набор команд не требует сложного математического обеспечения и вместе с тем дает возможность автоматизировать набор условий проверки, что значительно увеличивает производительность труда оператора Генератор не требует большого оборудования. При использовании микросхем средней .степени интеграции серии ИС 100 генератор может быть выполнен на 7-8 ТЭЗ, содержащих 100 ИМС с учетом резисторных ; сборок.

(4

llllinil Ш

)

,5,, :,

aid);) 5)CS} i)i

c.,.t- o St: 5; :l5 t S S 5:iSl г c5Sl 5

X: ч; ; Х:ХУЧЧЧЧХЧ

81

il

tslf

5|г5|§

CNl

IN

g

§1 §

I

|ЬчI

Bgf fog oa ty J Ы k loa I |atfJ« . щ||

S|SJiSr 5|

4 ч4

«3 ly. П5

Tf IЛ ji т i

fflljfll MiKiiMNJ iimiiiiiiii II

ч ;$ Sg 5;;S3

I II I I I t II I I ( I

15,I 1 1 §

« |qg M vi 1° N ° N 5 t 1 I ca 1

5|«1 ЫзУ 1|УзЬи У Уз1|1«ЬМ§|5 У Щ

1

t .Tiy ixiiJQa ПТП SS 4

5

i

§{

1

S

St 1

e

5 M Jy itiita. QciT Ictf f3 lyf 1. .y. Jj I III eULkWse s 54§V

ОРАИК

Фиг.4

OPAHM-7PAHM

OPSHM 7PJ}HM

Фаг. 5

Фиг.6

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 4047008, кл | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Многофункциональный генератор двоичных последовательностей | 1981 |

|

SU991397A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-01-07—Публикация

1983-03-25—Подача