и первого элемента ИЛИ блока расчета функ1щй, выход третьего элемента И блока расчета функций соединен с первыми.входами третьего, четвертого,- пятого элементов ИЛИ и девятого, десятого, одиннадцатого элементов И блока расчета функций, выход четвертого элемента И блока расчета функций соединен с вторыми входами девятого элемента И и треть го элемента РШИ блока расчета функций, выход шестого элемента И блока расчета функций соединен с вторым входами одиннадцатого элемента И и четвертого элемента ИЛИ блока расчета функций, выход седьмого элеменг та И блока расчета функций соединен с первыми входами двенадцатого элемента И и шестого элемента ИЛИ блока расчета функций, вторые входы десятого и двенадцатого элементов И блока расчета функций соединены с четвертым и девятым выходами пер- вого коммутатора соответственно, выход- восьмого элемента И .блока расчета функций соединен с вторым входом шестого элемента ШШ блока расчта функций и первыми входами тринадцатого элемента И и седьмого элемента ИЛИ блока расчета функций, выход девятого элемента И блока расчета функций соединен с вторь ми входами тринадцатого Элемента И и седьмого элемента ИЛИ блока расчета функций, выходы десятого и двенадцатого элементов И блока расчета функций соединены с вторыми входами .второго и пятого элементов ИЛИ блока расчета функций соответственно, выход первого элемента ИЛИ блока расчета функций соединен с .первы входом восьмого элемента ИЖ блока расчета функций, второй вход которого соединен с выходом четвертого элемента ИЛИ блока расчета функций, выход второго элемента ИЛИ блока расчета функций соединен с первым входом девятого элемента ИЛИ блока расчета функций, второй вход которого соединен с выходом пятого элемента ИЛИ блока расчета функций, входы десятого элемента ИЖ блока расчета функций соединены с выходами третьего и шестого элементов ШШ блока расчета функций соответственно, прямые входы импликаторов соединены с соответствующими выходами блока управления расчетом функций, первый вход которого

Соединен с инверсными входами первого, второго и третьего элементов ЗАПРЕТ, первыми входами первых t групп входов элементов (1-2) И-2ИЛИ, (1-2-3) И-ЗИЛИ, первым прямым входом первой группы вхрдов элемента (1-3-4) И-ЗИЛИ и первым инверсным входом второй группы, входов элемента (1-3-4) И-ЗИЛИ, второй вход блока управления расчетом функций соединен с первым входом элемента ИЛИ-НЕ, первым входом второй группы входов элемента (1-2-3) И-ЗИЛИ и вторым прямым входом первой группы входов элемента (1-3-4) И-ЗИЛИ, третий

вход блока управления расчетом функций соединен с первым инверсным входом четвертого элемента ЗАПРЕТ, первым прямым входом пятого элемента ЗАЙРЕТ, инверсным входом шестого элемента ЗАПРЕТ, вторым входом второй группы входов элемента (1-2-3) И-ЗИЛИ, инверсным входом первой группы входов и вторым инверсным входо.м второй группы входов элемента (1-3-4) И-ЗИЛИ, четвертый вход блока управления расчетом функций соединен с вторым инверсным входом четвертого элемента ЗАПРЕТ, инверсным входом пятого элемента ЗАПРЕТ, первым прямым входом шестого элемента ЗАПРЕТ и прямым входом седьмого элемента ЗАПРЕТ, пятый вход блока управления расчетом функций соединен с вторым входом элемента ИЛИ-НЕ, прямым входом третьего элемента ЗАПРЕТ и инверсным входом седьмого элемента ЗАПРЕ-Т, выход элемента ШШ-НЕ соединен с прямым входом четвертого элемента ЗАПРЕТ и вторыми прямыми входами пятого и шестого элементов ЗАПРЕТ, выход четвертого элемента ЗАПРЕТ соединен с прямым входом первого элемента ЗАПРЕТ и входом третьей группы входов элемента (1-3-4) И-ЗИЛИ, выход шестого элемента ЗАПРЕТ соединен с прямьп входом второго элемента ЗАПРЕТ, вторым входом первой группы входов элемента (1-2) И-2ШШ и вторым входом первой группы входов элемента

(1-2-3) И-ЗИЛИ, выход седьмого элемента ЗАПРЕТ соединен с третьим входом второй группы входов элемента (1-2-3) И-ЗИЛИ, прямым входом второй группы входЬв и третьим прямым входом первой группы входов элемента (1-3-4) И-ЗИЛИ, вход второй группы входов элемента (1-2) И-2ИЛИ и вход третьей группы входов элемента (1-2-3) И-ЗИЛИ.соединены с вы ходами первого и пятого элементов ЗАПРЕТ соответстБенно, выходы блока управления расчетом функций соединены с выходами элемента (1-2-3) И-, ЗИЛИ, третьего элеме нта ЗАПРЕТ, элемента (1-3-4) И-ЗИЛИ, элемента (1-2) И-2ИЛИ, пятого, второго и первого элементов ЗАПРЕТ соответственно, первая группа из восьми информационных входов первого мультиплексора соединена с вькодами десяг того, восьмого, седьмого элементов ИЛИ, тринадцатого элемента И, девятого, второго, первого элементов ИЖ и. восьмого элемента И блока расчета функций соответственно, вторая группа из четырех информационных входов первого мультиплексора соединена с выходами восьмого и первого элементов И, первого элемента. ИЛИ И восьмого элемента И блока расчета функций соответственн входы третьей группы-из шести ин- , формационных входовпервого мультиплексора объединены и соединены с в.ходбм.первого элемента И блока расчета функций,первая группа из восьм информационных входов второго мультиплексора соединена с выходами девятого, пятого- и третьего элементов ИЛИ, девятого, третьего и десятого элементов К, первого элемента ИЛИ и восьмого элемента И блока расчета функций соответственно, девятый и десятьш информационные входы второго мультиплексора объединены и соединены с выходом второго элемента И блока расчета функций, одиннадцатый, двенадцатый, тринадцатый и четырнадцатый информационные входы второго мультиплексора объединены и соединены с выходом первого элемента И блока расчета функций, первая группа из четырех информационных входов третьего нультиплексора соединена с выходами седьмого элемента ИЛИ, двенадцатого элемента И, четвертого элемента ИЛИ и одиннадцатого элемента И блока рачета функций соответственно, входы второй группы из шести информационных входов третьего мультиплексора попарно объединены и соединены с выходами третьего, первого и второго

элементов И блока расчета функций соответственно, первый и второй информационные входы четвертого мултиплексора соединены с выходами четвертого элемента ИЛИ и одиннадцатого элемента И блока расчета функций соответственно, с третьего по восьмой информационные входы четвертого мультиплексора попарно объединены и соединены с выходами четвертого, десятого и второго элементов И блока расчета функций соответственно, первый информационный вход пятого мультиплексора сое|динен с выходом четвертого элемента И блока расчета функций, с второго по пятый информационные входы пятог мультиплексора попарно объединены и соединены с выходами десятого и пятого элементов И блока расчета функций соответственно, первый и второй информационные входы шестого мультиплексора объединены и соед нены с выходом десятого элемента И блока расчета функций, третий и четвертый информационные входы шестого мультиплексора соединены с выходами пятого и третьего элементов И блока расчета функций соответственно, выход Р -го ( 1,6) мультиплексора соединен б -ми информационными входамивторого и третьего регистров, седьмые и восьмые информационные входы которых объединены соединены с выходом четвертого элемента И, блока расчета функций,, управляющий вход третьего регистра соединен с первым выходом первого регистра, с второго по шестой выходы которого соединены с входами блока управления переключателями, второй и третий входы которого соединены с входами первого депифратора, четвертый и пятый входы блока управления переключателя соединены с входами второго дешифратора, первый выход которого соединен с первыми входами первого, второго и третьего элементов И-НЕ, второй выход второго дешифратора соединен с первыми входами четвертого, пятого, шестого и седьмого элементов И-НЕ, третий выход второго дешифратора соединен с первыми входами восьмого и девятого элементов И-НЕ, с первого по седьмой выходы первого дешифратора соединены с вторыми входами первого девятого, четвертого, пятого, второго, третьего и седьмого элементов И-НЕ соответственно, вторые входы шестого и восьмого элементов И-НЕ соединены с шестым и первым выходами первого дешифратора соответственно, выход п -го () элемента И-НЕ соединен с гл -м.входом десятого элемента И-НЕ, седьмой к восьмой входы KQTOporo соединены с выходами восьмого и девятого элементов И-НЕ, входы одиннадцатого элемента И-НЕ соединены с выходами третье- го и седьмого элементов И-НЕ соответственно, первый и второй входы двенадцатого элемента И-НЕ соединены с выходами четвертого и пятого элементов И-НЕ соответственно, входы тринадцатого элемента И-НЕ соединеныс выходами шестого и седьмого элементов.И-НЕ соответственно, входы четыр-. надцатого элемента И-НЕ соединены

с выходами седьмого, восьмого и девятого элементов И-НЕ соответственно выход четьфнадцатого элемента И-НЕ соединен с третьим входом двенадцатого элемента И-НЕ, п -и (п 1,5) вьрсод блока управления переключателя ми соединен с выходом (Г)+9)-го элемента И-НЕ, выход шестого элемента И-НЕ соединен с шестым выходом блока управлъения переключателями, т-й выход блока управления переключателями соединен с первым входом m -го переключателя, второй и третий входы которого соединены с т-м выходом второго и выходом третьего регистров соответственно, первый вход т-го переключателя соединен с первыми входами первых групп и первыми инверсными входами вторых групп первого и второго элементов (2-2) И-2ИЛИ Но-го переключателя, второй

вход m-го переключателя соединен

с вторым входом первой группы вхо- . дон первого элемента (2-2) И-2ИЛИ tri-ro переключателя и с вторым инверс ным входом второй группы входов второго элемента (2-2) И-2ИЛИ т-го переключателя, третий вход fn-го переключателя соединен с вторым инверсным входом второй группы входов первого, элемента (2-2) И-2ИШ а-го переключателя и с вторым входом . первой группы входов второго элемента (2-2) И-2ИЛИ Пп-го переключателя, выхо)а;ы первого и второго элементов (2-2) И-2шта tn-ro переключателя соединены с выходами rti -го переключателя, вьЕХоды переключателей, элементов НЕ и седьмыевыходы второго и третье-го регистров соединены с первой груп-пой выходов модуля, входы первого и второго элементов НЕ соединены с восьмыми входами второго и третьего регистровсоответственно, вторая группа выходов модуля соединена с выходами блока маскирования, первым выходом которого является выход генератора логической единицы, вторым выходом блока маскирования является выход первого элемента ИЛИ блока маскирования, входы которого соединены с третьим, четвертым и пятым входами блока маскирования соответственно, четвертый и пятый входы

.блока маскирования соединены с входами второго элемента ИЛИ блока маскирования, вькод которого является третьим выходом блока маскирования, третий, четвертый и второй входы которого соединены соответственно с первым, вторым и . третьим входами элемента (2-2) И-2ИЛИ блока маскирования, четвертый вход которого соединен с четвертым вхо. дом блока маскирования, пятый вход

, ко.торого соеди нен с первым входом третьего элемента ИЛИ блока маскирования, второй вход которого соеди1нен с выxoдo элемента (2-2) И-2ИЛИ блока маскирования, выход.третьего

элемента ИЛИ блока маскирования является четвертым выходом.блока.маскирования, четвертый, третий и первый входы которого соединены соответственно с первым, вторым и третьим вх.одами элемента (3-3) И-2ИЛИ, четвертый, пятый и шестой входы которого соединены соответственно с четвертым, третьим и втор.ым входами блока маскирования, пятый вход которого соединен с первьпч входом четвертого элемента ИЛИ блока маскирования, второй вход которого соединен . с вькодом элемента (3-3) И-2ИЛИ, выход четвертого элемента ИЛИ блока маскирования соединен с .пятым выходом блока маркирования, второй, третий, четвертый и пятый входы которого соединены соответственно с входами элемента-(1-3)--И-2Ш1И, вь1ход которого является шестым выходом блока маскирования, седьмым выходом которого является выход элемента И блока маскирования, входы которого соединены с первым и пятым входами блока маскирования соответственно.

Изобретение относится к вычисли-, тельной технике и может быть использованр в качестве специализированного вычислительного устройст- ва в системах автоматического проек- 5 тирования логических объектов в процессе их разработки и для построения проверяющих тестов.

Цель изобретения - повышение быстродействия модуля.

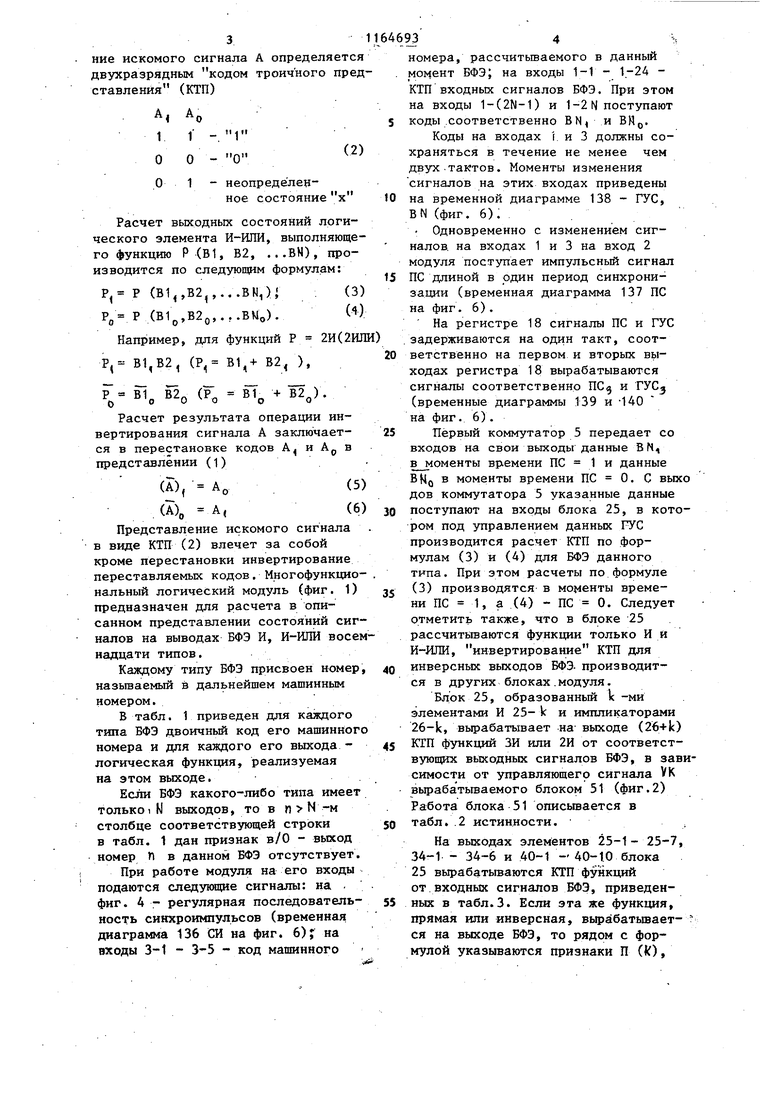

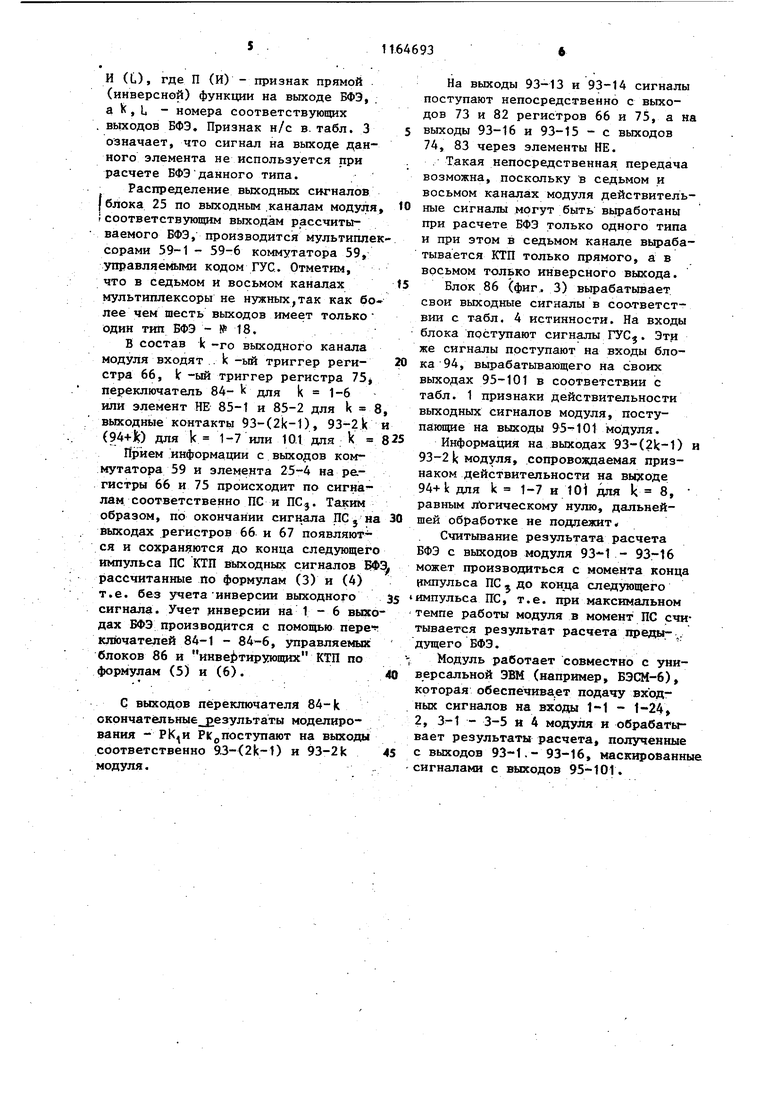

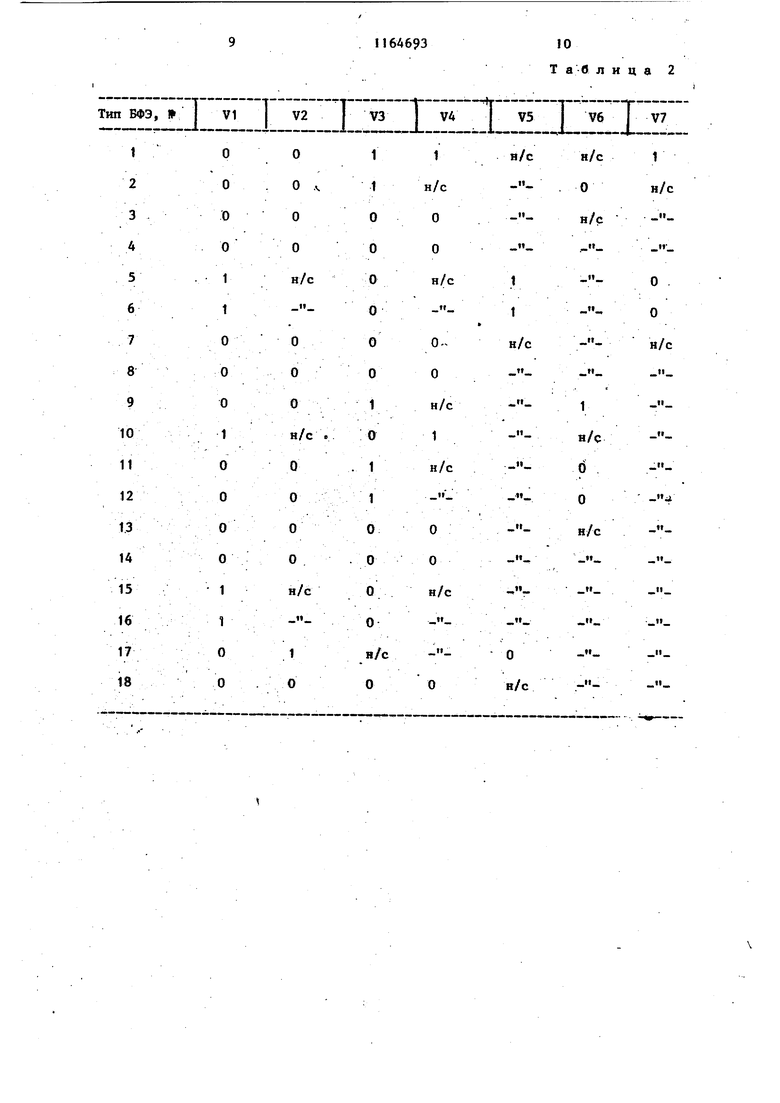

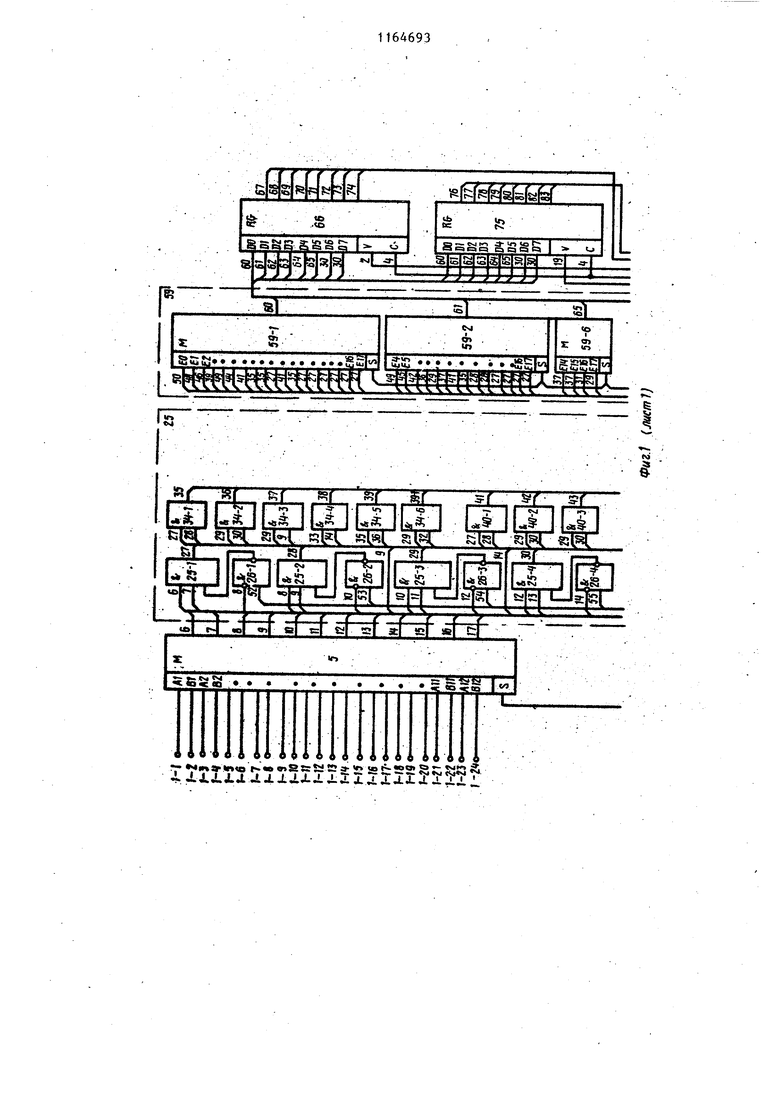

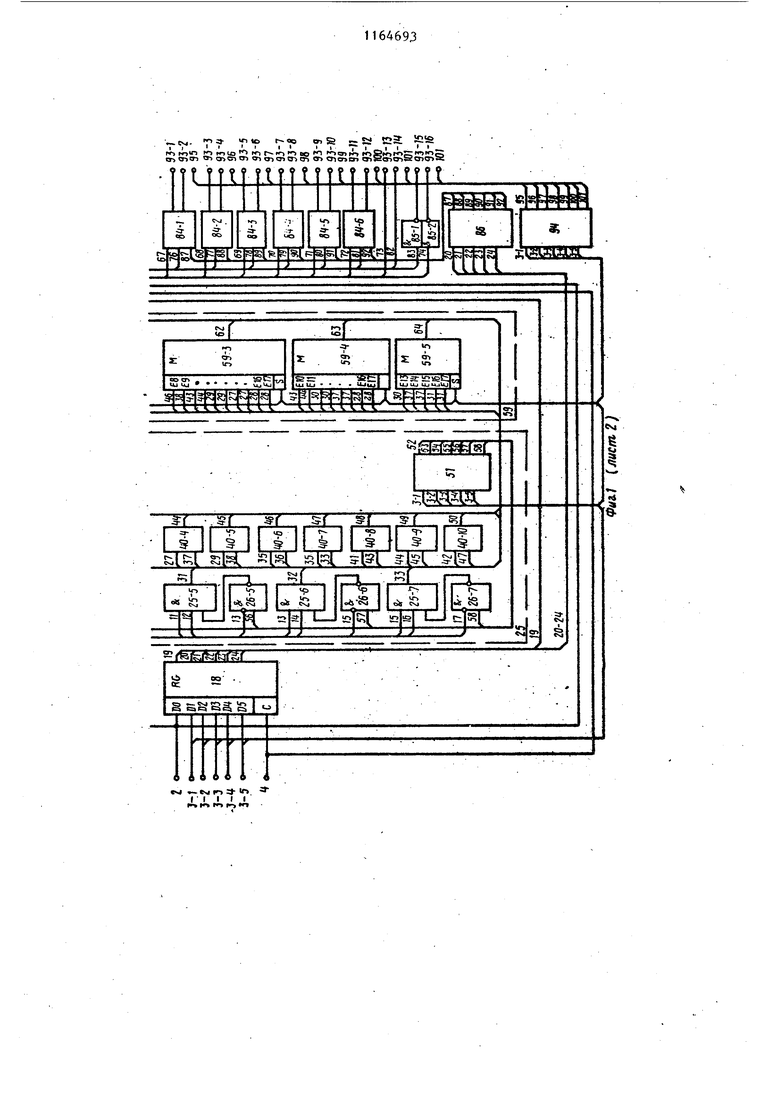

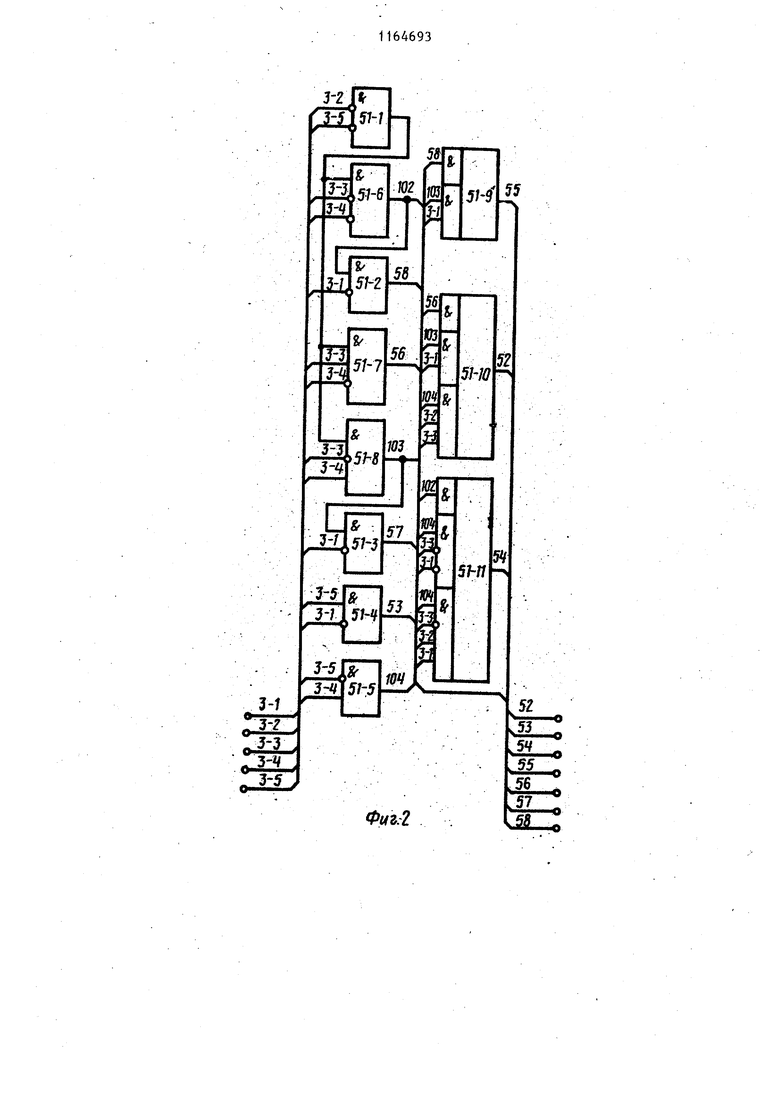

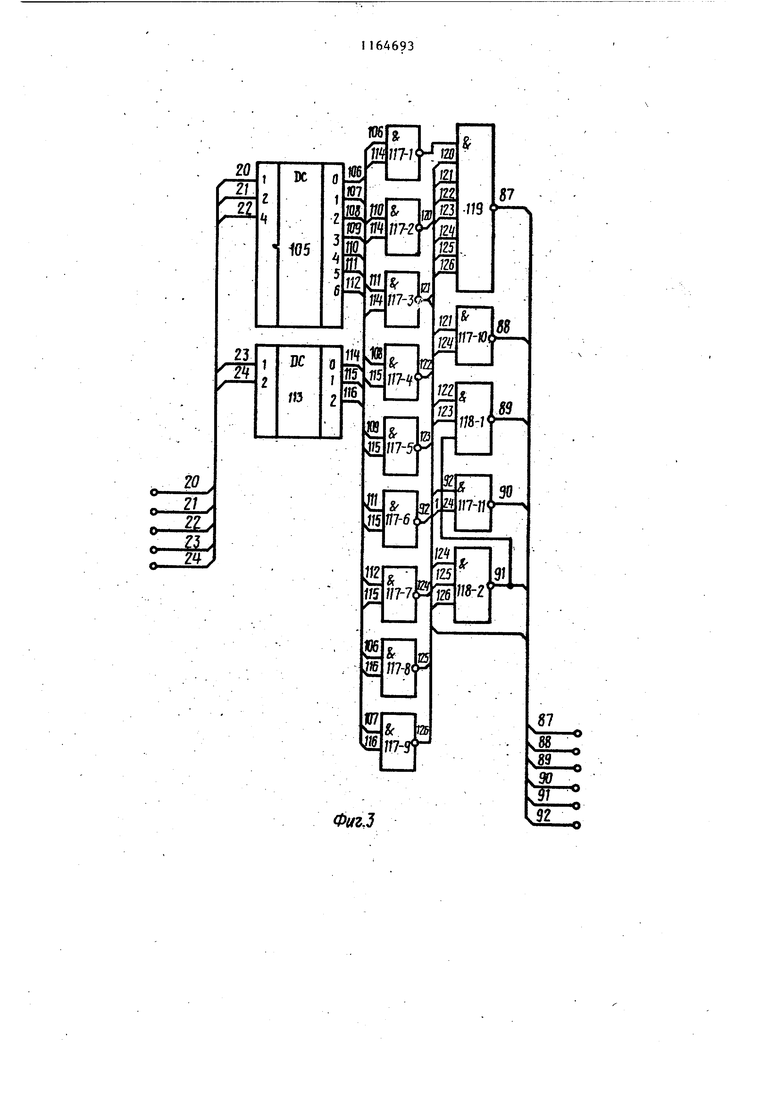

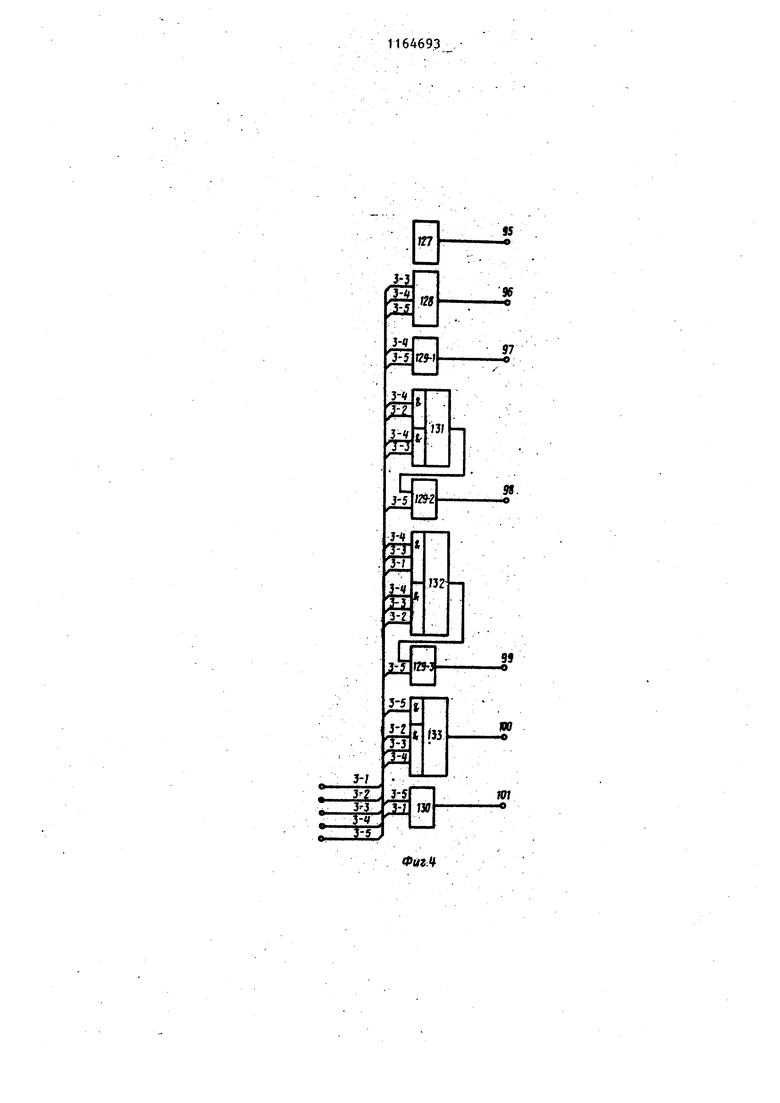

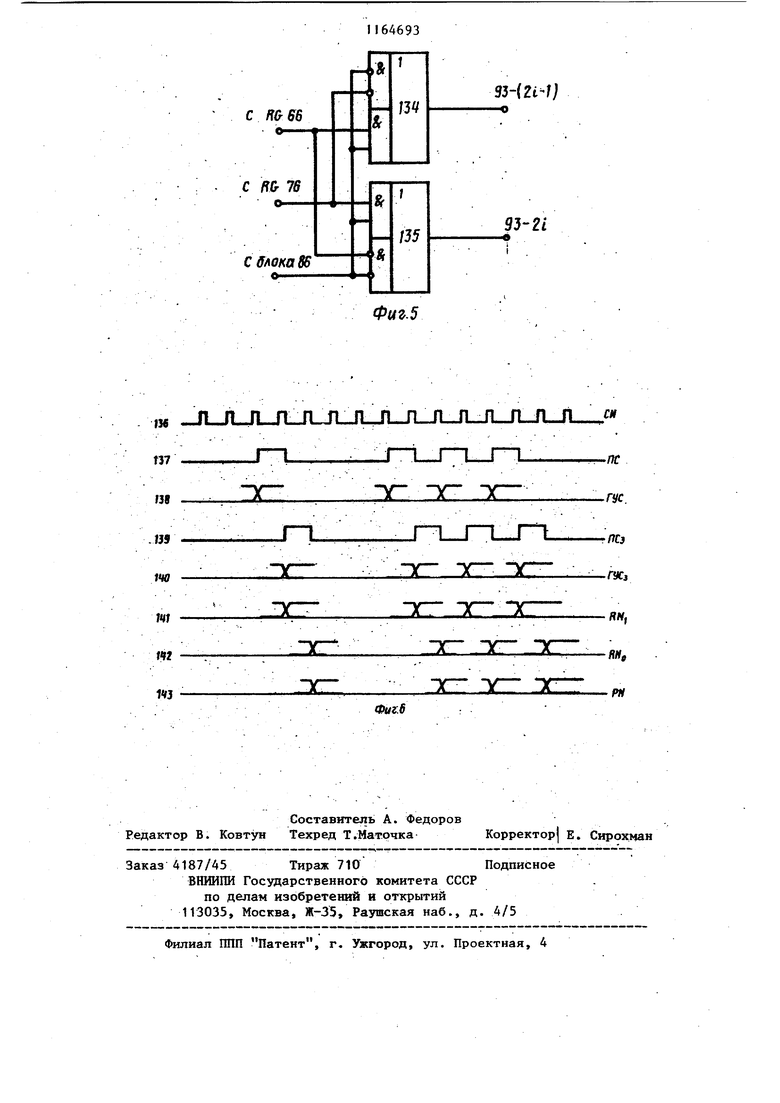

На фиг. 1 представлена схема многофункционального логического модуляJ на фиг. 2 - функциональная схема блока управления расчетом; на фиг. -3 - то же, блока управления 5 переключателями, на фиг. 4 - то же, блока маскирования/ на фиг. 5 - то же, переклнзчателя; на фиг. 6 - временная диаграмма работы модуля. Многофункциональный модуль содер-20 I жит информационные входы 1-1 - 1-24, : вход 2 запуска модуля, управляющие I входы 3-1-3-5, синхровход 4, пер.вый коммутатор 5, вькоды 6-17 первого коммутатора, первый регистр 18,.25 выходы 19-24 первого регистра, блок 25 расчета функций, элементы И 25-1; 25-7 блока расчета функций, импликаторы 26-1 - 26-7, выходы 27-33 элементов И блока расчета функций, 30. элементы И 34-1 - 34-6 блока расчета функций, выходы 35-39, 39-1 злементов И лока расчета функций, элементы ИЛИ 40-1 и 40-10 блока расчета функций, выходы 41 - 50 35 элементов- ИЛИ бл.ока расчета функций, 5лок 51 управления расчетом, элемент ИЛИ-НЕ 51-1, элементы ЗАПРЕТ 51-2 51-8, элемент (1-2) И-2ИЛИ 51-9, элемент (.1-2-3) И-ЭИЛИ 51-10, .эле- 40 мент (1-3-4) И-ЗИЛИ 51-11,. выхо-,-. ды 52 - 58 блока управления расче-; том, второй коммутатор 59, состоящий из шести мультиплексоров 59-1 ,59-6i вькоды 60 - 65 мультиплексо- 45 ров, второй регисцр 66, выходы 67 74 второго регистра, третий реги.стр 75, выходы 76 - 83 третьего регистра, переключатели 84-1 - 84-6,. элементы НЕ .85-1, 85-2, блок 86 управле- 50 ния переключателями, выходы 87-92 блока. зтаравления переключателями, . первая .группа выходов 93-1 - 93-16 модуля., блок 94 маскирования, выходы 95-101 блока маскирования, 55 выходы 102,;103, 104 четвертого, шестого и седьмого элементов ЗАДРЕТ f соответственно, первый дешифратор

105,. выходы 106 - 112.первого дешифратора, второй дешифратор 113, выходы 114-116 второго дешифратора, элементы И-НЕ 117-1 - 117-11, 118-1, 118-2 119, выходы 120-126 элементов И-НЕ 117-2 - 117-5, 117-7 - 117-9 соответственно, генератор 127 логической единицы, элементы ИЛИ 128, 129-1 - 129-3 блока маскирования, элемент И 130 блока маскирования, элемент (2-2) И-2ИЛИ 131, элемент (3-3) И-2ИЛИ 132, элемент (1-3 И-2ИЛИ 133, первый элемент (2-2 И-2ИЛИ 134 переключателя, второй элемент (2-2) И-2ИЛИ 135 переключателя. На фиг, 6 приведены диаграмма 136 сигнала СИ на-синхровходе 4 модуля, диаграмма 137 пускового сигнала -(ПС) на входе 2 . . запуска модуля, диаграмма 138 переключения группы управляющих сигналов (ГУС) на входах 3-1 - 3-5 модуля, диаграмма 139 задержанного пускового сигнала (ПС) на первом вькоде 19 первого регистра 18,диаграмма -140 переключения задержанных сигналов ГУС (ГУС) с грулпы вьпсодов 20 - 24 регистра 18, диаграмма 141 переключений сигнала RN, на Ц -м выходе (1 N: 8) второго регистра 66, диаграмма 142 переключен.ий сигнала RN на N - выходе третьего регистра. 75, диаграмма 143 переключений сигналов PN на (2N-1)-M и.2М-м выходах 93-(2 N-1) и 93-2N модуля из первой группы вькодов модуля.

Сигналы на входах и выходах подлежащего расчету БФЭ в дальнейшем обозначаются соответственно BN, PN где N - порядковый номер входа или выхода.

Реализуемый в данном модуле алгоритм р.асчета состояний сигналов на выходах логических схем предполагает представление состояния сигнала в троичном позиционном коде: Г О О - 1, О 1 О - О, О О 1 - неопределенное состояние х (1). .

Первый и вторсэй разряды такого представления сигнала А в дальнейшем обозначаются соответственно А, и Q, его третий разряд в модуле не

используется.

. На входы (на выходах) модуля сигналы BN, (РМ) поступают (вырабатываются) в прямом коде, а сигналы ВЧд

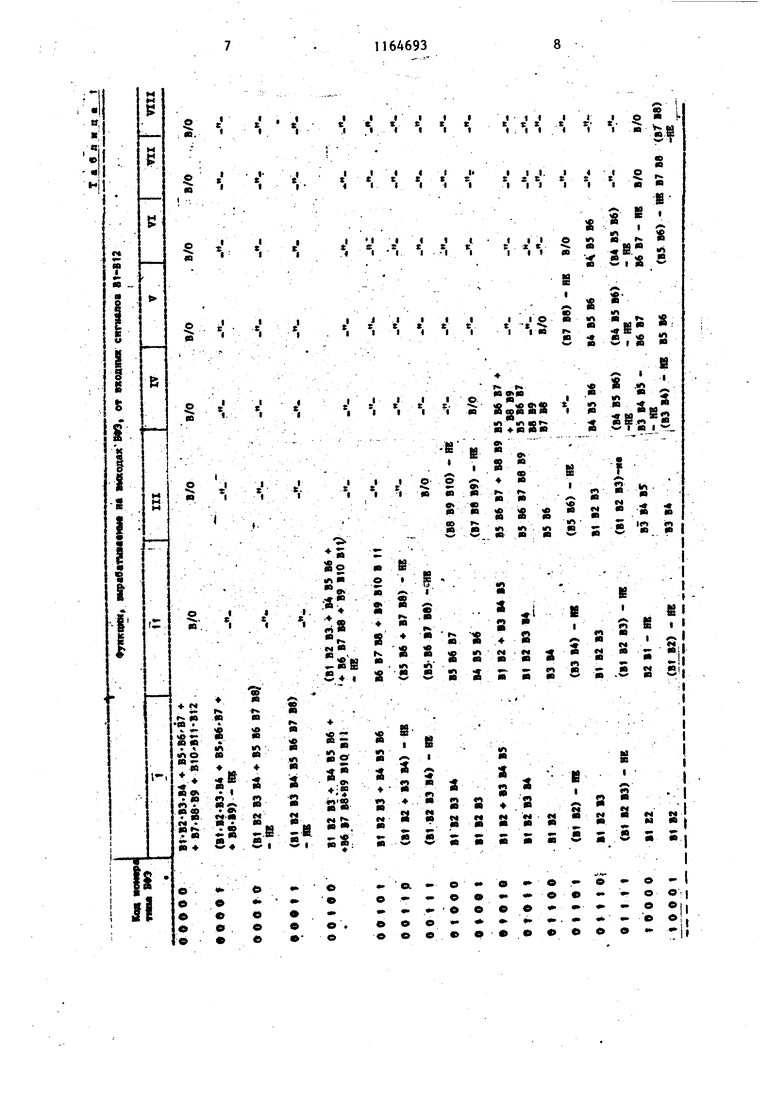

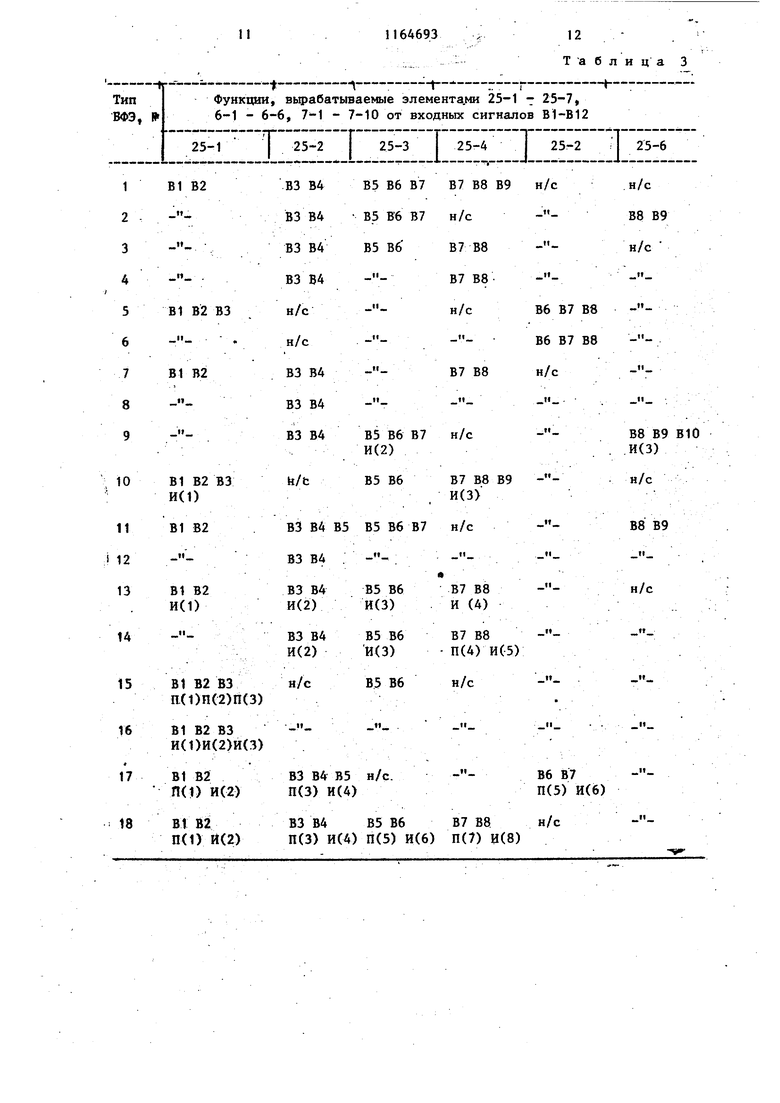

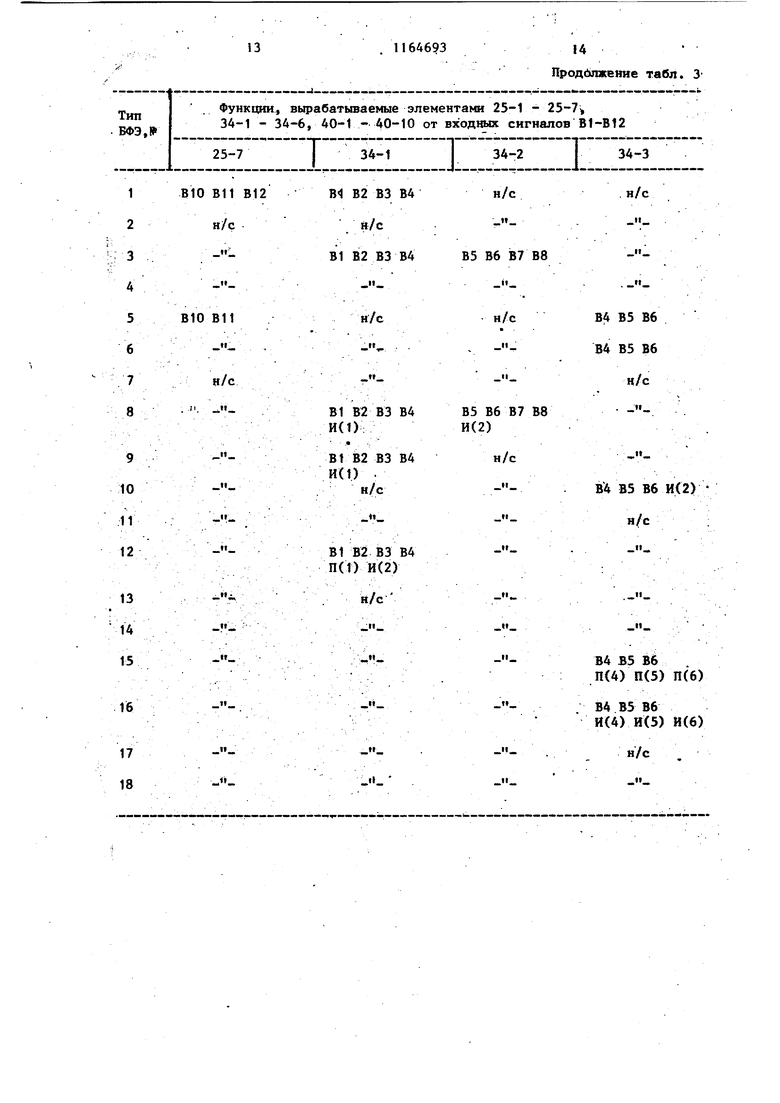

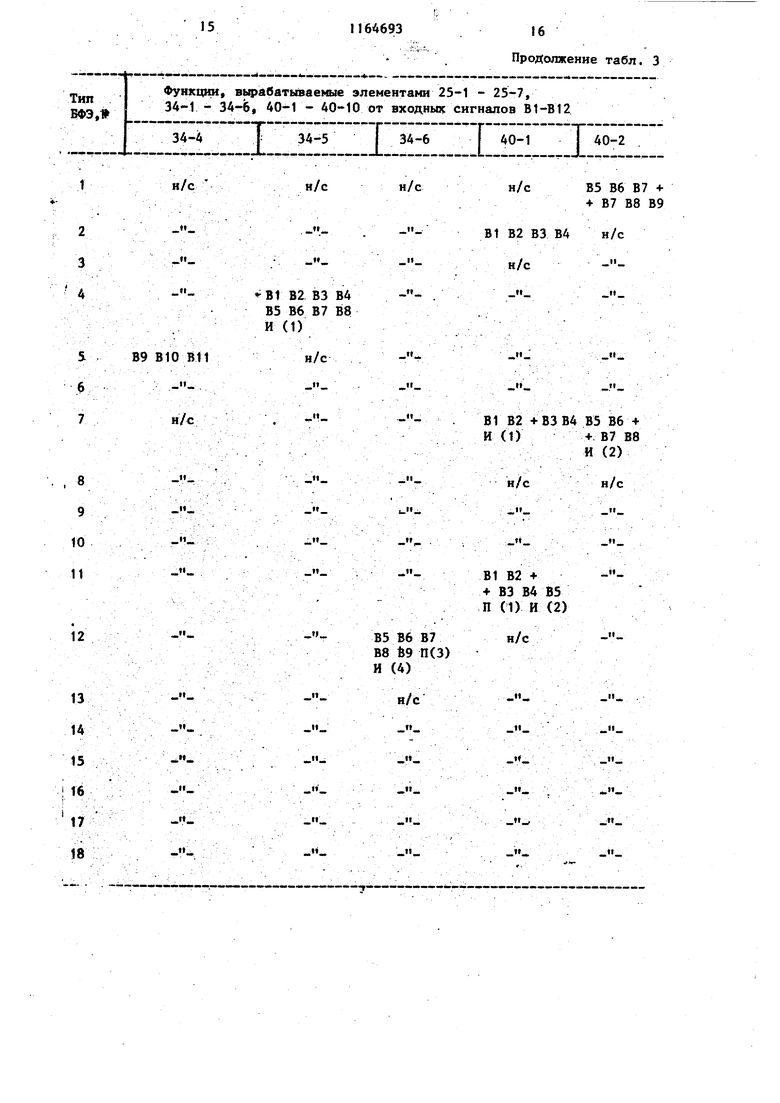

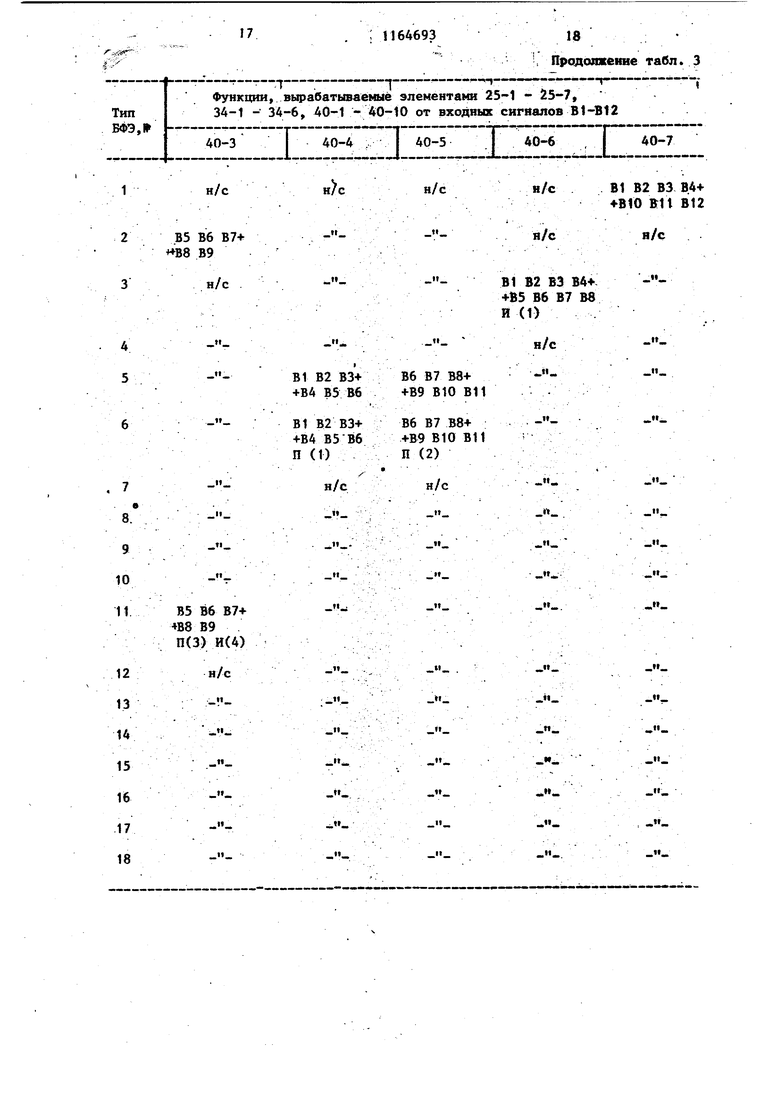

(РМо) - в инвертированном, и состояние искомого сигнала А определяетс двзгхразрядным кодом троичного пре ставления вое состояние х Расчет выходных состояний логического элемента И-ШТИ, выполняюще го функцию Р (В1, В2, ...BN), производится по следующим формулам: Р, Р (B1,B2,,...BHi)i ; Р (В1р,Б2о,.,.ВЫо). Например, для функций Р 2И(2И Р, В1,В2, (Р В1,+ В2 ), В1. Ъ2 4 В2). (РО о о -О Расчет результата операции инвертирования сигнала А заклю чается в перестановке кодов А и АО в представлении (1) (А)о А, Представление искомого сигнала в виде КТП (2) влечет за собой кроме перестановки инвертирование переставляемых кодов. Многофункцио нальный логический модуль (фиг. 1) предназначен для расчета в описанном представлении состояний сиг налов на выводах БФЭ И, И-ИПИ восе надцати типов. Каждому типу БФЭ присвоен номер называемый в дальнейшем машинным номером. В табл. 1 приведен для калздого типа БФЭ двоичньй код его машинног номера и для каждого его выхода логическая функция, реализуемая на этом выходе. Если БФЭ какого-либо типа имеет ТОЛЬКО и выходов, то в -м столбце соответствующей строки в табл. 1 дан признак в/0 - выход номер П в данном БФЭ отсутствует При работе модуля на его входы подаются следзгющие сигналы: на фиг. 4 - регулярная последователь ность синхроимпульсов (временная диаграмма 136 СИ на фиг. 6)j на входы 3-1 - 3-5 - код машинного (3 (4 номера, рассчитьшаемого в данный момент БФЭ; на входы 1-1 - 1-24 КТП входных сигналов БФЭ. При этом на входы 1-(2N-1) и 1-2 N поступают коды .соответственно BN и ВН. Коды на входах 1 и 3 должны сохраняться в течение не менее чем двух тактов. Моменты изменения сигналов на этих входах приведены на временной диаграмме 138 - ГУС, BN (фиг. 6). Одновременно с изменением сигналов, на входах 1 и 3 на вход 2 модуля поступает импульсный сигнал ПС длиной в один период синхронизации (временная диаграмма 137 ПС на фиг. 6). На регистре 18 сигналы ПС и ГУС задерживаются на один такт, соответственно на первом и вторых выходах регистра 18 вырабатываются сигналы соответственно ПС и ГУС (временные диаграммы 139 и -140 на фиг. 6). Первый коммутатор 5 передает со входов на свои выходы данные BN в моменты времени ПС 1 и данные В MO в моменты времени ПС 0. С выхо дов коммутатора 5 указанные данные поступают на входы блока 25, в котором под управлением данных ГУС производится расчет КТП по формулам (3) и (4) для БФЭ данного типа. При этом расчеты по формуле (3) производятся в моменты времени ПС 1 , а (4) - ПС 0. Следует отметить также, что в блоке 25 рассчитьшаются функции только И и И-ИЛИ, инвертирование КТП для инверсных выходов БФЭ- производится в других блоках.модуля. БЛОК 25, образованный k -ми элементами И 25-k и импликаторами 26-k, вырабатывает на выходе (26+k) КТП функций ЗИ или 2И от соответствующих выходных сигналов БФЭ, в зависимости от управляющего сигнала VK вырабатьгааемого блоком 51 (фиг.2) Работа блока 51 описьюается в табл. .2 истинности., На выходах элементов 25-1-25-7, 34-1 - 34-6 и 40-1 -40-1.0 блока 25 вырабатываются КТП фу нкций от входных сигналов БФЭ, приведенных в табл.3. Если эта же функция, прямая или инверсная, вырабатывается на выходе БФЭ, то рядом с формулой указываются признаки П (К),

И (L), где П (И) - признак прямой (инверсной) функции на выходе БФЭ, а К, L - номера соответствующих вь1ходов БФЭ. Признак н/с в. табл. 3 5 означает, что сигнал на выходе данного элемента не используется при расчете БФЭ данного типа.

Распределение выходных сигналов блока 25 по выходным .каналам модуля, Ю соответствующим выходам рассчитываемого БФЭ, производится мультиплексорами 59-1 - 59-6 коммутатора 59, управляемыми кодом ГУС. Отметим, что в седьмом и восьмом каналах 15 мультиплексоры не нужных,так как более чем шесть выходов имеет только один тип БФЭ - № 18.

В состав k -го выходного канала модуля входят . k -ый триггер реги- 20 стра 66, If -ый триггер регистра 75j переключатель 84- k для k 1-6 или элемент НЕ 85-1 и 85-2 для k 8, выходные контакты 93-(2k-1), 93-2k и (944- для k 1-7 или ЮЛ для k 825

Прием информации с выходов коммутатора 59 и элемента 25-4 на регистры 66 и 75 происходит по сигналам соответственно ПС и ПС j. Таким образом, по окончании сигнала ПСj на 30 выходах регистров 66 и 67 появляются и сохраняются до конца следующего импульса ПС КТП выходных сигналов бФЭ рассчитанные по формулам (3) и (4) т.е. без учетаинверсии выходного 35 сигнала. Учет инверсии на 1 - 6 вь1ходах БФЭ производится с помощью перет ключателей 84-1 - 84-6, управляемых блоков 86 и инве)тирующих КТП по формулам (5) и (6).

С выходов переключателя 84-k окончатёльные езультаты моделирования - Рк,поступают на выходы соответственно 93-(2k-1) и 93-2k 45 модуля.

На выходы 93-13 и 93-14 сигналы поступают непосредственно с выходов 73 и 82 регистров 66 и 75, а на выходы 93-16 и 93-15 - с выходов 74, 83 через элементы НЕ.

Такая непосредственная передача возможна, поскольку в седьмом и восьмом каналах модуля действительные сигналы могут быть выработаны при расчете БФЭ только одного типа и при этом в седьмом канапе вырабатывается КТП только прямого, а в восьмом только инверсного выхода.

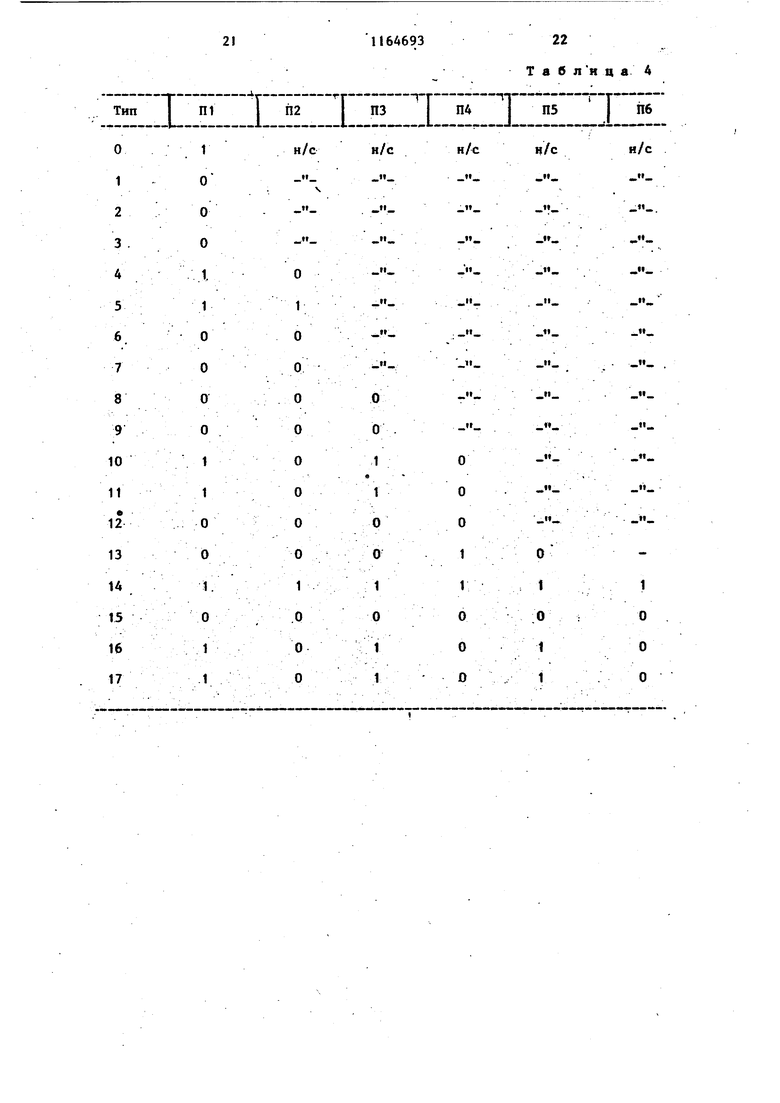

Блок 86 (фиг. 3) вьфабатывает свои выходные сигналы в соответствии с табл, 4 истинности. На входы блока поступают сигналы ГУС. Эти же сигналы поступают на входы блока 94, вырабатывающего на своих выходах 95-101 в соответствии с табл. 1 признаки действительности выходных сигналов модуля, поступающие на выходы 101 модуля.

Информация на выходах 93-(2k-1) 93-2 k модуля, сопровождаемая признаком действительности на выводе 94+k для k 1-7 и lOi для k 8, равным лЬгическому нулю, дальнейшей обработке не подлежит

Считывание результата расчета БФЭ с выходов модуля 93-1 - 93-16 может производиться с момента конца импульса ПС до конца следующего импульса ПС, т.е. при максимальном темпе работы модуля в момент ПС считывается результат расчета преды-,, дущего БФЭ.

Модуль работает совместно с универсальной ЭВМ (например, БЭСМ-6), которая обеспечивает подачу входных сигналов на вкоды 1-1 - 1-24, 2, 3-1 - 3-5 и 4 модуля и обрабатывает результаты расчета, полученные с выходов 93-1.- 93-16, маскированн сигналами с выходов 95-101.

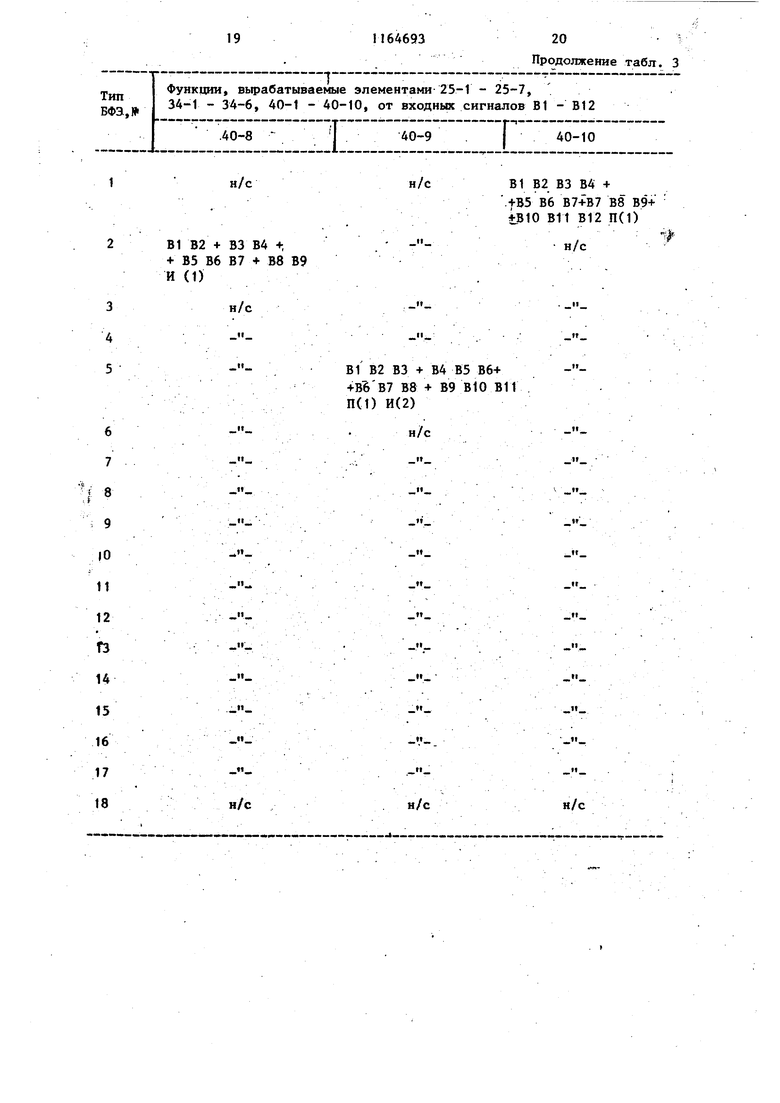

Т -а б л и ц а 3

Продблжение табл. 3

Продолжение табл. 3

19

1164693

20г

Продолжение табл. 3

rw

IOvvOO OOOvOOoO OOvOo Q Q Q

i-« «nstria S2 s s fcsa s;: йй f 4. iJLiJLJ. JL J. JL J.4. J. i 21 j. IJ.J. J. J. in. 1

- cv,. p fto «лa и сг ics

II I It- , I II

r ) Kir fOOeo ЮЙК ГОЁГ« Ю

о слсп«Т101спсг а 3 в oicnS aieeio- Soio S

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический модуль | 1984 |

|

SU1174918A1 |

| Многофункциональный логический модуль | 1987 |

|

SU1425649A1 |

| Устройство для моделирования конечных автоматов | 1980 |

|

SU955080A1 |

| Устройство для подсчета числа двоичных единиц (нулей) | 1990 |

|

SU1783515A1 |

| Электропривод | 1985 |

|

SU1354380A1 |

| Мультиплексор | 1990 |

|

SU1774491A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1163322A1 |

| Цифровой измеритель постоянной магнитной индукции | 1989 |

|

SU1704114A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ШАГОВЫМ ДВИГАТЕЛЕМ | 1997 |

|

RU2125762C1 |

| Генератор псевдослучайных последовательностей | 1984 |

|

SU1228236A1 |

МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ ЮДУЛЬ, содержащий блок расчета: функций, первый и второй коммутаторы п ричем информационные входы первого коммутатора соединены с информационными входами модуля, управляющие входы второго коммутатора соединены с управляющими входами модуля, отличающийся тем, что, с целью повышения быстродействия модуля, в него введены регистры, элементы НЕ, пер1екпючатели, содержащие элементы

CNi tsi r (r

t I I f I

ри |«4 PF) H-V

3

tf4

Ж

g ff6

т

20 21 2Z

b

1Мт-19. ш

«7

-IJ9

Ы

КЗ

И т

т

т

. mw-z

fr |;/7-(

1ZI /г

пнг

;z ш

«5

;;8-

SO

//7-/J

&- //7-6

й

///-ОЛ/1

Д.

91

/25 JZ6

(

;/8-2Г

e т

7

ж. м.

.ЭР ,

17

32

95

Ш

т

140

М

т

ю

Фиг.5

-ПС.

-ПСз

.Г9Сз

ян,

яна

РН n-AJUJLJlJT-JT-JLJl JLJl-Jl-J

| Рябов Г.Г., Лакшин Г.Л | |||

| Поэлементное моделирование вычислительных систем | |||

| Труды ИТМ и ВТ, М., 1978 | |||

| Авторское свидетельство СССР 754427, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Программируемый многофункциональныйлОгичЕСКий МОдуль | 1979 |

|

SU851399A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| , | |||

Авторы

Даты

1985-06-30—Публикация

1983-05-18—Подача