СП

О)

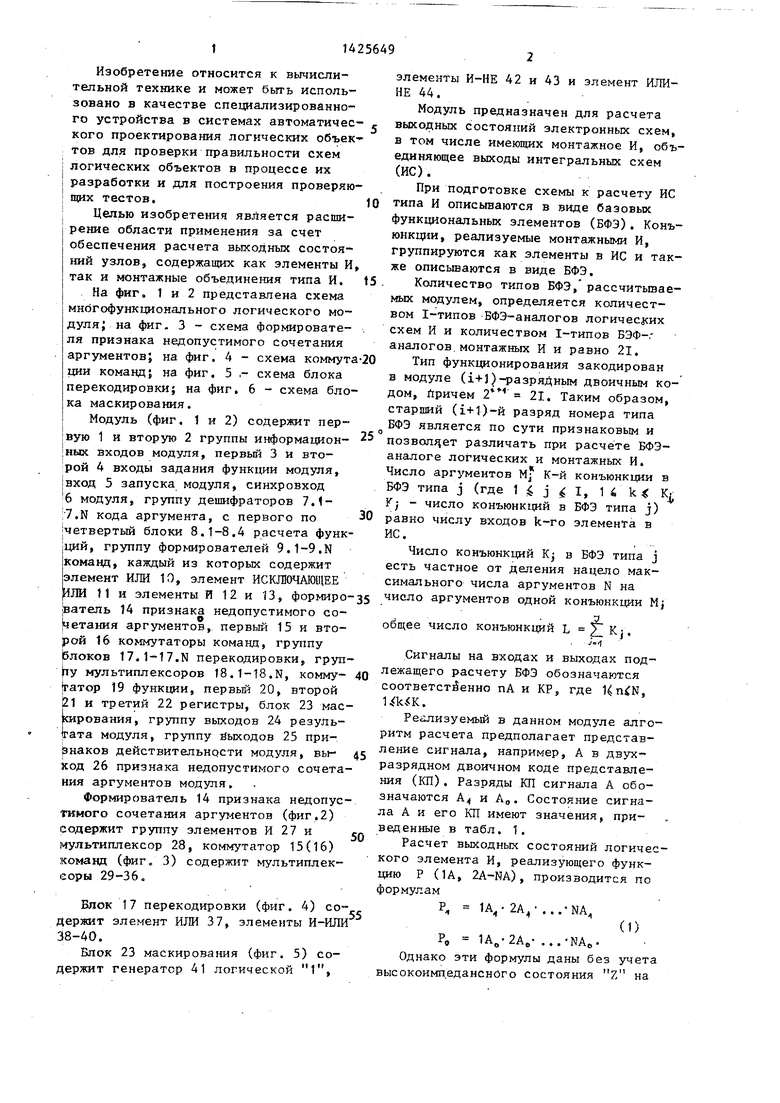

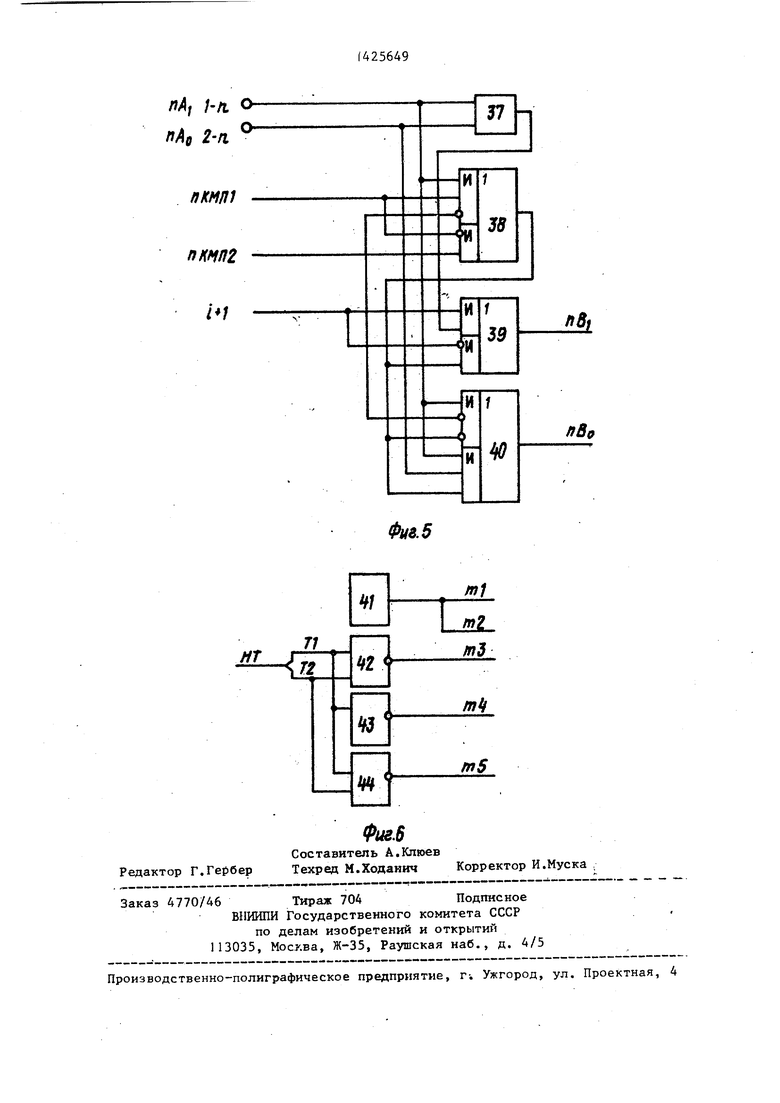

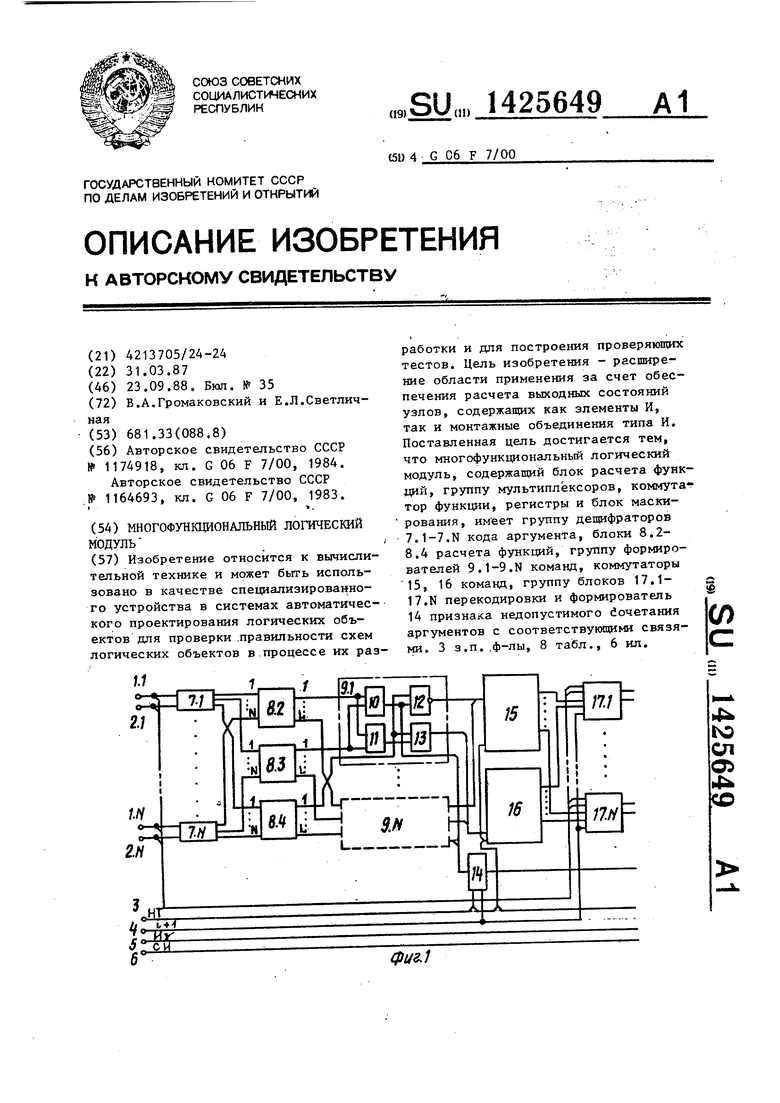

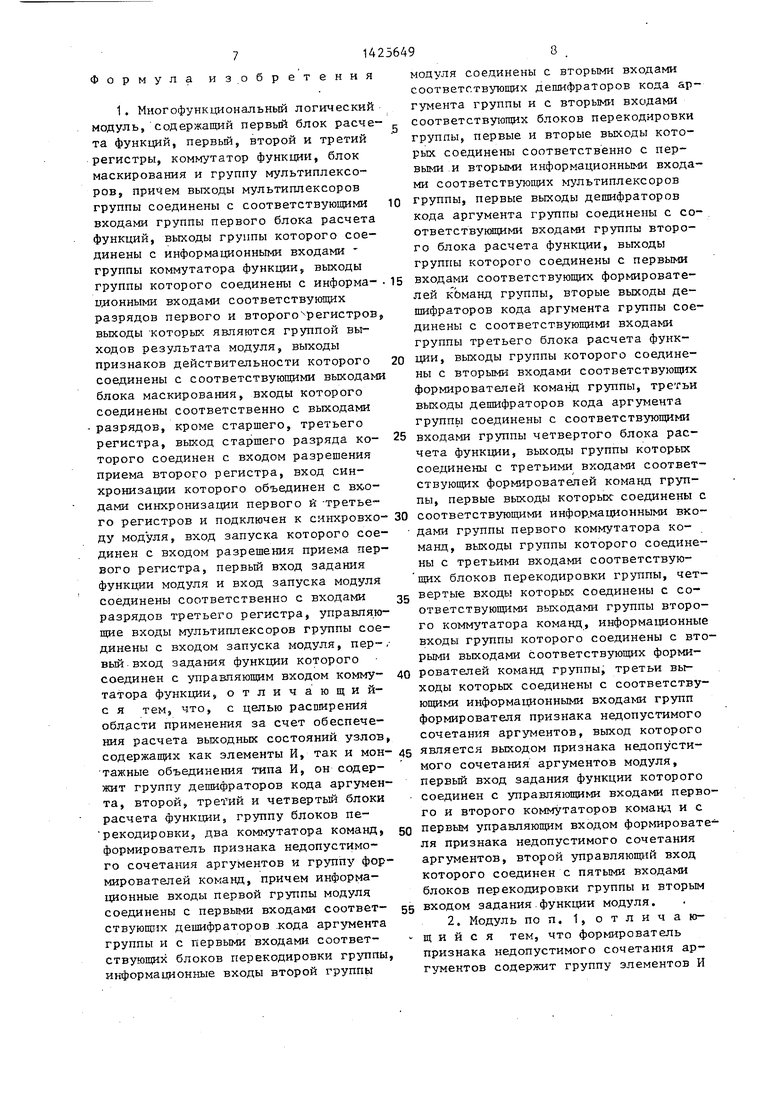

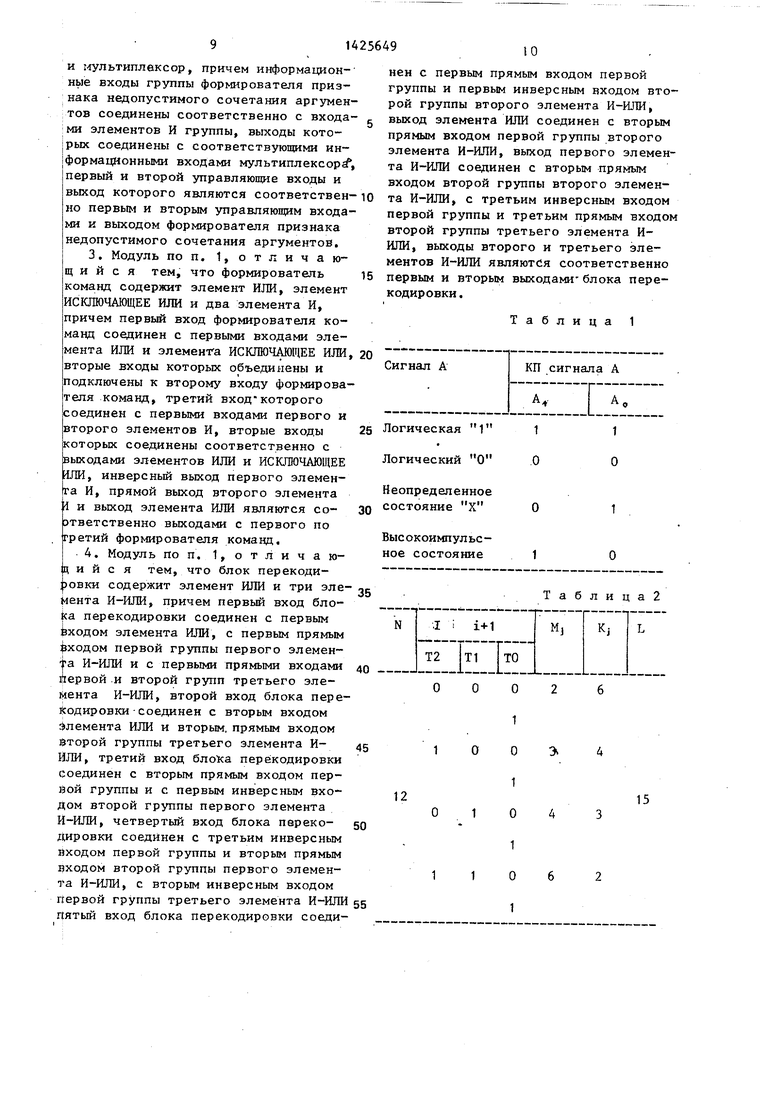

Изобретение относится к вычислительной технике и может быть использовано в качестве специализированного устройства в системах автоматичес- кого проектирования логических объектов для проверки правильности схем логических объектов в процессе их разработки и для построения проверяющих тестов, Целью изобретения является расши- I рение области применения за счет I обеспечения расчета выходных состоя- I НИИ узлов, содержащих как элементы И, I так и монтажные объединения типа И. I На фиг. 1 и 2 представлена схема I многофункционального логического модуля; на фиг. 3 - схема формировате- I ля признака недопустимого сочетания аргументов на фиг. 4 - схема коммута ции командJ на фиг. 5 ,- схема блока перекодировки; на фиг, 6 - схема блока маскирования.

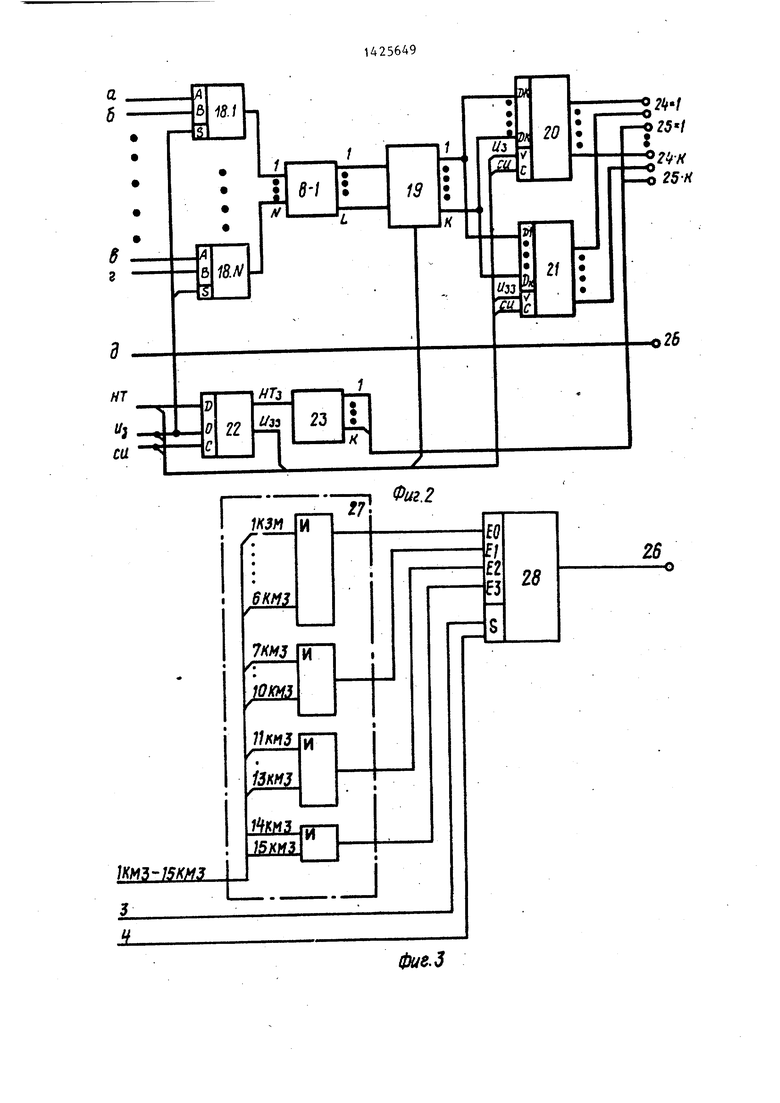

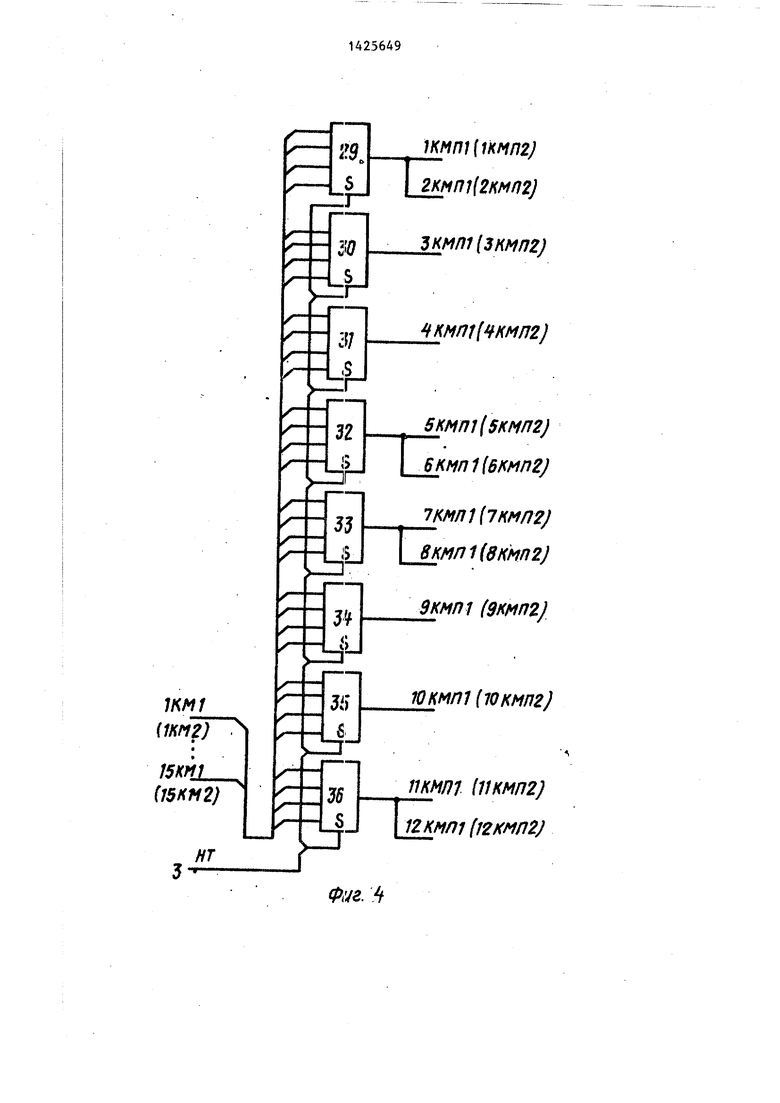

Модуль (фиг, 1 и 2) содержит пер- вую 1 и вторую 2 группы информацион- |ных входов модуля, первый 3 и второй 4 входы задания функции модуля, I вход 5 запуска модуля, синхровход 6 модуля, группу дешифраторов 7,- r7,N кода аргумента, с первого по

|четвертый блоки 8,1-8,4 расчета функ- |ций, группу формирователей 9,1-9,N команд, каждый из которых содержит элемент ИШ 10, элемент ИСКЛЮЧАЮЩЕЕ ЛИ 11 и элементы и 12 и 13, формиро|ватель 14 признака недопустимого со- етания аргументов, первый 15 и вто- |рой 16 коммутаторы команд, группу рлоков 17.1-17,N перекодировки, груп- у мультиплексоров 18.1-18,N, комму- jraTop 19 функции, первьй 20, второй 1 и третий 22 регистры, блок 23 мас- рования, группу выходов 24 результата модуля, группу йыходов 25 при- наков действительности модуля, вы- Ход 26 признака недопустимого сочетания аргументов модуля,

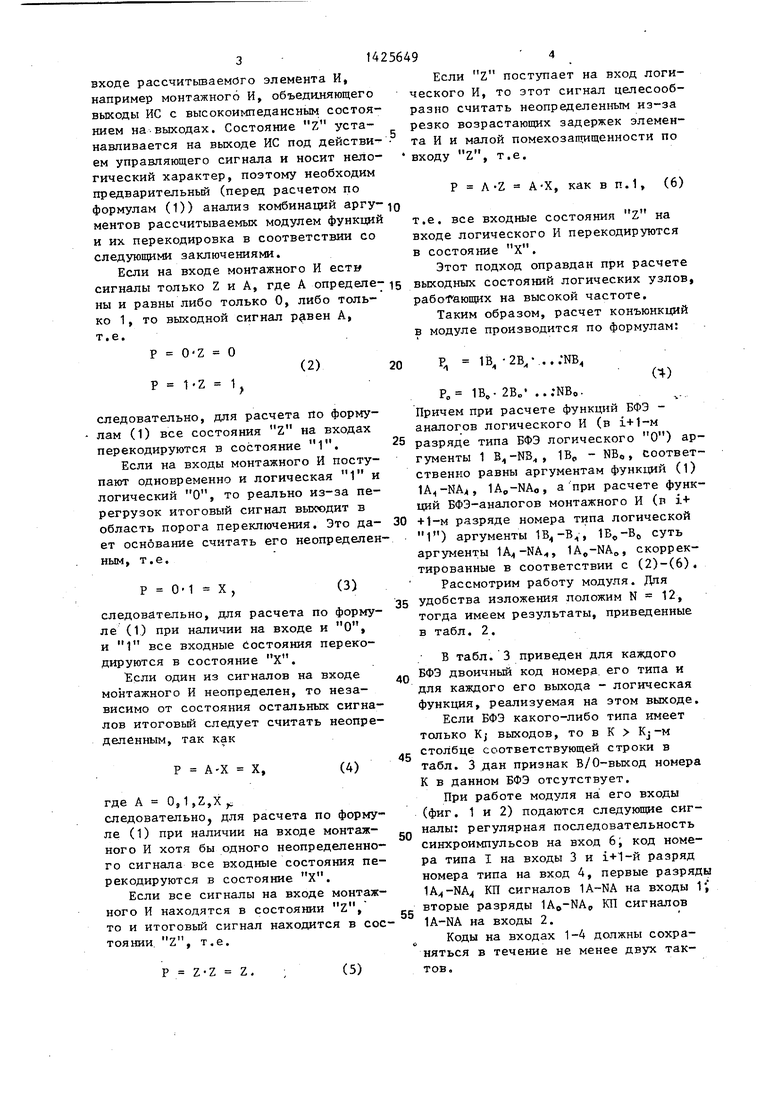

Формирователь 14 признака недопустимого сочетания аргументов (фиг,2) содержит группу элементов И 27 и

мультиплексор 28, коммутатор 13(16) команд (фиг. 3) содержит мультиплексоры 29-36.

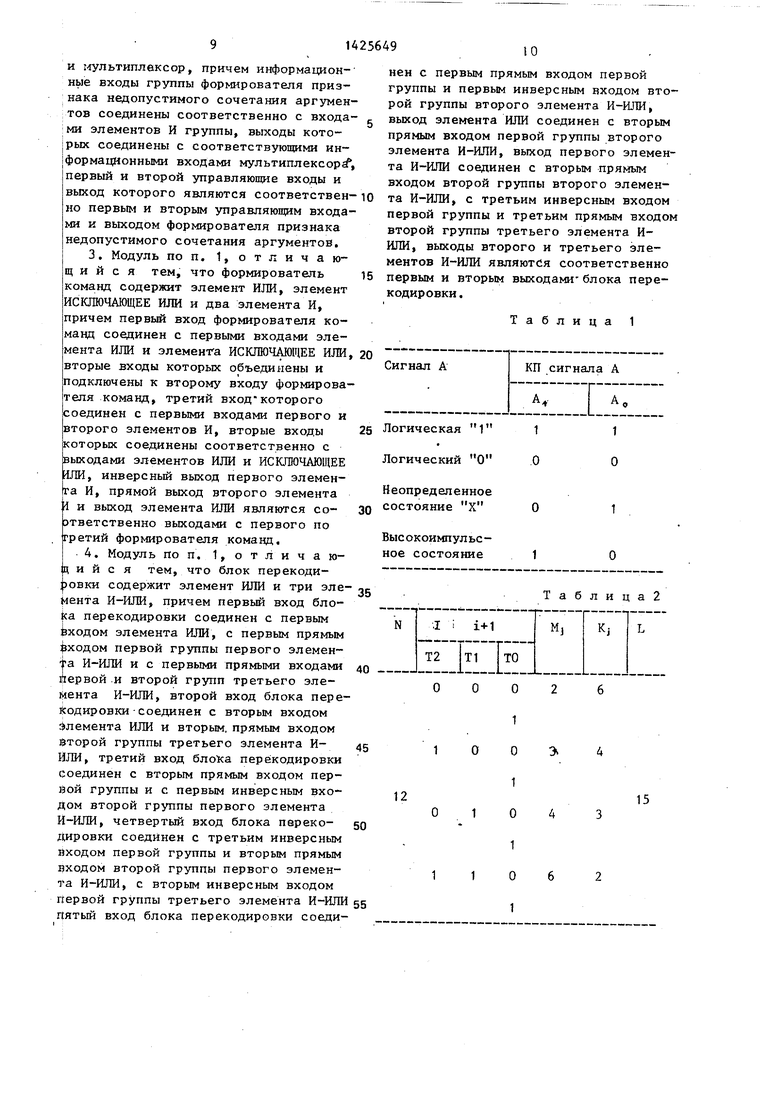

Блок 17 перекодировки (фиг, 4) содержит элемент ИЛИ 37, элементы И-ИЛИ 38-40,

Блок 23 маскирования (фиг, 5) содержит генератор 41 логической 1,

,5

, 10 t5 . 0

5 0

5 0 5

Q

5

элементы И-НЕ 42 и 43 и элемент ИЛИ- НЕ 44,

Модуль предназначен для расчета выходных состояний электронных схем, в том числе имеющих монтажное И, объединяющее выходы интегральных схем (ИС),

При подготовке схемы к расчету ИС типа И описываются в виде базовых функциональных элементов (БФЭ), Конъюнкции, реализуемые монтажными И, группируются как элементы в ИС и также описываются в виде БФЭ,

Количество типов БФЭ, рассчитьтае- мых модулем, определяется количеством 1-типов БФЭ-аналогов логичес} их схем И и количеством 1-типов БЭФ-г аналогов.монтажных И и равно 21,

Тип функционирования закодирован в модуле (i+J)-разрядным двоичным кодом, йричем 21, Таким образом, старший (1+1)-й разряд номера типа БФЭ является по сути признаковым и позвол ет различать при расчёте БФЭ- аналоге логических и монтажных И, Число аргументов Mj К-й конъюнкции в БФЭ типа j (где 1 ; j I, 1 4 k « К К; - число конъюнкций в БФЭ типа j) равно числу входов k-ro элемента в ИС,

Число конъюнкций Kj в БФЭ типа j есть частное от деления нацело максимального числа аргументов N на число аргументов одной конъюнкции Mj

общее число конъюнкций L - К;.

. ;.

Сигналы на входах и выходах подлежащего расчету БФЭ обозначаются соответственно пА и КР, где , Uk.K,

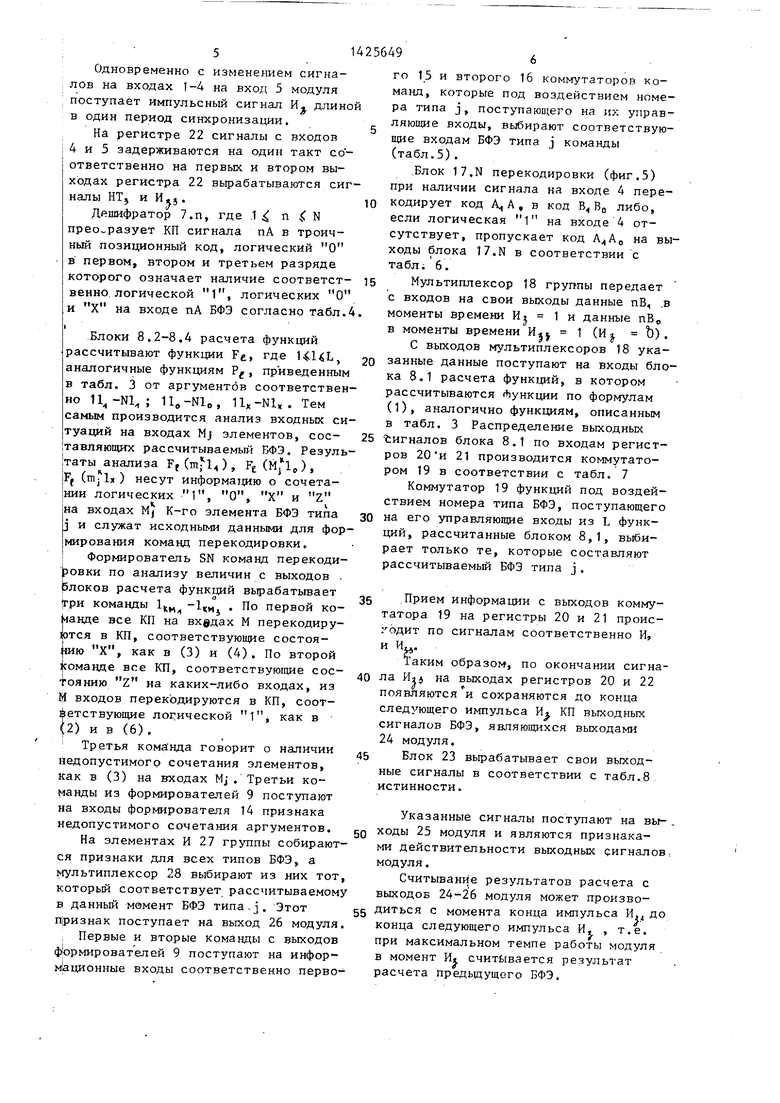

Реализуемый в данном модуле алгоритм расчета предполагает представление сигнала, например, А в двухразрядном двоичном коде представления (КП), Разряды КП сигнала А обозначаются А и АО, Состояние сигнала А и его КП имеют значения, приведенные в табл, 1,

Расчет выходных состояний логического элемента И, реализующего функцию Р (1А, 2A-NA), производится по формулам

Р ,,,-NA,

(1) РО 1А -2Ав- ,,, NAe

Однако эти формулы даны без учета высокоимп.едансного состояния Z на

входе рассчитьюаемого элемента И, например монтажного И, объединяющего выходы ИС с высокоимпедансным состоянием на выходах. Состояние Z устанавливается на выходе ИС под действи- ем управляющего сигнала и носит нелогический характер, поэтому необходим предварительный (перед расчетом по формулам (1)) анализ комбинагщй аргументов рассчитываемых модулем функций и их перекодировка в соответствии со следующими заключениями.

Если на входе монтажного И ест

Если Z поступает на вход логического И, то этот сигнал целесообразно считать неопределенным из-за резко возрастающих задержек элемента И и малой помехозащищенности по Z.

входу

т.е.

Р Л-Z А-Х, как в П.1, (6)

т.е. все входные состояния Z на входе логического И перекодируются в состояние X.

Этот подход оправдан при расчете

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональный логический модуль | 1984 |

|

SU1174918A1 |

| Многофункциональный логический модуль | 1983 |

|

SU1164693A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Устройство для определения значений булевых функций | 1985 |

|

SU1315965A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

| Многофункциональный генератор двоичных последовательностей | 1981 |

|

SU991397A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

| Устройство для моделирования конечных автоматов | 1980 |

|

SU955080A1 |

| Устройство для определения значений булевых функций | 1987 |

|

SU1508204A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве специализированного устройства в системах автоматического проектирования логических объектов для проверки .правильности схем логических объектов в процессе их разработки и для построения проверяющих тестов. Цель изобретения - расшире ние области применения за счет обеспечения расчета выходных состояний узлов, содержащих как элементы И, так и монтажные объединения типа И. Поставленная цель достигается тем, что многофункциональный логический модуль, содержащий блок расчета функ- дий, группу мультиплексоров, коммУта- тор функции, регистры и блок маски рования, им еет группу дешифраторов 7.1-7.N кода аргумента, блоки 8.2- 8.4 расчета функций, группу формирователей 9.1-9.N команд, коммутаторы 15, 16 команд, группу блоков 17.1- 17.N перекодировки и формирователь 14 признака недопустимого бочетания аргументов с соответствующими связями. 3 З.П..Ф-ЛЫ, 8 табл., 6 ил. $ (Л

сигналы только Z и А, где А определе-45 выходных состояний логических узлов,

ны и равны либо только О, либо только 1, то выходной сигнал А, т.е.

O Z О

Р

работающих на высокой частоте.

Таким образом, расчет конъюнкций в модуле производится по формулам:

(2)

I Z 1

следовательно, для расчета ito формулам (1) все состояния Z на входах перекодируются в состояние 1.

Если на входы монтажного И поступают одновременно и логическая 1 и логический О, то реально из-за перегрузок итоговый сигнал выходит в область порога переключения. Это дает основание считать его неопределенным, т.е.

Р 0-1 X

(3)

следовательно, для расчета по формуле (1) при наличии на входе и О, и 1 все входные состояния перекодируются в состояние X.

ЕСЛИ один из сигналов на входе монтажного И неопределен, то независимо от состояния остальных сигналов итоговьм следует считать неопределенным, так как

Р А Х X,

(4)

где А 0,1,Z,X

следовательно, для расчета по формуле (1) при наличии на входе монтажного И хотя бы одного неопределенного сигнала все входные состояния перекодируются в состояние X.

Если все сигналы на входе монтажного И находятся в состоянии Z, то и итоговый сигнал находится в состоянии. Z, т.е.

Р Z-Z Z.

(5)

работающих на высокой частоте.

Таким образом, расчет конъюнкций в модуле производится по формулам:

1В .... NB

W

„ 1В,. 2В„ ..;NBo. Причем при расчете функций БФЭ - аналогов логического И (в i+1-м

разряде типа БФЭ логического О) аргументы 1 , 1Во - NBo, соответственно равны аргументам функ11 1й (1) , lAp-NAo, а при расчете функций БФЭ-аналогов монтажного И (в i+

+1-М разряде номера типа логической 1) аргументы , суть аргументы , 1A,-NAo, скорректированные в соответствии с (2)-(6), Рассмотрим работу модуля. Для

удобства изложения положим N 12, тогда имеем результаты, приведенные в табл. 2.

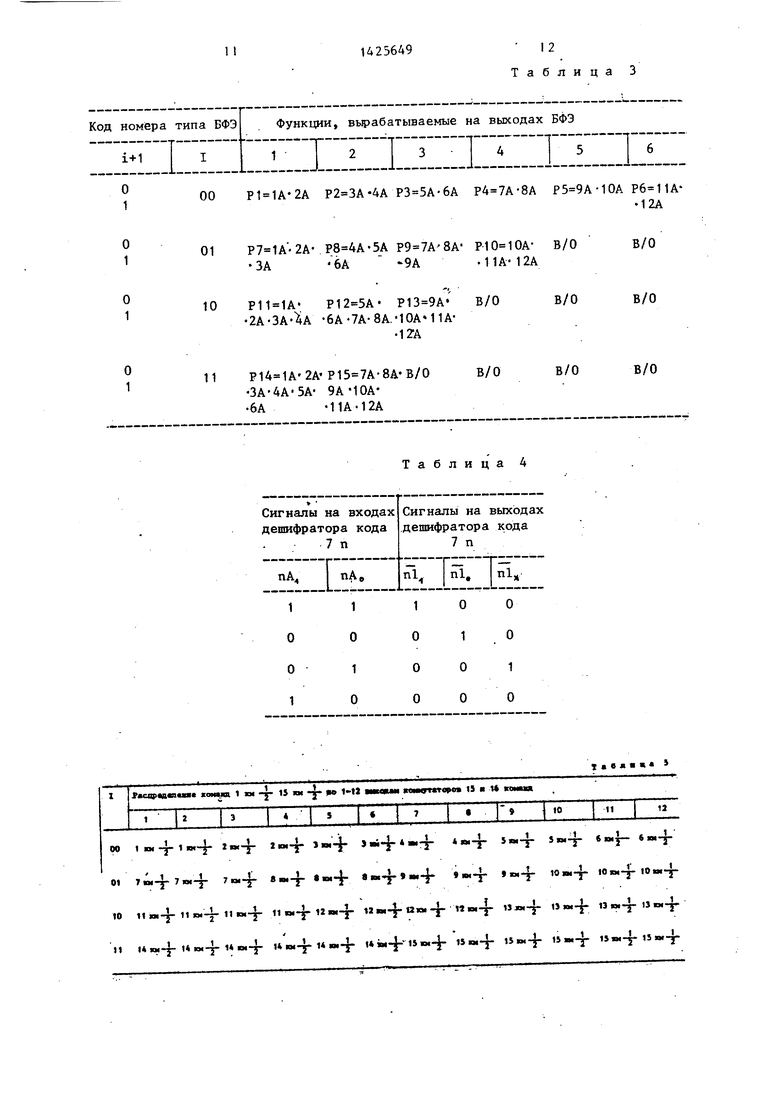

В табл. 3 приведен для каждого БФЭ двоичный код номера, его типа и для каждого его выхода - логическая функция, реализуемая на этом выходе.

Если БФЭ какого-либо типа имеет только Kj выходов, то в К Kj-м столбце соответствующей строки в табл. 3 дан признак В/0-выход номера К в данном БФЭ отсутствует.

При работе модуля на его входы (фиг. 1 и 2) подаются следующие сигналы: регулярная последовательность синхроимпульсов на вход 6; код номера типа I на входы 3 и i+1-й разряд номера типа на вход 4, первые разряды КП сигналов 1A-NA на входы 1 |

55

вторые разряды , КП сигналов 1A-NA на входы 2.

Коды на входах 1-4 должны сохраняться в течение не менее двух тактов.

51425649

Одновременно с изменением сигна- лов на входах 1-4 на вход 5 модуля поступает импульсный сигнал И, длиной в один период синхронизации.

На регистре 22 сигналы с входов 4 и 5 задерживаются на один такт со - ответственно на первых и втором выходах регистра 22 вырабатываются сигналы HTj и И.J.10

Дешифратор 7.П, где .1 п N преобразует КП сигнала пА в троичный позиционный код, логический О в первом, втором и третьем разряде которого означает наличие соответственно логической 1, логических О и X на входе пА БФЭ согласно табл.4.

Блоки 8.2-8.4 расчета функций рассчитывают функции Fe, где , аналогичные функциям Р, приведенным в табл. 3 от аргументов соответствен15

20

го ма ра ля щи

пр ко ес су хо та

с мо в

за ка ра в

но 11,-N1, ;

1b-Nlo. 1b-Nb

Тем

С выходов мультиплексоров 18 указанные данные поступают на входы бло ка 8,1 расчета функций, в котором рассчитываются пункции по формулам (1), аналогично функциям, описанным в табл. 3 Распределение выходных

о -к -l

самым производится анализ входных ситуаций на входах Mj элементов, сое- 25 -Сигналов блока 8.1 по входам регист- |тавляющих рассчитываемый БФЭ. Резуль- ров 20 и 21 производится коммутато- |таты анализа F((), F () , Ff (га) ) несут информацию о сочета1нии логических 1, О, X и Z

.к

ром 19 в соответствии с табл. 7

Коммутатор 19 функций под воздействием номера типа БФЭ, поступающего на его управляющие входы из L функций, рассчитанные блоком 8,1, выбирает только те, которые составляют рассчитываемьй БФЭ типа j.

X и

1на входах Mj К-го элемента БФЭ типа зо р и служат исходными данными для фор- |мирования команд перекодировки. I Формирователь SN команд перекодировки по анализу величин с выходов . )5локов расчета функций вырабатывает (три команды 1 licMi По первой команде все КП на входах М перекодиру- IJOTCH в КП, соответствующие состоя- ию X, как в (3) и (4). По второй

омавде все КП, соответствующие сое- „ выходах регистров 20 и 22 1гоянию Z на каких-либо входах, из

35

.Прием информации с выходов коммутатора 19 на регистры 20 и 21 происходит по сигналам соответственно И, и И,,

Таким образом, по окончании сигнапоявляются и сохраняются до конца следующего импульса И КП выходных сигналов БФЭ, являющихся выходами 24 модуля.

М входов перекодируются в КП, соот- етствующие логической 1, как в |2) и в (6).

Третья команда говорит о наличии недопустимого сочетания элементов, как в (3) на входах Mj .Третьи команды из формирователей 9 поступают Иа входы формирователя 14 признака недопустимого сочетания аргументов.

На элементах И 27 группы собираются признаки для всех типов БФЭ, а мультиплексор 28 выбирают из них тот, который соответствует рассчитываемому

в данный момент БФЭ THna,j. Этотgg диться с момента конца импульса И. до

п|ризнак поступает на выход 26 модуля. конца следующего импульса И, , т.е.

при максимальном темпе работы модуля

; Первые и вторые команды с выходов ф1ормирователей 9 поступают на инфор- м|ационные входы соответственно первов момент И. считывается результат расчета предыдущего БФЭ.

0

5

0

го 15 и второго 16 коммутаторов команд, которые под воздействием номера типа J, поступающего на их управляющие входы, выбирают соответствующие входам БФЭ типа j команды (табл.5).

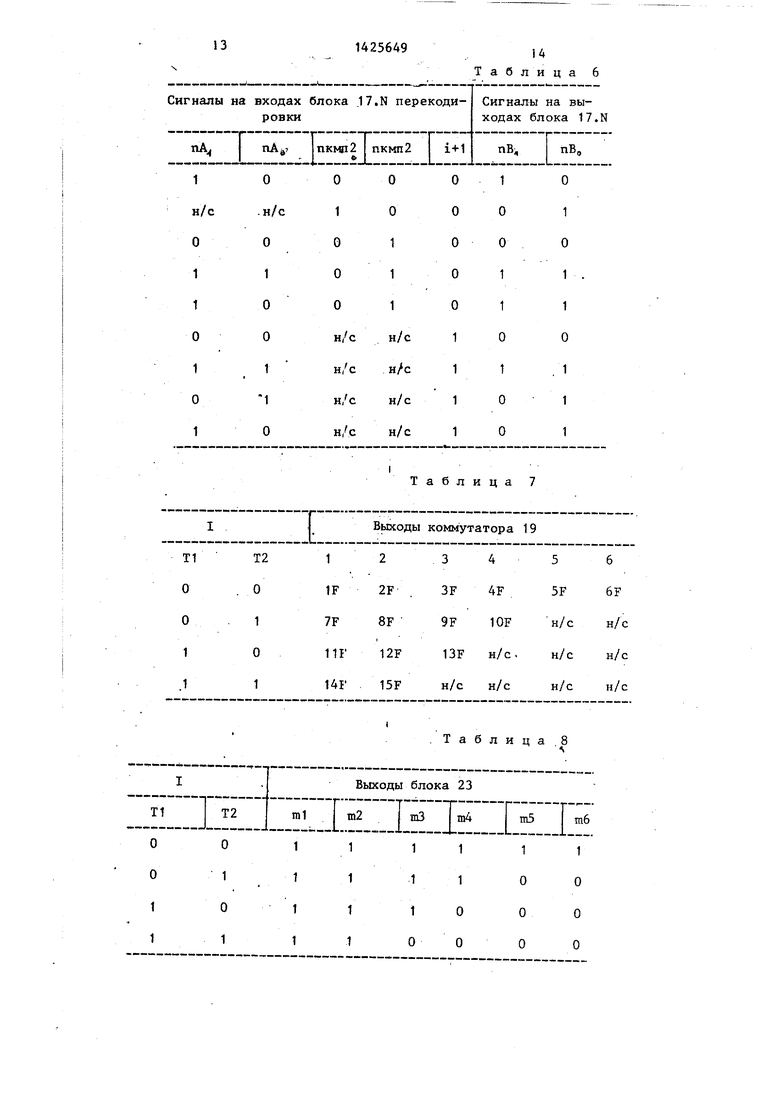

.Блок 17.N перекодировки (фиг,5) при наличии сигнала на входе 4 перекодирует код А А , в код В BO либо, если логическая 1 на входе 4 отсутствует, пропускает код ,, на выходы блока 17.N в соответствии с табл; 6.

Мультиплексор 18 группы передает с входов на свои выходы данные пВ, .в моменты времени lii 1 и данные пВо в моменты времени И. 1 (Hi Ь).

С выходов мультиплексоров 18 указанные данные поступают на входы блока 8,1 расчета функций, в котором рассчитываются пункции по формулам (1), аналогично функциям, описанным в табл. 3 Распределение выходных

5 -Сигналов блока 8.1 по входам регист- ров 20 и 21 производится коммутато-

-Сигналов блока 8.1 по входам регист- ров 20 и 21 производится коммутато-

ром 19 в соответствии с табл. 7

Коммутатор 19 функций под воздействием номера типа БФЭ, поступающего на его управляющие входы из L функций, рассчитанные блоком 8,1, выбирает только те, которые составляют рассчитываемьй БФЭ типа j.

зо

„ выходах регистров 20 и 22

35

.Прием информации с выходов коммутатора 19 на регистры 20 и 21 происходит по сигналам соответственно И, и И,,

Таким образом, по окончании сигна „ выходах регистров 20 и 22

появляются и сохраняются до конца следующего импульса И КП выходных сигналов БФЭ, являющихся выходами 24 модуля.

Блок 23 вырабатывает свои выходные сигналы в соответствии с табл.8 истинности.

Указанные сигнапы поступают на вы- . ходы 25 модуля и являются признаками действительности выходных сигналов модуля.

Считывание результатов расчета с выходов 24-26 модуля может произвов момент И. считывается результат расчета предыдущего БФЭ.

Формула изобретения

модуля соединены с вторьми входами соответствующих дешифраторов кода аргумента группы и с вторыми входами соответствующих блоков перекодировки группы, первые и вторые выходы кото- рьос соединены соответственно с первыми и вторыми информационными входами соответствуюшдх мультиплексоров группы, первые выходы дешифраторов кода аргумента группы соединены с со- ответствукщими входами группы второго блока расчета функции, выходы группы которого соединены с первыми входами соответствующих формирователей кЬманд группы, вторые выходы дешифраторов кода аргумента группы соединены с соответствующими входами группы третьего блока расчета функции, выходы группы которого соединены с вторыми входами соответствующих формирователей команд группы, третьи выходы дешифраторов кода аргумента группы соединены с соответствующими входами группы четвертого блока расчета функции, выходы группы которых соединены с третьими входами соответствующих формирователей команд группы, первые выходы которых соединены с соответствующими инфор.мационными вко- дами группы первого коммутатора команд, выходы группы которого соединены с третьими входами соответствую- 1ЩИХ блоков перекодировки группы, четвертые входы которых соединены с соответствующими выходами группы второго коммутатора команд, информационные входы группы которого соединены с вторыми выходами соответствующих формирователей команд группы, третьи выходы которьк соединены с соответствующими информационными входами групп формирователя признака недопустимого сочетания аргументов, выход которого является выходом признака недопустимого сочетания аргументов модуля, первьй вход задания функции которого соединен с упразпяютщми. входами первого и второго коммутаторов команд и с первым управляющим входом формирователя признака недопустимого сочетания аргументов, второй управляющий вход которого соединен с пятьми входами блоков перекодировки группы и вторым входом задания.функции модуля.

и мультиплексор, причем информационные входы группы формирователя признака недопустимого сочетания аргументов соединены соответственно с входа ;ми элементов И группы, выходы кото- |рых соединены с соответствующими ин- 1формацнонными входами мультиплексор первый и второй управляющие входы и выход которого являются соответствен но первым и вторым управляющим входами и выходом формирователя признака недопустимого сочетания аргументов.

Таблица 1

Неопределенное состояние X

Высокоимпульс- ное состояние

Таблица2

12

15

11

01

10

. 2А- Р8 4А-5А Р9 7А 8А В/О ЗА-бА 9А.11А-12А

В/О 2А-ЗА ХА 6А-7А-8А. 10АЧ1АIZA

В/О

11

Р14 1А 2А Р15 7А-8А В/0 ЗА-4А 5А 9А-10А- 6А-IIA-UA

Р«сар«в«дша ° « -J- 15 «и -J ре i

торев Ч т U комввя

1 JI Гэ 4 5 « 7 I 0 I 11

001 «и- 11п-| -г

01Тш- Т - вш- «к- 9 IM-J -}- 10 m- lOn-j-tOn 10 И хм- 11 ni-|- Пки- 11 iM- 1Z m-j-12 п-у-Оки-р17 Ю|-|- 11лм- О «м- 13 см-j- 13 п

V

IM-J- U KM-j- 15

Л 1 км- t «M-j- 1 et-j

4

lOn-j- Ют i-|- 13 jo.- 13 m- 13cM-j-l3i

,-f 15

1- 15ie«-|- m- 13«и-у

1425649

12 Таблица 3

В/О

В/О

В/О

В/О

В/О

В/О

Таблица 4

t«eji ««

торев Ч т U комввя

-г

« IM-J -}- 10 m- lOn-j-tOn -р17 Ю|-|- 11лм- О «м- 13 см-j- 13 п

4lOn-j- Ют-у- i-|- 13 jo.- 13 m- 13cM-j-l3i

,-f 15.41- 15ie«-|- m- 13«и-у

13

1425649

i4 Таблица 6

Таблица 7

Таблица ,8

, 4

нт

77

Г2

Редактор Г.Ге()бер

Составитель А.Клюев

Техред М.Ходанич Корректор И.Муска

Фиг. 5

1

/

w|

3 3

Лй.5

| Многофункциональный логический модуль | 1984 |

|

SU1174918A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР ,№ 1164693, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| , | |||

Авторы

Даты

1988-09-23—Публикация

1987-03-31—Подача