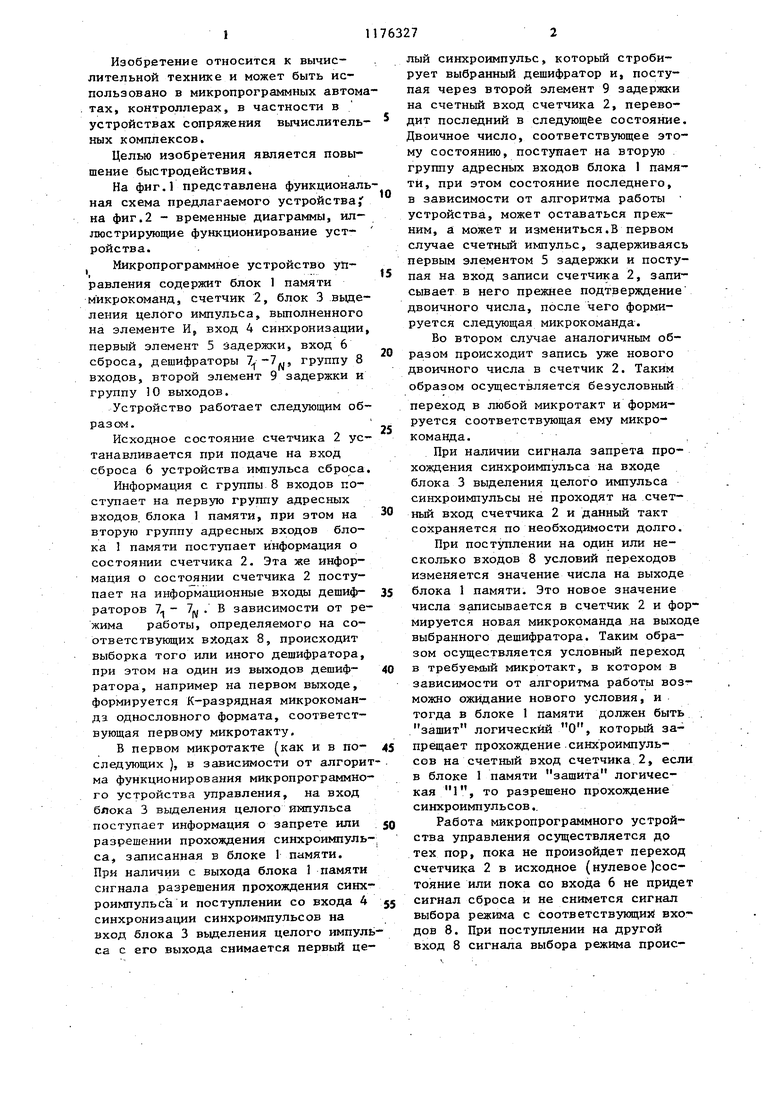

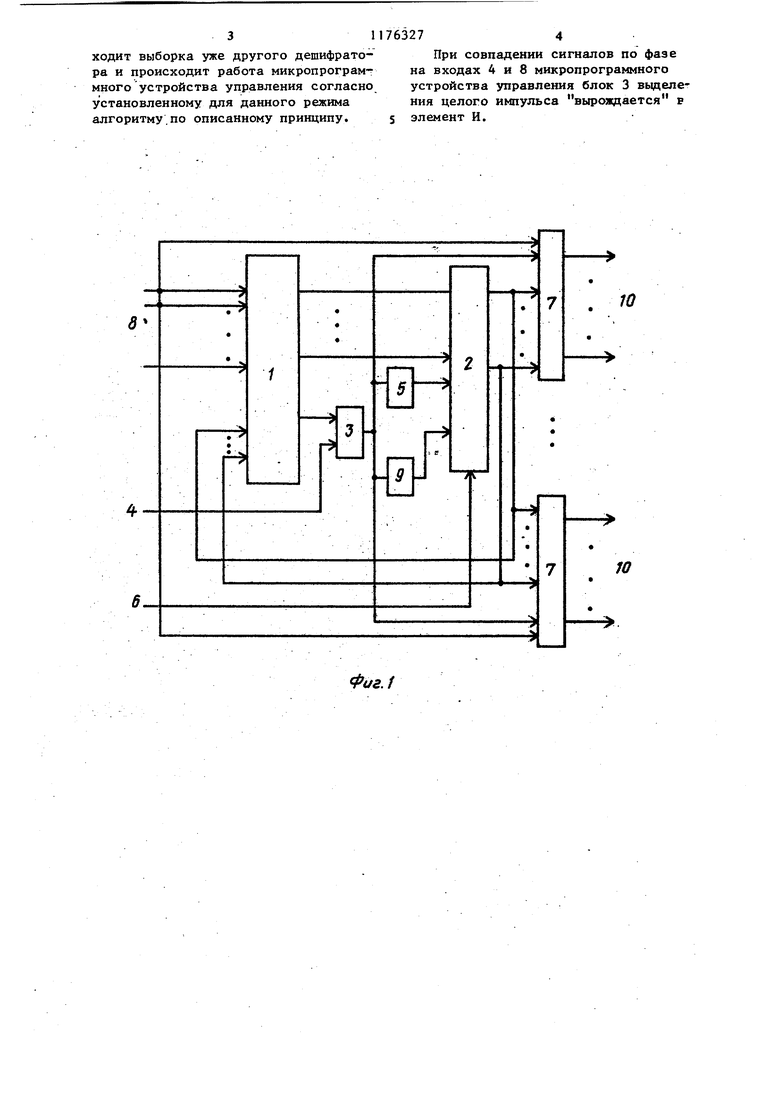

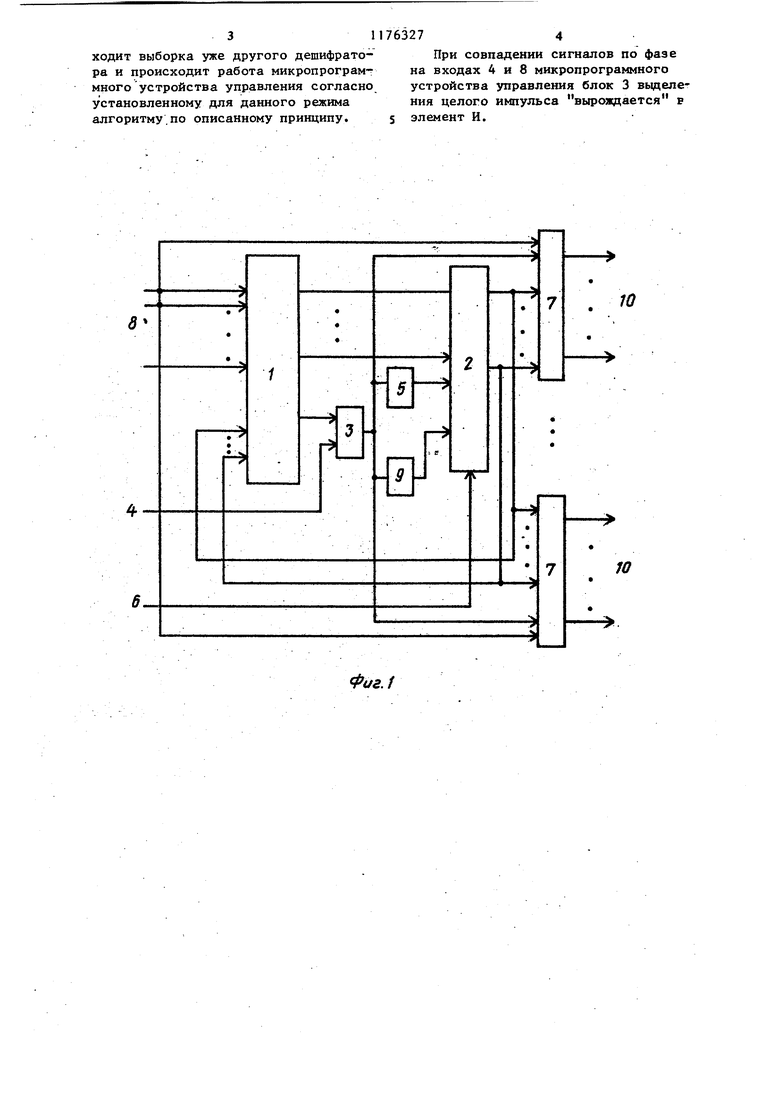

Изобретение относится к вычислительной технике и может быть использовано в микропрограммных автом тах, контроллерах, в частности в устройствах сопряжения вычислитель ных комплексов. Целью изобретения является повышение быстродействия На фиг.1 представлена функционал ная схема предлагаемого устройства/ на фиг.2 - временные диаграммы, иллюстрирующие функционирование устройства. I Микропрограммное устройство управления содержит блок 1 памяти микрокоманд, счетчик 2, блок 3 выде ления целого импульса, вьтолненного на элементе И, вход 4 синхронизации первый элемент 5 задержки, вход 6 сброса, дешифраторы .,, группу 8 входов, второй элемент 9 задержки и группу 10 выходов. Устройство работает следующим об разом. Исходное состояние счетчика 2 ус танавливается при подаче на вход сброса 6 устройства импульса сброса Информация с группы 8 входов поступает на первую группу адресных входов, блока 1 памяти, при этом на вторую группу адресных входов блока 1 памяти поступает информация о состоянии счетчика 2. Эта же информация о состоянии счетчика 2 поступает на информационные входы дешифраторов 1, - 7.J . В зависимости от ре жима работы, определяемого на соответствующих входах 8, происходит выборка того или иного дешифратора, при этом на один из выходов дешифратора, например на первом выходе, формируется К-разрядная микрокоманда однословного формата, соответствующая первому микротакту. В первом микротакте как и в последующих ), в зависимости от алгори ма функционирования микропрограммно го устройства управления, на вход блока 3 выделения целого импульса поступает информация о запрете или разрешении прохождения синхроимпуль са, записанная в блоке 1 памяти. При наличии с выхода блока 1 памяти сигнала разрешения прохождения синх роимпульса и поступлении со входа 4 синхронизации синхроимпульсов на вход блока 3 выделения целого импул са с его выхода снимается первый це лый синхроимпульс, который стробирует выбранный дешифратор и, поступая через второй элемент 9 задержки на счетный вход счетчика 2, переводит последний в следующее состояние. Двоичное число, соответствующее этому состоянию, поступает на вторую группу адресных входов блока I памяти, при этом состояние последнего, в зависимости от алгоритма работы устройства, может оставаться прежним, и может и измениться.В первом случае счетный импульс, задерживаясь первым элементом 5 задержки и поступая на вход записи счетчика 2, записывает в него прежнее подтверждение двоичного числа, после чего формируется следующая микрокоманда. Во втором случае аналогичным образом происходит запись уже нового двоичного числа в счетчик 2. Таким образом осуществляется безусловный переход в любой микротакт и формируется соответствующая ему микрокоманда. При наличии сигнала запрета прохождения синхроимпульса на входе блока 3 выделения целого импульса синхроимпульсы не проходят на счетный вход счетчика 2 и данный такт сохраняется по необходимости долго. При поступлении на один или несколько входов 8 условий переходов изменяется значение числа на выходе блока 1 памяти. Это новое значение числа записывается в счетчик 2 и фор мируется новая микрокоманда на выходе выбранного дешифратора. Таким образом осуществляется условный переход в требуемый микротакт, в котором в зависимости от алгоритма работы возможно ожидание нового условия, и тогда в блоке 1 памяти должен быть зашит логический О, который запрещает прохождение .синхроимпульсов на счетный вход счетчика.2, если в блоке 1 памяти зашита логическая 1, то разрешено прохождение синхроимпульсов.. Работа микропрограммного устройства управления осуществляется до тех пор, пока не произойдет переход счетчика 2 в исходное (нулевое )состояние или пока ао входа 6 не придет сигнал сброса и не снимется сигнал выбора режима с соответствующие входов 8. При поступлении на другой вход 8 сигнала выбора режима происходит выборка уже другого дешифратора и происходит работа микропрограм-; много устройства управления согласно Остановленному для данного режима алгоритму.по описанному принципу.

При совпадении сигналов по фазе на входах 4 И 8 микропрограммного устройства управления блок 3 выделения целого импульса вырождается в элемент И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1985 |

|

SU1304023A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1109751A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1111161A1 |

| Микропрограммное устройство управления | 1981 |

|

SU1005049A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1140120A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1179337A1 |

| Многотактное микропрограммное устройство управления | 1986 |

|

SU1332318A1 |

| Микропрограммное устройство управления | 1981 |

|

SU964641A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1989 |

|

SU1702377A1 |

| Устройство микропрограммного управления с контролем | 1990 |

|

SU1805466A1 |

МИКРОПРОГРАШНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее блок па- : мяти микрокоманд, счетчик и группу дешифраторов, причем выходы дешифраторов являются выходами устройства, выходы счетчика подключены к первой группе адресных входов блока памяти микрокоманд, группа из(п-1) выходов которого соединена с группой информационных входов счетчика ( где П - разрядность микрокоманды.), о т личающееся тем, что, с целью повышения быстродействия, оно дополнительно содержит блок выделения целого импульса, выполненньй на элементе И, и два элемента задержки, причем вторая группа адресных входов блока памяти микрокоманд подключена к группе входов кода команды устройства, Г)-и выход блока памяти микрокоманд соединен с первым входом элемента И, второй вход которого подключен ко входу синхронизации устройства, выход элемента И соединен с первыми стробирующими входами дешифраторов и со входами первого и второго элементов задержки, выт ходы которых соединены соответственно со входом записи и счетным вхос дом счетчика, вход сброса которого подключен ко входу сброса устройства, вторые стробирующие входы дешифраторов подключены к соответс вунлцИм входам кода команды устройства. а Од го s|

Фаг.1

Фиг. 2

Авторы

Даты

1985-08-30—Публикация

1983-07-11—Подача