начальной микрокоманды устройства, счетчика и с группой входов третьегруппа выходов мультиплексора соедиг го элемента ИШ1, выход которого соенена с группой информационных входов динен с входом установки в 1 триггера.

1109751

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1103230A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130864A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1142832A1 |

| Многотактное микропрограммное устройство управления | 1983 |

|

SU1151963A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1381506A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1156071A1 |

| Устройство для программного управления и контроля | 1985 |

|

SU1280574A1 |

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

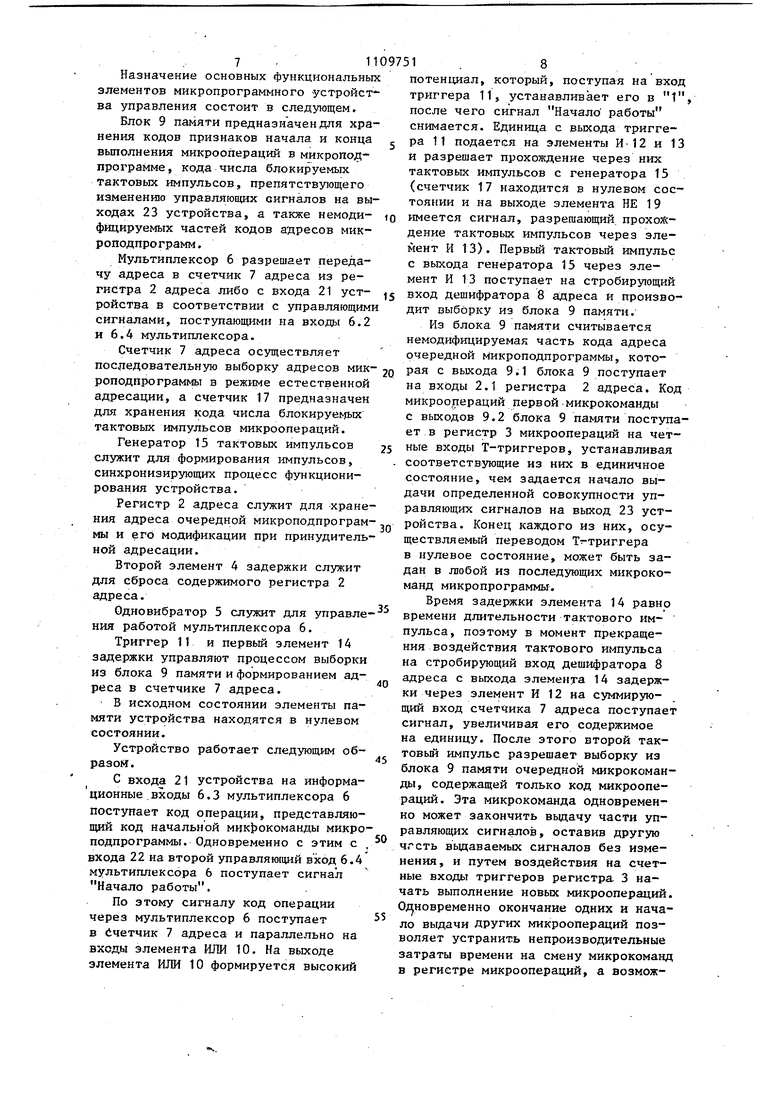

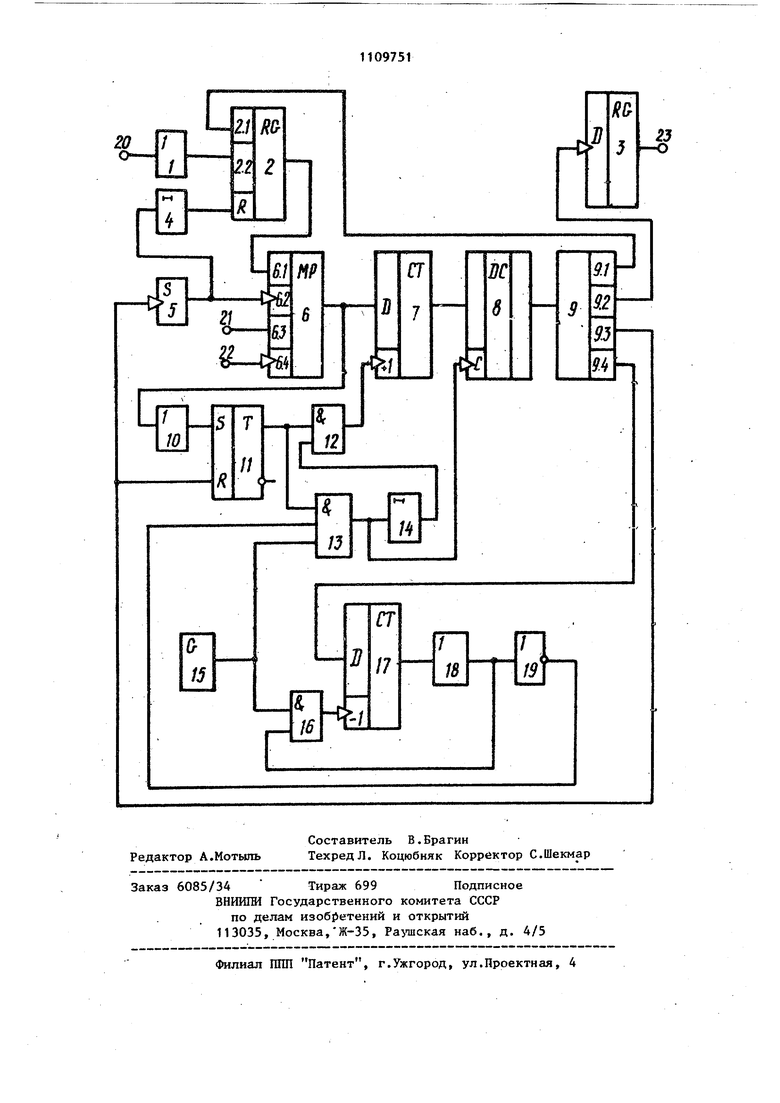

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее регистр адреса, три элемента ИЖ, первый и второй счетчики, дешифратор адреса, блок памяти микрокоманд, три элемента И, генератор тактовых импульсов, регистр микроопераций, причем группа входов первого элемента ИЛИ является группой входов логических условий устройства, выход первого элемента ИЛИ соединен с первым входом группы информационных входов регистра адреса, остальные входы группы информационных входов которого соединены с выходами адресного кода блока памяти микрокоманд, выходы кода микроопераций которого через регистр микроопераций соединены с управляющими выходами устройства, выходы кода числа блокируемых тактовых импульсов блока памяти соединены с информационными входами первого счетчика, вычитающий вход которого соединен с выходами первого элемента И, первый вход которого соединен с выходом второго элемента ИЛИ и через элемент НЕ с первым входом второго элемента И, группа входов второго элемента ИЛИ соединена с группой информационных выходов первого счетчика, второй вход первого элемента И соединен с выходом генератора тактовых импульсов и с вторым входом второго элемента И, выход которого соединен со стробирующин входом дешифратора адреса, группавходов и группа выходов которого соответственно соединены с группой информационных выходов второго счетчика и с группой адресных входов блока памяти микрокоманд, суммирующий, вход второго счетчика соединен с выходом третьего элемента И, отличающееся тем, что, с целью расширения области применения за счет реализации возможности асинхронной вьщачи управляющих сигналов, оно дополнительно содержит два элемента задержки, мультиплексор, одновибратор и триггер, причем выход триггера соединен с первым входом третьего элемента И и с третьим вхо дом второго элемента И, второй вход третьего элемента И через первый элемент задержки соединен с выходом второго элемента И, вход установки СО в О триггера соединен с выходом уп ел равления формированием адреса микрокоманды блока памяти микрокоманд и с входом одновибратора, выход которого соединен с первьм управляющим входом мультиплексора и через второй элемент задержки - с входом установки в О регистра адреса, группа выходов которого соединена с первой группой информационных входов мульти плексора, второй управляющий вход которого является входом -управления началом работы устройства, вторая группа информационных входов мультиплексора является группой входов кода

Изобретение относится к вычислительной технике и может быть использовано в качестве управляющего устройства с программируемой логикой в ЭВМ общего и специального назначения.

Известно микропрограммное устройство управления, содержащее генератор тактовых импульсов, группу счетчиков, группу триггеров, элемент И, регистр адреса, элемент задержки, блок памяти, регистр микрокоманд, дешифраторы, которое обеспечивает переменный микротакт, переходя в следующее состояние после выполнения самой длинной микрооперации в текущей микрокоманде 1.

Недостатком устройства является узкая область применения, обусловленная невозможностью выполнения микроопераций с произвольными моментами начала и длительностью в микротакте.

Известно также микропрограммное устройство управления, содержащее блок памяти микрокоманд,- счетчик адреса, дешифратор адреса, регистр микрокоманд, счетчик тактов, блок памяти микроопераций, дешифратор микроопераций, группы элементов И, элемент ИЛИ 23.

Недостатком указанного устройства является узкая область применения, обусловленная выполнением микроопераций за один микротакт и невозможностью выполнения микроопераххий с произвольными моментами начала и длительностью в микротакте.

Наиболее близким к предлагаемому по технической сущности и достигаемому результату является микропрограммное устройство управления, содержаще последовательно соединенные первьй регистр адреса., первый-дешифратор, первый блок памяти, второй регистр- адреса и первый блок элементов И, второй вход которого является входом логичес ких условий устройства, а выход соединен с входом первого регистра адреса, генератор тактовых импульсов, элемент ИЛИ, счетчик, выход которого соединен с входом дешифратора, второй, третий и четвертый блоки памяти, второй, третий и четвертый дешифраторы, третий и четвертый регистры адреса, группу счетчиков, узел коммутации моментов начала микроопераций, группу блоков элементов И, первый, второй и третий элементы И, группу элементов ИЛИ, элемент НЕ, причем перв1йй выход генератора тактовых импульсов подключен к первому входу первого элемента И, второй вхо которого подключен через элемент НЕ к выходу элемента ИЛИ и к первому входу второго элемента И, выход первого элемента И соединен с управляющими входами первого, второга, третьего и четвертого дешифраторов, информационные входы второго, третьего четвертого дешифраторов соединены соответственно с вторым, третьим, четвертым выходами первого регистра адреса, а выходы через второй, третий, четвертьпЧ блоки памяти - с первым выходом устройства, входами третьего и четвертого регистров адреса соответственно, выходы разрядов, кроме последнего третьего регистра адреса, соединены с первыми входами узла коммутации моментов начала микроопераций, вторые входы которого соединены с выходами дешифратора импульсов, а выходы узла коммутации соединены с первыми входами группы блоков элементов И, вторые входы которых соединены с выходами четвертого регистра адреса, а выходы - с информационными входами группы счечиков, выходы которых групу элементов ИЛИ подключены к второму выходу устройства и к входам элемента ИЛИ, второй выход генератора импульсов соединен с первым входом трет| его элемента И, второй вход, которого под лючен к выходу последнего разряда третьего регистра адреса, а выход - к счетному входу счетчика и к второму входу элемента И, выход которого соединен с вычитающими входани группы счетчиков 3. Недостатком известного устройства является узкая область применения. При формировании микроопераций с про .извольньми моментами начала и длиIтельноетью в микротакте известное устройство не позволяет выдавать несколько микроопераций с одного выход за время выдачи одной длинной микр операции с другого выхода. Оно не no воляет формировать микрооперации с длительностью, превьппающей длительность микротакта. Крсже того, во время выборки приз наков микроопераций из блоков памяти на объект управления не выдается полезной информации, что в значитель ной степени снижает быстродействие известного устройства и ограничивает область его применения. Задание в блоке памяти кодов длительности микроопераций влечет за собой большой объем оборудования для дополнительного хранения кода на выходе устройства и разворачивания его во временную последовательность. Это снижает в конечном счете функциональ ные возможности и быстродействие за счет временной задержки сигналов на элементах и приводит к увеличению внутреннего цикла работы устройства. Цель изобретения - расширение области применения за счет реализации возможности асинхронной вьдачи управляющих сигналов. Поставленная цель достигается тем что в устройство, содержащее регистр адреса, три элемента ИЛИ, первый и второй с 1етчики, дешифратор адреса, блок памяти микрокоманд, три элемента И, генератор тактовых импульсов, регистр микроопераций, причем группа входов первого элемента ИЛИ является группой входов логических условий устройства, выход первого элемен та ИЛИ Соединен с первым входом груп пы информационных входов регистра адреса, остальные входы группы инфор мационных входов которого соединены с выходами адресного кода блока памяти.микрокоманд, выходы кода микроопераций которого через- регистр микроопераций соединены с управляющими выходами устройства, выходы кода числа блокируемых тактовых импульсов блока памяти соединены синформацион- ными входами первого счетчика, вычитающий вход которого соединен с выходами первого элемента И, первый вход которого соединен с выходом второго элемента ИЛИ и через элемент НЕ с первым входом второго элемента И, группа входов второго злемента ИЛИ соединена с группой информационных выходов первого счетчика, второй вход первого элемента И соединен с выходом генератора тактовых импульсов и с вторым входом второго элемента И, выход которого соединен со стробирующим входом дешифратора адреса, груп|па входов и группа выходов которого соответственно соединены с группой информационных выходов второго счетчика и с группой адресных входов блока памяти микрокоманд, суммирующий вход второго счетчика соединен с выходом третьего элемента И, дополнительно введены два элемента задержки, мультиплексор, одновибратор и триггер, причем выход триггера соединен с первым входом третьего элемента И и с третьим входом второго элемента И, второй вход третьего элемента И через первый элемент задержки соединен с выходом второго элемента И, вход установки в О триггера соединен с выходом управления формирования адреса микрокоманды блока памяти микрокоманд и с входом одновибратора, выход которого соединен с первым управляющим входом мультиплексора и через второй элемент задержки - с входом установки в О регистра адреса, группа выходов которого соединена с первой группой информационных входов мультиплексора, второй управляющий вход которого является входом управления началом работы устройства, вторая группа информационных входов мультиплексора является группой входов кода начальной микрокоманды устройства, групп.а выходов мультиплексора соединена с группой информацион-. ных входов второго счетчика и с группой входов третьего элемента ИЛИ, выход которого соединен с входом установки в 1 триггера. Сущность изобретения состоит в том, что управляющие сигналы, вьдаваемые микропрограммными устройствами управления, характеризуются начаS11лом, длительностью и концом выдачи. Каждый из этих признаков может быть закодирован в блоке памяти. В предла гаемом устройстве, в отличие от известных, применяется кодирование начала и конца управляющего импульса Сам импульс формируется счетным триг гером регистра микроопераций в процессе двух выборок из блока памяти устройства. По первому сигналу из блока памят счетный триггер переходит к единично состояние и начинает вьщавать управляющий импульс, по второму сигналу триггер возвращается в исходноесоетояние и управляющий импульс прерывается. Такое кодирование с применением счетных триггеров позволяет орг низовать асинхронну о вьщачу сигналов управления не только во время выполнения одной микрокоманды или микротакта, но и в пределах всей микропрограммы. Одна микрокоманда в блоке памяти может хранить как признаки начала, так и признаки конца микроопераций, а также признак отсутствия смены состояния счетного триггера. Микрокоманды выбираются по мере необ ходимости изменения управляющих сиг1налов. В один и тот же момент могут задаваться как окончание выполнивших ся микроопераций, так и начало выпол нения очередных микроопераций. При этом управляю;щие сигналы на третьей группе выходов могут оставаться без изменения ввиду отсутствия воздействия на счетньй вход триггера регистра микроопераций. Так как начало и конец сигнала управления задшотся в различных микрокомандах, то его . длительность может быть произвольной в предела:; микропрограммы. Наименьшая длительность управляющего сигнала равна наименьшей выполняемой в операционном устройстве микроопе-. рации и зависит только от быстродействия выбранной элементной базы микропрограммного устройства управления Для блокировок, например запрещения прерывания выполняемой микропрограммы, длительность определенного управ ляющего сигнала может быть равна вре мени выполнения всей микропрограммы. За время выполнения подобных длинных микрооперации на регистре микро операций может смениться несколько микрокоманд, каждая из которых на одном или нескольких выходах может последовательно начинать и заканчи1вать вьщачу коротких или средних по длительности управляющих импульсов микроопераций, за счет чего организуется асинхронный режим работы устройства. Выборка очередной микрокоманды совмещается со временем выполнения предьщущей микрокоманды, чем обеспечивается непрерывная выдача микроопераций и значительное повышение быстродействия устройства. Кроме того, независимая вьщача управляющих сигналов с каждого выхода позволяет оптимизировать во времени выполнение групп линейных последовательностей микрокоманд и объединить их в отдельные микроподпрограммы с присвоением одного адреса, причем производить выполнение микропрограммы в режиме естественной адресации, а переходы между микроподпрограммами - в режиме принудительной адресации. На чертеже приведена функциональная схема микропрограммного устройства управления. Устройство содержит первый элемент ИЛИ 1, регистр 2 адреса с входами 2.1 (труппа информационных входов), на которые поступает немодифицируемая часть адресного кода,2.2первый группы информационных входов, на который поступает модифицируемая часть адресного кода, регистр 3 микроопераций, второй элемент 4 задержки, одновибратор 5, мультиплексор 6 с входами 6.1 (первая группа информационных входов), 6.2 (первый управляющий ), (вторая группа информационных входов), 6.4 (второй управляющий вход), счетчик 7 адреса, дешифратор 8 адреса, блок 9 памяти микрокоманд с выходами 9.1 (выходы адресного кода), 9.2 (выходы кода микроопераций), 9.3 (выход управления формирования адреса микрокоманды) , 9.4 (выходы кода числа блокируемых тактовых импульсов), третий элемент ИЛИ 10, триггер 11, третий элемент И 12, второй элеент И 13, первый элемент 14задержки, генератор 15-тактовых импульсов, первьй элемент И 16, счетчик 17, торой элемент ИЛИ 18, элемент НЕ 19, ход 20, логических условий устройста, вход 21 кода начальной микрокоанды устройства, входв 22 управления ачалом работы устройства, управляюие выходы 23 устройства. 7 . 1 Назначение основных функциональны элементов микропрограммного устройст ва управления состоит в следующем. Блок 9 памяти предназначен для хра нения кодов признаков начала и конца вьтолнения микроопераций в микроподпрограмме, кода числа блокируемых тактовых импульсов, препятствующего изменению управляющих сигналов на вы ходах 23 устройства, а также немодифйцируемых частей кодов адресов микроподпрограмм . Мультиплексор 6 разрешает передачу адреса в счетчик 7 адреса из регистра 2 адреса либо с входа 21 устройства в соответствии с управляющим сигналами, поступающими на входы 6.2 и 6.4 мультиплексора. Счетчик 7 адреса осуществляет последовательную выборку адресов мик роподпрограммы в режиме естественной адресации, а счетчик 17 предназначен для хранения кода числа блокируемых тактовых импульсов микроопераций. Генератор 15 тактовых импульсов служит для формирования импульсов, синхронизирующих процесс функционирования устройства. Регистр 2 адреса служит для хране ния адреса очередной микроподпрограм мы и его модификации при принудитель ной адресации. Второй элемент 4 задержки служит для сброса содержимого регистра 2 адреса. Одно вибратор 5 служит для управле ния работой мультиплексора 6. Триггер 11 и первый элемент 14 задержки управляют процессом выборки из блока 9 памяти и формированием адреса в счетчике 7 адреса. В исходном состоянии элементы памяти устройства находятся в нулевом состоянии. Устройство работает следующим образои. С входа 21 устройства на информационные.входы 6.3 мультиплексора 6 поступает код операции, представляющий код начальной микрокоманды микро подпрограммы. Одновременно с этим с входа 22 на второй управляющий вход 6.4 мультиплексора 6 поступает сигнал Начало работы. По этому сигналу код операции через мультиплексор 6 поступает в йчетчик 7 адреса и параллельно на Влод.ы элемента ИЛИ 10. На выходе элемента ИЛИ 10 формируется высокий 1 потенциал, который, поступая на вход триггера 11, устанавливает его в 1, после чего сигнал Начало работы снимается. Единица с выхода триггера 11 подается на элементы И-12 и 13 и разрешает прохождение через них тактовых импульсов с генератора 15 (счетчик 17 находится в нулевом состоянии и на выходе элемента НЕ 19 имеется сигнал, разрешающий, прохождение тактовых импульсов через элемент И 13). Первый тактовый импульс с выхода генератора 15 через элемент И 13 поступает на стробирующий вход дешифратора 8 адреса и производит выборку из блока 9 памяти. Из блока 9 памяти считывается немодифицируемая часть кода адреса очередной Микроподпрограммы, которая с выхода 9.1 блока 9 поступает на входы 2.1 регистра 2 адреса. Код микроопераций первой микрокоманды с выходов 9.2 блока 9 памяти поступает в регистр 3 микроопераций на четные входы Т-триггеров, устанавливая соответствующие из них в единичное состояние, чем задается начало выдачи определенной совокупности управляющих сигналов на выход 23 устройства. Конец каждого из них, осуществляемый переводом Т триггера в нулевое состояние, может быть задан в любой из последующих микрокоманд микропрограммы. Время задержки элемента 14 равно времени длительности тактового импульса, поэтому в момент прекращения воздействия тактового импульса на стробирующий вход дешифратора 8 адреса с выхода элемента 14 задержки через элемент И 12 на суммирующий вход счетчика 7 адреса поступает сигнал, увеличивая его содержимое на единицу. После этого второй тактовьй импульс разрешает выборку из блока 9 памяти очередной микрокоманды, содержащей только код микроопераций. Эта микрокоманда одновременно может закончить вьщачу части управляющих сигналов, оставив другую чгсть выдаваемых сигналов без изменения, и путем воздействия на счетные входы триггеров регистра 3 начать выполнение новых микроопераций. Одновременно окончание одних и начало выдачи других микроопераций позволяет устранить непроизводительные затраты времени на смену микрокоманд в регистре микроопераций, а возможность не прерывать управляющий сигна при смене микрокоманд обеспечивает произвольную длительность этого сигнала ь пределах микропрограм ш. Такая организация работы устройст за предполагает выборку из блока 9 памяти микрокоманд только в необходи мые моменты, времени, когда требуется изменение выходных сигналов. Если в течение нескольких тактов генера- тора 15, начиная; с (h+1)-го такта, не требуется не прерывать и не начинать микрооперации, то в микрокоманде, выполняемой в п-м такте, задает ся код числа блокируемых тактовых импульсов. После выбора микрокоманды из блока 9 памяти код числа блокируемых тактовых импульсов с выхода 9.4 блока 9 поступает на информационные входы счетчика 17 и через элемент ИЛИ 18, элемент НЕ 19 запрещает прохождение тактовых импульсов че рез элемент И 13. Одновременно сигнал с выхода элемента ИЛИ 18 поступает на вход элемента И 16, разрешая прохождение через него тактовых импульсов с генератора 15 на вычитак)щи вход счетчика 17. В (n+l)-м такте работы устройства выборки микрокоман ды из блока 9 памяти не происходит, а импульс с генератора 15, поступая через элемент И 16 на вычитающий вход счетчика 17, уменьшает его содержимое на единицу. После обнуления счетчика 17 на выходе элемен та ИЛИ 18 устанавливается низкий потенциал, которьй через элемент НЕ 19 разрешает прохождение очередного так тового импульса через элемент И 13. Одновременно низкий потенциал с выхо да элемента ИЛИ 18 запрещает прохождение тактовых импульсов с генератора 15 на вычитаю1ций вход счетчика 17 через элемент И 16. Схема блокировки тактовых импульсов позволяет исключить хранение в блоке 9 памяти пустых микрокоманд. Линейная последовательность микро команд выполняется устройством в режиме естественной адресации, т.е. каждой последующей выборке из памяти предшествует увеличение содержимого счетчика адреса на единицу. Это позволяет не хранить в блоке 9 памяти адресные части всех микрокоманд, а следовательно, и уменьшить его объем Переходы между микроподпрограммами, т.е. переходы по логическим условиям осуществляются следуюпщм образом С регистра 3 микроопераций п --и микрокомандой задается микрооперация опроса устройства, от состояния которого зависит ветвление в микропрограм|ме. Сигнал с опрошенного устройства поступает на вход 20 микропрограммного устройства управления и через элемент ИЛИ 1 устанавливает триггер (вход 2.2) регистра 2 адреса в единицу, Если сигнала с опрашиваемого устройства не поступило, состояние моди фицируемого разряда регистра 2 адреса остается нулевым и таким образом формируется второй возможный адрес перехода. В (п+1)-и микрокоманде, соответствующей последней микрокоманде микроподпрогра1Ф1ы, задается конец микрооперации опрашиваемого устройства и сигнал управления перезаписью сформированного адреса из регистра 2 адреса в счетчик 7 адреса. После выборки из памяти 7п+1)-й микрокоманды управляющий сигнал с выхода 9.3 блока 9 памяти поступает на .вход установки а О триггера 11, устанавливая его в нулевое состояние, и на вход одновибратора 5. Нулевой потенциал с выхода триггера 11 запрещает прохождение тактовых имцульсов с генератора 15 через элементы И 12 и 13. В результате этого увеличение содержимого счетчика 7 адреса на единицу будет блокировано. Одновибратор 5 под воздействием управлякщего сигнала на его входе формирует импульс, длительность которого равна времени перезаписи-адреса из регистра 2 адреса в счетчик 7 адреса. Этот импульс с выхода одновибратора 5 поступает на управляющий вход 6.2 мультиплексора 6, разрешая перезапись адреса очередной микроподп1юграм о 1, и через элемент 4 задержки поступает на вход установки в О регистра 2 адреса, сбрасывая его содержимое после перезаписи адреса. Параллельно с перезаписью адреса в счетчик 7 адреса код адреса через элемент ИЛИ 10 устанавливает триггер 11 в 1. Сигнал выхода триггера 11 поступает на элементы И 12 и 13 и вновь разрешает генератору 15 тактовых импульсов производить последовательную выборку микрокоманд микроподпрограммы. Заметим, что переход по логическим условиям вызывается не всей совокупностью устройств управляемого объекта, а отдельными его частями, например

сумматором, поэтому нет необходимости прекращать выдачу управляющих сигналов в остальные части объекта, что и реализовано в управляющем устройстве, В то время, когда микропрограммное устройство управления переходит к другой микроподпрограмме, управляющие сигналы не выдаются на те устройства, от которых зависит этот переход, но вьщача их не прекращается для части управляемого объекта. Эти особенности должны быть учтены при программировании управляющей памяти микропрограммного устройства управления.

Для программ с большим количеством ветвлений возможности устройства позволяет организовать чисто принудительный режим адресации следующим образом. Группа микроопераций реализуется двумя микрокомандами, первая из которых содержит адресную часть и операционную часть, задающую начало выполнения микроопераций. Вторая микрокоманда содержит операционную часть, задающую конец выполняемых микроопераций и управляющий сигнал перезаписи адреса из регистра 2 адреса в счетчик 7 адреса. При этом работа устройства организуется так же, и было описано. Использование же естественной адресации при линейной последовательности микрокоманд позволяет значительно сократить общее время выполнения микроподпрограммы за счет рационального размещения во времени выполняемых микроопераций. Это обеспечивается новыми возможностями устройства, одновременно начинать одни и заканчивать другие микрооперации,а также свойством сохранения сигнала на выходе устройства при смене микрокоманд.

Окончание работы устройства после выполнения микропрограммы задается программным способом. Последняя микроподпрограмма осуществляет переход к микрокоманде с нулевой адресной частью и единственным управляющим признаком в операционной части. После выборки КЗ памяти управляющий сигнал с выхода 9.3 блока 9 памяти устанавливает триггер 11 в нулевое состояние, чем блокируются последующие сигналы обращения к памяти, и запускает одновибратор 5. Одновибратор 5 разрешает перезапись адреса через мультиллексор 6 из регистра 2 в счетчик 7. Но так как код адреса нулевой, то он, пройдя элемент ИЛИ 10, не может установить триггер 11 в единичное состояние, что сохраняет блоkиpoвкy тактовых импульсов генератора 15. Устройство ждет прихода нового кода операций и сигнала Начало работы.

Таким образом, асинхронная выдача сигналов управления улучшает технические характеристики предлагаемого устройства и расширяет область .его применения.

m

20

27

23

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Микропрограммное устройство управления | 1979 |

|

SU834700A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Микропрограммное устройство управления | 1976 |

|

SU615480A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Микропрограммное устройство управления | 1981 |

|

SU945866A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-23—Публикация

1983-04-15—Подача