первого элемента ИЛИ блока формирования установочных сигналов и со счетным входом счетчика адреса, второй выход постоянной памяти соединен с третьим входом блока элементов ИЛИ, вход чтения постоянной памяти соединен с выходом признака условного ветвления первого блока памяти микропрограмм, i -и выход кода номера канала внешнего ежима синхронизации которого (где ,к) соединен с первым входом j-ro элемента И группы блока коммутации обращений, второй вход которого соединен с выходом триггера, информационный вход которого соединен с (к+1)-м выходом кода номера канала внешнего режима синхронизации первого блока памяти микропрограмм, j-й выход кода номера канала внешнего режима синхронизации которого соединен CJ-M управляющим входом каждого мультиплексора группы (где 1,п, Я1- количество управляюш,их входов у мультиплексоров) , группа адресных входов постоянной памяти является группой входов логических условий устройства, вход второго формирователя импульсов соединен с выходом признака безусловного ветвления второго блока памяти микропрограмм, вход третьего формирователя импульсов является входом запуска устройства, вход шестого формирователя импульсов соединен с выходом признака линейной последовательности микрокоманд второго блока памяти микропрограмм, выход признака режима которого соединен через элемент НЕ блока коммутации обращений с входом синхронизации триггера, вход установки в «О которого подключен к установочному входу устройства, выход i -го элемента И группы блока коммутации обрашений соединен со стробирующим входом i-ro мультиплексора группы, выход которого соединен с i -м входом элемента ИЛИ блока коммутации обращений, группа информационных входов i -го мультиплексора группы является i -и группой входов внешних обращений устройства, выход кода микрооперации второго блока памяти микропрограмм является вторым управляющим выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1980 |

|

SU955058A1 |

| Параллельное микропрограммное устройство управления | 1983 |

|

SU1109750A1 |

| Устройство для управления восстановлением микропрограмм при сбоях | 1982 |

|

SU1056193A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Микропрограммное устройство управления и отладки микропрограмм процессора | 1984 |

|

SU1168937A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1259262A1 |

| Микропрограммное устройство управ-лЕНия | 1979 |

|

SU842815A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1130865A1 |

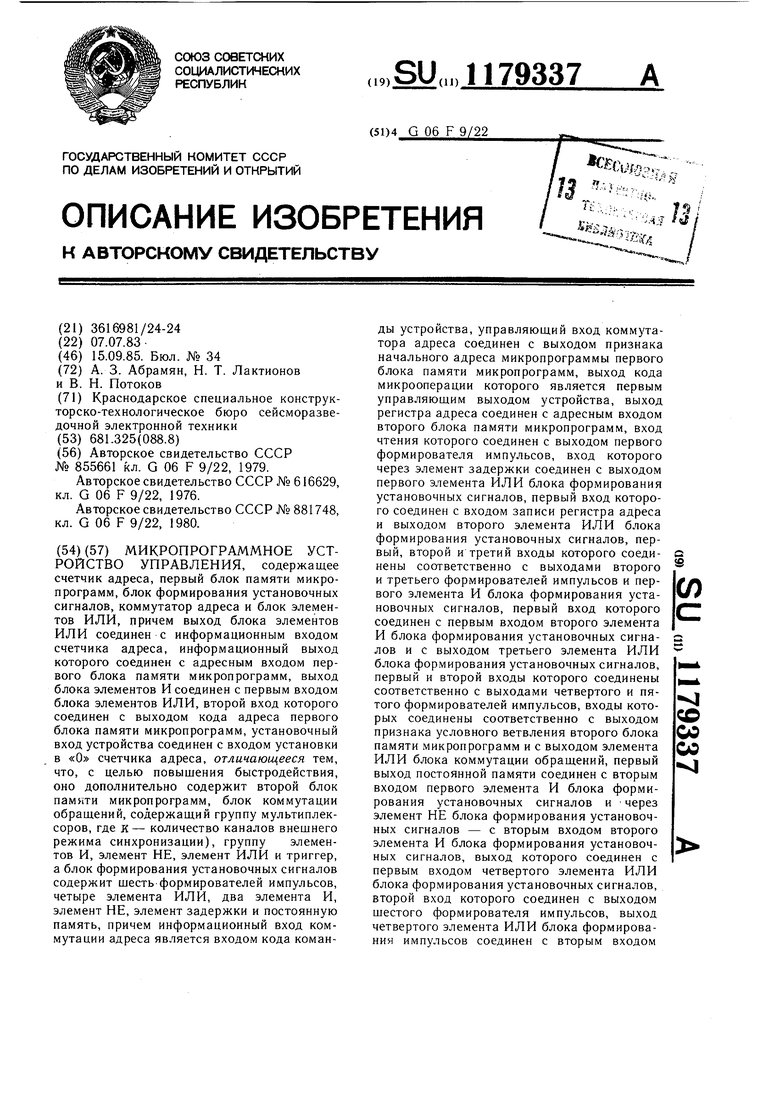

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее счетчик адреса, первый блок памяти микропрограмм, блок формирования установочных сигналов, коммутатор адреса и блок элементов ИЛИ, причем выход блока элементов ИЛИ соединен с информационным входом счетчика адреса, информационный выход которого соединен с адресным входом первого блока памяти микропрограмм, выход блока элементов И соединен с первым входом блока элементов ИЛИ, второй вход которого соединен с выходом кода адреса первого блока памяти микропрограмм, установочный вход устройства соединен с входом установки в «О счетчика адреса, отличающееся тем, что, с целью повышения быстродействия, оно дополнительно содержит второй блок памяти микропрограмм, блок коммутации обращений, содержащий группу мультиплексоров, где к- количество каналов внешнего режима синхронизации), группу элементов И, элемент НЕ, элемент ИЛИ и триггер, а блок формирования установочных сигналов содержит шесть формирователей импульсов, четыре элемента ИЛИ, два элемента И, элемент НЕ, элемент задержки и постоянную память, причем информационный вход коммутации адреса является входом кода команды устройства, управляющий вход коммутатора адреса соединен с выходом признака начального адреса микропрограммы первого блока памяти микропрограмм, выход кода микрооперации которого является первым управляющим выходом устройства, выход регистра адреса соединен с адресным входом второго блока памяти микропрограмм, вход чтения которого соединен с выходом первого формирователя импульсов, вход которого через элемент задержки соединен с выходом первого элемента ИЛИ блока формирования установочных сигналов, первый вход которого соединен с входом записи регистра адреса и выходом второго элемента ИЛИ блока формирования установочных сигналов, первый, второй и третий входы которого соеди§ нены соответственно с выходами второго и третьего формирователей импульсов и пер(Л вого элемента И блока формирования установочных сигналов, первый вход которого соединен с первым входом второго элемента И блока формирования установочных сигналов и с выходом третьего элемента ИЛИ блока формирования установочных сигналов, первый и второй входы которого соединены соответственно с выходами четвертого и пя того формирователей импульсов, входы кото;о со со рых соединены соответственно с выходом признака условного ветвления второго блока памяти микропрограмм и с выходом элемента ИЛИ блока коммутации обращений, первый выход постоянной памяти соединен с вторым входом первого элемента И блока формирования установочных сигналов и через элемент НЕ блока формирования установочных сигналов - с вторым входом второго элемента И блока формирования установочных сигналов, выход которого соединен с первым входом четвертого элемента ИЛИ блока формирования установочных сигналов, второй вход которого соединен с выходом щестого формирователя импульсов, выход четвертого элемента ИЛИ блока формирования импульсов соединен с вторым входом

1

Изобретение относится к вычислительной технике, в частности к устройствам микропрограммного управления, и может быть использовано при построении цифровых вычислительных машин и контроллеров внешних устройств, например, в телеметрических сейсморазведочных станциях.

Целью изобретения является повышение быстродействия.

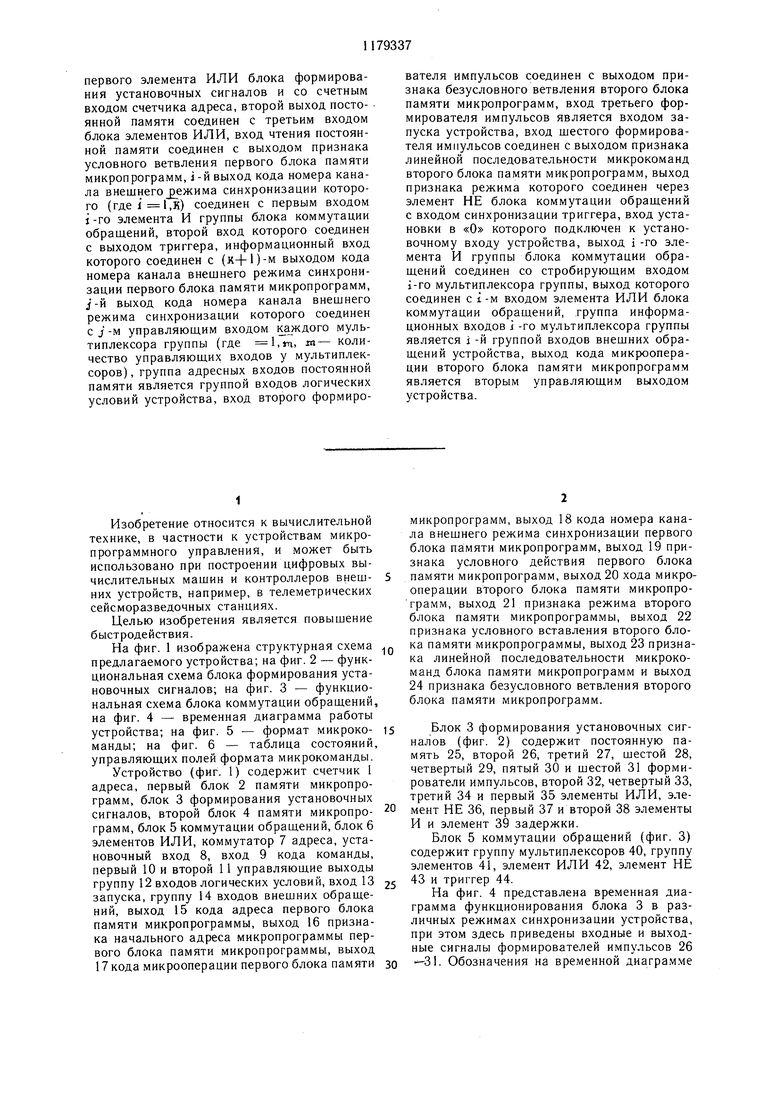

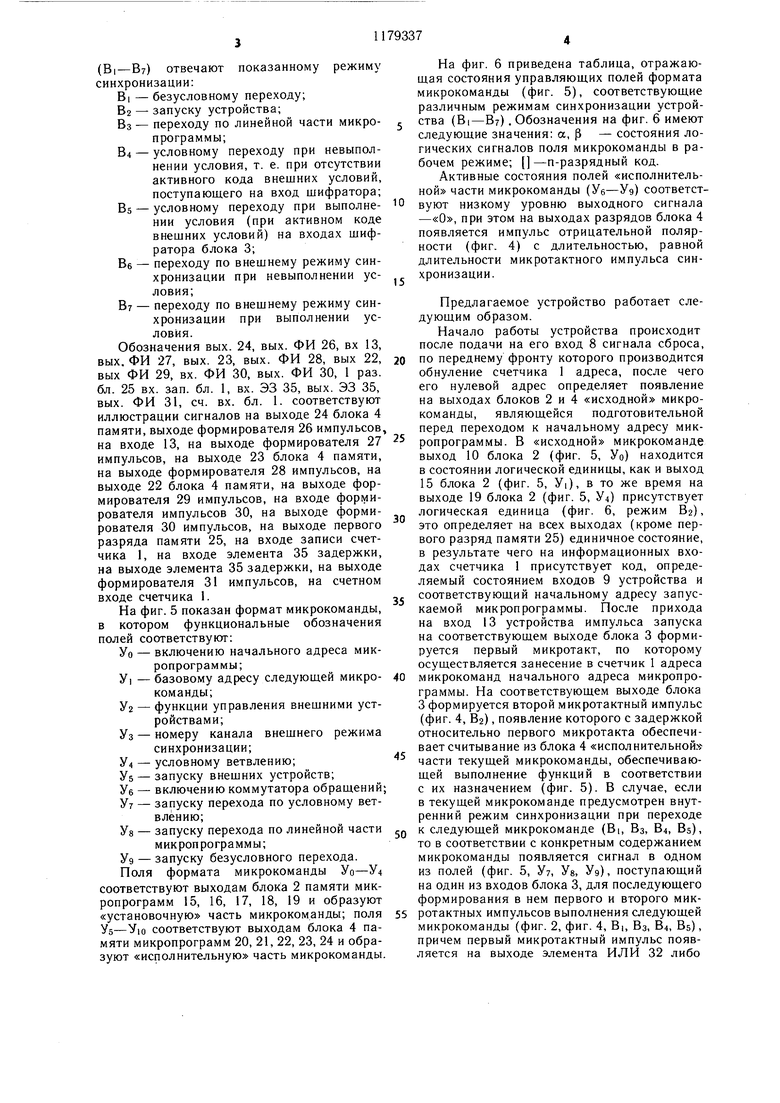

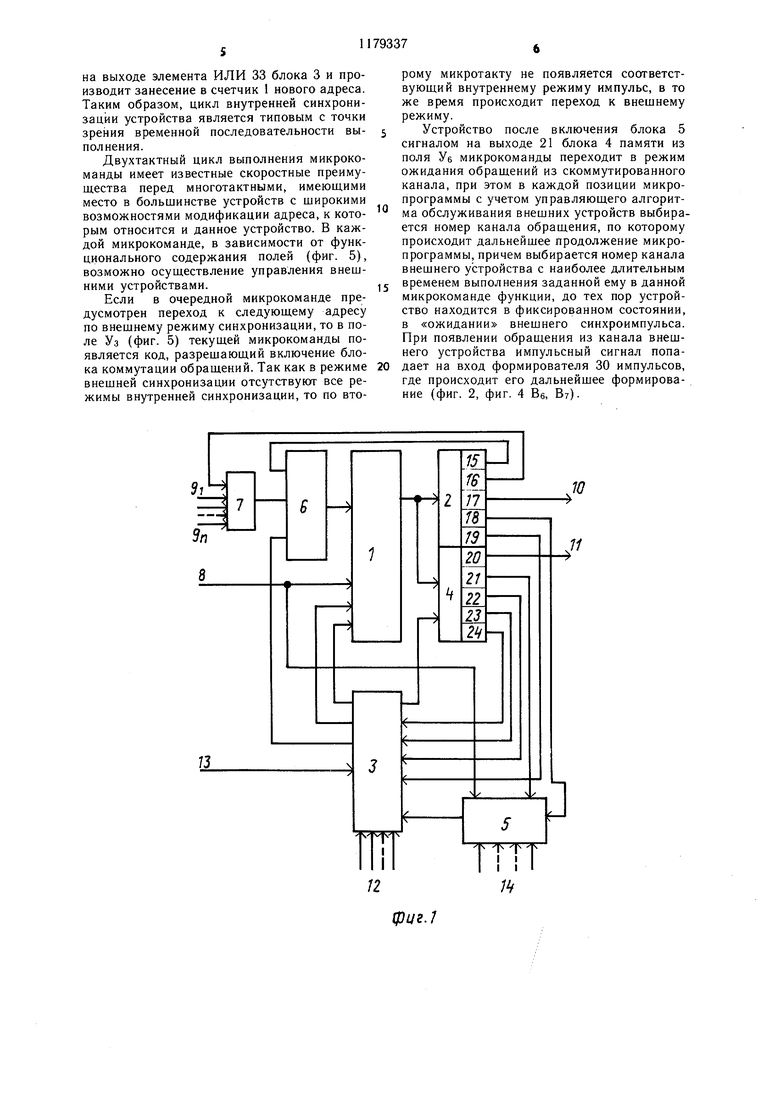

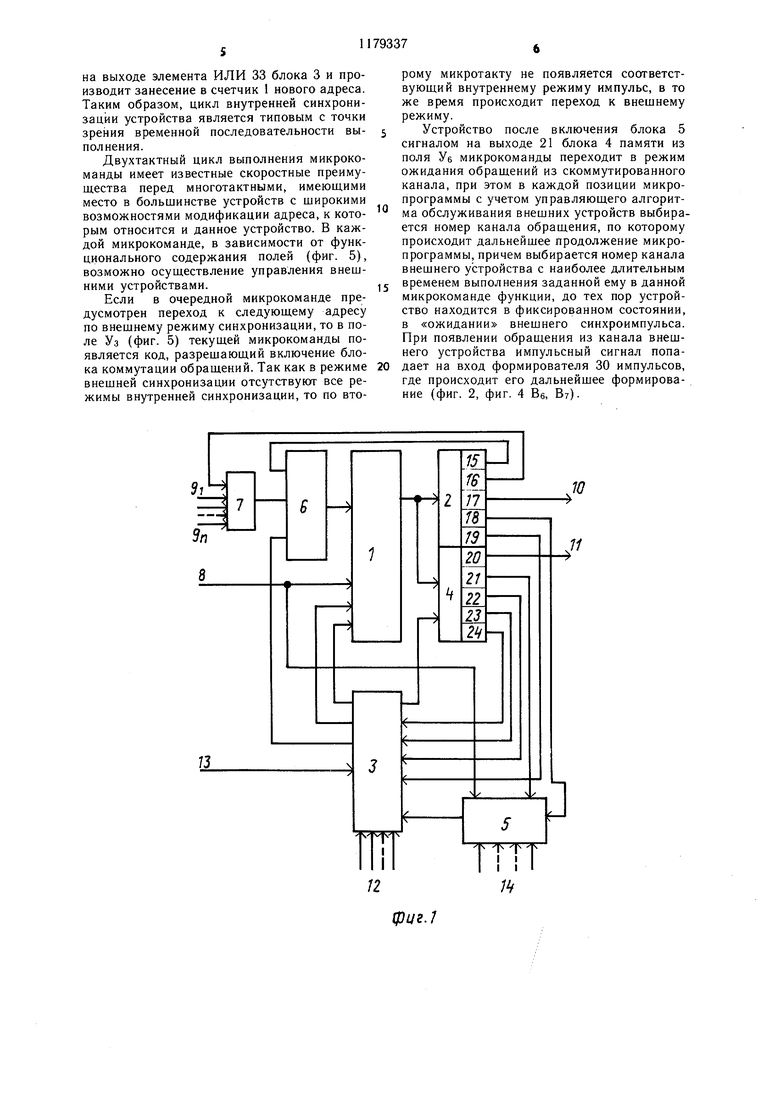

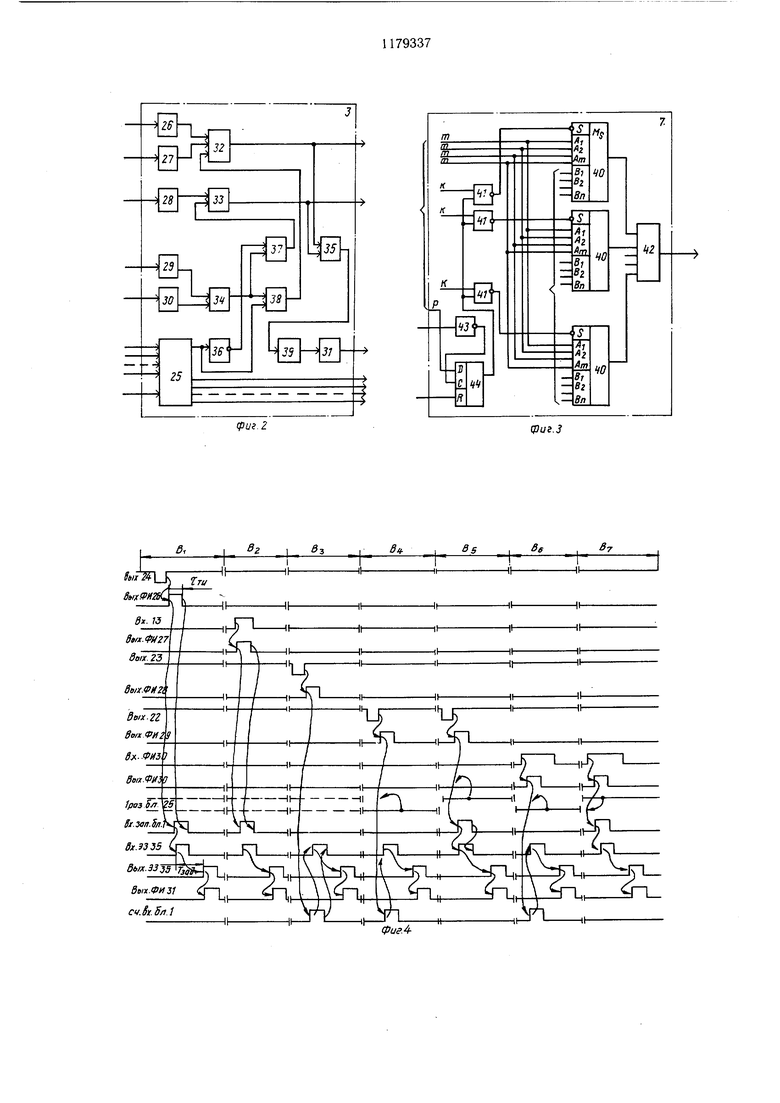

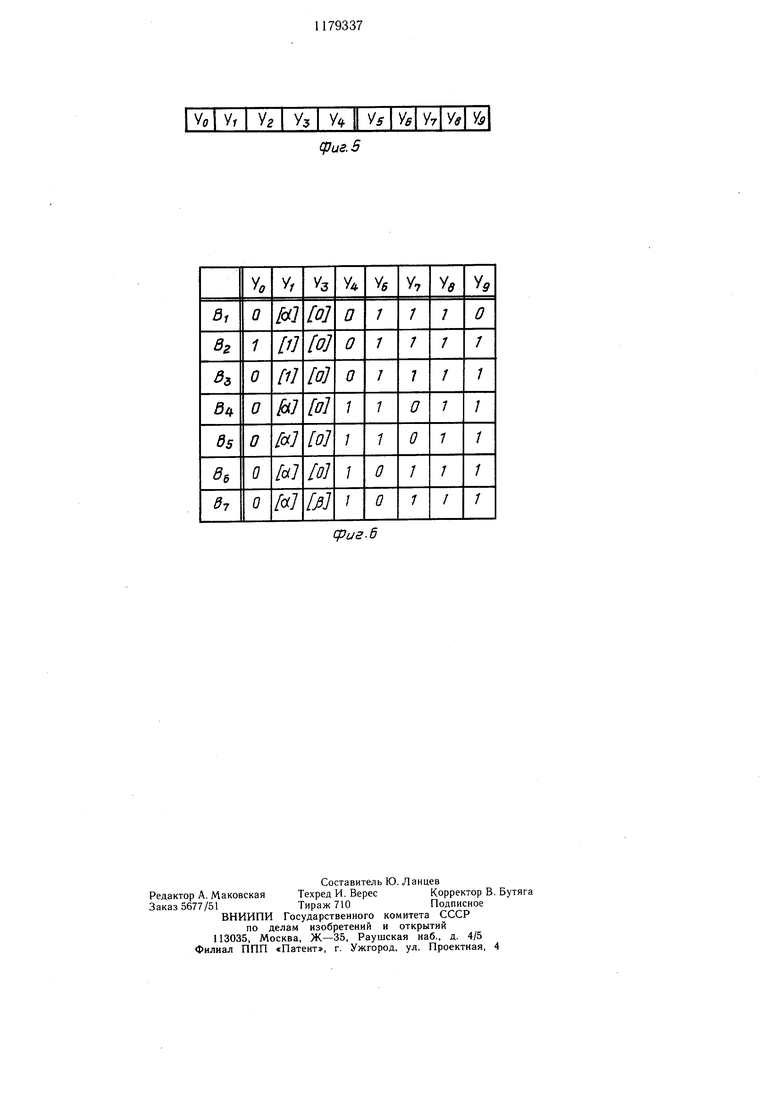

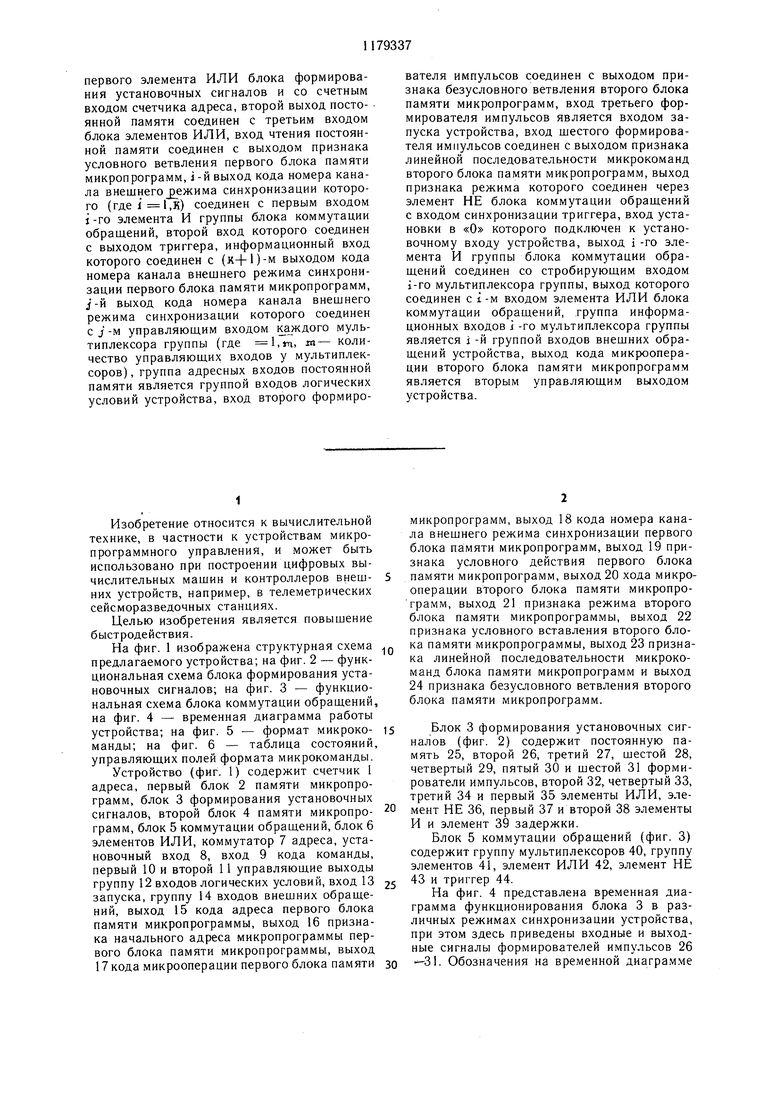

На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 - функциональная схема блока формирования установочных сигналов; на фиг. 3 - функциональная схема блока коммутации обращений, на фиг. 4 - временная диаграмма работы устройства; на фиг. 5 - формат микрокоманды; на фиг. 6 - таблица состояний, управляющих полей формата микрокоманды.

Устройство (фиг. 1) содержит счетчик 1 адреса, первый блок 2 памяти микропрограмм, блок 3 формирования установочных сигналов, второй блок 4 памяти микропрограмм, блок 5 коммутации обращений, блок 6 элементов ИЛИ, коммутатор 7 адреса, установочный вход 8, вход 9 кода команды, первый 10 и второй 11 управляющие выходы группу 12 входов логических условий, вход 13 запуска, группу 14 входов внешних обращений, выход 15 кода адреса первого блока памяти микропрограммы, выход 16 признака начального адреса микропрограммы первого блока памяти микропрограммы, выход 17 кода микрооперации первого блока памяти

микропрограмм, выход 18 кода номера канала внещнего режима синхронизации первого блока памяти микропрограмм, выход 19 признака условного действия первого блока памяти микропрограмм, выход 20 хода микрооперации второго блока памяти микропрограмм, выход 21 признака режима второго блока памяти микропрограммы, выход 22 признака условного вставления второго блока памяти микропрограммы, выход 23 признака линейной последовательности микрокоманд блока памяти микропрограмм и выход 24 признака безусловного ветвления второго блока памяти микропрограмм.

Блок 3 формирования установочных сигналов (фиг. 2) содержит постоянную память 25, второй 26, третий 27, шестой 28, четвертый 29, пятый 30 и шестой 31 формирователи импульсов, второй 32, четвертый 33, третий 34 и первый 35 элементы ИЛИ, элемент НЕ 36, первый 37 и второй 38 элементы И и элемент 39 задержки.

Блок 5 коммутации обращений (фиг. 3) содержит группу мультиплексоров 40, группу элементов 41, элемент ИЛИ 42, элемент НЕ 43 и триггер 44.

На фиг. 4 представлена временная диаграмма функционирования блока 3 в различных режимах синхронизации устройства, при этом здесь приведены входные и выходные сигналы формирователей импульсов 26 -31. Обозначения на временной диагра.мме

(B|-В) отвечают показанному режиму синхронизации:

В| - безусловному переходу;

82- запуску устройства;

83- переходу по линейной части микропрограммы;

84- условному переходу при невыполнении условия, т. е. при отсутствии активного кода внешних условий, поступающего на вход шифратора; BS - условному переходу при выполнеНИИ условия (при активном коде внешних условий) на входах шифратора блока 3;

Вб - переходу по внешнему режиму синхронизации при невыполнении условия;

В - переходу по внешнему режиму синхронизации при выполнении условия.

Обозначения вых. 24, вых. ФИ 26, вх 13, вых. ФИ 27, вых. 23, вых. ФИ 28, вых 22, вых ФИ 29, вх. ФИ 30, вых. ФИ 30, 1 раз. бл. 25 вх. зап. бл. 1, вх. ЭЗ 35, вых. ЭЗ 35, вых. ФИ 31, сч. вх. бл. 1. соответствуют иллюстрации сигналов на выходе 24 блока 4 памяти, выходе формирователя 26 импульсов на входе 13, на выходе формирователя 27 импульсов, на выходе 23 блока 4 памяти, на выходе формирователя 28 импульсов, на выходе 22 блока 4 памяти, на выходе формирователя 29 импульсов, на входе формирователя импульсов 30, на выходе формирователя 30 импульсов, на выходе первого разряда памяти 25, на входе записи счетчика 1, на входе элемента 35 задержки, на выходе элемента 35 задержки, на выходе формирователя 31 импульсов, на счетном входе счетчика 1.

На фиг. 5 показан формат микрокоманды, в котором функциональные обозначения полей соответствуют:

УО - включению начального адреса микропрограммы;У| - базовому адресу следующей микрокоманды;

У2 - функции управления внешними устройствами;УЗ - номеру канала внешнего режима

синхронизации;

У4 - условному ветвлению;

У5 - запуску внешних устройств; Уб - включению коммутатора обращений; УГ - запуску перехода по условному ветвлению;УЗ - запуску перехода по линейной части

микропрограммы;

УЭ - запуску безусловного перехода. Поля формата микрокоманды УО-У4 соответствуют выходам блока 2 памяти микропрограмм 15, 16, 17, 18, 19 и образуют «установочную часть микрокоманды; поля YS-УЮ соответствуют выходам блока 4 памяти микропрограмм 20, 21, 22, 23, 24 и образуют «исполнительную часть микрокоманды.

На фиг. 6 приведена таблица, отражающая состояния управляющих полей формата микрокоманды (фиг. 5), соответствующие различным режимам синхронизации устройства (В|-В). Обозначения на фиг. 6 имеют следующие значения: а, р - состояния логических сигналов поля микрокоманды в рабочем режиме; -п-разрядный код.

Активные состояния полей «исполнительной части микрокоманды (Уе-Уд) соответствуют низкому уровню выходного сигнала -«О, при этом на выходах разрядов блока 4 появляется импульс отрицательной полярности (фиг. 4) с длительностью, равной длительности микротактного импульса синхронизации.

Предлагаемое устройство работает следующим образом.

Начало работы устройства происходит после подачи на его вход 8 сигнала сброса, по переднему фронту которого производится обнуление счетчика 1 адреса, после чего его нулевой адрес определяет появление на выходах блоков 2 и 4 «исходной микрокоманды, являющейся подготовительной перед переходом к начальному адресу микропрограммы. В «исходной микрокоманде выход 10 блока 2 (фиг. 5, УО) находится в состоянии логической единицы, как и выход 15 блока 2 (фиг. 5, У|), в то же время на выходе 19 блока 2 (фиг. 5, У4) присутствует логическая единица (фиг. 6, режим Вг), это определяет на всех выходах (кроме первого разряд памяти 25) единичное состояние, в результате чего на информационных входах счетчика 1 присутствует код, определяемый состоянием входов 9 устройства и соответствующий начальному адресу запускаемой микропрограммы. После прихода на вход 13 устройства импульса запуска на соответствующем выходе блока 3 формируется первый микротакт, по которому осуществляется занесение в счетчик 1 адреса микрокоманд начального адреса микропрограммы. На соответствующем выходе блока 3 формируется второй микротактный импульс (фиг. 4, В2), появление которого с задержкой относительно первого микротакта обеспечивает считывание из блока 4 «исполнительной части текущей микрокоманды, обеспечивающей выполнение функций в соответствии с их назначением (фиг. 5). В случае, если в текущей микрокоманде предусмотрен внутренний режим синхронизации при переходе к следующей микрокоманде (В, Вз, В4, BS), то в соответствии с конкретным содержанием микрокоманды появляется сигнал в одном из полей (фиг. 5, У, Ув, УЭ) , поступающий на один из входов блока 3, для последующего формирования в нем первого и второго микротактных импульсов выполнения следующей микрокоманды (фиг. 2, фиг. 4, Bi, Вз, 64, ВБ) , причем первый микротактный импульс появляется на выходе элемента ИЛИ 32 либо

на выходе элемента ИЛИ 33 блока 3 и производит занесение в счетчик 1 нового адреса. Таким образом, цикл внутренней синхронизации устройства является типовым с точки зрения временной последовательности выполнения.

Двухтактный цикл выполнения микрокоманды имеет известные скоростные преимущества перед многотактными, имеющими место в больщинстве устройств с щирокими возможностями модификации адреса, к которым относится и данное устройство. В каждой микрокоманде, в зависимости от функционального содержания полей {фиг. 5), возможно осуществление управления внещними устройствами.

Если в очередной микрокоманде предусмотрен переход к следующему адресу по внешнему режиму синхронизации, то в поле УЗ (фиг. 5) текущей микрокоманды появляется код, разрешающий включение блока коммутации обращений. Так как в режиме внешней синхронизации отсутствуют все режимы внутренней синхронизации, то по второму микротакту не появляется соответствующий внутреннему режиму импульс, в то же время происходит переход к внешнему режиму.

Устройство после включения блока 5 сигналом на выходе 21 блока 4 памяти из поля Уб микрокоманды переходит в режим ожидания обращений из скоммутированного канала, при этом в каждой позиции микропрограммы с учетом управляющего алгоритма обслуживания внешних устройств выбирается номер канала обращения, по которому происходит дальнейшее продолжение микропрограммы, причем выбирается номер канала внешнего устройства с наиболее длительным временем выполнения заданной ему в данной микрокоманде функции, до тех пор устройство находится в фиксированном состоянии, в «ожидании внешнего синхроимпульса. При появлении обращения из канала внешнего устройства импульсный сигнал попадает на вход формирователя 30 импульсов, где происходит его дальнейшее формирование (фиг. 2, фиг. 4 Вб, В).

J5

,

сриг.5

ери г-6

| Микропрограммное устройство управления | 1979 |

|

SU855661A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1976 |

|

SU616629A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное устройство управления | 1980 |

|

SU881748A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-15—Публикация

1983-07-07—Подача