готовности записи блока формирование режимов, и с первым входом (п+2)-го элемента И, выход квитанции считьтания .блока формирования режимов соединен с управляющими входами первых п элементов И и с выходом готовности считывания устройства, информационный рход устройства соединен с информационным входом сдвигающего регистра, выходы разрядов с 1 по п которого соединены с информационными входами первых п элементов памяти, входы записи и считьшания п первых элементов памяти соединены соответственно с выходами записи информации и считывания информации блока формирования режимов, выход квитанции записи которого соединен с вторым входом (п+2)-го элемента И, с информационным входом (n+l) элемента памяти и с вторым входом (п+1) элемента И, третий вход которого соединен с выходом опроса памяти блока формирования режимов и с входом считывания (n+l) элемента памяти, выход разрешения тактов блока формирования режимов соединен с счетным входом адресного счетчика и с третьим инверсным входом (п+2)-го элемента И, выход которого соединен с вторым входом сброса делителя частоты и с тактовьм входом сдвигающе.го регистра, четвертый вход (п+2)-го элемента И соединен с тактовым входом устройства, выход объема памяти которого соединен с выходом первого триггера, а адресные входы всех элементов памяти соединены с выходами адресного счетчика, второй выход первого дешиф-ратора соединен с входом переполнения памяти блока формирования режимов, выход которого Запись признака занято соединен с входом записи (n+l)-го элемента памяти, информационный выход которого соединен с S входом второго триггера, выход (п+1)-го элемента И соединен с S входом первого триггера, причем блок формирования режимов содержит триггер записи, триггер считывания, триггер стирания, шесть D-триггеров, 5 элементов ИЛИ, 8 элементов И, элемент ЗИ-ИЛИ, элемент НЕ, причем вход режима записи блока формирования режимов соединен с S входом триггера записи, выход которого соединен с D входом первого D-триггера, вход режима считьшания блока формирования режимов соединен с первым входом первого элемента И,

выход которого соединен с S входом триггера считывания, вход сброса режима записи блока формирования режимов соединен с первым R-входом триггера записи, второй R-вход которого qoeдинeн с вьпсодом первого элемента ИЛИ, с первыми входами второго и третьего элементов ИЛИ, с R-входом четвертого D-триггера, с Н-входом триггера стирания и с первым Б-входом триггера считьгоания, вход режима стирания блока соединен с S-входом триггера стирания, выход которого соединен с D-входом второго D-триггера выход первого D-триггера соединен с выходом квитанции записи бгока, с первым входом первого элемента И элемента ЗИ-ИЛИ, с первыми входами второго II третьего элементов И, с первым входом четвертого элемента ИЖ, с вторым R-входом триггера считьюания, выход которого соединен с D-входом третьего D-триггера, тактовые входы первого, второго и третьего D-триггеров объединены и соединены с входом начала режима блока формирования, вход установки исходного состояния которого соединен с R-BXOдами первого, второго, третьего D-триггеров и первым входом первого элемента ИЛИ, инверсный выход первого D-триггера соединен со вторым входом первого элемента И и с первым входом второго элемента И элемента ЗИ-ИЛИ, второй вход второго элемента И которого соединен с первым входом четвертого элемента И и с инверсным выходом второго D-триггера, выход второго D-триггера соединен с первым входом третьего элемента И, элемента ЗИ-ИЛИ и с первым входом пятого элемента ШШ, второй вход которого соединен со вторым входом четвертого элемента И и с выходом четвертого элемента ИЛИ, второй вход четвертого элемента ИЛИ соединен с первыми входами пятого и шестого элементов И, со вторым входом первого элемента И элемента ЗИ-ИЛИ и с выходом

.третьего D-триггера, инверсный выход которого соединен с третьим входом второго элемента И элемента ЗИ-ИЛИ, выход элемента ЗИ-ИЛИ соединен с: первым выходом сброса блока формирования режимов и с R-входом пятого D-триггера, D-вход которого соединен с входом переполнения памяти блока формирования режимов, вход синхронизации записи блока формирования режимов соединен с третьим входом второго элемента И, с первым входом седьмого элемента И и с тактовым входом пятого D-триггера, выход которого соединен со вторым входом первого элемента ИЛИ вход состояние памяти блока формирования режимов соединен с третьим входом третьего элемента И, со вторым входом второго элемента И и через элемент НЕ со вторыми входами пятого и шестого элементов И, третий вход пятого элемента И соединен с входом строба тактов информации блока формирования режимов, вход анализа состояния служебного разряда блока формирования режимов соединен с третьим входом четвертого элемента И, выход которого соединен с выходом опроса памяти блока формирования режимов, вход синхронизации информации блока формирования режимов соединен со вторым входом третьего элемента И и с третьим входом шестого элемента И, выход которого соединен с выходом квитанции считывания блока формирования режима, вход готовности записи блока формирования режимов соединен с третьим входом седьмого элемента И и с четвертым входом второго элемента И, выход кото рого соединен с выходом записи инфор мации и со вторым входом второго элемента ИЛИ, выход второго элемента ИЛИ подключен к входу R шестого D-триггера , входы С и D которого объединены и соединены со входами С и D четвертого D-триггера, с выходом третьего элемента И, со вторым входом третьего элемента ИЛИ и с первым входом восьмого элемента И, выход которого соединен со вторым входом третьего элемента И элемента ЗИ-ШШ и с выходом запроса тактов блока формирования режимов, выход пятого элемента ИЛИ соединен со вторым входом седьмого элемента И, выход которого соединен с выходом Запись признака занято блока формирования режимов, инверсный выход четвертого D-триггера соединен со вторым входом восьмого элемента И, выход третьего элемента ИЛИ соединен с вторым выходом сброса блока формирования режимов, выход разрешения тактов которого соединен с четвертым входом третьего элемента И и с инверсньм выходом шестого D-триггера, выход пятого элемента И соединен с выходом считывания информации блока формирования режимов,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вывода графической информации | 1986 |

|

SU1403092A1 |

| Устройство для поиска информации в памяти | 1985 |

|

SU1352494A1 |

| Устройство для отображения графической информации на телевизионном индикаторе | 1986 |

|

SU1374272A1 |

| Устройство для отображения графической информации | 1990 |

|

SU1772822A1 |

| Сигнатурный анализатор | 1983 |

|

SU1140123A1 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705873A1 |

| Вычислительное устройство с совмещением операций | 1989 |

|

SU1716528A1 |

| Устройство для отладки программ | 1987 |

|

SU1462327A1 |

| Запоминающее устройство | 1987 |

|

SU1495849A1 |

| Устройство для вычисления скользящего спектра | 1983 |

|

SU1095188A1 |

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ, содержащее- первый дешифратор, адресный счетчик, первый триггер, (n+l) элементов памяти, (п+2) элементов И, причем выходы адресного счетчика соединены с входами первого дешифратора, а информационные выходы первых п элементов памяти соединены с информационными входами первых п элементов И, выходы которых являются информационными выходами устройства, первый выход первого дешифратора соединен с первым входом (п+1) элемента И, отличающееся тем, что, с целью расширения области применения, в устройство введены делитель частоты, второй дешифратор, второй и третий триггеры, сдвигающий регистр и блок формирования режимов, причем первый, второй и третий командные входы устройства соединены соответственно с входами режимов записи, считьшания и стирания блока формирования режимов, а входы конца записи и начала работы устройства соединены соответственно с входами сброса режима записи и установки в исходное состояние блока формирования режимов, третий командный вход устройства соединен с первым Й-входомпервого триггера, а вход начала работы устройства соединен с вторым R-входом первого триггера и первым входом сброса делителя частоты, тактовый вход которого соединен с синхровходом устройства, выход готовности считьтания которого соединен с выходом запроса тактов блока формирования режимов, а входы анализа состояния служебного разряда, синхронизации информации, синхронизации записи, начало режима блока формирования режимов соединены соответственно с первым, вторым, третьим и четвертым, выходами второго дешифратора, информационные входы (А С которого сбединены с информационными выходами делителя частоты, а пятый и шестой выходы второго дешиф.ратора соединены соответственно с S-входом второго триггера и К-входом третьего триггера, инверсный выход которого соединен с входом сос тояния памяти блока формирования реОд 00 00 SI жимов, а прямой пыход третьего триггера соединен с входом строба тактов информации блока формирования режимов, четвертый и третий выходы второго дешифратора соединены соответственно с тактовым входом адресного счетчика и R-входом третьего триггера, первый выход сброса блока формирсва ния режимов соединен с выходом наличия режима устройства и с входом сброса адресного счетчика, второй выход сброса блока формирования режимов соединен с установочными входами сдвигающего регис -ра, прямой, и инверсный (п+1) выходы сдв щего регисч- ра соединены соответственно с входом

Изобретение относится к автоматике и вычислительной технике и может найти применение в автоматизированных системах управления в качестве буферного устройства памяти.

Целью изобретения является расширение области применения устройства.

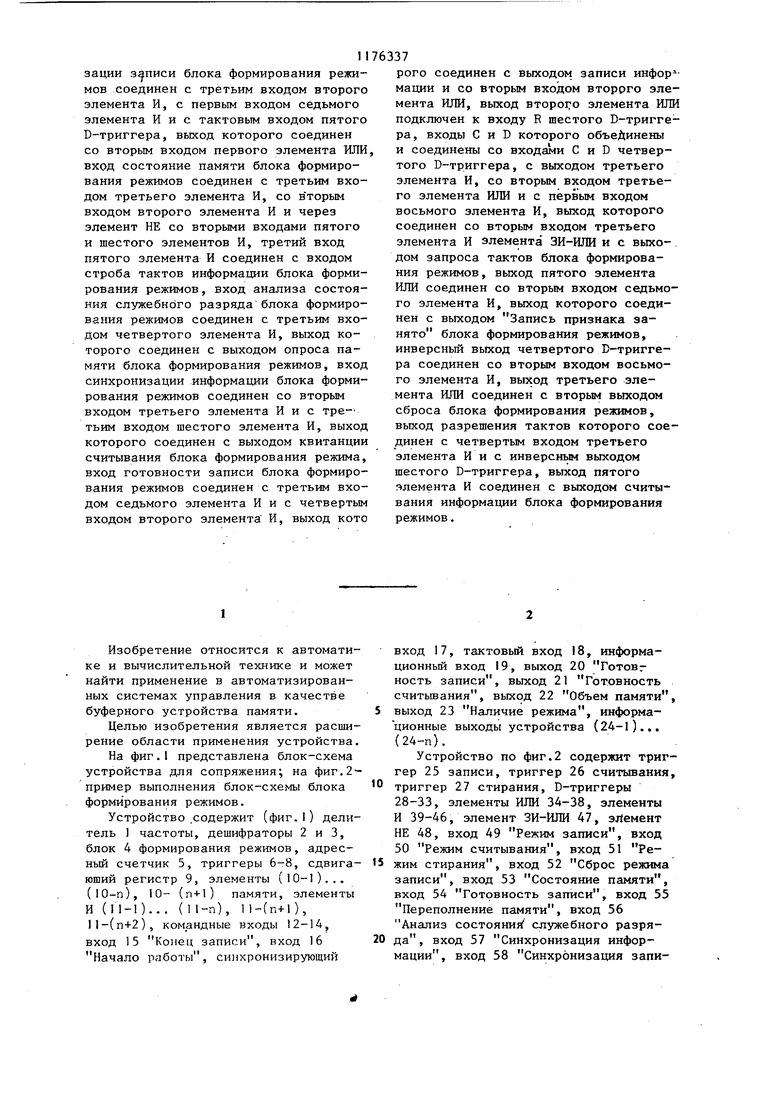

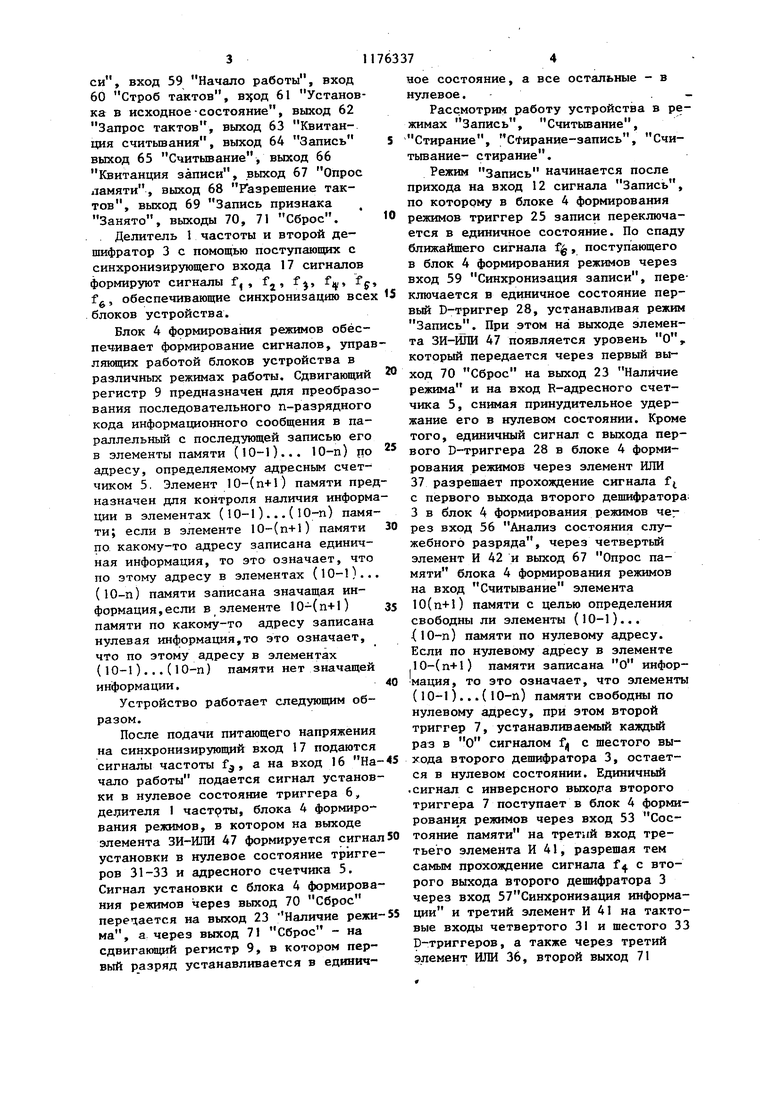

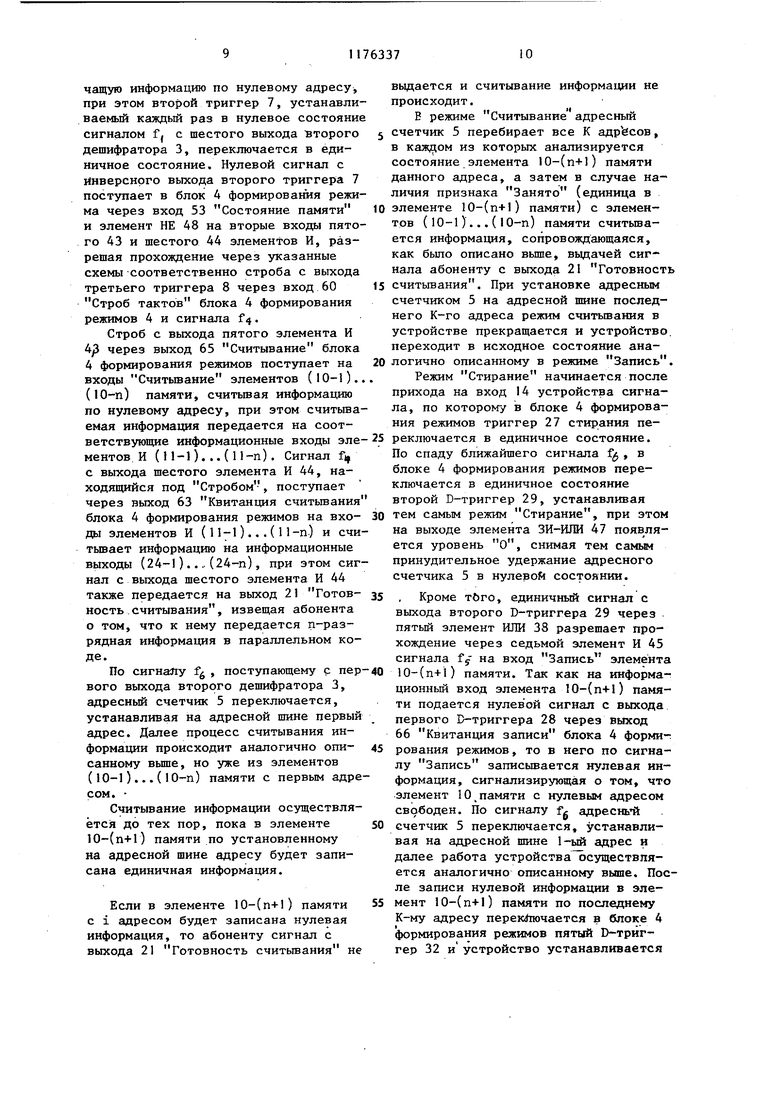

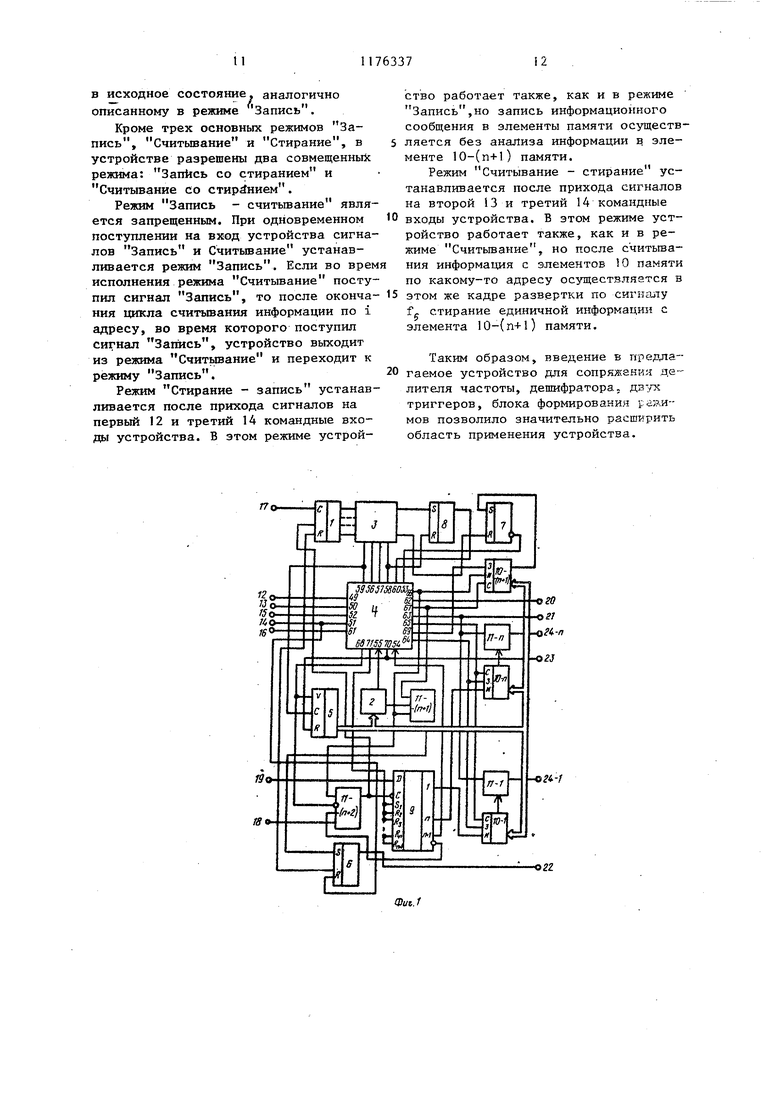

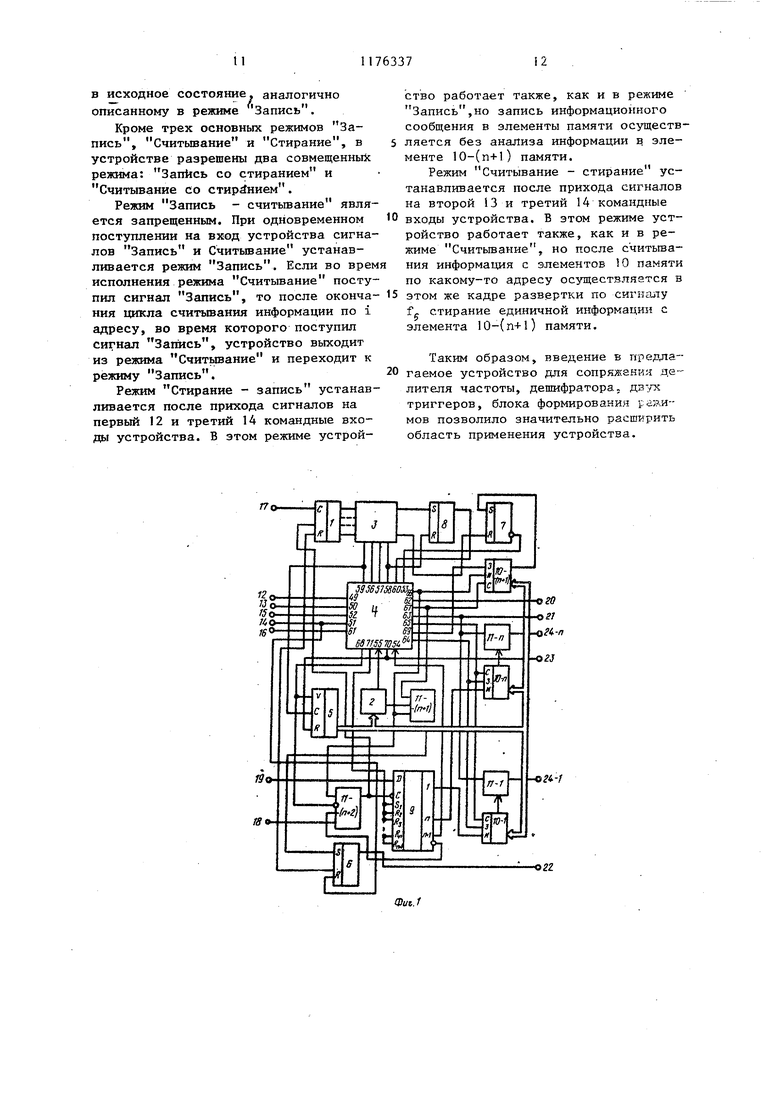

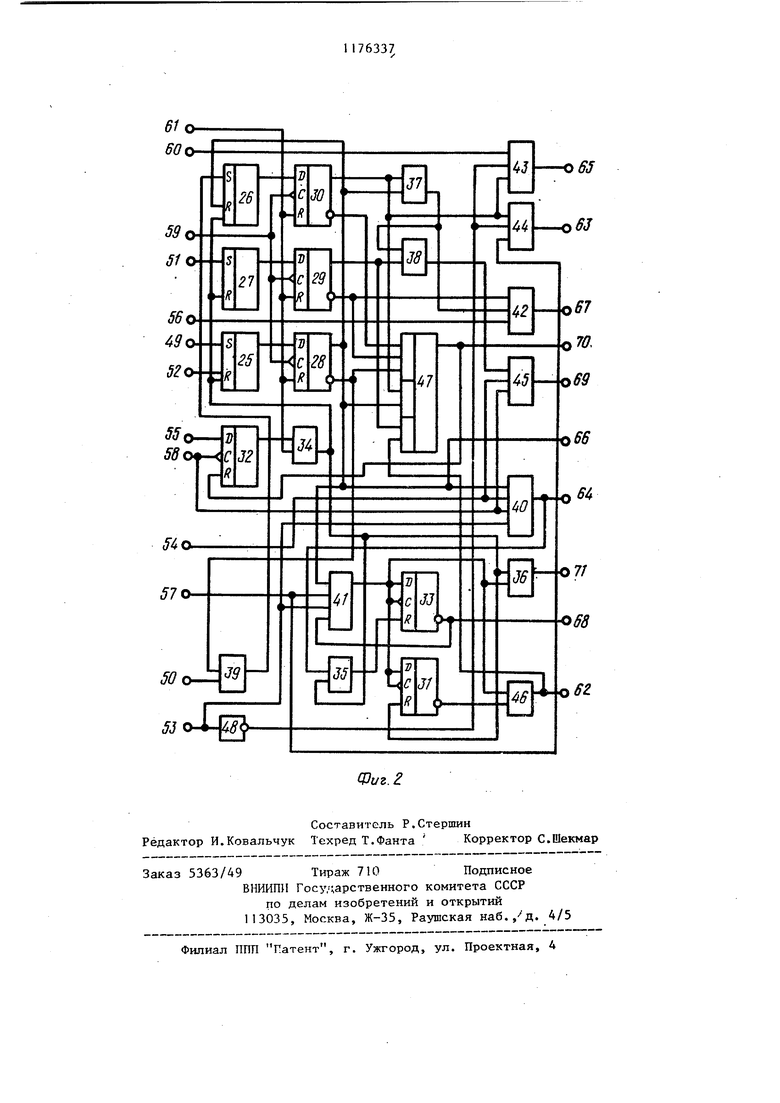

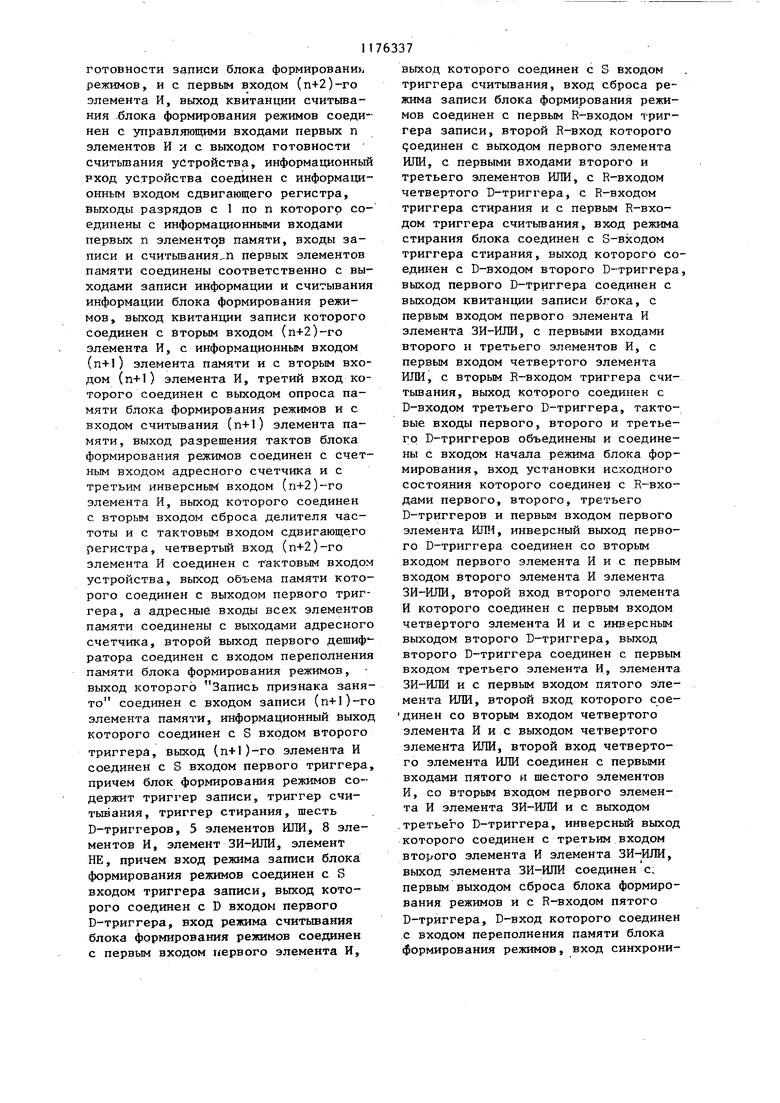

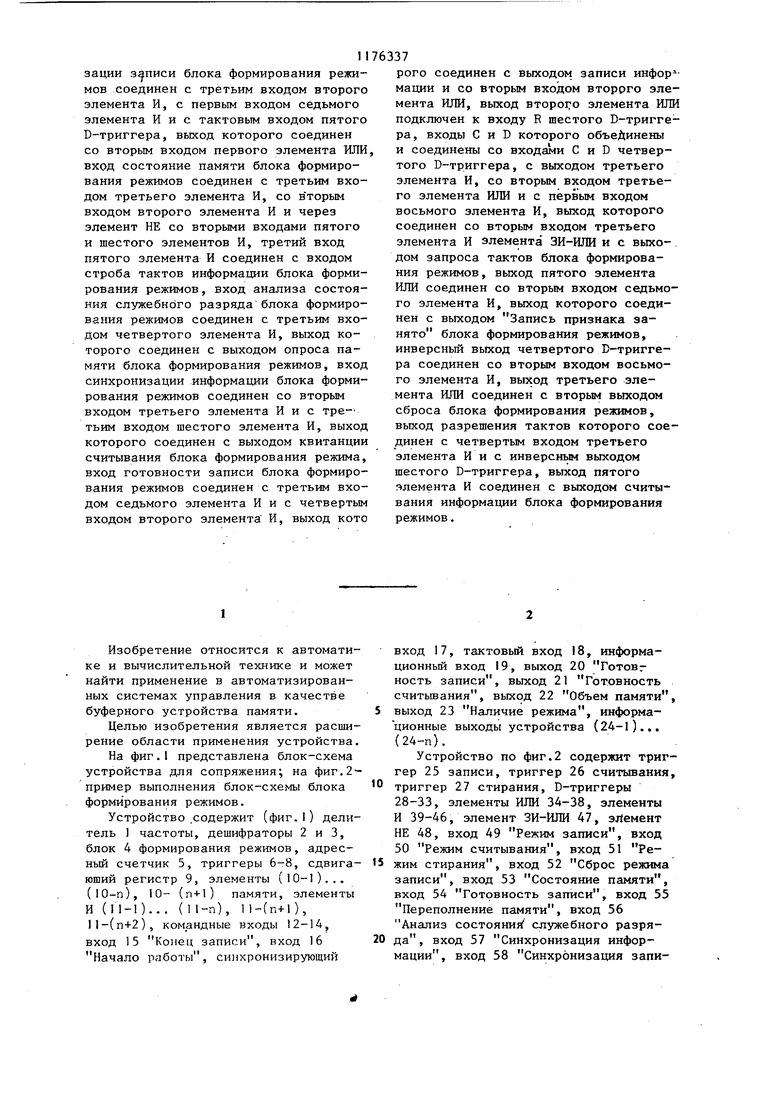

На фиг.1 представлена блок-схема устройства для сопряжения; на фиг.2пример выполнения блок-схемы блока формирования режимов.

Устройство .содержит (фиг.1) делитель 1 частоты, дешифраторы 2 и 3, блок 4 формирования режимов, адресный счетчик 5, триггеры 6-8, сдвигаюший регистр 9, элементы (lO-l)... (lO-n), 10- (n+l) памяти, элементы И (11-1)... (11-п), 11-(п+1), 11-(п+2), ком андные входы 12-14, вход 15 Конец записи, вход 16 Начало работы, си)хронизирующий

вход 17, тактовый вход I8, информационный вход 19, выход 20 Готовг ность записи, выход 21 Готовность считьшания, выход 22 Объем памяти,

выход 23 Наличие режима, информационные выходы устройства (24-1)... (24-п).

Устройство по фиг.2 содержит триггер 25 записи, триггер 26 считывания,

триггер 27 стирания, D-триггеры

28-33, элементы ИЛИ 34-38, элементы И 39-46, элемент ЗИ-ИЛИ 47, элемент НЕ 48, вход 49 Режим записи, вход 50 Режим считывания, вход 51 Ре-

жим стирания, вход 52 Сброс режима записи, вход 53 Состояние памяти, вход 54 Готовность записи, вход 55 Переполнение памяти, вход 56 Анализ состояний служебного разряда, вход 57 Синхронизация информации, вход 58 Синхронизация записи, вход 59 Начало работы, вход 60 Строб тактов, вз5од 61 Установка в исходное-состояние, выход 62 Запрос тактов, выход 63 Квитанция считьтания, выход 64 Запись выход 65 Считывание, выход 66 Квитанция записи, выход 67 Опрос памяти, выход 68 Газреюение тактов, выход 69 Запись признака Занято, выходы 70, 71 Сброс. Делитель 1 частоты и второй дешифратор 3 с помощью поступающих с синхронизирующего входа 17 сигналов формируют сигналы f, V Р fg, обеспечивающие синхронизацию всех .блоков устройства. Блок 4 формирования режимов обеспечивает формирование сигналов, управ ляющих работой блоков устройства в различных режимах работы. Сдвигающий регистр 9 предназначен для преобразо вания последовательного п-разрядного кода информационного сообщения в параллельный с последующей записью его в элементы памяти (10-1)... 10-п) jio адресу, определяемому адресным счетчиком 5, Элемент lO-(n-fl) памяти пред назначен дпя контроля наличия информа ции в элементах (10-1)...(10-п) памя ти; если в элементе 10-(п-ь1) памяти по какому-то адресу записана единичная информация, то это означает, что по этому адресу в элементах (10-1).. (10-п) памяти записана значащая информация, если в элементе 10-(п-ь1) памяти по какому-то адресу записана нулевая информация,то это означает, что по этому адресу в элементах (10-1)...(10-п) памяти нет значащей информации. Устройство работает следующим образом. После подачи питающего напряжения на синхронизирующий вход 17 подаются сигналы частоты f , а на вход 16 На чало работы подается сигнал установ ки в нулевое состояние триггера 6, делзмтеля I частрты, блока 4 формирования режимов, в котором на выходе элемента ЗИ-ИЛИ 47 формируется сигна установки в нулевое состояние тригге ров 31-33 и адресного счетчшса 5. Сигнал установки с блока 4 формирова ния режимов через выход 70 Сброс пере- ается на выход 23 Наличие режи ма, а через выход 71 Сброс - на сдвигакмций регистр 9, в котором первый разряд устанавливается в единичное состояние, а все остальные - в нулевое.. Рассмотрим работу устройства в режимах Запись, Считывание, Стирание, Сдирание-запись, Считьгоание- стираиие. Режим Запись начинается после прихода на вход 12 сигнала Запись, по которому в блоке 4 формирования режимов триггер 25 записи переключается в единичное состояние. По спаду ближайшего сигнала f , поступающего в блок 4 формирования режимов через вход 59 Синхронизация записи, переключается в единичное состояние первый D-триггер 28, устанавливая режим Запись. При этом на выходе элемента ЗИ-ЙЛИ 47 появляется уровень О,, который передается через первый выход 70 Сброс на выход 23 Наличие режима и на вход R-адресного счетчика 5, снимая принудительное удержание его в нулевом состоянии. Кроме того, единичный сигнал с выхода первого D-триггера 28 в блоке 4 формирования режимов через элемент ИЛИ 37 разрешает прохождение сигнала f с первого выхода второго дешифратора 3 в блок 4 формирования режимов четрез вход 56 Анализ состояния служебного разряда, через четвертый элемент И 42 и выход 67 Опрос памяти блока 4 формирования режимов на вход Считывание элемента lO(n-t-l) памяти с целью определения свободны ли элементы (10-1)... ОО-п) памяти по нулевому адресу. Если по нулевому адресу в элементе .lO-(n-bl) памяти записана О информация, то это означает, что элементы (10-1)...(10-п) памяти свободны по нулевому адресу, при этом второй триггер 7, устанавливаемый каждьй раз в о сигналом f с шестого выхода второго дешифратора 3, остается в нулевом состоянии. Единичный сигнал с инверсного выхода второго триггера 7 поступает в блок 4 формировани я режимов через вход 53 Состояние памяти на третий вход третьего элемента И 41, разрешая тем самым прохождение сигнала f с второго выхода второго дешифратора 3 через вход 57 Синхронизация информации и третий элемент И 41 на тактовые входы четвертого 31 и шестого 33 р-триггеров, а также через третий элемент ИЛИ 36, второй выход 71

Сброс на установку исходного состояния сдвигающего регистра 9. Кроме того, сигнал с выхода третьего элемента И 41 Запрос ТИ поступает через восьмой элемент И 46 и выход 62 Запрос тактов блока 4 формирования режимов на выход 20 Готовность записи для запроса информационного сообщения. По спаду выходного сигнала третьего элемента И 41 четвертый 31 и шестой 33 D-триггеры устанавливаются в единичные состояния, при этом Четвертый D-триггер 31 запрещает передачу на выход 62 Запрос тактов выходного сигнала третьего элемента И 41, а нулевой сигнал с инверсного выхода шестого D-триггера 33 запрещает по входу 57 Синхронизация информации прохождение через третий элемент И 41 сигнала f , а также через выход 68 Разрешение тактов блока 4 формирования режимов запрещает по входу V переключение адресного счетчика 5 к новому адресу. Кроме того, этот же сигнал разрешает прохождение тактовых импульсов с тактового входа 18 через элемент И 11-(п+2) на тактовый вход сдвигающего регистра 9 и на второй R вход делителя 1 частоты. Так как в исходном состоянии в первом разряде сдвигающего регистра 9 записана I, а в остальных - О, в том числе и в (n+l)-OM разряде, то нулевой сигнал с (п+1)-го разряда через вход 54 Готовность записи в блоке 4 формирования режимов запрещает формирование с.игналов Запись элементами И вторым 40 и седьмым 45, а сигнал 1 с инверсного выхода (n+l) разряда разрешает по третьему входу прохождение тактов через элемент 11-(п+2) на тактовый вход сдвигающего регистра 9 для записи в нег информационного сообщения с информационного входа 19. После записи в сдвигающий регистр 9 п символов сообщения на инверсном выходе (n+l)разряда сдвигающего регистра 9 появляется сигнал о, запрещающий прохождение тактов в регистр, а появившийся по спаду п-го такта едининый сигнал на выходе (п+1) разряда сдвигающего регистра 9 в блоке 4 формирования режимов разрешает прохождение сигнала Г.-через второй элемент И 40 в элементы (10-1)...

(10-п) памяти для записи информации с первых п разрядов сдвигающего регистра 9, а также разрешает фод мирование седьмым элементом И 45 сигнала, который через выход 69 Запись признака Занято записьшает единичную информацию с выхода лервого D-триггера 28 в элемент 10-(п+1)памяти, фиксируя тем самым, что в элементы (10-1)...(10-ц) памяти с нулевым адресом записано информационное сообщение. Одновременно с записью информационного сообщения в элементы (10-1)...(0-п) памяти по сигналу Запись в блоке 4 формирования режимов через второй элемент ИЛИ 35 шестой D-триггер 33 по входу R переключается в нулевое состояние,

разрешая тем самым цо входу V работу адресного счетчика 5 и прохождение через третий элемент И 41 сигнала Гц в следующем такте работы устройства.

По сигналу fg с четвертого выхода второго дешифратора 3 адресный счетчик 5 переключается, устанавливая на адресной шине код для выбора в элементах 10 памяти ячеек с первым ад ресом. На этом заканчивается такт работы устройства.

В следующих тактах работа устройства проходит аналогично описанному. По сигналу f, с шестого выхода дешифратора 3 убтанавливается в нулевое состояние второй триггер 7; по сигналу fy осуществляется опрос элемента 10-(п+1) памяти с запоминанием результата опроса вторым триггером 7; при наличии нулевой информации в элементе 10-(n+l) памяти, а следовательно и во втором триггере 7, по сигналу f4 осуществляется установка в исходное состояние сдвигающего регист- ра 9 и шестым D-триггером 33 блоки- руется по входу V работа адресного счетчика 5, а также разрешается прием информационного сообщения в сдвигаю-щий регистр 9; после приема п разрядов информационного сообщения осуществляется синхронизация последним тактом делителя 1 частоты и разрешается формирование сигнала Запись ; по сигналу формируется сигнал

5 Запись и осуществляется запись информационного обобщения со сдвигающего регистра 9 в элементы (10-1)...(10-п) памяти, а также запись единичной информации с выхода первого D триггера 28 в элемент 10-(п4-1) памяти, кроме того, по сигналу Запись разрешается шестым D-триггером 33 по входу V работа адресиого счетчика 5; по сигналу f осуществляется переключение адресног счетчика 5 на новый адрес и т.д. Есл при нулевом адресе в элементе lO-Cn+ памяти будет записана 1 (элементы 10 памяти с нулевым адресом заняты), -то по сигналу fg второй триггер 7 переключится в 1, запретит блоку 4 формирования режимов формирование сигналов Запись и Запрос ТИ, а по сигналу fg адресный счетчик 5 переключится на первый адрес, т.,е. формирование сигналов Запрос и Запись будет разрешено только посл нахождения свободных элементов 10 памяти.

Режим Запись заканчивается посл поступления в блок 4 формирования режимов через вход 15 устройства Коне записи и его вход 52 Сброс режима записи от абонента сигнала Конец записи. В блоке 4 формирования режимов по этому сигналу триггер 25 записи переключается в О, разрешая по ближайшему сигналу fg переключ ние первого D-триггера 28 в нулевое состояние, при этом устройство, как показано Bbmie, переходит в исходное состояние.При большом Объеме записьгааемой от абонента информации в устройстве после установки на адресной шине ко- да, соответствующего (К-Р) адресу, (где К - обшее количество адресов, Р - количество свободных п-разрядных элементов памяти), на первом выходе первого дешифратора 2 появляется сигнал, разрешающий прохождение в режиме Запись через элемент И 11-(п+1) на З-рход первого триггера 6 сигнала f . Первый триггер 6 переключается в единично состояние, а его выходной сигнал передается через выход 22 Объем памяти на выхсд и сигнализирует абоненту о том, что в устройстве осталось место только для записи Р слов.

При дальнейшем поступлении информации, на запись после записи информационного п-разрядного сообщения по К-му адресу в элементы 10 пдмяти на втором выходе первого дешифратора 2 появляется единичный сигнал, поступающий в блок 4 формирования режимов на вход пятого D-триггера 32 через вход 55 Переполнение памяти. По спаду сигнала f пятый D триггер 32 переключается в единичное состояние, а его выходной сигнал через первый элемент ИЛИ 34-устанавливает«в исходное состояние четвертый D-триггер 31, шестой D-триггер 33, сдвигающий регистр 9 и триггер 25, разрешающий установку в нулевое состояние по спаду сигнала f первому триггеру 28, после чего устройство переходит в исходное состояние, как описано выше. При этом, на выходе 23 Наличие режима формируется единичный сигнал, сигнализирующий о том, что устройство закончило работу.

Режим Считывание начинается после прихода на вход 13 устройства сигнала Считьгоание, по которому в блоке 4 формирования режимов через первый элемент И 39 при отсутствии на его втором входе запрещающего сигнала от первого D-триггера 28 триггер 26 считывания переключается в единичное состояние. По спаду ближайшего сигнала fg, поступающего в блок 4 формирования режимов через вход 59 Начало режима, переключается в единичное состояние третий D-триггер 30, устанавливая в устройстве режим Считьюание; при этом на выходе элемента ЗИ-ШШ 47 появляет-г ся уровень о, который передается через первый выход 70 Сброс на выход 23 Наличие режима, а также на вход R адресного счетчика 5, снимая тем самым принудительное удержание адресного счетчика в нулевом состоянии. Кроме того, сигнал с выхода третьего D-триггера 30 -в блоке 4 формирования режимов через четвертый элемент ИЛИ 37 разрешает прохождение сигнала f, с первого выхода второго дешифратора 3 через четвертый элемен И 42 и выход 67 0пpoc памяти блока 4 формирования режимов на вход Считывание элемента 10-(п+1) памяти с целью определения наличия значащей информации в элементах (10-1)... (10-п) памяти нулевого адреса. Если в элементе 10-(n+l) памяти записана 1, то это означает, что элементы (10-1)...(10-п) памяти содержат дначащуго информацию по нулевому адресу, при этом второй триггер 7, устанавли ваемый каждый раз в нулевое состояни сигналом fJ с шестого выхода второго дешифратора 3, переключается в единичное состояние. Нулевой сигнал с инверсного выхода второго триггера 7 поступает в блок 4 формирования режи ма через вход 53 Состояние памяти и элемент НЕ 48 на вторые входы пято го 43 и шестого 44 элементов И, разрешая прохождение через указанные схемы соответственно строба с выхода третьего триггера 8 через вход 60 Строб тактов блока 4 формирования режимов 4 и сигнала f4. Строб с выхода пятого элемента И 4р через выход 65 Считывание блока 4 формирования режимов поступает на входы Считьтание элементов (lO-l). (lO-n) памяти, считьшая информацию по нулевому адресу, при этом считьша емая информация передается на соответствующие информационные входы эле ментов. И (11-1)...(11-п). Сигнал f с выхода шестого элемента И 44, находящийся под Стробом, поступает через выход 63 Квитанция считывания блока 4 формирования режимов на входы элементов И (11-1).,.(11-п) и счи тьшает информацию на информационные выходы (24-1)..,. (24-п), при этом сиг нал с выхода шестого элемента И 44 также передается на выход 21 Готовность считывания, извещая абонента о том, что к нему передается п-разрядная информация в параллельном коде. По сигналу f , поступающему с пер вого выхода второго дешифратора 3, адресный счетчик 5 переключается, устанавливая на адресной шине первый адрес. Далее процесс считывания информации происходит аналогично описанному выше, но уже из элементов (10-1)...(10-п) памяти с первым адре сом. Считывание информации осуществляется до тех пор, пока в элементе 10-(n+l) памяти по установленному на адресной шине адресу будет записана единичная информация. Если в элементе 10-(п+1) памяти с i адресом будет записана нулевая информация, то абоненту сигнал с выхода 21 Готовность считьшания не выдается и считывание информации не происходит. В режиме Считывание адресный счетчик 5 перебирает все К адресов, в каждом из которых анализируется состояние элемента 10-(n+l) памяти данного адреса, а затем в случае наличия признака Занято (единица в элементе 10-(п+1) памяти) с элементов (10-1)...(I0-п) памяти считьшается информация, сопровождающаяся, как было описано выше, выдачей сигнала абоненту с выхода 21 Готовность считывания. При установке адресным счетчиком 5 на адресной шине последнего К-го адреса режим считьтання в устройстве прекращается и устройство, переходит в исходное состояние аналогично описанному в режиме Запись. Режим Стирание начинается после прихода на вход 14 устройства сигнала, по которому в блоке 4 формирования режимов триггер 27 стирания переключается в единичное состояние. По спаду ближайшего сигнала f, в блоке 4 формирования режимов переключается в единичное состояние второй D-триггер 29, устанавливая тем самым режим Стирание, при этом на выходе элемента ЗИ-ИЛИ 47 появляется уровень о, снимая тем самьм принудительное удержание адресного счетчика 5 в нулевой состоянии. Кроме тбго, единичный сигнал с выхода второго D-триггера 29 через пятый элемент ИЛИ 38 разрешает прохождение через седьмой элемент И 45 сигнала fy на вход Запись элемента 10-(п+1) памяти. Так как на информационный вход элемента 10-(п4-1) памяти подается нулевой сигнал с выхода первого D-триггера 28 через выход 66 Квитанция записи блока 4 формит рования режимов, то в него по сигналу Запись записывается нулевая информация, сигнализирующая о том, что элемент 10 памяти с нулевым адресом свободен. По сигналу f, адресньтй счетчик 5 переключается, устанавливая на адресной шине 1-ый адрес и далее работа устройства осуществпяется аналогично описанному выше. После записи нулевой информации в элемент 10-(n+l) памяти по последнему К-му адресу переключается в блоке 4 формирования режимов пятый D-трнггер 32 и устройство устанавливается

в исходное состояние, аналогично описанному в режиме Запись.

Кроме трех основных режимов Запись, Считывание и Стирание, в устройстве разрешены два совмещенньйс режима: Запись со стиранием и Считывание со стиранием.

Режим Запись - считьгоание является запрещенным. При одновременном поступлении на вход устройства сигналов Запись и Считывание устанавливается режим Запись. Если во врем исполнения режима Считывание поступил сигнал Запись, то после окончания цикла считьгоания информации по i адресу, во время которого поступил сигнал Запись, устройство выходит из режима Считывание и переходит к режиму Запись.

Режим Стирание - запись устанавливается после прихода сигналов на первый 12 и третий 14 командные входы устройства. В зтом режиме устройство работает также, как и в режиме Запись,но запись информационного сообщения в элементы памяти осуществляется без анализа информации в элементе 10-(n+l) памяти.

Режим Считывание - стирание устанавливается после прихода сигналов на второй 13 и третий 14 командные входы устройства, В этом режиме устройство работает также, как и в режиме Считьтание, но после считьшания информация с элементов 10 памяти по какому-то адресу осуществляется в этом же кадре развертки по сигналу fc стирание единичной информации с элемента lO-(n-i-l) памяти.

Таким образом, введение в предлагаемое устройство для сопряжения делителя частоты, дешифратора, двух триггеров, блока формирования vгримов позволило значительно расширить область применения устройства.

Авторы

Даты

1985-08-30—Публикация

1983-05-03—Подача