Изобретение относится к вычислительной технике, в частности к запоминающим устройствам с электрическим стиранием и преимуп1ественным считыванием информации, и может быть использовано в составе специализированных ЦБК или систем обработки данных в качестве энергонезависимого носителя информации.

Цель изобретения .- повышение надежности и расширение функциональных возможностей за счет обеспечения автоматического стирания перед записью, считывания информации в режиме записи и контроля достоверности

записанной информации в режиме записи.

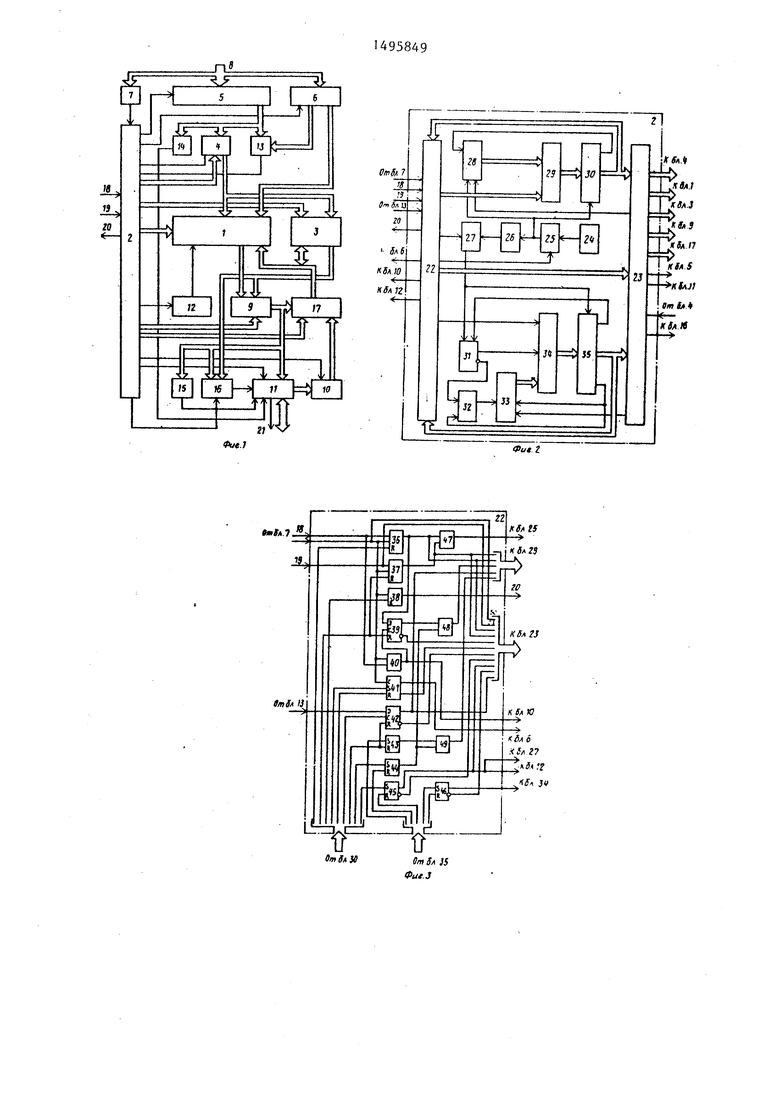

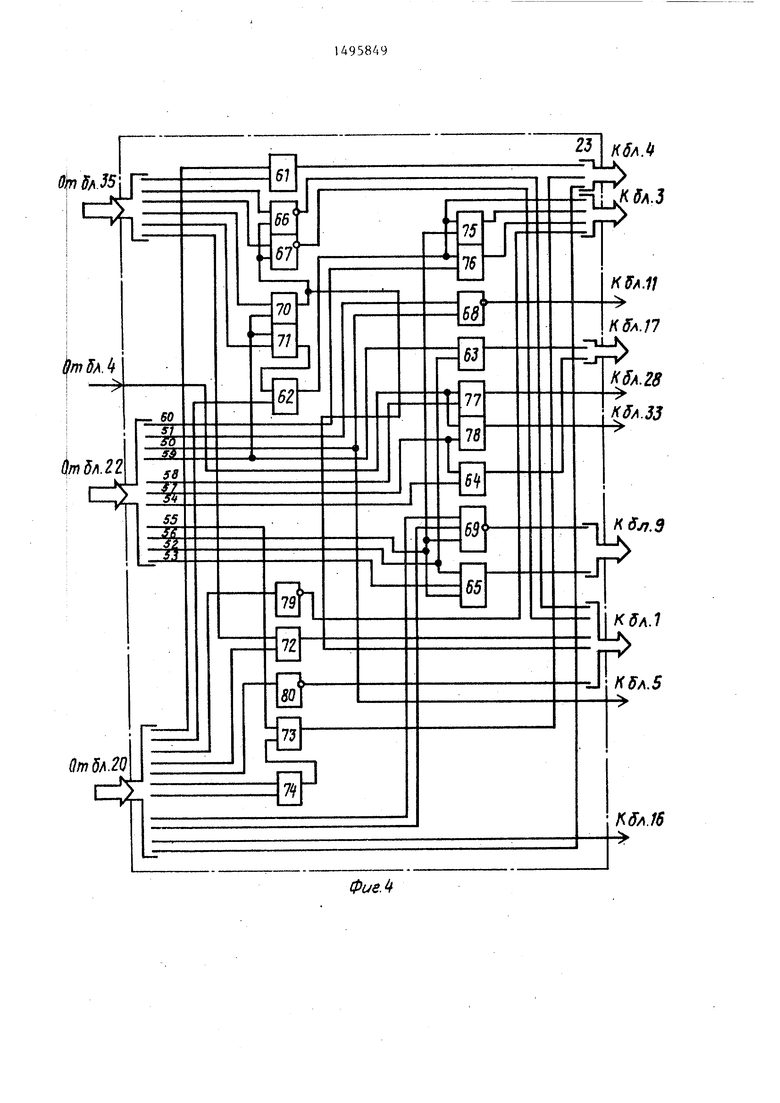

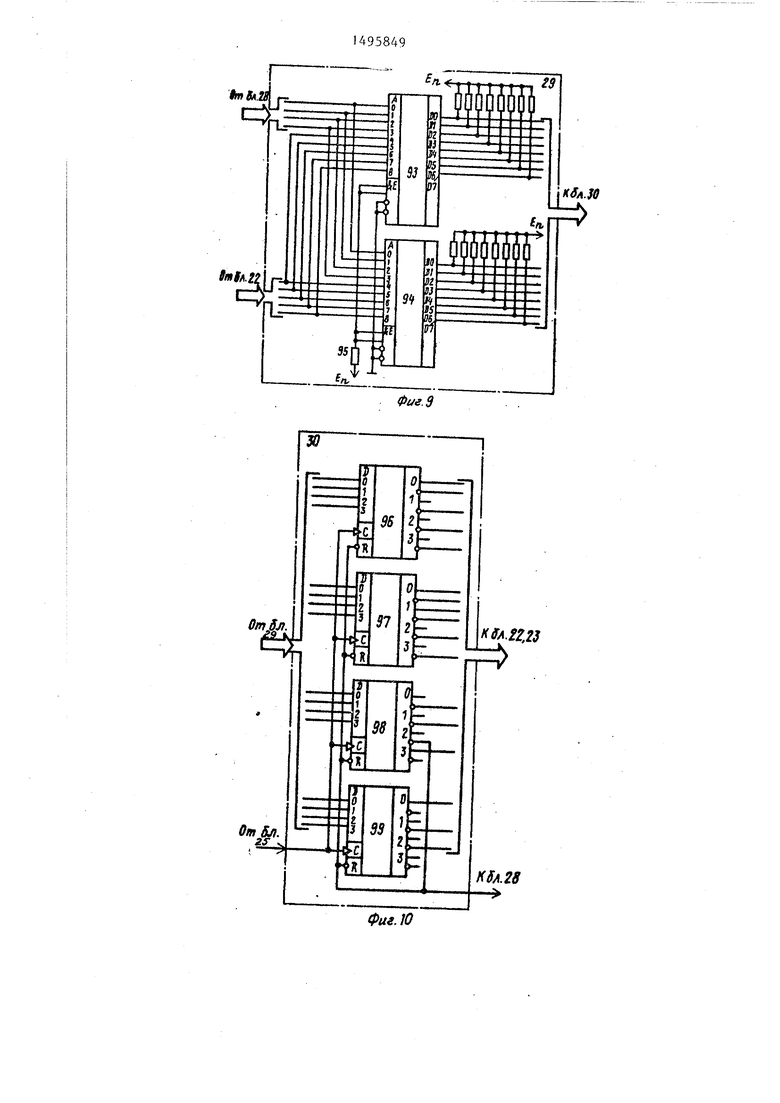

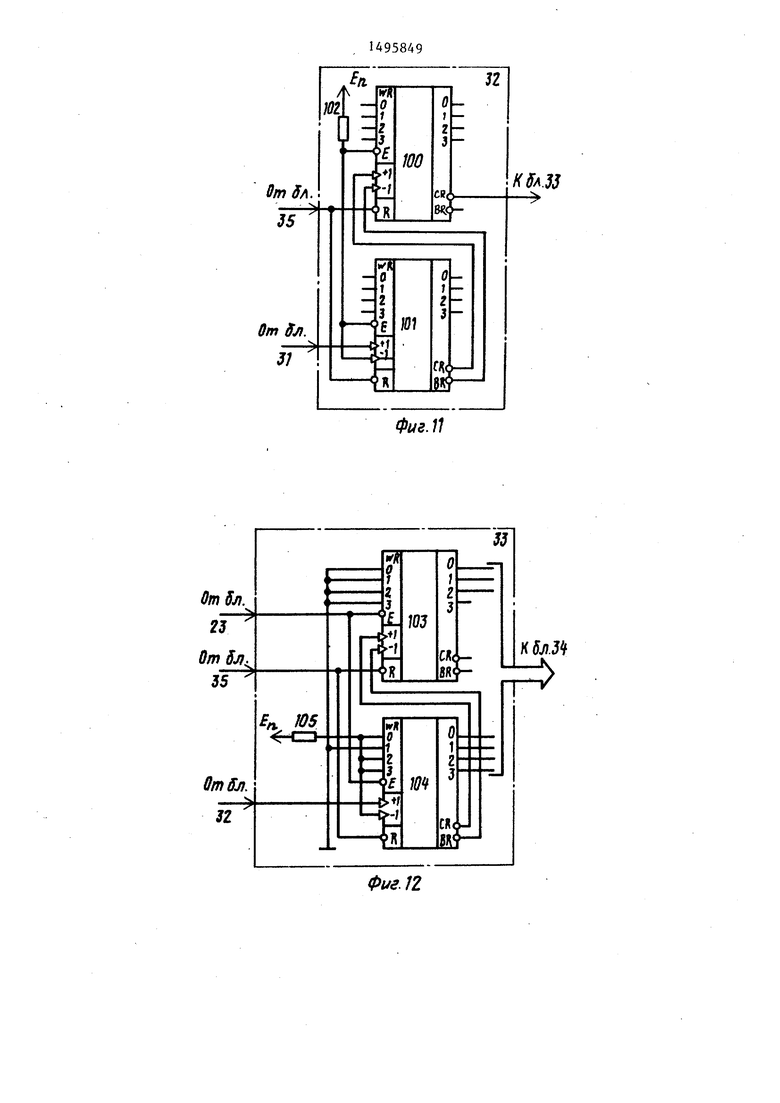

На фиг. 1 изображена схема запоминающего устройства; на фиг. 2 - схема блока управления; на фиг.З - схема регистра состояний; на фиг. 4 - схема блока сопряжения; на фиг. 5 - схема тактового генератора; на фиг. 6 - схема первого и второго синхронизаторов; на фиг.7 - схема делителя частоты; на фиг. 8 - схема первого регистра адреса микрокоманд; на фиг. 9 - схема первого управляющего ПЗУ; на фиг. 10 - схема первого регистра микрокоманд; на

.(

СО СП

00

со

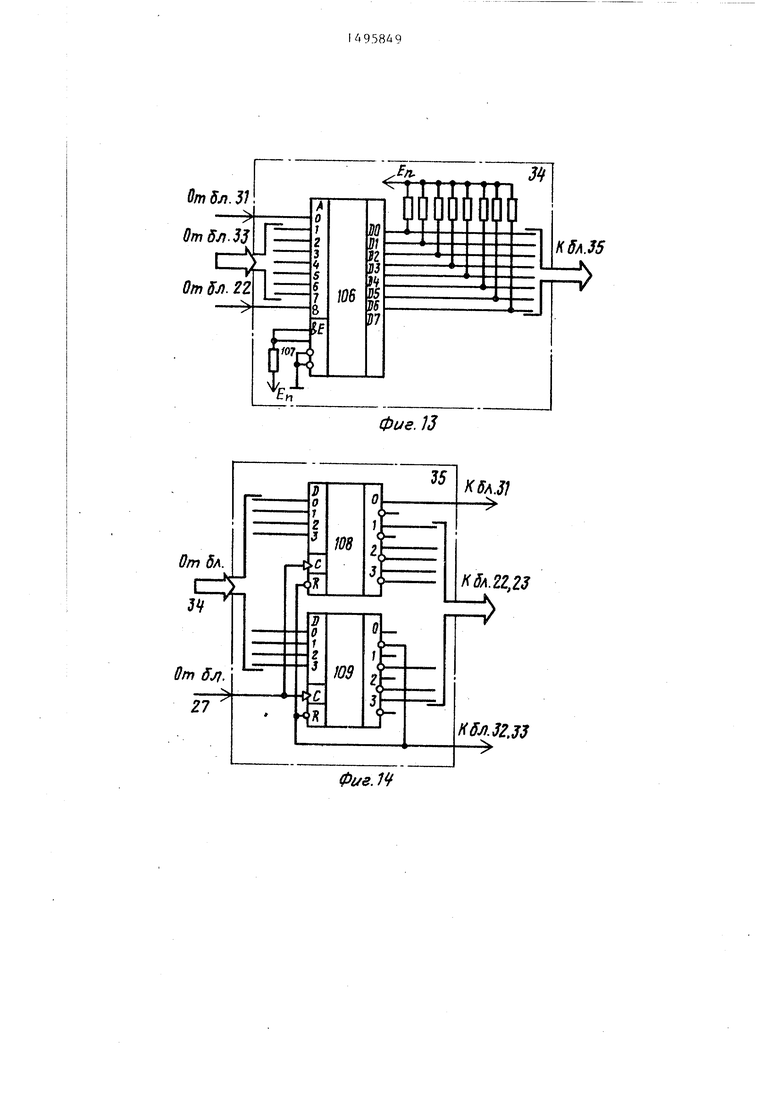

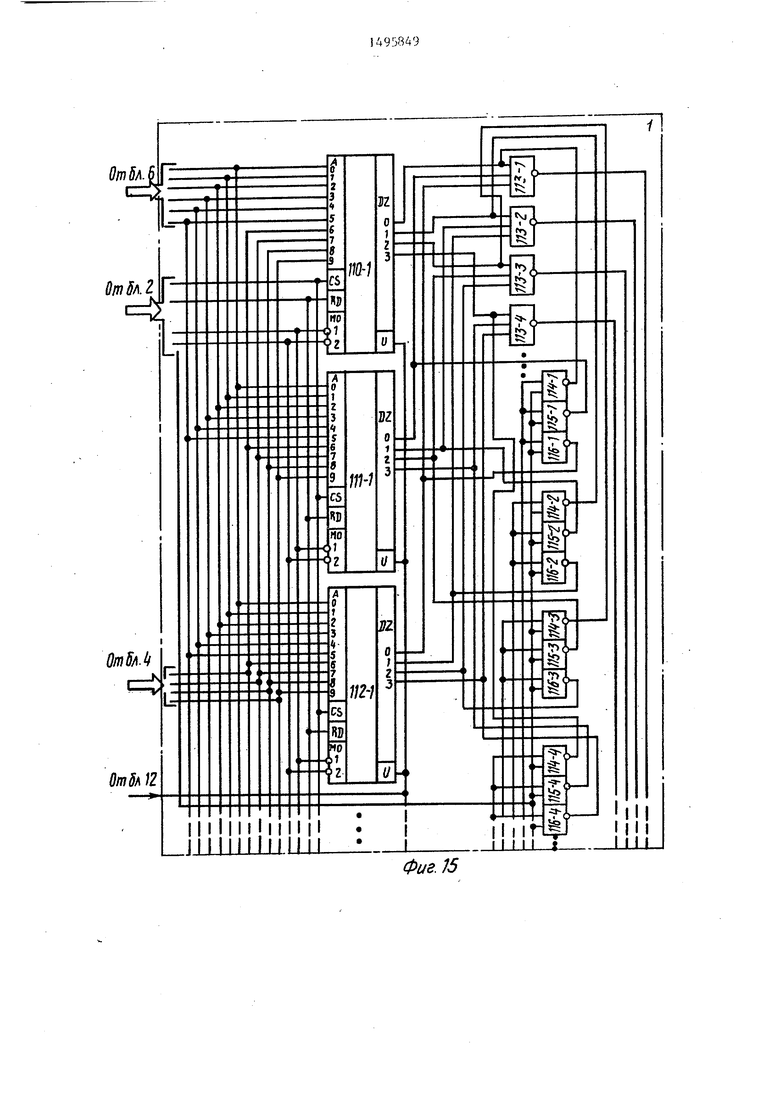

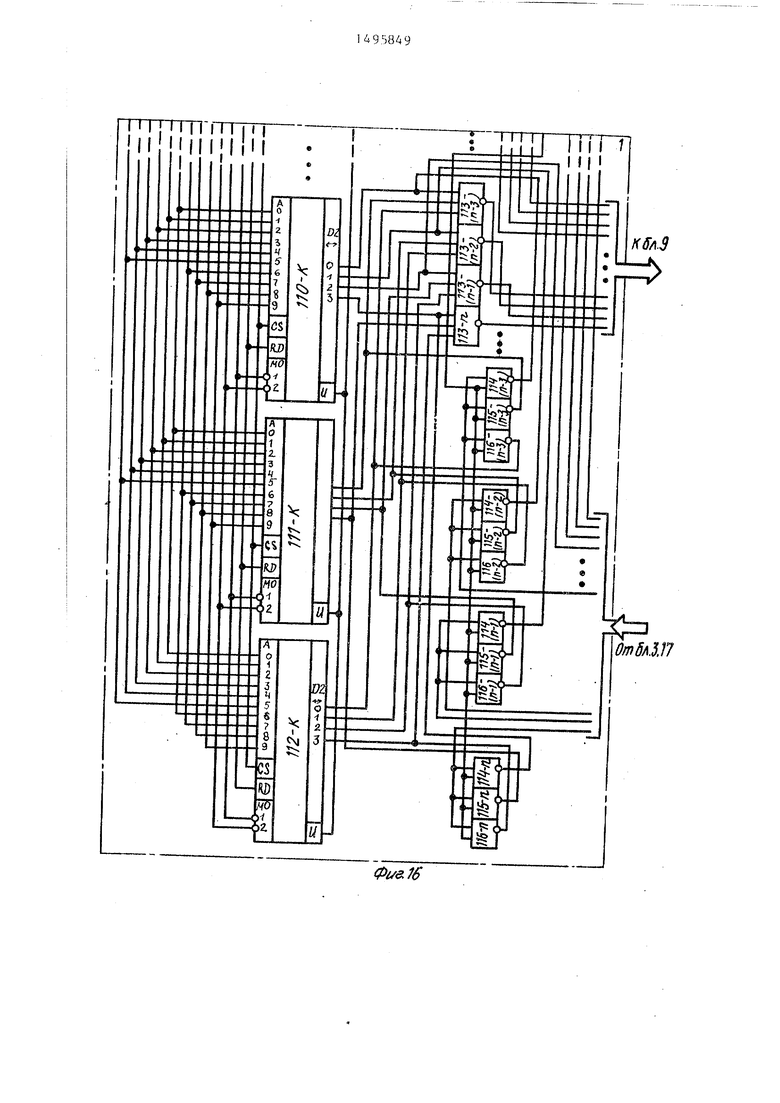

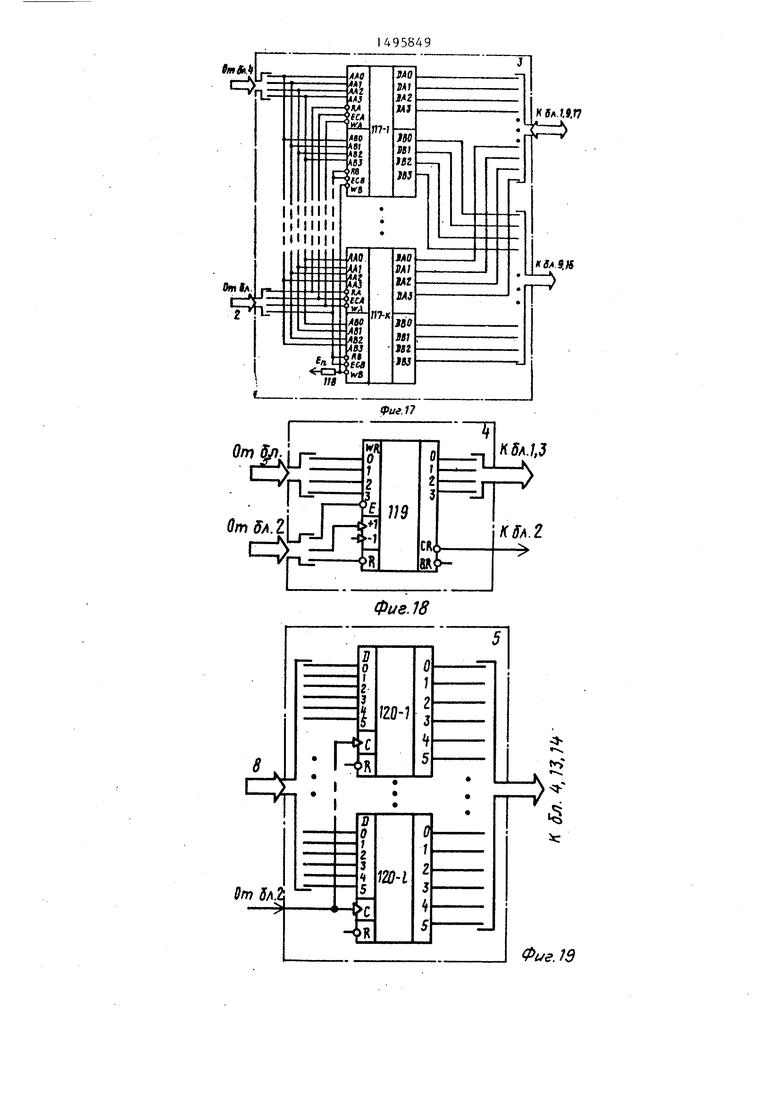

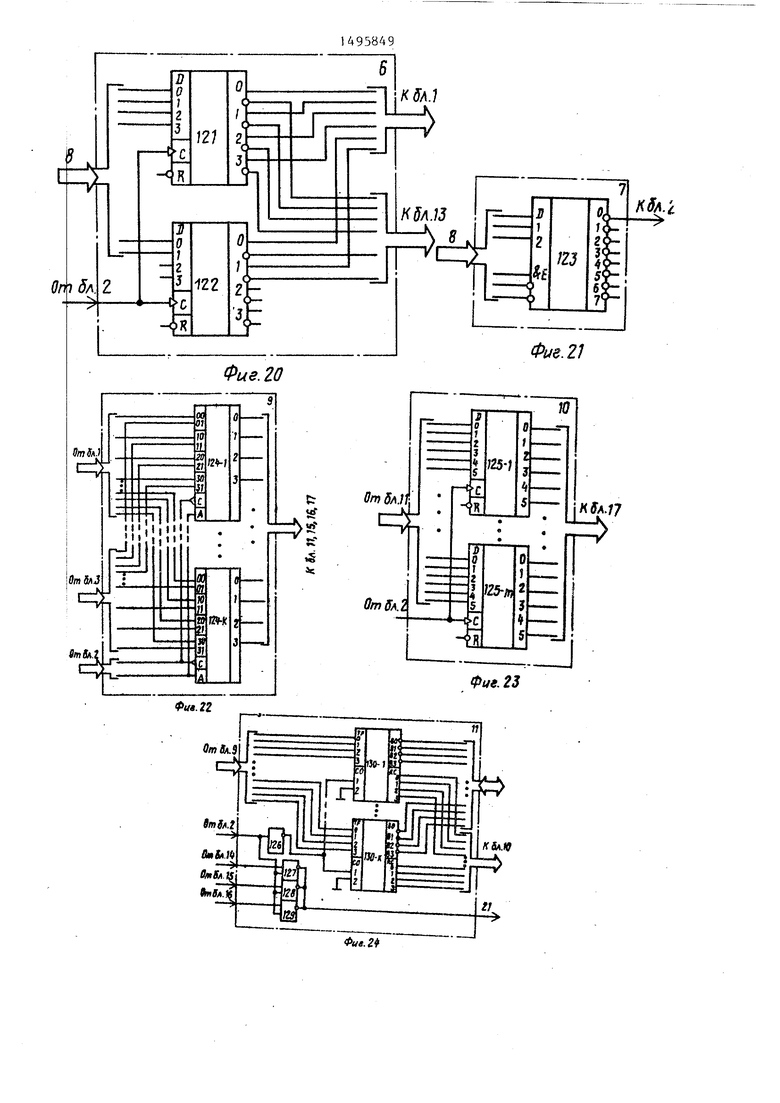

иг. 11 - схема счетчика циклов; на иг. 12 - схема второго регистра адреса микрокоманд; на фиг, 13 схема второго управляющего ПЗУ; на фиг.14- схема второго регистра микрокоманд; на фиг. 15 и 16 - схемы блока памяти; на фиг, 17 - схема страничного регистра; на фиг, 18 - схема счетчика адреса страницы; на фиг. 19 - схема регистра адреса; на фиг. 20 - схема регистра-защелки адреса; на фиг. 21 - схема дешифратора выборки; на фиг, 22 - схема регистра чтения; на фиг, 23 -. схема регистра записи; на фиг, 24 - схема блока приемопередатчиков; на фиг. 25 - схема формирователя высокого напряжения; на фиг, 26 - схема блока сравнения; на фиг, 27 - схема первого и второго блоков обнаружения ошибок; на фиг.28- схема формирователя сигнала ошибки; на фиг. 29 - схема блока мультиплексоров.

Запоминающее устройство (фиг,1) 25 ПЗУ (ШШ) 93 и 94 с нагрузочными резисторами и резистор 95.

UepBt регистр 30 микрокоманд (фиг. 10) содержит регистровые микросхемы 96-99 с общей синхронизацией 30 и сбросом на основе D-триггеров.

Счетчик 32 циклов (фиг. 11) содержит микросхемы двоичных счетчиков 100 и 101 и резистор 102.

Второй регистр 33 адреса микрокосодержит блок 1 памяти, блок 2 управления, страничный регистр 3,.счетчик 4 адреса страницы, регистр 5 адреса, регистр-защелку 6 адреса, дешифратор 7 выборки, адресные входы В устройства, регистр 9 чтения, регистр 10

записи, блок П приемопередатчиков,

формирователь 12 высокого напряжения,

блок 13 сравнения, первый блок 14

обнаружения ошибок, второй блок 15 35 (фиг. 12)- содержит двоичные че-

обнаружения ошибок, формирователь 16 тырехразрядные счетчики 103 и 104 с

сигнала ошибки, блок 17 мультиплексоров, вход 18 записи устройства, вход 19 считывания устройства, выход 20 готовности (готов/занят) устройства, выход 21 неисправности устройства,

Блок 2. управления (фиг, 2) содержит регистр 22 состояний, блок 23 сопряжения, тактовый генератор 24, первый синхронизатор 25, делитель 26 частоты, второй синхронизатор 27, первый регистр 28 адреса микрокоманд, первое унравлянлцее ПЗУ 29 (ЗТ13У 1), первый регистр 30 микрокоманд, триггер 31, счетчик 32 циклов, второй регистр 33 адреса микрокоманд, второе управляющее ПЗУ 34 (УПЗУ 2), второй регистр 35 микрокоманд.

Регистр 22 состояний (фиг. 3) содержит защелку 36 записи, защелку 37 чтения, триггер 38 блокировки, триггер 39 вторичной записи,элемент И 40, триггер 41 адреса страницы, триггер 42 схемы сравнения, триггер 43 контропредварительной установкой и сбросом и резистор 105.

УПЗУ 2 34 (фиг. 13) содержит БИС 40 ПЗУ 106 с нагрузочными резисторами и резистор 107.

Второй регистр 35 микрокоманд (фиг. f4) содержит регистровые микросхемы 108 и 109 с общей синхрони- 45 зацией и сбросом на основе D-триггеров.

Блок 1 памяти (фиг. 15 и 16) содержит К триад БИС перепрограммируемых постоянных запоминающих устройств 110-112 с электрическим стиранием (ЭСППЗУ), п мажоритарных элементов 113 и п триад .элементов 2И-НЕ 114116, причем К г , где п - разряд55 ность устройства; b - разрядность БИС ЭСППЗУ,

Страничный регистр 3 (фиг. 17) содержит К БИС I17 двухадресньвс регистров общего назначения с двумя

50

ля, триггер 44 холостого хода, триггер 45 стирания, триггер 46 перезаписи, элементы ИЛИ 47-49, управляю- щие выходы 50-60,

Блок 23 сопряжения (фиг. 4) содержит элементы И 61-65, элементы И-НЕ 66-69, элементы ИЛИ 70-78 и элементы НЕ 79 и 80,

Тактовый генератор 24 (фиг, 5) содержит элементы ЬГЕ 81-83, резисторы 84 и 85 и кварцевый резонатор 86. Первый 25 и второй 27 синхронизаторы (фиг. 6) содержат элемент И 87 и D-триггер 88.

Делитель 26 частоты (фиг, 7) последовательно включенные D-триггеры 89 и-90.

Первый регистр 28 адреса микроко- манд (фиг. 8) содержит двоичный четырехразрядный счетчик 91 с предварительной установкой и сбросом и резистор 92,

УНЗУ 1 29 (фиг. 9) содержит БИС

предварительной установкой и сбросом и резистор 105.

УПЗУ 2 34 (фиг. 13) содержит БИС ПЗУ 106 с нагрузочными резисторами и резистор 107.

Второй регистр 35 микрокоманд (фиг. f4) содержит регистровые микросхемы 108 и 109 с общей синхрони- зацией и сбросом на основе D-триггеров.

Блок 1 памяти (фиг. 15 и 16) содержит К триад БИС перепрограммируемых постоянных запоминающих устройств 110-112 с электрическим стиранием (ЭСППЗУ), п мажоритарных элементов 113 и п триад .элементов 2И-НЕ 114116, причем К г , где п - разрядность устройства; b - разрядность БИС ЭСППЗУ,

Страничный регистр 3 (фиг. 17) содержит К БИС I17 двухадресньвс регистров общего назначения с двумя

51

портами ввода-вывода и резистор 118 Счетчик 4 адреса страницы (фиг.18) содержит двоичный четырехразрядный счетчик 119 с предварительной уста- новкой и сбросом.

Регистр 5 адреса (фиг. 19) содержит 1 регистровых микросхем 120 с общей синхронизацией на основе D-триг- геров.

Регистр-защелка 6 адреса (фиг.20) содержит регистровые микросхемы 121 и 122 с общей синхронизацией на основе D-триггеров.

Дешифратор 7 выборки (фиг. 21) содержит двоичный дешифратор 123 типа 3-8.

Регистр 9 чтения (фиг, 22) содержит К двухканальных мультиплексоро в 124 со встроенными регистрами на вы- ходе.

Регистр 10 записи (фиг. 23) содержит m регистровых микросхем 125 с общей синхронизацией на основе D-три

геров.

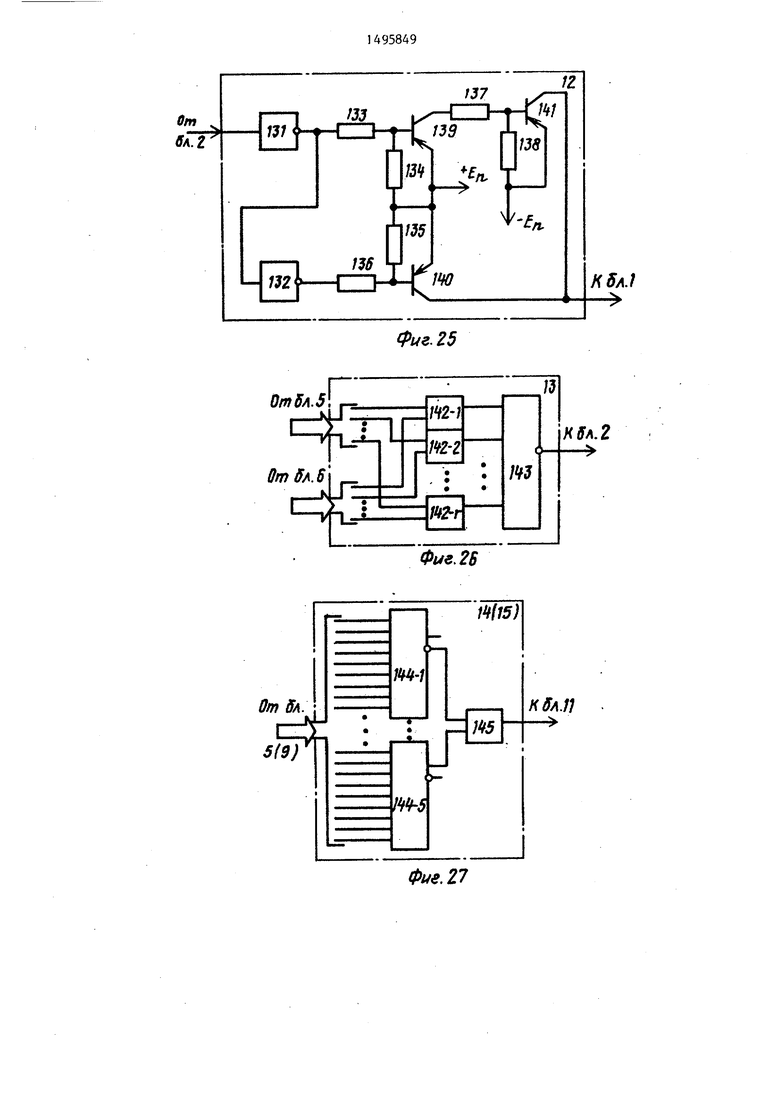

Блок 11 приемопередатчиков (фиг. 24) содержит элемент НЕ 126, элементы 2И-НЕ 127-129 с открытым коллектором и К микросхем приемопередатчиков 130.

Формирователь -12 высокого напряжения (фиг. 25) содержит элементы НЕ 131 и 132, регистры 133-138 и транзисторы 139-141.

Блок 13 сравнения (фиг. 26) содержит г элементов НЕРАВНОЗНАЧНОСТЬ 142 и элемент И-НЕ 143, где г - разрядность адреса страницы.

Первый 14 и второй 15 блоки обнаружения ошибок (фиг. 27) содержат S микросхем 144 генераторов четности и элемент НЕРАВНОЗНАЧНОСТЬ 145.

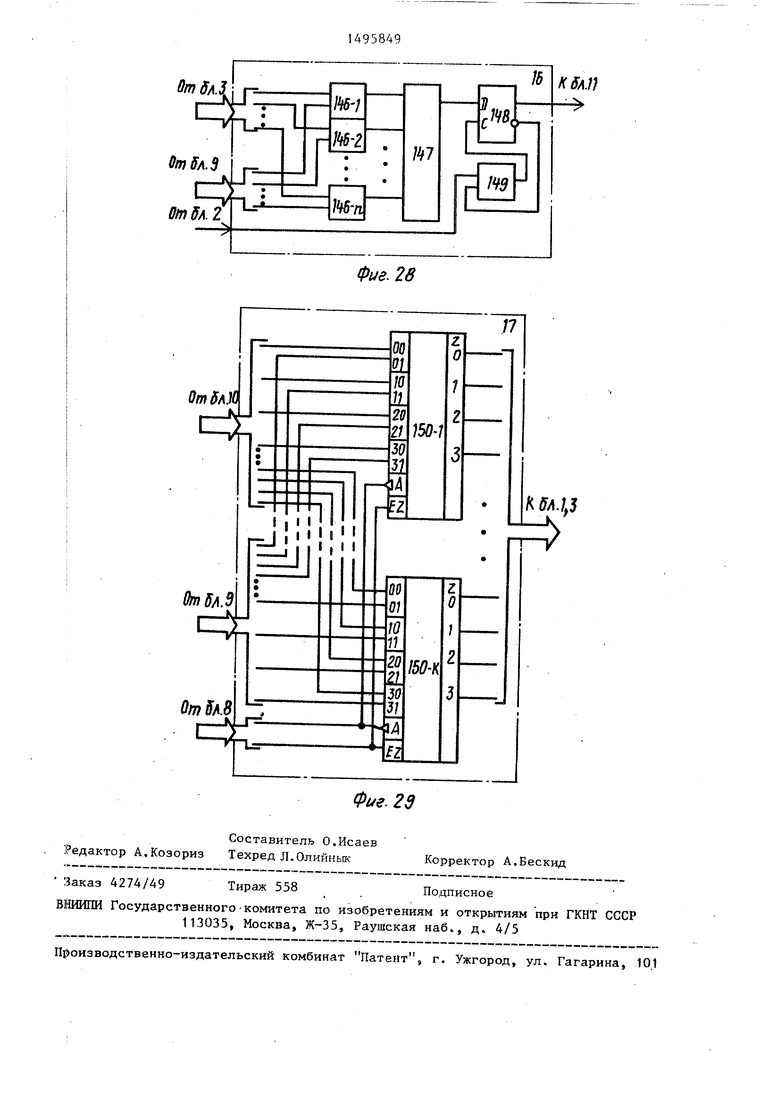

Формирователь 16 сигнала ошибки (фиг. 28) содержит п элементов НЕРАВНОЗНАЧНОСТЬ ,146, элемент ИЛИ 147, D-триггер 148 и элемент И 149.

Блок 17 мультиплексоров (фиг. 29) содержит К двухканальных мультиплексоров 150.

Устройство работает следующим об- разом.

При включении питающих напряжений происходит обнуление всех регистров (схема сброса по включению питания не показана).

В режиме считывания после появления сигналов адреса и считывания на соответствующих входах устройства дешифратор 7 выборки разрешает рабо

0

ту блока 2 управления, устанавливаII

5

0

5

0

З

0

5

ются в высокое состояние Г защелка 37 чтения и триггер 38 блокировки регистра 22 состояний, на выходе 20 устройства устанавливается сигнал готовности Готов/занят, одновременно происходит обнуление первого регистра 28 адреса микрокоманд и разрешается прохождение синхроимпульсов с выхода тактового генератора 24 через первый синхронизатор 25 на вход последовательного счета первого регистра 28 адреса микрокоманд и вход загрузки первого регистра 30 микрокоманд; загружается также код адреса в регистр 5 адреса и регистр- защелку 6 адреса. При этом регистр- защелка 6 адреса защелкивается благодаря тому, что ее вход загрузки соединен с выходом триггера 41 адреса страницы регистра 22 состояний. Сигналы, поступающие из регистра 22 состояний на группу входов УПЗУ1 29, определяют область адресов микропрограммы считывания. Управляющие сигналы, задаваемые микропрограммой, через первый регистр 30 микрокоманд и блок 23 сопряжения поступают на соответствующие узлы устройства. Старшие разряды адреса (адрес страницы) поступают на входы блока 1 памяти из регистра-защелки 6 адреса. По первой микрокоманде микропрограммы считывания младщие разряды адреса загружаются в счетчик 4 адреса страницы и поступают на блок 1 памяти. Затем вырабатываются и подаются на блок 1 памяти сигналы, соответствующие режиму считывания (сигналы выборки кристалла и разрешения считывания) . Одновременно первый блок 14 обнаружения ошибок осуществляет контроль по модулю два поступающего адресного кода, В случае ошибки вырабатывается сигнал неисправности, который через блок 11 приемопередатчиков поступает на выход 21 неисправности устройства.

По истечении времени выборки используемых в блоке 1 памяти микросхем ЭСППЗУ снимаются сигналы считывания и подается сигнал загрузки регистра 9 чтения, на группу входов которого подаются данные, считанные из блока 1 памяти. После загрузки регистра 9 чтения данные поступают через блок 11 приемопередатчиков на информационные входы-выходы устройства и одновременно на второй блок 15 обнаружения ошибок, который осуществляет контроль по модулю два поступающей информации и в случае ошиб- ки вырабатывает сиг нал неисправности которьм через блок 11 приемопередатчиков поступает на выход 21 неисправности устройства. Поскольку считанная информация поступает с блока 1 памяти, мажоритарные элементы которого исправляют все одиночные ошибки элементарных разрядов, соответствующих различным разрядам слова данных, второй блок 15 обнаружения ошибок обнаруживает все одиночные ошибки в слове данных, к которым могут привести кратные овшбки в элементарных разрядах блока 1 памяти, и вероятность ошибки более высокого порядка низка. Затем все задействованные регистры устройства обнуляются. Устройство готово к следующему обращению.

В режиме записи после появления сигналов записи, адреса и входной информации на соответствующих входах устройства, дешифратор 7 выборки разрешает работу- блока 2 управления, устанавливаются в высокое состояние 1 защелка 36 записи и триггер 38 блокировки регистра 22 состояний, на выходе 20 устройства устанавливается сигнал готовности Готов/занят, загружаются регистр 5 адреса, регистр- защелка 6 адреса и регистр 10 записи. Одновременно происходит обнуление первого регистра 28 адреса микрокоманд и первого регистра 30 микрокоманд и разрешается прохождение син хроимпульсов с выхода тактового генератора 24 через первый синхронизатор 25 на соответствующие входы первого регистра 30 микрокоманд. Сигналы, поступающие из регистра 22 состояний на группу входов УПЗУ1 29, определяю область адресов микропрограммы,считывания страницы.

При этом адрес считываемой страницы определяется состоянием регистра- защелки 6 адреса. Микропрограмма осуществляет считывание данных из блока 1 памяти при нулевом состоянии счетчика 4 адреса страницы, загружает их в регистр 9 чтения, затем записыв ает эти данные в страничный регистр 3 через первый порт ввода-вывода. Далее инкрементнруется счетчик 4 адреса страницы и обнуляются первый ре

Q

5

5

гистр 28 адреса микрокоманд и первый регистр 30 микрокоманд. Описанный участок микропрограммы повторяется. Таким образом,происходит циклическая перезапись страницы информации из блока 1 памяти в страничньй регистр 3. После перезаписи последнего слова страницы и инкрементирования счетчика 4 адреса страницы по переполнению последнего происходит выход из ицкла микропрограммы. Сигнал переполнения счетчика 4 адреса страницы через блок 23 сопряжения поступает на вход параллельной загрузки первого регистра 28 адреса микрокоманд, загружая адрес перехода, после чего младшие разряды принятого по обращению адреса из регистра 5 адреса записываются в счетчик 4 адреса страницы. Затем по этому адресу в страничный регистр 3 заносится информация из регистра 10 записи через первый порт ввода-вывода. Устанавливаются триггер 45 стирания и триггер 44 холостого хода и сбрасывается триггер 38 блокировки регистра 22 состояний, с выхода 20 устройства снимается сигнал блокировки Готов/занят. Таким образом, в микропрограмме считывания страницы происходят перезапись страницы данных из блока 1 памяти в страничный регистр 3 и ее модификация в соответствии с принятой в регистр 10 записи информацией.

После установки триггера 45 стирания разрешается прохождение синхроимпульсов через делитель 26 частоты и второй синхронизатор 27 на соответствующие входы триггера 31 и второго регистра 35 микрокоманд. Прямой выход триггера 31 подключен к младшему разряду адреса УПЗУ2 34, а инверсный выход триггера 31 через счетчик 32 циклов - к последовательному входу второго регистра 33 адреса микрокоманд. Переключение младшего разряда адреса УПЗУ2 34 и инкре- ментирование счетчика циклов осуществляются за счет того, что в одном из разрядов данных У113У2 34 записаны поочередно нули О и единицы 1. I Вследствие этого при каждом синхроимпульсе информация в этом разряде, подключенном к информационному входу триггера 31, меняется, вызывая переключение последнего. Инкрементирова- ние второго регистра 33 адреса микрокоманд осуществляется по переполне

нию счетчика 32 циклов. Такая организация позволяет отрабатывать длительные временные диаграмг и Сигнал, поступающий из регистра 22 состоя- НИИ на вход старшего разряда адреса УПЗУ2 34, определяет область адресов микропрограммы стирания. После установки триггера 34 холостого хода сигналы, поступающие из регистра 22 состояния на группу входов УПЗУ1 29, определяют область адресов с холостыми микрокомандами, т.е. на выходе первого регистра 30 микрокоманд управляющие сигналы отсутствуют.

С выхода второго регистра 35 микрокоманд на блок 1 памяти через блок 23 сопряжения поступают сигналы разрешения выборки, разрешения записи и разрешения стирания. Формирователь 12 высокого напряжения вырабатывает импульс высокого напряжения, и в блоке 1 памяти происходит стирание страницы по адресу, задаваемому регистром-защелкой 6 адреса. Так как про- цесс стирания занимает довольно длительное время (от десятков до сотен и более миллисекунд для различных БИС ЭСППЗУ), разрешается обращение к устройству после окончания микропро- Граммы считывания страницы и начала микропрограммы стирания.

При считывании сбрасывается триггер 44 холостого хода, загружается регистр 5 адреса и устанавлива

ется защелка 37 чтения и триггер 38 блокировки регистра 22 состояний. На выходе 20 устройства появляется сигн готовности Готов/занят. Инициирует ся выполнение микропрограммы вторичного считывания. При этом блок 13 сравнения осзпществляет поразрядное сравнение состояний защелки 6 адреса и соответствующих разрядов регистра 5 адреса. В случае несовпадения единичное 1 значение сигнала с выхода блока 13 сравнения поступает на информационный вход триггера 42 схемы сравнения регистра 22 состояния, и первая микрокоманда взводит этот триггер, в результате чего код, поступающий на группу адресных входов УПЗУ1 29, определяет область адресов йикропрограммы, устанавливающей триггер 44 холостого хода. При этом триггер 38 блокировки и защелки 37 чтения регистра 22 состояния остаются взведенными.

Q|5

2025зо

«

ал - .„ .

50

В случае совпадения кодов адреса, загруженного в регистр 5 адреса и регистр-защелку 6 адреса, когда на выходе блока 13 сравнения устанавливается нулевой ур овень О сигнала и триггер 42 схемы сравнения не взводится, следукщая микрокоманда микропрограммы вторичного считывания загружает в счетчик 4 адреса страницы младшие разряды адреса из регистра 5 адреса, затем вырабатываются соответствующие сигналы для считывания слова данных из страничного регистра 3 через второй порт ввода-вывода. Считанное слово загружается в регистр 9 чтения и через блок 11 приемопередатчиков поступает на информационные входы-выходы устройства. Одновременно сбрасываются триггер 38 блокировки сигналом готовности Готов/занят на выходе 20 устройства и защелка 37 чтения, устанавливается триггер 44 холостого хода регистра 22 состояний.

При этом микропрограмма стирания либо продолжает выполняться, либо заканчивается и устройство ожидает следующего обращения.

При обращении по записи в момент стирания защелка 36 записи уже взведена, поэтому взводятся триггер 39 вторичной записи, триггер 38 блокировки сигналом готовности Готов/занят на выходе 20 устройства, сбрасывается триггер 44 холостого хода регистра 22 состояний, загружаются регистр 5 адреса и регистр 10 записи, по началу обращения обнуляются первьй регистр 28 адреса микрокоманд и первьй регистр 30 микрокоманд. Слово состояния, поступающее из регистра 22 состояний на группу адресных входов УПЗУ1 29, определяет область адресов микропрограммы вторичной записи. Загружается триггер 42 схемы сравнения и если он взводится (коды регистра 3 и регистры-защелки 6 адреса не совпадают) на выходе регистра 22 состояний появляется код, определяющий область адресов микропрограммы, сбрасывающей триггер 39 вторичной записи и устанавливающей триггер 44 холостого хода регистра 22 состояний. При этом триггер 38 блокировки сигналом готовности Готов/занят на выходе 20 устройства остается взведенным.

Если микрокоманда загрузки триггера 42 схемы сравнения не взводит его.

т.е. обращение производится в ту же страницу, которая в данный момент обрабатывается, то младшие разряды адреса из регистра 5 адреса загружаются в счетчик 4 адреса страницы, и вырабатываются сигналы записи информации из регистра 10 записи в страничный регистр 3 через первый порт ввода-вывода.

Затем сбрасываются триггер 39 вторичной записи, триггер 38 блокировки, устанавливается триггер 44 холостого хода, и устройство ожидает следующего обращения.

По окончании микропрограммы стирания устанавливается триггер 46 перезаписи, сбрасывается триггер 45 стирания, т.е. запрещается прохождение синхроимпульсов через второй синхронизатор 27 на соответствующие входы триггера 31 и второго регистра 35 микрокоманд, и обнуляются второй регистр 33 адреса микрокоманд, счетчик 32 циклов и второй регистр 35 микрокоманд. Устройство ожидает следующего обращения. В том случае, когда обращения происходят в ту же страницу, адрес которой защелкнут в защелке 6 адреса, обрабатываются микропрограммы вторичного считывания либо вторичной записи, и доступ осуществляется только в страничный регистр 3. При обращении в другую страницу взводится триггер 45 стирания и триггер 44 холостого хода регистра 22 состояний, разрешается прохождение синхроимпульсов через второй синхронизатор 27 на счетные входы триггера 31 и второго регистра 35 мик- рокоманд. Сигнал, поступающий из регистра 22 состояний на вход старшего разряда адреса УПЗУ2 34 (взведенный триггер 46 перезаписи), определяет область-адресов микропрограммы перезаписи.

В микропрограмме перезаписи выра- батьгеаются сигналы разрешения записи для блока I памяти, формирователь 12 высокого напряже:ния вырабатывает импульсы напряжения программирования, подаются сигналы разрешения выборки и разрешения считывания на страничный регистр 3 для считывания данных через первый порт ввода-вбшод и подачи их в качестве входной информации на блок 1 памяти.

При этом на блок 1 памяти старшие разряды адреса, определяющие адрес

5

0 5 о д 5

5

0

страницы, подаются из регистра-защелки 6 адреса, а младшие разряды адреса подаются одновременно на блок I памяти и страничный регистр 3 со счетчика 4 адреса страницы, причем микропрограмма перезаписи начинается с нулевого значения счетчика 4 адреса страницы. По окончании перезаписи слова с нулевым адресом внутри страницы из страничного регистра 3 в блок 1 памяти происходят инкремени- рование счетчика 4 адреса страницы и обнуление второго регистра 33 адреса микрокоманд, счетчика 32 циклов и второго регистра 35 микрокоманд, т.е. осуществляется возврат на начало микропрограммы с новым значением адреса внутри страницы. По окончании перезаписи последнего слова страницы происходит переполнение счетчика 4 адреса страницы. Импульс переполнения через блок 23 сопряжения загружает во второй регистр 33 адреса микрокоманд адрес перехода и, таким образом, инициирует выход из цикла на линей- . ный участок микропрограммы перезаписи. Далее вырабатываются холостые команды (отсутствие управляющих сигналов) для формирования времени выдержки до обращения после записи, длительность которого специфицируется техническими условиями на данный тип БИС ЭСППЗУ. Затем устанавливается триггер 43 контроля, сбрасываются триггер 46 перезаписи, триггер 45 стирания и триггер 44 холостого хода регистра 22 состояний,, обнулйются второй регистр 33 адреса микрокоманд, счетчик 32 циклов, второй регистр 35 микрокоманд. Сигналы, поступающие из регистра 22 состояний на группу входов Л13У1 29, определяют область адресов микропрограммы контроля,

В микропрограмме конт))оля счетчику 4 адреса страницы присваивается нулевое значение и вырабатываются сигналы.разрешения выборки и разрешения считывания для блока 1 памяти Считанное слово загружается в регистр 9 чтения. Одновременно вырабатываются сигналы разрешения выборки и разрешения считывания слова данных из страничного регистра 3 через .второй порт ввода-вывода. Информация из регистра 9 чтения поступает на первую группу входов формирователя 16 сигнала ошибки, а информация из страничного регистра 3 - на вторую rpyjiпу входов блока 16. Блок 16 осуществляет поразрядное сравнение, и в случае несовпадения хотя бы по одному разряду срабатывает защелка неис- правности (D-триггер 148, элемент И 149).

Затем счетчик 4 адреса страницы инкрементируется, обнуляются первый регистр 28 адреса микрокоманд и пер- вый регистр 30 микрокоманд, и процес циклически повторяется до заполнения счетчика 4 адреса страницы, т.е. осуществляется сравнение всей информации вновь записанной страницы с со- держимым страничного регистра З По переполнению счетчика 4 адреса страницы, микропрограмма контроля выходит из цикла (импульс переполнения счетчика 4 адреса страницы через блок 23 сопряжения загружает адрес перехода в первый регистр 28 адреса микрокоманд), осуществляется сброс триггера 41 адреса страницы, затем триггер 41 адреса страницы вновь взводится, т.е. осуществляется загрузка нового адреса той страницы в регистр-защелку 6 адреса, обращение к которой инициирует микропрограмму перезаписи. Одновременно сбрасывают- ся триггер 42 схемы сравнения и триггер 43 контроля регистра 22 состояния.

Если обращение в новую страницу, инициировавшее микропрограмму пере- записи, осзществляется по записи, то проводятся обнуление регистра 28 адреса микрокоманд и первого регистра 30 микрокоманд и переход к микропрограмме считывания страницы. На- чинается обработка новой страницы по записи.

Если обращение в новую страницу, инициировавшее микропрограмму пере- записи, осуществляется по считыванию (защелка 37 чтения взведена), производится сброс заделки 36 записи, обнуление первого регистра 28 адреса микрокоманд и первого регистра 30 микрокоманд и переход к микропрограмме считывания. После окончания микропрограммы считывания все задействованные регистры обнуляются, и устройство приходит в исходное состояние.

Использование микропрограммного блока управления обеспечивает большу гибкость устройства и позволяет использовать в блоке памяти любые тиио- номиналы БИС ЭСиПЗУ, а также организовывать различные контрольные и диагностические проверки на микропрограммном уровне.

Стирание осуществляется автоматически в режиме записи, при этом стираемая информация сохраняется в страничном регистре. Перезапись в блок памяти происходит только после модификации всей страницы либо при обращении в другую страницу. В цикле записи данные страничного регистра доступны пользователю. Такая организация повышает производительность предлагаемого устройства, а также осуществляет экономию циклов стирание-запись.

Контроль достоверности записанных данных осуществляется в цикле записи путем считывания информации из блока памяти и сравнивания ее с содержимым страничного регистра.

Формула изобретения

Запоминающее устройство, содержащее блок памяти, блок управления, первый выход которого соединен с управляющим входом блока приемопередатчиков, информационные выходы которого подключены к информационным входам регистра записи, а информационные входы соединены с выходами регистра чтения, информационные входы первой и второй групп которого подключены соответственно к выходам страничного регистра и блока памяти, вход питания которого соединен с выходом формирователя высокого напряжения, информационные входы и адресные входы первой группы блока памяти подключены соответственно к входам-выходам страничного регистра и к прямым выходам регистра-защелки адреса, информационные входы которого являются адресными входами первой группы устройства, а синхровход соединен с вторым выходом блока управления, выходы первой, второй и третьей групп которого подключены соответственно к управляющим входам страничного регистра, регистра чтения и блока памяти, третий и четвертый выходы блока управления соединены соответственно с управляющим входом формирователя высокого напряжения и с синхровходом регистра записи, первый и второй входы и пятый выход бло-

ка управления являются соответственно входами записи и считывания и выходом готовности устройства, управляющий выход блока приемопередатчиков является выходом неисправности устройства, отличающееся тем, что, с целью повьшеиия надежнос- |ги и расширения функциональных возусловного перехода блока управления, вход задания режима и выходы четвертой группы которого подключены соответственно к выходу переполнения и управляющим входам счетчика адреса страницы, информационные выходы которого соединены с адресными входами второй группы блока памяти и с ад

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с накопителем на магнитных дисках | 1986 |

|

SU1410046A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Устройство управления накопителями на магнитных дисках | 1988 |

|

SU1532956A1 |

| Процессор | 1984 |

|

SU1247884A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737510A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1188736A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам с электрическим стиранием и преимущественным считыванием информации, и может быть использовано в составе специализированных ЦВМ или систем обработки данных в качестве энергонезависимого носителя информации. Целью изобретения является повышение надежности и расширение функциональных возможностей за счет обеспечения автоматического стирания перед записью, считывания информации в режиме записи и контроля достоверности записанной информации в режиме записи. Устройство содержит блок памяти, блок управления, страничный регистр, счетчик адреса страницы, регистр адреса, регистр-защелку адреса, дешифратор выборки, регистр чтения, регистр записи, блок приемопередатчиков, формирователь высокого напряжения, блок сравнения, первый и второй блоки обнаружения ошибок, формирователь сигнала ошибки и блок мультиплексоров.Цель изобретения достигается тем, что во время цикла стирания обеспечиваются запись и считывание данных из стираемой страницы, микропрограммно загруженной в страничный регистр. 29 ил.

ожиостей за счет обеспечения автома- д ресными входами страничного регистра.

1гического стирания перед записью, О-читывания информации в режиме записи и контроля достоверности записанной информации в режиме записи, в )стройство введены первый и второй Ьлоки обнаружения ошибок, блок муль- (гиплексоров, блок сравнения, счетчик реса страницы,регистр адреса, де- иифратор выборки и формирователь сиг- аала ошибки, причем входы дешифрато- ра выборки являются адресными входами второй группы устройства, выход де- иифратора выборки соединен с входом 1ризнака разрешения блока управления, (иестой выход которого подключен к |синхровходу регистра адреса, информационные входы которого соединены с адресными входами первой группы уст- |)ойства, а вьрсоды подключены к входам

hepBoro блока обнаружения ошибок, ус- 30 ды второй группы и выходы которого

тановбчным входам счетчика адреса ртраницы и к входам первой группы Ьлока сравнения, входы второй группы и выход которого соединены соответственно с инверсными выходами регистра- ,, информационными входами-выходами уст

защелки адреса и с входом признака

ройства.

информационные входы первой группы блока мультиплексоров подключены к выходам регистра чтения, к входам второго блока обнаружения ошибок и к информационным входам первой группы формирователя сигнала ошибки,, информационные входы второй группы, управляющий вход и выход которого соединены соответственно с выходами страничного регистра, седьмым выходом блока управления и с первым входом признака ошибки блока приемопередатчиков, второй и третий входы признака ошибки которого подключены к выходам соответственно первого и второго блоков обнаружения ошибок, выходы пятой группы блока управления соединены с управляющими входами блока мультиплексоров, информационные вхоподключены соответственно к выходам регистра записи и к входам-выходам страничного регистра, входы-выходы блока приемопередатчиков являются

ройства.

Фие.)

tmh.J

Йт1л 1}

ff

OmftK

Фи Z

KfflS

3V

Фие.

Фие.5

Фие.в

К5А.25 -

Фив.7

Фие.в

Фиг. Ю

Фиг. 11

Фиг. 12

К5л.35

фие. 13

Фиг. /

Фи8. /5

KffA.c.,;

фиг. 18

1

Фие. J9

От 5л

Фие.гО

даЫ

Сг

-Nuf rr-V,

tS Se

Фив. 22

ОтЙл.5

Фив. 2

495849

.i

Фие.21

Ю

Ш

KSA.17

От5л.г

Фиг. 23

OmSA.sl Г-.

От Л|. 6

От SA.

5(9)

JUyLJ -r

:

Фиг. 25

Фие.26

иГ

Jits

Кбл.П -

Фие.27

. 28

| Запоминающее устройство | 1984 |

|

SU1243033A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Electronic Design | |||

| August | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Устройство для разметки подлежащих сортированию и резанию лесных материалов | 1922 |

|

SU123A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-07-23—Публикация

1987-12-16—Подача