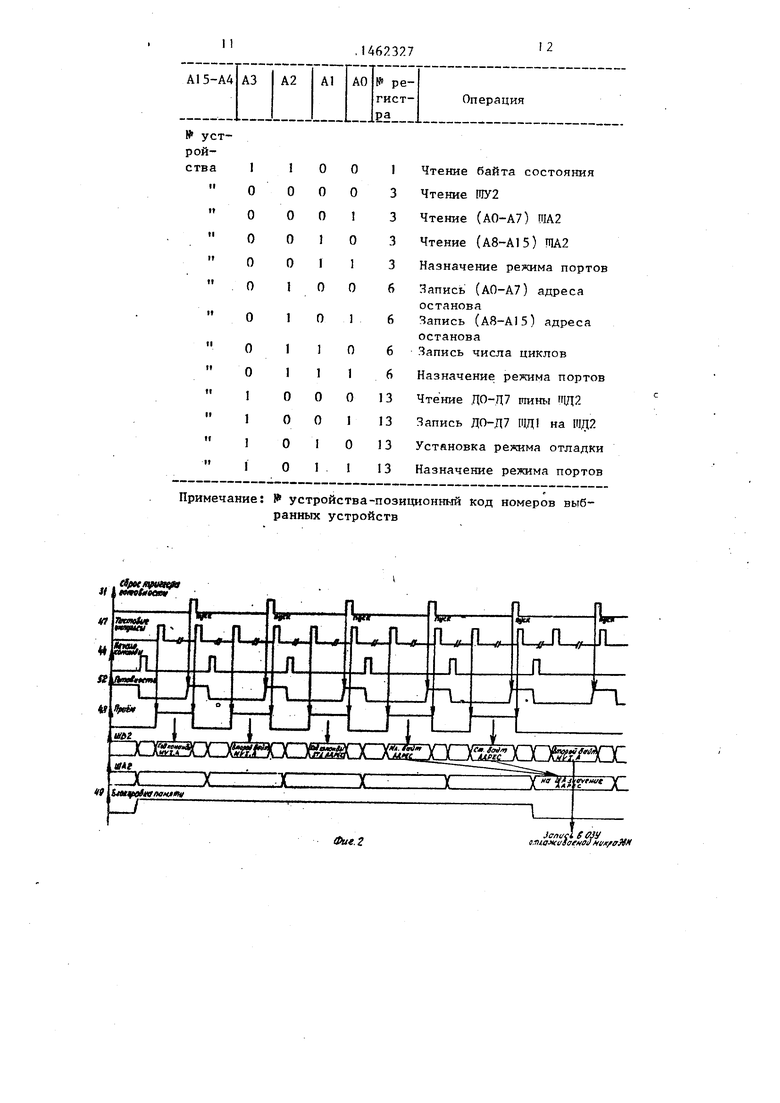

.роЭВМ переходит в состояние ожидания g ША2, Память разблокируется в резульи память ее блокируется.

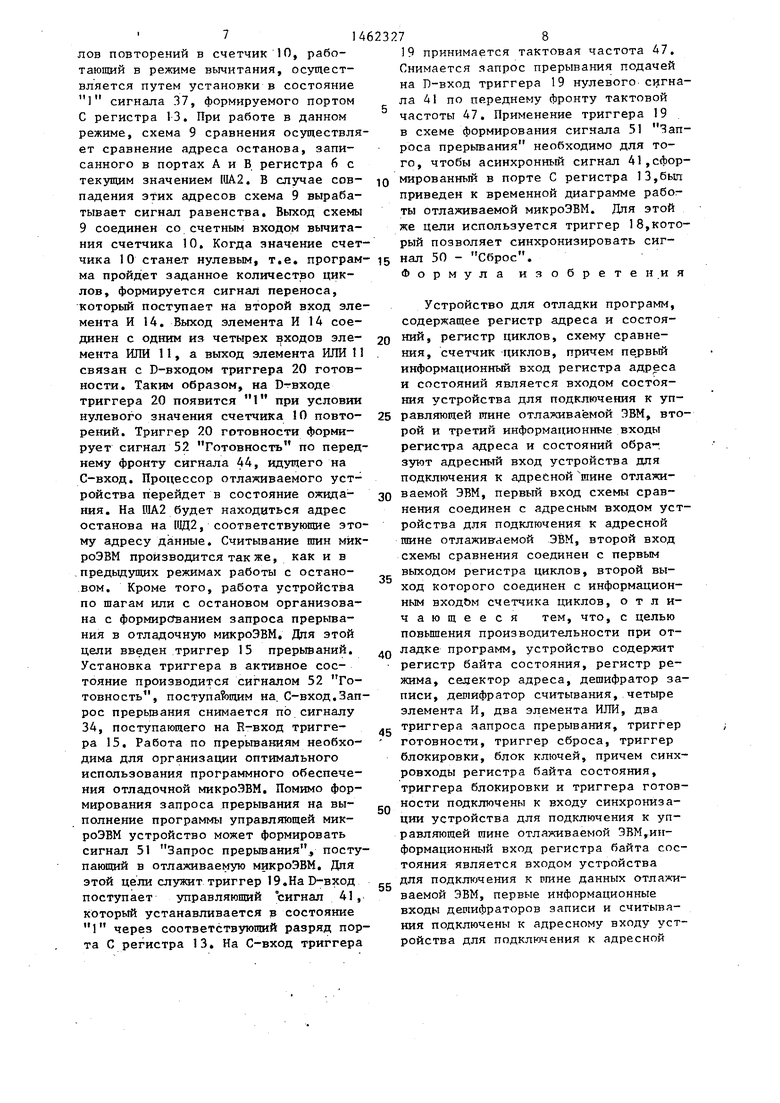

Затем в порт В регистра 13 загружается значение байта данных команды MVTA, ДАННЫЕ, которое через блок 16 ключей поступает на шину данных ШД2, Сигнал 31 сбрасьгеает триггер 20 готовности, вследствие чего микроЭВМ выходит из состояния ОЖИДАНИЕ, принимает значение байта данных и обрабатывает его в соответствии с кодом команды. Таким образом, в аккумуляторе отлаживаемой микроЭВМ будет записана требуемая информация, значение которой определяется вторым бай50

тате установки триггером 17 сигнала 49 Блокировка памяти за счет подачи на D-вход триггера 17 через порт С регистра 13 сигнала 36 Блокировка памяти с уровнем О, Таким образом, реализуется этап загрузки отлаживаемых программ в память.

Следующий этап прогона программ осуществляется либо в непрерывном ре- g жиме, либо по шагам. Требуемый режим работы определяется состоянием порта С регистра 13 данных и задания режимов, запись информации в который производится по сигналу 32 записи данША2, Память разблокируется в резуль

тате установки триггером 17 сигнала 49 Блокировка памяти за счет подачи на D-вход триггера 17 через порт С регистра 13 сигнала 36 Блокировка памяти с уровнем О, Таким образом, реализуется этап загрузки отлаживаемых программ в память.

Следующий этап прогона программ осуществляется либо в непрерывном ре- жиме, либо по шагам. Требуемый режим работы определяется состоянием порта С регистра 13 данных и задания режимов, запись информации в который производится по сигналу 32 записи данHbix в регистр 13, Во всех перечисленных режимах внутренний управляющий сигнал 36, поступаютоий на D-вход триггера 17 блокировки памяти и сигнал 39, поступающий на D-вход триггера 18 сброса обеспечивают сигналы Блокировка памяти 49 и Сброс 50 уровня О. В случае непрерьтно- го режима работы в порте С регистра 13 устанавливается в состояние О Оигналы 38,40,42 и 43 в результате ч(его с выхода элемента ИЛИ 11 на li-вход триггера 20 готовности посту10

входов элемента ИЛИ им выходом соединен гера 20 готовности. пает управляющий си начала такта. Таким личии в щестом или де Щ 2 1,по пере нала 44 триггер- 30 52 Готовность, На диться адрес внешне на гад2 данные ВВОДА ние ШУ2 осуществляе В и С регистра 3 по

порт А регистра 11 ние регистра 13,

20

25

35

г|ает О информируется единичный сиг- is сигнала 33, ПЩ2 Нал 52 ШУ2 Готовность,

При работе в режиме выполнения отваживаемой программы по шагам уста- йавливается в единичное состояние Сигнал 40, который через элемент ИЛИ 11 поступает на D-вход триггера 20, На С-вход поступает сигнал 44 Начало команды, В результате фop fиpyeтcя сигнал 52 Готовность j. Йосле чего по сигналу 32 Чтение регистра 1 производится считывание байта состояния микроЭВМ, записанного в регистр 1, затем кода команды, находящегося на ПЩ2, через порт А регистра 13 и чтение адреса ОМУ через порты В и С регистра 3, Выборка указанных регистров осуществляется ; управляющими сигналами 35 и 33,

Функционирование устройства в режиме прогона рабочих программ с остановом определяется установкой в единичное состояние следующих сиг- ; налов: -38 - задание режима Останов по адресу, 42 - задание режима Ос- танов по прерьгааниям и 43 - задание режима Останов по командам ВВОД и ВЫВОД,

При отладке рабочих программ с остановом по командам ВВОД и ВЫВОД управляющий сигнал 43 поступает на первьй вход элемента И 12, Второй вход элемента И 12 соединен с выходом элемента ИЛИ 8, на два входа которого подаются соответственно шестой и четвертый разряды ШД2, Привязка к данным разрядам необходима для определения машинных циклов ВВОД и ВЫВОД, Единичное состояние шестого разряда ШУ2, при наличии стробирую- щего сигнала-44 - Начало команды, определяет цикл ВВОД, аналогичным образом четвертый разряд ШД2 определяет цикл ВЫВОД, Выход элемента И 12 поступает на один из четьфех

При отладке рабо танов по прерьгаания стра 13 устанавлива единичное состояние нал 42i, который пос вход элемента И7, Н поступает нулевой р ным состоянием кото стробирующего сигна манды и определяем НИЕ ПРЕРЫВАНИЯ, Вы связан с одним из ч 30 мента ИЛИ 11, котор соединен с D-входом товности. На тактов 20 поступает сигнал ды. Таким образом тавит сигнал 52 Го в случае появления ПОДТВЕРЖДЕНИЕ ПРЕР будет находиться ад лаживаемую программ обработки прерьюани команды EST, опред прерываний, Считьге производится так ж ВВОД и ВЫВОД,

При отладке раб жиме Останов по а переходит в состоя отлаживаемая прогр рез заданный адрес мое количество цик 29 - запись в реги и В регистра 6 зап танова, в порт С р чество циклов повт данного режима осу новкой в порте С р ничное состояние у ла 38, который пос вход элемента И 13

40

45

50

55

входов элемента ИЛИ 11, который своим выходом соединен с В-входом триггера 20 готовности. На С-вход поступает управляющий сигнал 44 - признак начала такта. Таким образом, при наличии в щестом или четвертом разряде Щ 2 1,по переднему фронту сигнала 44 триггер- 30 выставляет сигнал 52 Готовность, На Ш2 будет находиться адрес внешнего устройства, на гад2 данные ВВОДА или ВЫВОДА, Чтение ШУ2 осуществляется через порты В и С регистра 3 подачей управляющепорт А регистра 11 ние регистра 13,

сигнала 33, ПЩ2

считывается через по сигналу 35 чте0

5

5

При отладке рабочих программ Останов по прерьгааниям в порте С регистра 13 устанавливается в активное единичное состояние управляющий сигнал 42i, который поступает на первый вход элемента И7, На второй вход поступает нулевой разряд ЩЦ2, единичным состоянием которого при наличии стробирующего сигнала 44 Начало ко- манды и определяем цикл ПОДТВЕРЖДЕНИЕ ПРЕРЫВАНИЯ, Выход элемента И., связан с одним из четырех входов эле- 0 мента ИЛИ 11, который своим выходом соединен с D-входом триггера 20 готовности. На тактовый вход триггера 20 поступает сигнал 44 Начало команды. Таким образом, триггер 20 выставит сигнал 52 Готовность только в случае появления машинного цикла ПОДТВЕРЖДЕНИЕ ПРЕРЫВАНИЯ, На 1ЧУ2 будет находиться адрес возврата в отлаживаемую программу по завершению обработки прерьюаний, на иЩ2 - код команды EST, определяющий вектор прерываний, Считьгеание шин микроЭВМ производится так же как и в цикле ВВОД и ВЫВОД,

При отладке рабочих программ в режиме Останов по адресу, микроЭВМ переходит в состояние ожидания,когда отлаживаемая программа проходит че- рез заданный адрес останова требуемое количество циклов. По сигналу 29 - запись в регистр 6, в порты А и В регистра 6 записывается адрес останова, в порт С регистра 6 - количество циклов повторений. Задание данного режима осуществляется--установкой в порте С регистра 5 3 в единичное состояние управляющего сигнала 38, который поступает на первый вход элемента И 13, Запись числа цик0

5

0

55

лов повторений в счетчик 10, работающий в режиме вычитания, осуществляется путем установки в состояние 1 сигнала 37, формируемого портом С регистра 13. При работе в данном режиме, схема 9 сравнения осуществляет сравнение адреса останова, записанного в портах А и В регистра 6 с текзпцим значением ЦА2. В случае совпадения этих адресов схема 9 вырабатывает сигнал равенства. Выход схемы 9 соединен со счетным входом вычитания счетчика 10, Когда значение счетчика 10 станет нулевым, т,е, программа пройдет заданное количество циклов, формируется сигнал переноса, который поступает на второй вход элемента И 14, Выход элемента И 14 соединен с одним из четырех входов элемента ИЛИ 11, а выход элемента ИЛИ 11 связан с D-входом триггера 20 готовности. Таким образом, на О входе триггера 20 появится 1 при условии нулевого значения счетчика 10 повторений. Триггер 20 готовности формирует сигнал 52 Готовность по переднему фронту сигнала 44, идущего на С-вход. Процессор отлаживаемого устройства перейдет в состояние ожидания. На D1A2 будет находиться адрес останова на 1ЦД2, соответствующие этому адресу данные. Считывание шин мйк- роЭВМ производится так же, как и в ,предьщущих режимах работы с остановом. Кроме того, работа устройства по шагам или с остановом организована с формирсгванием запроса прерывания в отладочную микроЭВМ, Для этой цели введен триггер 15 прерьюаний. Установка триггера в активное состояние производится сигналом 52 Готовность, поступающим на. С-вход,Запрос прерьдаания снимается по сигналу 34, поступающего на Е-вход триггера 15, Работа по прерьгааниям необходима для организации оптимального использования программного обеспечения отладочной микроэвм. Помимо формирования запроса прерывания на выполнение программы управляющей мик- роЭВМ устройство может формировать сигнал 51 Запрос прерывания, поступающий в отлаживаемую микроЭВМ, Для этой цели служит триггер 19.На1 -вход поступает управляющий сигнал 41, который устанавливается в состояние 1 через соответствующий разряд порта С регистра 13. На С-вход триггера

19 принимается тактовая частота 47. Снимается запрос прерывания подачей на П-вход триггера 19 нулевого сигнала 41 по переднему фронту тактовой частоты 47, Применение триггера 19 в схеме формирования сигнала 51 Запроса прерьгоания необходимо для того, чтобы асинхронный сигнал 41,сфор10 мированный в порте С регистра 13,был приведен к временной диаграмме работы отлаживаемой микроЭВМ. Для этой же цели используется триггер 18,который позволяет синхронизировать сиг15 нал 50 - Сброс,

Формула изобретения

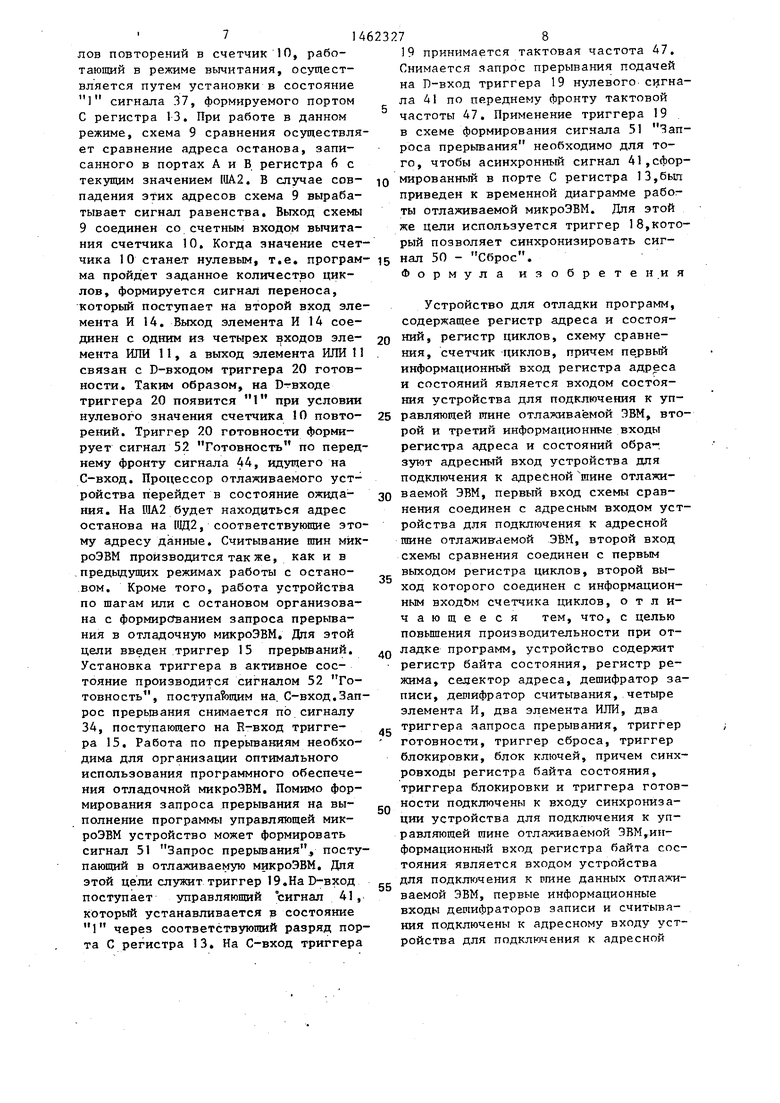

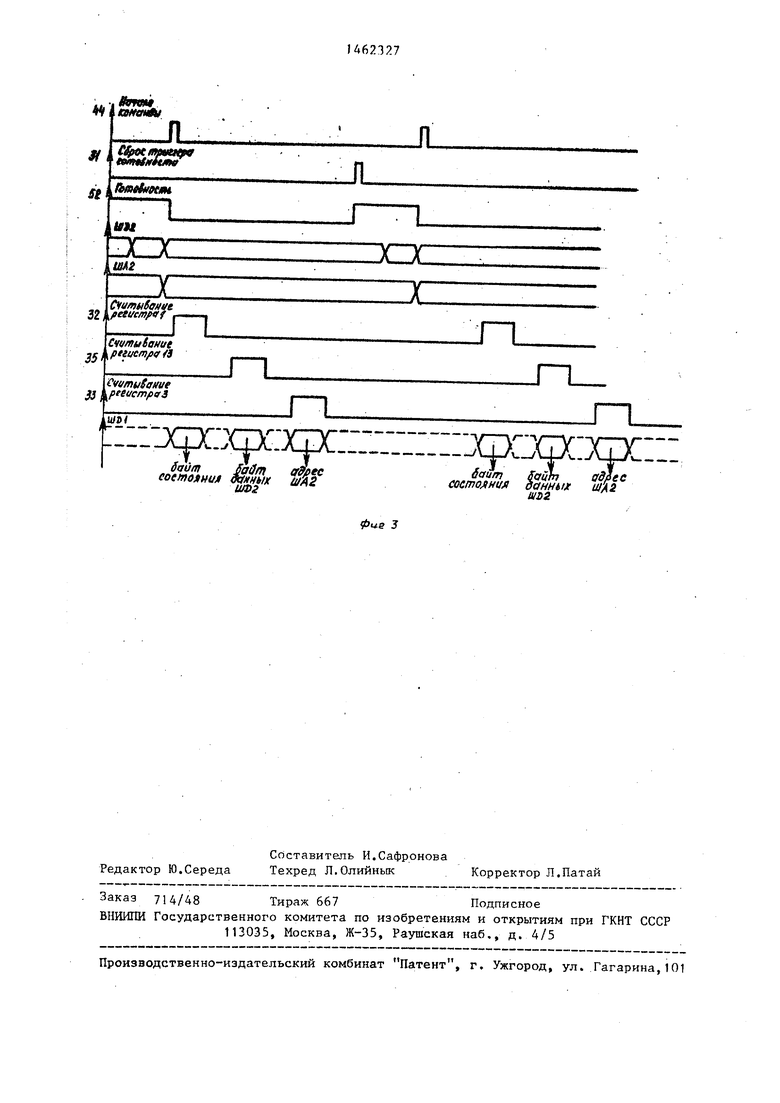

Устройство для отладки программ, содержащее регистр адреса и состоя20 НИИ, регистр циклов, схему сравнения, счетчик циклов, причем пе.рвый информационный вход регистра адреса и состояний является входом состояния устройства для подключения к уп25 равляющей иине отлаживаемой ЭВМ, второй и третий информационные входы регистра адреса и состояний обра-, зуит адресный вход устройства для подключения к адресной шине отлажи30 ваемой ЭВМ, первый вход схемы сравнения соединен с адресным входом устройства для подключения к адресной шине отлажинаемой ЭВМ, второй вход схемы сравнения соединен с первым выходом регистра циклов, второй выход которого соединен с информационным вход&м счетчика циклов, отличающееся тем, что, с целью повьшения производительности при отдд ладке программ, устройство содержит регистр байта состояния, регистр режима, селектор адреса, дешифратор записи, дешифратор считывания, четыре элемента И, два элемента ИЛИ, два триггера запроса прерывания, триггер готовности, триггер сброса, триггер блокировки, блок ключей, причем синх- ровходы регистра байта состояния, триггера блокировки и триггера готовности подключены к входу синхронизации устройства для подключения к управляющей шине отлаживаемой ЭВМ,ии- формационный вход регистра байта состояния является входом устройства для подключения к иине данных отлаживаемой ЭВМ, первые информационные входы дешифраторов записи и считывания подключены к адресному входу устройства для подключения к адресной

35

50

55

шине отладочной ЭВМ, входы разрешения дешифраторов -записи и считывания являются входами записи и чтения устройства для подключения к управляющей шине отладочной ЭВМ, выходы дешифратора считывания с первого по четвертый подключены соответственно (к входу чтения регистра байта состояния, входу чтения регистра адреса и состояния, входу установки в О I первого триггера запроса прерьшания, I входу чтения регистра режима, выхо- : ды дешифратора записи с первого по четвертый соединены соответственно .: с входами записи регистра адреса и ; состояния регистра циклов, регистра : режима и входом установки в О триг гера готовности, выход селектора ад- i раса подключен с вторым информацион- I ным входам дешифраторов записи и j считывания, информационный вход се- лектора адреса является адресным I входом устройства для подключения к I адресной шине отладочной ЭВМ, адрес- I ный вход, селектора адреса является i входом задания режима устройства,пер 1 вьй информационный вход разрешения ; и второй информационный входы регистра режима являются соответственно адресным входом устройства для подключения к адресной шине отладочной ЭВМ и информационным входом устройства для подключения к шине данных отладочной ЭВМ, первая группа выходов регистра режима соединена с группой информационных входов блока ... ключей, разрядные выходы второй группы выходов регистра режима подключены к информационным входам триггеров блокировки сброса запроса прерывания, установочному входу счетчика циклов, первым входам первого и второго элементов И и первого элемента ИЛИ и первому входу третьего элемента И, второй вход которого соединен с выходом второго элемента ИЛИ, первый и второй входы которого и второй вход второго элемента И образуют группу информационных входов

5

0

устройства для подключения к шине данных отлаживаемой ЭВМ, синхровхо- ды триггеров сброса и запроса прерывания подключены к тактовому входу устройства для подключения к управляющей шине отлаживаемой ЭВМ, выход схемы сравнения соединен с вьмитаю- щим входом счетчика циклов, выход которого соединен с вторым входом первого элемента И, выход которого соединен с вторым входом первого элемента ИЛИ, третий и четвертый входы которого .соединены соответственно с выходами второго и третьего элементов И, выход первого элемента ИЛИ соединен с информационным входом триггера .готовности, прямые выходы триггеров ,блокировки сброса, готовности и инверсный выход второго триггера запроса прерывания являются выходами устройства для подключения к управляющей шине отлаживаемой ЭВМ, прямой выход триггера готовности сое- 5 динен с синхровходом первого триггера запроса прерывания, входы приема и блокировки блока ключей являются входами устройства для подключения к управляющей шине отлаживаемой ЭВМ, выход блока ключей является выходом устройства для подключения к шине данньрс отлаживаемой ЭВМ, прямой выход первого триггера запроса прерывания является выходом устройства для подключения к управляющей шине отладочной ЭВМ, входы разрешения регистров адреса и состояний циклов и режима являются адресным входом устройства для подключения к адресной пгане отла- .- дочной ЭВМ, четвертый информационньш вход-выход регистра адреса и состояния является входом-выходом устройства для подключения к шине данных отладочной ЭВМ, информационный вход- выход регистра циклов является входом-выходом устройства для подключения к щине данных отладочной ЭВМ, выход регистра байта состояния является выходом устройства для подключе- ния к шине данных отладочной ЭВМ,

vjU

0

5

45

Фие.2

jsnucisejy

ша- ки1аеыоа fii/xfffXH

«. ч evfwt.

iOftOH

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для отладки программ | 1985 |

|

SU1297064A1 |

| Устройство для отладки программ | 1987 |

|

SU1425685A1 |

| Устройство для отладки микроЭВМ | 1989 |

|

SU1677708A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1247877A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство для отладки микроЭВМ | 1987 |

|

SU1553981A1 |

| Устройство для отладки программно-аппаратных блоков | 1983 |

|

SU1242965A1 |

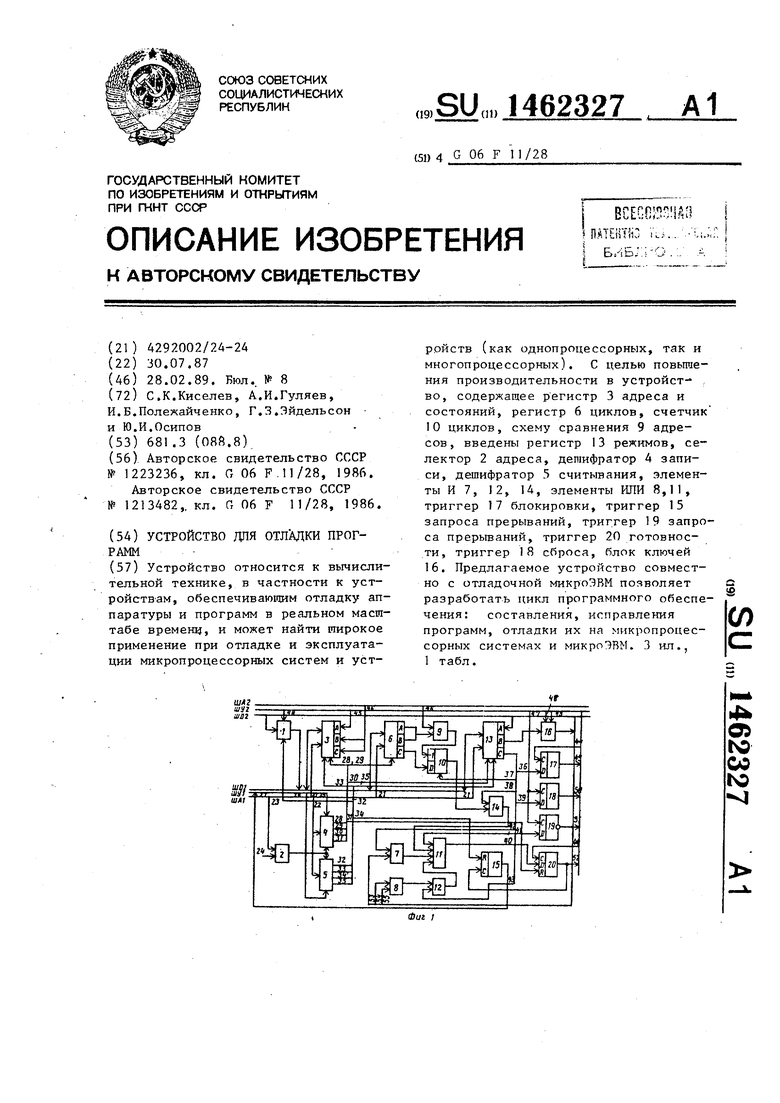

Устройство относится к вычислительной технике, в частности к устройствам, обеспечиваюним отладку аппаратуры и программ в реальном масштабе временц, и может найти широкое применение при отладке и эксплуатации микропроцессорных систем и устррйств (как однопроцессорных, так и многопроцессорных). С целью повышения производительности в устройство, содержащее регистр 3 адреса и состояний, регистр 6 циклов, счетчик 10 циклов, схему сравнения 9 адресов, введены регистр 13 режимов, селектор 2 адреса, дешифратор 4 записи, дешифратор 3 считывания, элементы И 7, 12, 14, элементы ИЛИ 8,11, триггер 17 блокировки, триггер 15 запроса прерываний, триггер 19 запроса прерываний, триггер 20 готовности, триггер 18 сброса, блок ключей 16, Предлагаемое устройство совместно с отладочной микроЭВМ позволяет разработать цикл программного обеспечения: составления, исправления программ, отладки их на микропроцессорных системах и микроЭВМ. 3 ил., 1 табл. с /)

СО(ШЛНи &Tf, I

состояния Ьаннчх Ж/

| Устройство для отладки программ | 1984 |

|

SU1223236A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для отладки программ | 1984 |

|

SU1213482A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-02-28—Публикация

1987-07-30—Подача