Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микросхем оперативной памяти | 1983 |

|

SU1149312A1 |

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Устройство для управления динамической памятью | 1987 |

|

SU1524089A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1705875A1 |

| Устройство для считывания и отображения видеоинформации | 1988 |

|

SU1817116A1 |

| Устройство для контроля блоков оперативной памяти | 1986 |

|

SU1336123A1 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705874A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| Устройство управления динамической памятью | 1990 |

|

SU1735858A1 |

| Устройство для обработки видеоинформации | 1988 |

|

SU1640714A1 |

Изобретение относится к вычислительной технике и может быть использовано для функционального контроля оперативных запоминающих устройств (ОЗУ). Цель изобретения - повышение достоверности контроля, Устройство содержит ОЗУ 1, первый счетчик 2. первый элемент И 3, мультиплексор 4, коммутатор 5, анализатор 6 кодов, генератор 7 импульсов, второй счетчик 8, блок 10 памяти, первый элемент 12 задс.-рж- ки, второй элемент 14 задержки, триггер 15, второй элемент И16, первый и второй элементы И17 и 18с инверсией. Возможность тестирования динамических ОЗУ во всех основных режимах работы, а именно в режиме считывания и записи, в режиме считывание - модификация - запись и в страничных режимах считывания и записи повышает полноту контроля и расширяет область применения устройства.4 ил,

Xf

О

ел

00

VI

OJ

Изобретение относится к области вычислительной техники и может быть использовано для функционального контроля оперативных запоминающих устройств

(ОЗУ),

Цель изобретения - повышение достоверности контроля.

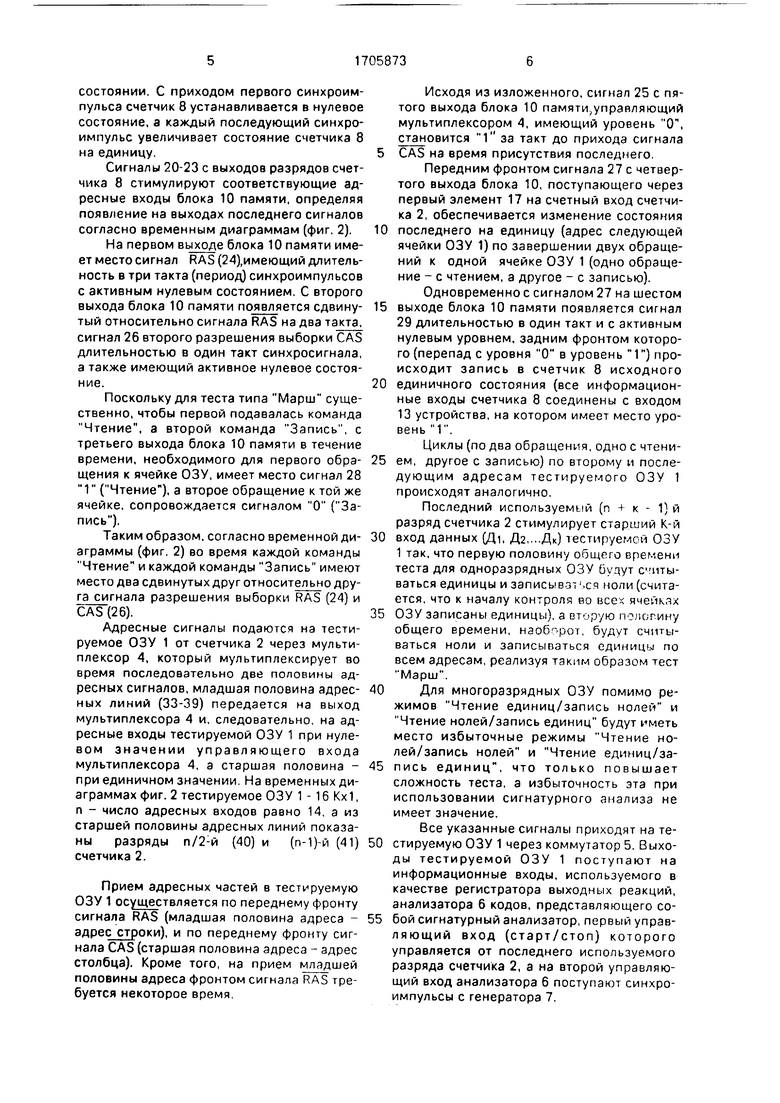

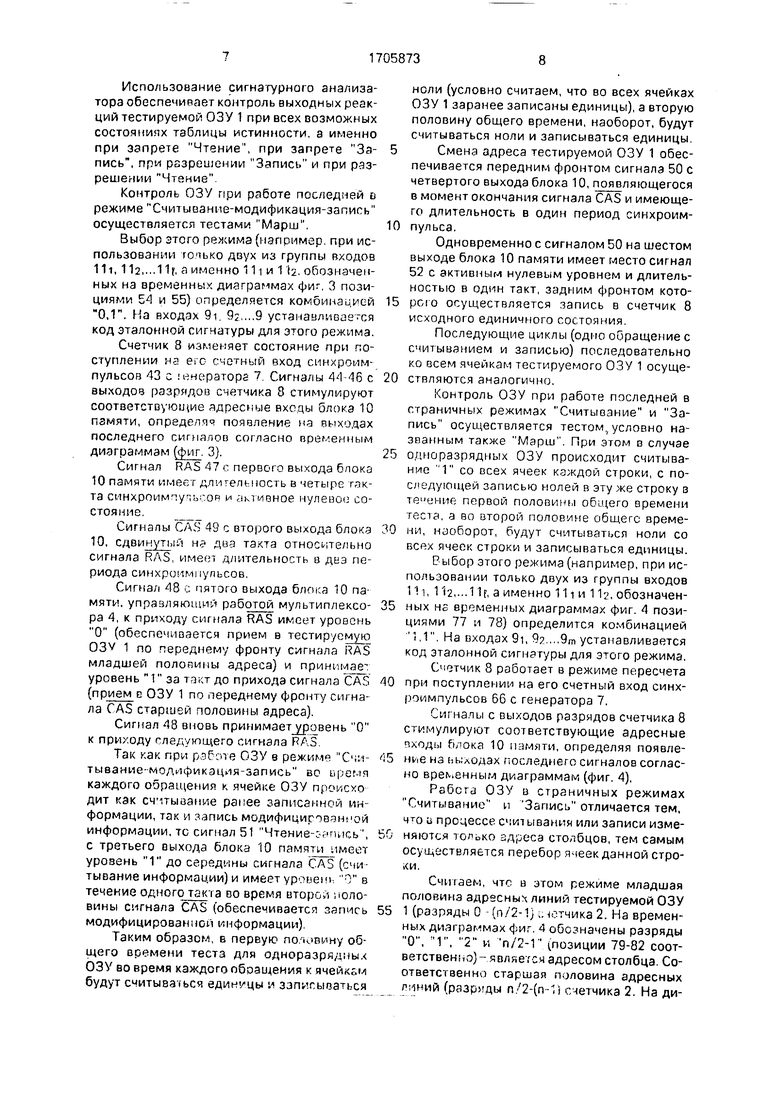

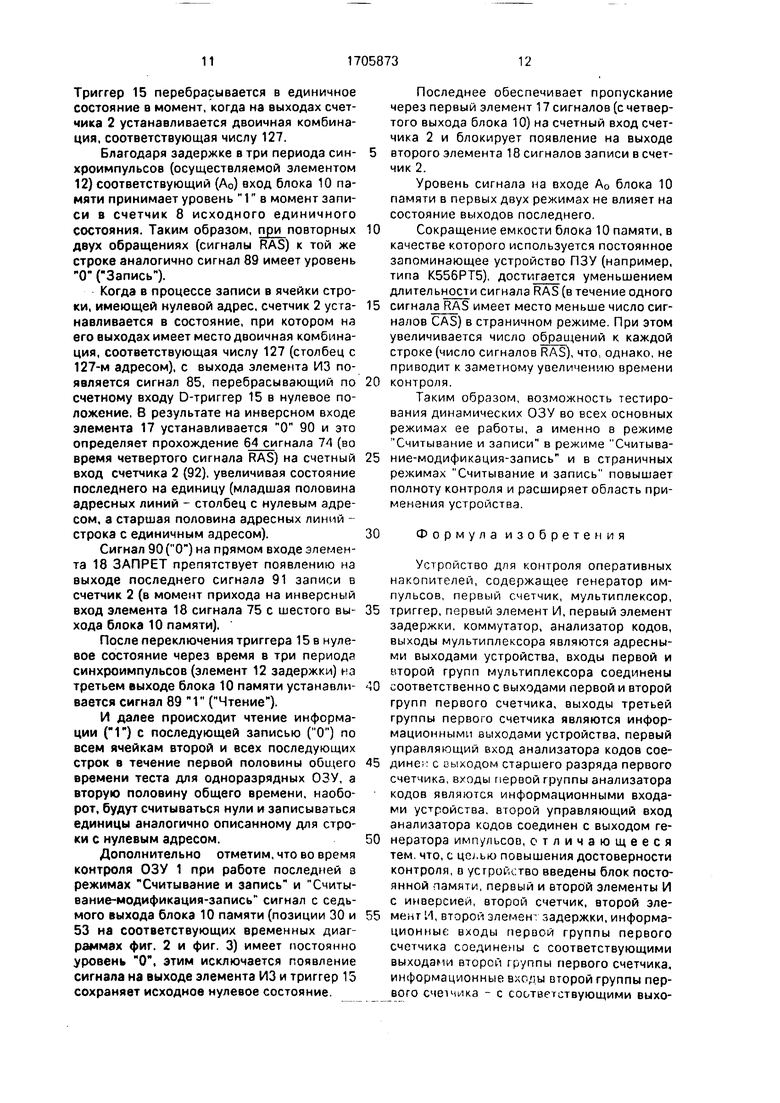

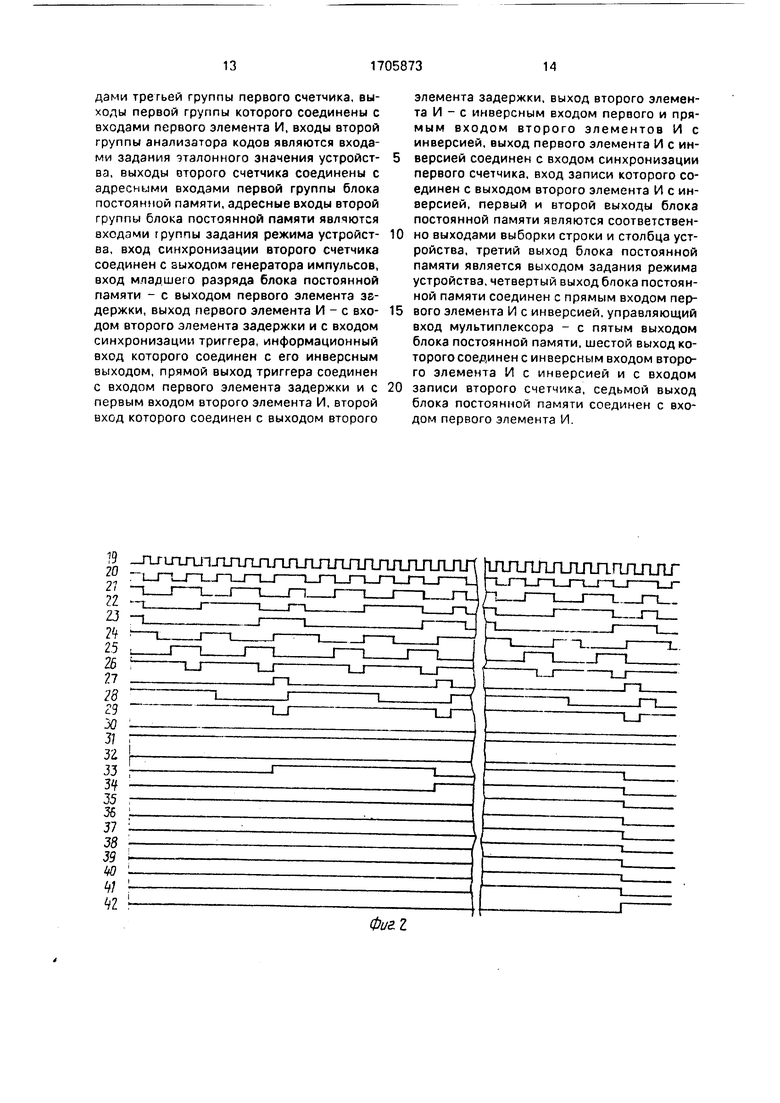

На фиг.1 приведена структурная схема устройства; на фиг, 2 - временные диаграммы работы устройства для контроля ОЗУ в режиме Считывание и Запись ; на фиг. 3 - временные диаграммы работы устройства при контроле ОЗУ в режиме Считывание-модификация-запись ; на фиг. 4 - временные диаграммы работы устройства при контроле ОЗУ в страничных режимах Считывание и Запись.

Устройство подключается к тестируемому ОЗУ 1 и содержит первый счетчик 2, первый элемент ИЗ, мультиплексор 4, коммутатор 5, представляющий интерфейсную коммутационную матрицу, анализатор 6 кодов, в качестве которого может быть использован сигнатурный анализатор,генератор 7 импульсов, второй счетчик 8, первую группу входов 9i, 92,... 9m устройства, блок 10 постоянной памяти, в качестве которого может быть использовано постоянное запоминающее устройство (ПЗУ), вторую группу входов 11i, 112....11fустройства, первый элемент 1Ј задержки, вход 13 устройства, второй элемент 14 задержки D-триггер 15, второй элемент И1б, первый элемент И17 с инверсией, второй элемент И18 с инверсией.

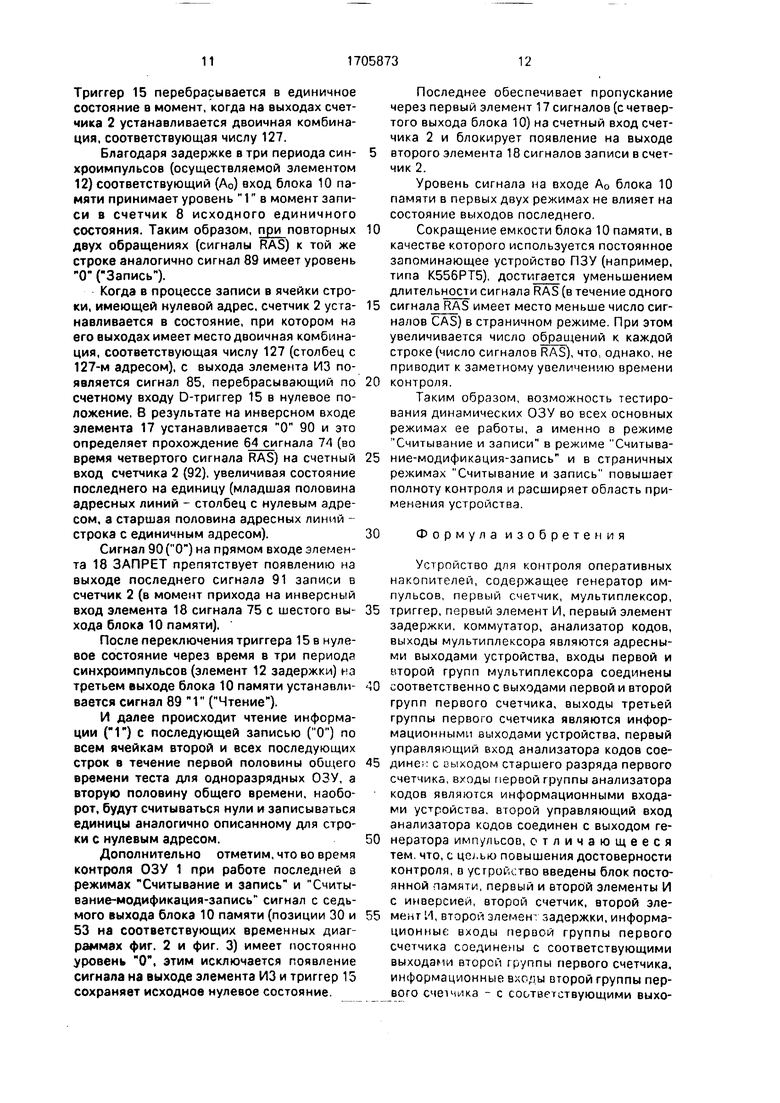

На временной диаграмме (фиг. 2) обозначены импульсы 19 генератора 7, разряд О(20) счетчика 8, разряд 1 (21) счетчика 8, разряд 2 (22) счетчика 8. разряд 3 (22) счетчика 8, сигнал RAS 24 с первого выхода блока 10 памяти, сигнал 25 управления мультиплексора 4 на входе X (пятый выход блока 10), сигнал CAS 26 с второго выхода блока 10, сигнал 27 на счетном входе счетчика 2, сигнал Чтение/запись (28) на третьем выходе блока 10 памяти, сигнал Запись (29) на входе записи счетчика 8, сигнал 30 с седьмого выхода блока 10, сигналы с выходов 11i и 112 устройства обозначены позициями 31 и 32, разряды с О по 6 счетчика 2 обозначены позициями 33-39, разряды 7 и 13 счетчика 2 обозначены позициями 40 и 41, разряд 14 (42)счетчика 2 (стимулирует информационный вход тестируемой ОЗУ 1).

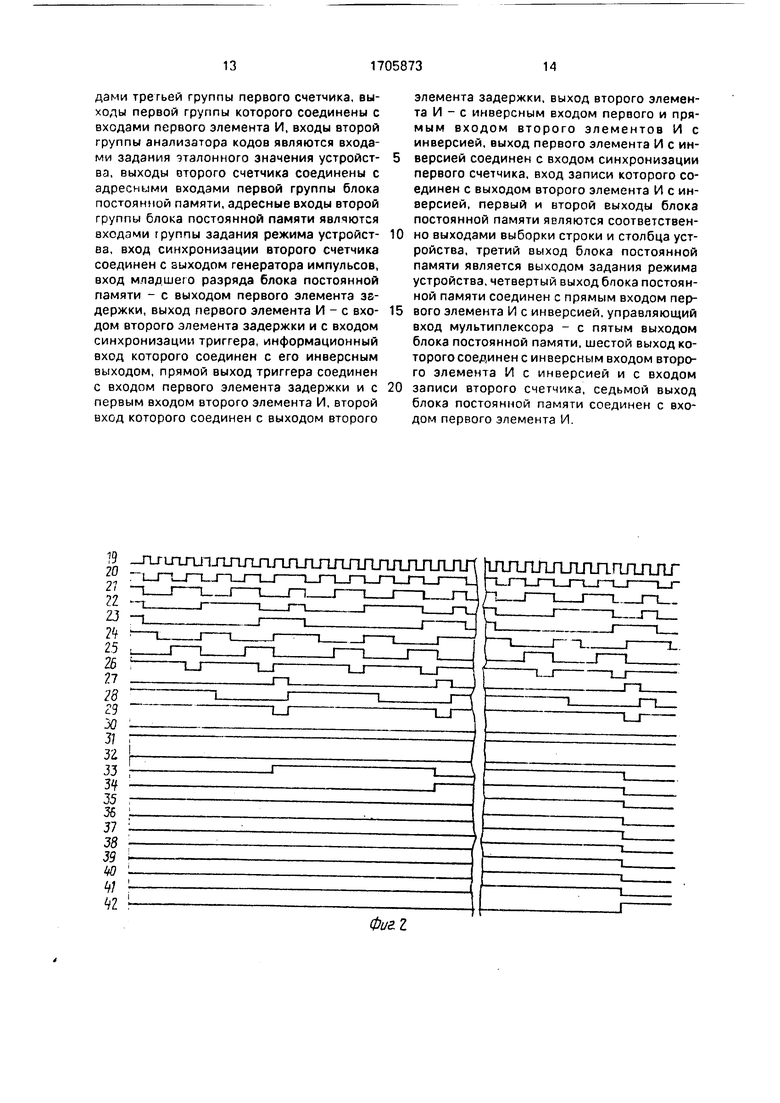

На временной диаграмме (фиг. 3) обозначены импульсы 43 генератора 7, разряды с О по 2 счетчика 8 обозначены позициями 44-46, сигнал RAS 47 с первого выхода блока 10 памяти, сигнал 48 управления

мультиплексора 4 на входе X, сигнал CAS 49 с второго выхода блока 10, сигнал 50 на счетном входе счетчика 2, сигнал Чтение/запись 51 на третьем выходе блока 10,

сигнал Запись 52 на входе записи счетчика 8, сигнал 53 с седьмого выхода блока 10, сигналы с входов 111 и 112 устройства обозначены позициями 54 и 55, разряды с О по 6 счетчика 2 обозначены позициями 56-62,

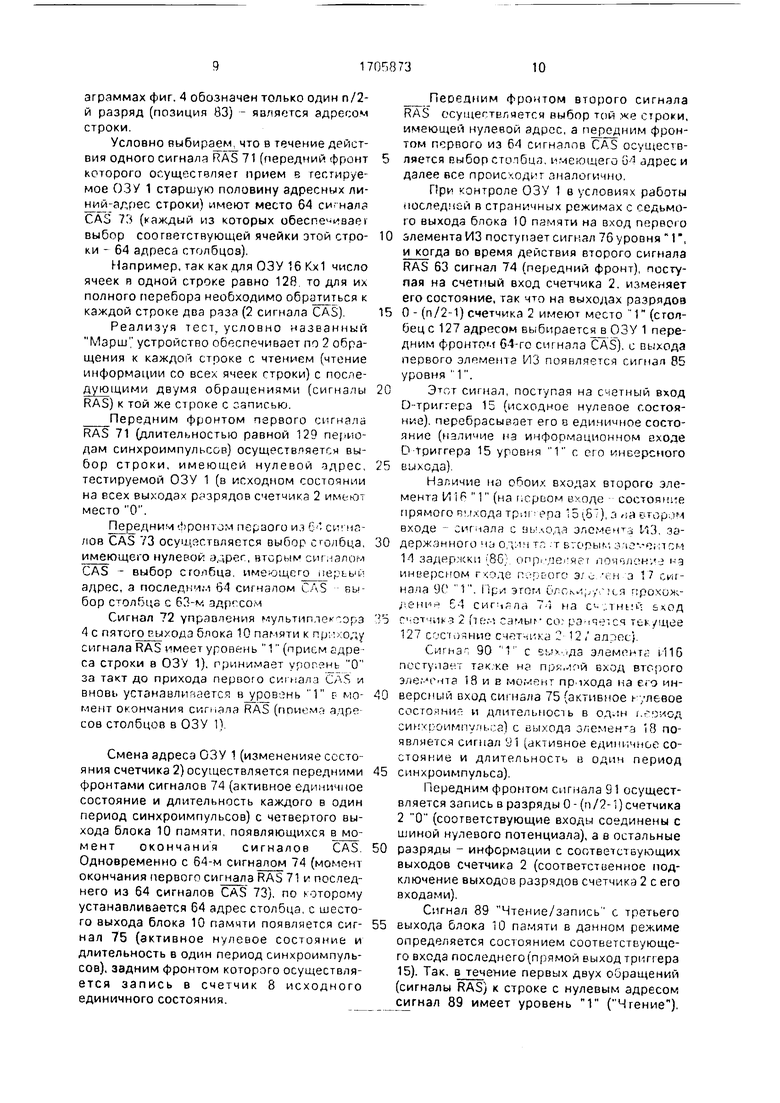

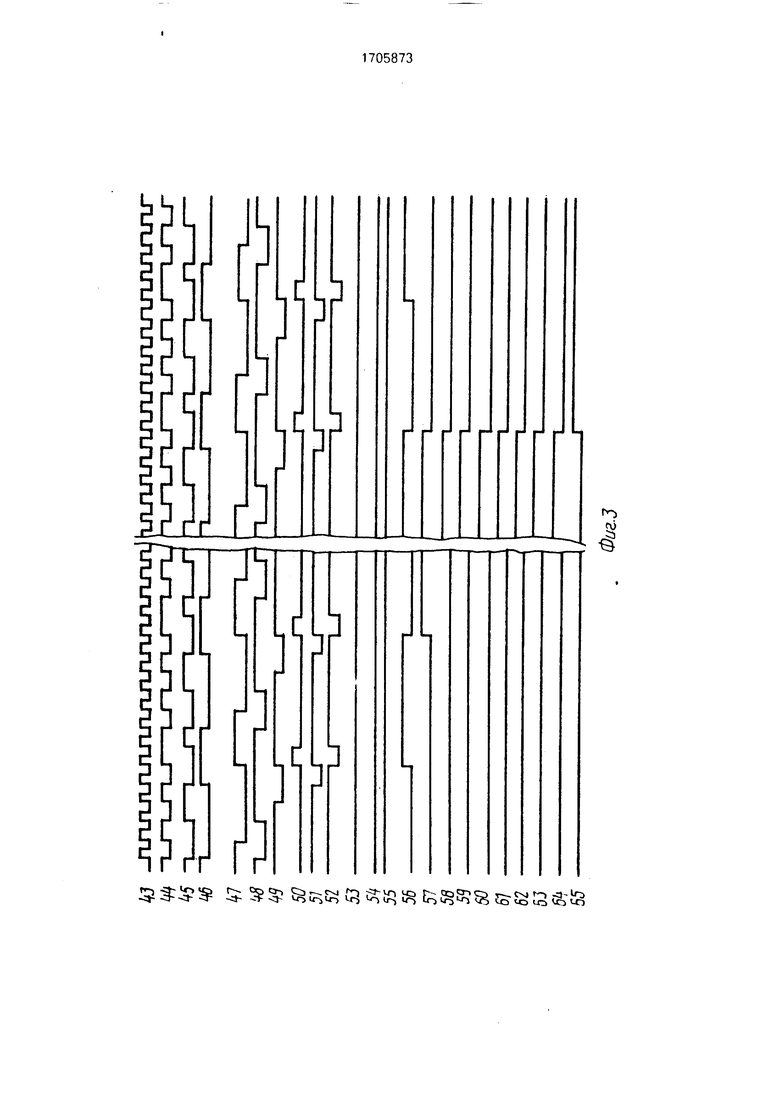

разряды 7 и 13 счетчика 2 обозначены позициями 63 и 64, разряд 14 65 счетчика 2, На временной диаграмме (фиг. 4) обозначены импульсы 66 генератора 7, разряды О, 1, 2 и 7 счетчика 8. обозначенные

позициями 67-70, сигнал RAS 71 с первого выхода блока 10, сигнал 72 управления мультиплексора 4 на входе X, сигнал CAS 73 с второго выхода блока 10, сигнал 74 с четвертого выхода блока 10, сигнал Запись 75

на входе записи счетчика 8, сигнал 76 с седьмого выхода блока 10, сигналы с входов 111 и 112 устройства обозначены позициями 77 и 78, разряды О, 1, 2, и 6 счетчика 2 обозначены позициями 79-82, разряд 7

(83) счетчика 2, разряд 14(84)счетчика 2, сигнал 85 с выхода элемента ИЗ, сигнал 86 с выхода элемента 14 задержки, сигнал 87 с прямого выхода D-триггера 15, сигнал 88 с выхода элемента 12 задержки, сигнал Чтение/запись (89) на третьем выходе блока 10, сигнал 90 с выхода элемента И 16, сигнал 91 на выходе записи счетчика 2, сигнал 92 на счетном входе счетчика 2.

Устройство обеспечивает контроль ОЗУ

при работе последней в режимах Считывание и запись, Считывание-мидификация- запись и Страничные считывание и запись следующим образом.

Режим работы ОЗУ, при котором осуществляется ее контроль, определяется кодовой комбинацией, устанавливаемой на входах 11i, 112,...11t устройства. На входах 9i, 92,...9m устройства устанавливается кодовая комбинация эталонной сигнатуры

контроля для выбранного режима работы ОЗУ.

Контроль ОЗУ при работе последней в режимах Считывание и запись осуществляется реализацией теста Марш.

Выбор этого режима (например, при использовании только дьух из групп входов 111, 1l2,...11f. а именно 11т и 112, обозначенных на временных диаграммах фиг. 2, позициями 31 и 32) определяется комбинацией

1,0.

Генератор 7 формирует синхроимпульсы 19, которые поступают на счетный вход второго двоичного счетчика 8, работающего в режиме пересчета. К началу работы все

разряды счетчика 8 находятся в единичном

состоянии. С приходом первого синхроимпульса счетчик 8 устанавливается в нулевое состояние, а каждый последующий синхроимпульс увеличивает состояние счетчика 8 на единицу.

Сигналы 20-23 с выходов разрядов счетчика 8 стимулируют соответствующие адресные входы блока 10 памяти, определяя появление на выходах последнего сигналов согласно временным диаграммам (фиг. 2).

На первом выходе блока 10 памяти имеет место сигнал RAS (24),имеющий длительность в три такта (период) синхроимпульсов с активным нулевым состоянием. С второго выхода блока 10 памяти появляется сдвинутый относительно сигнала RAS на два такта, сигнал 26 второго разрешения выборки CAS длительностью в один такт синхросигнала, а также имеющий активное нулевое состояние.

Поскольку для теста типа Марш существенно, чтобы первой подавалась команда Чтение, а второй команда Запись, с третьего выхода блока 10 памяти в течение времени, необходимого для первого обращения к ячейке ОЗУ, имеет место сигнал 28 1 (Чтение), а второе обращение к той же ячейке, сопровождается сигналом О (Запись),

Таким образом, согласно временной диаграммы (фиг. 2) во время каждой команды Чтение и каждой команды Запись имеют место два сдвинутых друг относительно друга сигнала разрешения выборки RAS (24) и CAS(26).

Адресные сигналы подаются на тестируемое ОЗУ 1 от счетчика 2 через мультиплексор 4, который мультиплексирует во время последовательно две половины адресных сигналов, младшая половина адресных линий (33-39) передается на выход мультиплексора 4 и, следовательно, на адресные входы тестируемой ОЗУ 1 при нулевом значении управляющего входа мультиплексора 4, а старшая половина - при единичном значении. На временных диаграммах фиг. 2 тестируемое ОЗУ 1-16 Кх1, п - число адресных входов равно 14, а из старшей половины адресных линий показаны разряды п/2:й (40) и (п-1)-й (41) счетчика 2.

Прием адресных частей в тестируемую ОЗУ 1 осуществляется по переднему фронту сигнала RAS (младшая половина адреса - адрес строки), и по переднему фронту сигнала CAS (старшая половина адреса - адрес столбца). Кроме того, на прием младшей половины адреса фронтом сигнала RAS требуется некоторое время.

Исходя из изложенного, сигнал 25 с пятого выхода блока 10 памяти управляющий мультиплексором 4, имеющий уровень О, становится 1 за такт до прихода сигнала

CAS на время присутствия последнего.

Передним фронтом сигнала 27с четвертого выхода блока 10, поступающего через первый элемент 17 на счетный вход счетчика 2, обеспечивается изменение состояния

0 последнего на единицу (адрес следующей ячейки ОЗУ 1) по завершении двух обращений к одной ячейке ОЗУ 1 (одно обращение - с чтением, а другое - с записью). Одновременно с сигналом 27 на шестом

5 выходе блока 10 памяти появляется сигнал 29 длительностью в один такт и с активным нулевым уровнем, задним фронтом которого (перепад с уровня О в уровень 1) происходит запись в счетчик 8 исходного

0 единичного состояния (все информационные входы счетчика 8 соединены с входом 13 устройства, на котором имеет место уровень 1.

Циклы (по два обращения, одно с чтени5 ем, другое с записью) по второму и последующим адресам тестируемого ОЗУ 1 происходят аналогично.

Последний используемый (п + к - 1) и разряд счетчика 2 стимулирует старший К-й

0 вход данных {Дт, Д2,...ДК) тестируемой ОЗУ 1 так, что первую половину общего времени теста для одноразрядных ОЗУ будут считываться единицы и записываться ноли (считается, что к началу контроля во всех ячейках

5 ОЗУ записаны единицы), а вторую пологину общего времени, наоборот, будут считываться ноли и записываться единицы по всем адресам, реализуя таким образом тест Марш.

0 Для многоразрядных ОЗУ помимо режимов Чтение единиц/запись нолей и Чтение нолей/запись единиц будут иметь место избыточные режимы Чтение нолей/запись нолей и Чтение единиц/за5 пись единиц, что только повышает сложность теста, а избыточность эта при использовании сигнатурного анализа не имеет значение.

Все указанные сигналы приходят на те0 стируемую ОЗУ 1 через коммутатор 5. Выходы тестируемой ОЗУ 1 поступают на информационные входы, используемого в качестве регистратора выходных реакций, анализатора 6 кодов, представляющего со5 бой сигнатурный анализатор, первый управ- ляющий вход (старт/стоп) которого управляется от последнего используемого разряда счетчика 2, а на второй управляющий вход анализатора 6 поступают синхроимпульсы с генератора 7.

Использование сигнатурного анализатора обеспечивает контроль выходных реакций тестируемой ОЗУ 1 при всех возможных состояниях таблицы истинности, а именно при запрете Чтение, при запрете Запись, при разрешении Запись и при разрешении Чтение.

Контроль ОЗУ при работе последней в режиме Считывзние-модификация-запись осуществляется тестами Марш,

Выбор этого режима (например, при использовании только двух из группы входов 11i, 112,...11f, а именно 111 и 1 2. обозначенных на временных диаграммах фиг, 3 позициями 54 и 55) определяется комбинацией О,Г. На входах 9i. 9Ј,..,9 устанавливается код эталонной сигнатуры для этого режима.

Счетчик 8 изменяет состояние при поступлении на его счетный вход синхроимпульсов 43 с . енератора 7. Сигналы 44-46 с выходов разрядов счетчика 8 стимулируют соответствующие адресные входы блока 10 памяти, определяв появление на выходах последнего сигналов согласно временным диаграммам (фиг. 3).

Сигнал RAS 47 с первого выхода блока 10 памяти имеет длительность в четыре такта синхроимпульсов и активное нулевое состояние.

Сигналы CAS 49 с второго выхода блока 10, сдвинутый на два такта относительно сигнала RAS, имеет длительность в дна периода синхроимпульсов.

Сигнал 48 с пятого выхода блока 10 памяти, управляющий работой мультиплексора 4, к приходу сигнала RAS имеет уровень О (обеспечивается прием в тестируемую 03V 1 по переднему фронту сигнала RAS младшей половины адреса) и принимает уровень 1 за такт до прихода сигнала CAS (прием в ОЗУ 1 по переднему фронту сигнала CAS старшей половины адреса).

Сигнал 48 вновь принимает у ровень О к приходу следующего сигнала РАЗ.

Так как при работе ОЗУ е режиме Счи- тывание-модификэция-зэпись во время каждого обращения к ячейке ОЗУ происходит как считывание ранее записанной информации, так и запись модифицированной информации, тс сигнал 51 Чтение-запись, с третьего выхода блока 10 памяти имеет уровень 1 до середины сигнала С AS (считывание информации) и имеет уровен -. О в течение одного такта во время второй половины сигнала CAS (обеспечивается запись модифицированной информации),

Таким образом, Б первую половину общего времени теста для одноразрядных ОЗУ во время каждого обращения к ячейкгм будут считываться единицы и записываться

ноли (условно считаем, что во всех ячейках ОЗУ 1 заранее записаны единицы), а вторую половину общего времени, наоборот, будут считываться ноли и записываться единицы.

Смена адреса тестируемой ОЗУ 1 обеспечивается передним фронтом сигнала 50 с четвертого выхода блока 10, появляющегося в момент окончания сигнала CAS и имеющего длительность в один период синхроим0 пульса.

Одновременно с сигналом 50 на шестом выходе блока 10 памяти имеет место сигнал 52 с активным нулевым уровнем и длительностью в один такт, задним фронтом кото5 рсго осуществляется запись в счетчик 8 исходного единичного состояния.

Последующие циклы (одно обращение с считыванием и записью) последовательно ко всем ячейкам тестируемого ОЗУ 1 осуще0 ствляются аналогично.

Контроль ОЗУ при работе последней в страничных режимах Считывание и Запись осуществляется тестом, условно названным также Марш. При этом в случае

5 одноразрядных ОЗУ происходит считывание 1 со всех ячеек каждой строки, с последующей записью нолей в эту же строку в течение первой половины общего времени теста, а во второй половине общего време0 ни, наоборот, будут считываться ноли со всех ячеек строки и записываться единицы. Выбор этого режима (например, при использовании только двух из группы входов Hi, 1 i2,...11f, а именно 111 и 11, обозначен5 ных на временных диаграммах фиг. 4 позициями 77 и 78) определится комбинацией 1,1, На входах 9i, 92,...9m устанавливается код эталонной сигнатуры для этого режима. Счетчик 8 работает в режиме пересчета

0 при поступлении на его счетный вход синхроимпульсов 66 с генератора 7.

Сигналы с выходов разрядов счетчика 8 стимулируют соответствующие адресные входы блока 10 памяти, определяя появле5 ние на ьыходах последнего сигналов согласно временным диаграммам (фиг. 4),

Работа ОЗУ в страничных режимах Считывание и Запись отличается тем, что а процессе считывания или записи изме0 няются только адреса столбцов, тем самым осуществляется перебор ячеек данной строки.

Считаем, что в этом режиме младшая половина адресных линий тестируемой ОЗУ

5 1 (разряды 0 -(п/2-1) летчика 2. На временных диаграммах фиг. 4 обозначены разряды О, 1, 2 и п/2-1 (позиции 79-82 соответственно)-является адресом столбца. Соответственно старшая половина адресных линий (разряды n/2-(n-Vi счетчика 2. На диаграммах фиг. 4 обозначен только один п/2- й разряд (позиция 83) - является адресом строки.

Условно выбира ем что в течение действия одного сигнала RAS 71 (передний фронт которого осуществляет прием в тестируемое ОЗУ 1 старшую половину адресных ли- ний-адрес строки) имеют место 64 сигнала CAS 73 (каждый из которых обеспечивавi выбор соответствующей ячейки этой строки - 64 адреса столбцов).

Например, так как для ОЗУ 16 Кх1 число ячеек в одной строке равно 128. то для их полного перебора необходимо обратиться к каждой строке два раза (2 сигнала CAS).

Реализуя тест, условно названный Марш , устройство обеспечивает по 2 обращения к каждой строке с чтением (чтение информации со всех ячеек строки) с последующими двумя обращениями (сигналы RAS) к той же строке с записью. Передним фронтом первого сигнала RAS 71 (длительностью равной 129 периодам синхроимпульсов) осуществляется выбор строки, имеющей нулевой адрес, тестируемой ОЗУ 1 (в исходном состоянии на всех выходах разрядов счетчика 2 имеют место О.

Де р едним фронтом первого из С-- сигналов CAS 73 осуществляется выбор столбца, имеющего нулевой эдрег, вторым сигналом CAS - выбор столбца, имеющего первый адрес, а последним 64 сигналом CAS -- выбор столбца с 63-м адресом

Сигнал 72 упраоления мультиплексора 4 с пятого выхода блока 10 памяти к приходу сигнала RAS имеет уровень 1 (прием адреса строки в ОЗУ 1), принимает уропень О за такт до прихода первого сигнала CAS и вновь устанавливается в уровйнь 1 г момент окончания сигнала RAS (приема адресов столбцов в ОЗУ 1).

Смена адреса ОЗУ 1 (измененияе состояния счетчика 2) осуществляется передними фронтами сигналов 74 (активное единичное состояние и длительность каждого в один период синхроимпульсов) с четвертого выхода блока 10 памяти, появляющихся в мо- мент окончания сигналов CAS. Одновременно с 64-м сигналом 74 (момент окончания первого сигнала RAS 71 и последнего из 64 сигналов CAS 73), по которому устанавливается 64 адрес столбца, с шестого выхода блока 10 памяти появляется сигнал 75 (активное нулевое состояние и длительность в один период синхроимпульсов), задним фронтом которого осуществляется запись в счетчик 8 исходного единичного состояния.

Передним Фронтом второго сигнала RAS осуществляется выбор той же строки, имеющей нулевой адрес, а передним фронтом первого из 64 сигналов CAS осуществляется выбор столбца, имеющего G- l адрес и далее все происходит аналогично.

При контроле ОЗУ 1 в условиях работы последней в страничных режимах с седьмого выхода блока 10 памяти на вход первого

0 элемента ИЗ поступает сигнал 76 уровня 1, и когда во время действия второго сигнала RAS 63 сигнал 74 (передний фронт), поступая на счетный вход счетчика 2. изменяет его состояние, так что на выходах разрядов

5 0 - (п/2-1) счетчика 2 имеют место 1 (столбец с 127 адресом выбирается ОЗУ 1 передним фронтом 64-го сигнала CAS), с выхода первого элемента ИЗ появляется сигнал 85 уровня 1.

0Этот сигнал, поступая на счетный вход D-триггерэ 15 (исходное нулевое состояние), перебрасывает его в единичное состояние (наличие на информационном входе D-триггера 15 уровня 1 с его инверсного

5 выхода).

Наличие на обоих входах второго элемента И16 1 (на первом входе состояние прямого выхода триггера 15 (87), а на втором входе - сигнала с аы.ода элемента ИЗ, зэ0 держанного на один т .т в т о рым зче-.-естсм 14 задержки (86). определяет лочолени-э ua инверсном г ходе первого э.гс ч:н а 17 сигнала 90 1. При этом ,-уг м.я прохождение 64 7ч на с.лннй вход

5 счзтчик-з 2 (тем самыг со; рэмчется темщее 127 состояние счетчика 212/ адрес}.

Сигнап 90 1;1 с БЫ.ХОДЭ элементе: И16 поступает также на пря.лой вход второго 18 и в момент прохода на его ин0 версный вход сигнала 75 (активное кулевое состояние и длительность в один г.г-оиод синхроимпульса) с выхода элемента 18 появляется сигнал 91 (активное единичное состояние и длительность в один период

5 синхроимпульса).

Передним фронтом сигнала 91 осуществляется запись в разряды 0- (п/2-1)счетчика 2 О (соответствующие входы соединены с шиной нулевого потенциала), а в остальные

0 разряды - информации с соответствующих выходов счетчика 2 (соответственное подключение выходов разрядов счетчика 2 с его входами).

Сигнал 89 Чтение/запись с третьего

5 выхода блока 10 памяти в данном режиме определяется состоянием соответствующего входа последнего (прямой выход триггера 15). Так. в течение первых двух обращений (сигналы RAS) к строке с нулевым адресом сигнал 89 имеет уровень 1 (Чтение).

Триггер 15 перебрасывается в единичное состояние в момент, когда на выходах счетчика 2 устанавливается двоичная комбинация, соответствующая числу 127.

Благодаря задержке в три периода синхроимпульсов (осуществляемой элементом 12) соответствующий (А0) вход блока 10 памяти принимает уровень 1 в момент записи в счетчик 8 исходного единичного состояния. Таким образом, при повторных двух обращениях (сигналы RAS) к той же строке аналогично сигнал 89 имеет уровень О ( Запись).

Когда в процессе записи в ячейки строки, имеющей нулевой адрес, счетчик 2 устанавливается в состояние, при котором на его выходах имеет место двоичная комбинация, соответствующая числу 127 (столбец с 127-м адресом), с выхода элемента ИЗ появляется сигнал 85, перебрасывающий по счетному входу D-триггер 15 в нулевое положение. В результате на инверсном входе элемента 17 устанавливается О 90 и это определяет прохождение 64 сигнала 74 (во время четвертого сигнала RAS) на счетный вход счетчика 2 (92), увеличивая состояние последнего на единицу (младшая половина адресных линий - столбец с нулевым адресом, а старшая половина адресных линий - строка с единичным адресом).

Сигнал 90 (О) на прямом входе элемента 18 ЗАПРЕТ препятствует появлению на выходе последнего сигнала 91 записи в счетчик 2 (в момент прихода на инверсный вход элемента 18 сигнала 75 с шестого выхода блока 10 памяти).

После переключения триггера 15 в нулевое состояние через время в три периода синхроимпульсов (элемент 12 задержки) на третьем выходе блока 10 памяти устанавливается сигнал 89 1 (Чтение).

И далее происходит чтение информации (1) с последующей записью (О) по всем ячейкам второй и всех последующих строк в течение первой половины общего времени теста для одноразрядных ОЗУ, а вторую половину общего времени, наоборот, будут считываться нули и записываться единицы аналогично описанному для строки с нулевым адресом.

Дополнительно отметим, что во время контроля ОЗУ 1 при работе последней а режимах Считывание и запись и Считы- вание-модификация-запись сигнал с седьмого выхода блока 10 памяти (позиции 30 и 53 на соответствующих временных диаграммах фиг. 2 и фиг. 3) имеет постоянно уровень О, этим исключается появление сигнала на выходе элемента ИЗ и триггер 15 сохраняет исходное нулевое состояние.

й

Последнее обеспечивает пропускание через первый элемент 17 сигналов (с четвертого выхода блока 10) на счетный вход счетчика 2 и блокирует появление на выходе 5 второго элемента 18 сигналов записи в счетчик 2.

Уровень сигнала на входе А0 блока 10 памяти в первых двух режимах не влияет на состояние выходов последнего. 10 Сокращение емкости блока 10 памяти, в качестве которого используется постоянное запоминающее устройство ПЗУ (например, типа К556РТ5), достигается уменьшением длительности сигнала RAS (в течение одного 15 сигнала RAS имеет место меньше число сигналов CAS) в страничном режиме. При этом увеличивается число обращений к каждой строке (число сигналов RAS), что, однако, не приводит к заметному увеличению времени 20 контроля.

Таким образом, возможность тестирования динамических ОЗУ во всех основных режимах ее работы, а именно в режиме Считывание и записи в режиме Считыва- 25 ние-модификация-запись и в страничных режимах Считывание и запись повышает полноту контроля и расширяет область применения устройства.

30 Формула изобретения

Устройство для контроля оперативных накопителей, содержащее генератор импульсов, первый счетчик, мультиплексор,

триггер, первый элемент И, первый элемент задержки, коммутатор, анализатор кодов, выходы мультиплексора являются адресными выходами устройства, входы первой и «торой групп мультиплексора соединены

соответственно с выходами первой и второй групп первого счетчика, выходы третьей группы первого счетчика являются информационными выходами устройства, первый управляющий вход анализатора кодов соедине;: с выходом старшего разряда первого счетчика, входы первой группы анализатора кодов являются информационными входами устройства, второй управляющий вход анализатора кодов соединен с выходом генератора импульсов, отличающееся тем, что, с целью повышения достоверности контроля, в устройство введены блок постоянной памяти, первый и второй элементы И с инверсией, второй счетчик, второй элемент И, второй элемент задержки, информа- ционные входы первой группы первого счетчика соединены с соответствующими выходами второй группы первого счетчика, информационные входы второй группы первого счетчика - с соответствующими выходами третьей группы первого счетчика, выходы первой группы которого соединены с входами первого элемента И, входы второй группы анализатора кодов являются входами задания эталонного значения устройства, выходы второго счетчика соединены с адресными входами первой группы блока постоянной памяти, адресные входы второй группы блока постоянной памяти являются входами группы задания режима устройства, вход синхронизации второго счетчика соединен с выходом генератора импульсов, вход младшего разряда блока постоянной памяти - с выходом первого элемента задержки, выход первого элемента И - с входом второго элемента задержки и с входом синхронизации триггера, информационный вход которого соединен с его инверсным выходом, прямой выход триггера соединен с входом первого элемента задержки и с первым входом второго элемента И, второй вход которого соединен с выходом второго

-jTj-LrLmnjinjTjTTLTLminJTJT

элемента задержки, выход второго элемента И - с инверсным входом первого и прямым входом второго элементов И с инверсией, выход первого элемента И с инверсией соединен с входом синхронизации первого счетчика, вход записи которого соединен с выходом второго элемента И с инверсией, первый и второй выходы блока постоянной памяти являются соответственно выходами выборки строки и столбца устройства, третий выход блока постоянной памяти является выходом задания режима устройства, четвертый выход бпока постоянной памяти соединен с прямым входом первого элемента И с инверсией, управляющий вход мультиплексора - с пятым выходом блока постоянной памяти, шестой выход которого соединен с инверсным входом второго элемента И с инверсией и с входом

записи второго счетчика, седьмой выход блока постоянной памяти соединен с входом первого элемента И.

гшллг

Фиг. Z

t

i

5

fD 3:lC tr 9T Гп -о г-- оарлсэ

--Э--Э-- - -- J OU-iU- lrJL :Slr Ji : U-)

±T

-ч-1) to UD LO Чэ to

| Устройство для контроля полупроводниковой памяти | 1978 |

|

SU749887A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1992-01-15—Публикация

1989-05-16—Подача