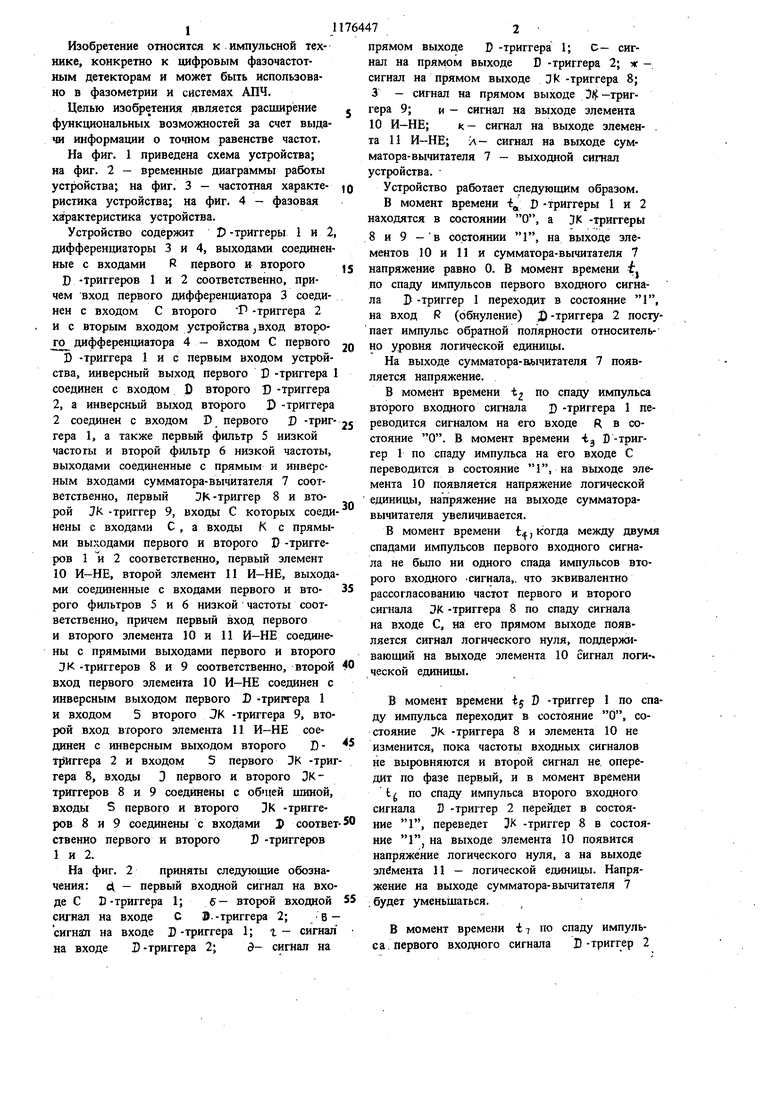

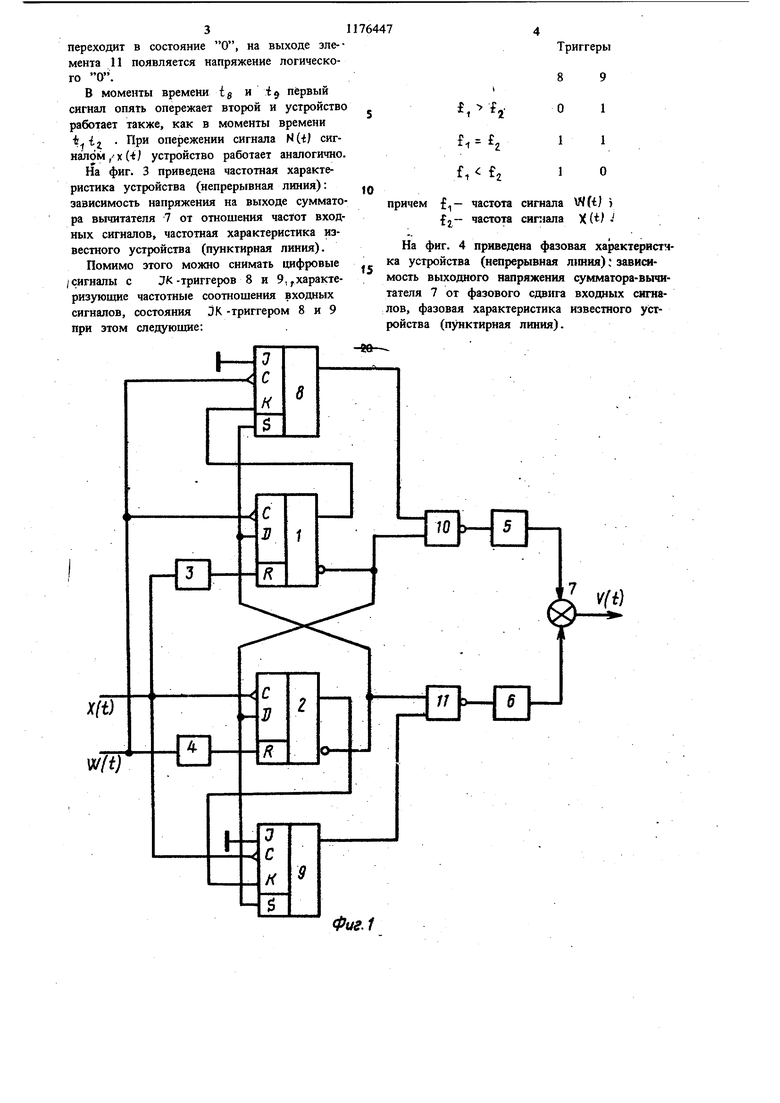

11 Изобретение относится к импульсной технике, конкретно к цифровым фазочастотным детекторам и может быть использовано в фазометрии и системах АПЧ. Целью изобретения является расширение функциональных возможностей за счет выдачи информации о точном равенстве частот. На фиг. 1 приведена схема устройства; на фиг. 2 - временные диаграммы работы устройства; на фиг, 3 - частотная характеристика устройства; на фиг. 4 - фазовая характеристика устройства. Устройство содержит D-триггеры 1 и 2, дифференциаторы 3 и 4, выходами соединенные с входами R первого и второго D -триггеров 1 и 2 соответственно, причем вход первого дифференциатора 3 соединен с входом С второго Т -триггера 2 и с вторым входом устройства, вход вторюго дифференциатора 4 - входом С первого D -триггера 1 и с первым входом устройства, инверсный выход первого D -триггера 1 соединен с входом D второго D -триггера 2, а инверсный выход второго D -триггера 2 соединен с входом D первого D -триггера 1, а также первый фильтр 5 низкой частогы и второй фильтр 6 низкой частоты, выходами соединенные с прямым и инверсным входами сумматора-вычитателя 7 соответственно, первый К-триггер 8 и второй Jk -триггер 9, входы С которых соеди нены с входами С , а входы К с прямыми выходами первого и второго D -триггеров 1 и 2 соответственно, первый элемент 10 И-НЕ, второй злемент 11 И-НЕ, выхода ми соединенные с входами первого и второго фильтров 5 и 6 низкой частоты соответственно, причем первый вход первого и второго элемента 10 и 11 И-НЕ соединены с прямыми выходами первого и второго ЭК -триггеров 8 и 9 соответственно, второй вход первого элемента 10 И-НЕ соединен с инверсным выходом первого D -триггера 1 и входом 5 второго JK -триггера 9, второй вход второго элемента И И-НЕ соединен с инверсным выходом второго Dтриггера 2 и входом S первого ЗК -триг гера 8, входа D первого и второго ЗКтриггеров 8 и 9 соединены с общей шиной, входы S первого и второго DK -триггеров 8 и 9 соединены с входами D соответ ственно первого и второго D -триггеров На фиг. 2 приняты следующие обозначения: 4 - первый входной сигнал на входе С D-триггера 1; 5- второй входной сигнал на входе С В--триггера 2; . Б - снгнал на входе Л-триггера 1; г - сигнал на входе В -триггера 2; Э- сигнал на 7 D -триггера 1; с- сигпрямом выходе нал на прямом выходе D -триггера 2; ж -. сигнал на прямом выходе ЗК-триггера 8; 3 - сигнал на прямом выходе Э) -триггера 9; и - сигнал на выходе элемента 10 И-НЕ; (с- сигнал на выходе злемен- . та 11 И-НЕ; л- сигнал на выходе сумматора-вычитателя 7 - выходной сигнал устройства. Устройство работает следующим образом. В момент времени i 0 -триггеры 1 и 2 находятся в состоянии О, а JK -триггеры 8 и 9 -в состоянии 1, на выходе злементов 10 и 11 и сумматора-вычитателя 7 напряжение равно 0. В момент времени t напряжение равно 0. В момент времени fj по спаду импульсов первого входного сигнала В-триггер 1 переходит в состояние 1, на вход R (обнуление) Д) -триггера 2 поступает импульс обратной полярности относитель„Q уровня логической единицы. На выходе сумматора-вычитателя 7 появляется напряжение. В момент времени t по спаду импульса второго входного сигнала D -триггера 1 переводится сигналом на его входе R в состояние О. В момент времени i D-триггер 1 по спаду импульса на его входе С переводится в состояние 1, на выходе элемента 10 появляется напряжение логической единицы, напряжение на выходе сумматоравычитателя увеличивается. В момент времени t, когда между двумя спадами импульсов первого входного сигнала не было ни одного спада импульсов второго входного Сигнала,, что эквивалентно рассогласованию частот первого и второго сигнала JK -триггера 8 по спаду сигнала на входе С, на его прямом выходе появляется сигнал логического нуля, поддерживающий на выходе элемента 10 сигнал логи-. единиш,. В момент времени 5 -триггер 1 по спаду импульса переходит в состояние О, состояние JK -триггера 8 и элемента 10 не изменится, пока частоты входных сигналов не выровняются и второй сигнал не. опередит по фазе первый, и в момент времени t по спаду импульса второго входного сигнала Б -триггер 2 перейдет в состояние 1, переведет JK -триггер 8 в состояние 1, на выходе элемента 10 появится напряжение логического нуля, а на выходе элемента 11 - логической ещшицы. Напряжение на выходе сумматора-вычитателя 7 будет уменьшаться В момент времени i по спаду импульса, первого входного сигнала D-триггер 2

переходит в состояние О, иа выходе эле-мента 11 появляется напряжение логического О.

В моменты времени ig и i первый сигнал опять опережает второй и устройство работает также, как в моменты времени . При опережении сигнала N(-tJ сигналом/x(-t устройство работает аналогично.

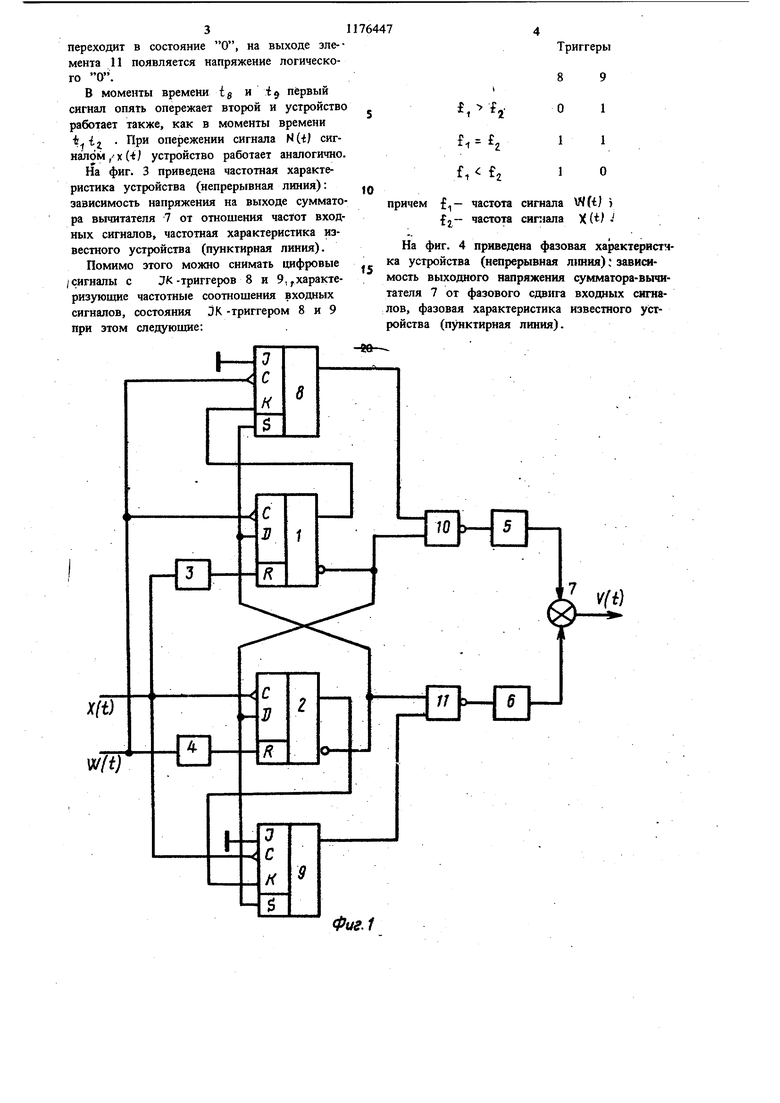

На фиг. 3 приведена частотная характеристика устройства (непрерывиая линия): зависимость напряжения на выходе сумматора вычитателя -7 от отношения частот входных сигналов, частотная характеристика известного устройства (пунктирная линия).

Помимо этого можно снимать цифровые /сигналы с JK-триггеров 8 и 9,,характеризующие частотные соотношения входных сигналов, состояния JK -триггером 8 и 9 при этом следующие:

Фиг.1

Триггеры

, ft

А 21

О

wrt;

частотасигнала

XWfj- частотасишала

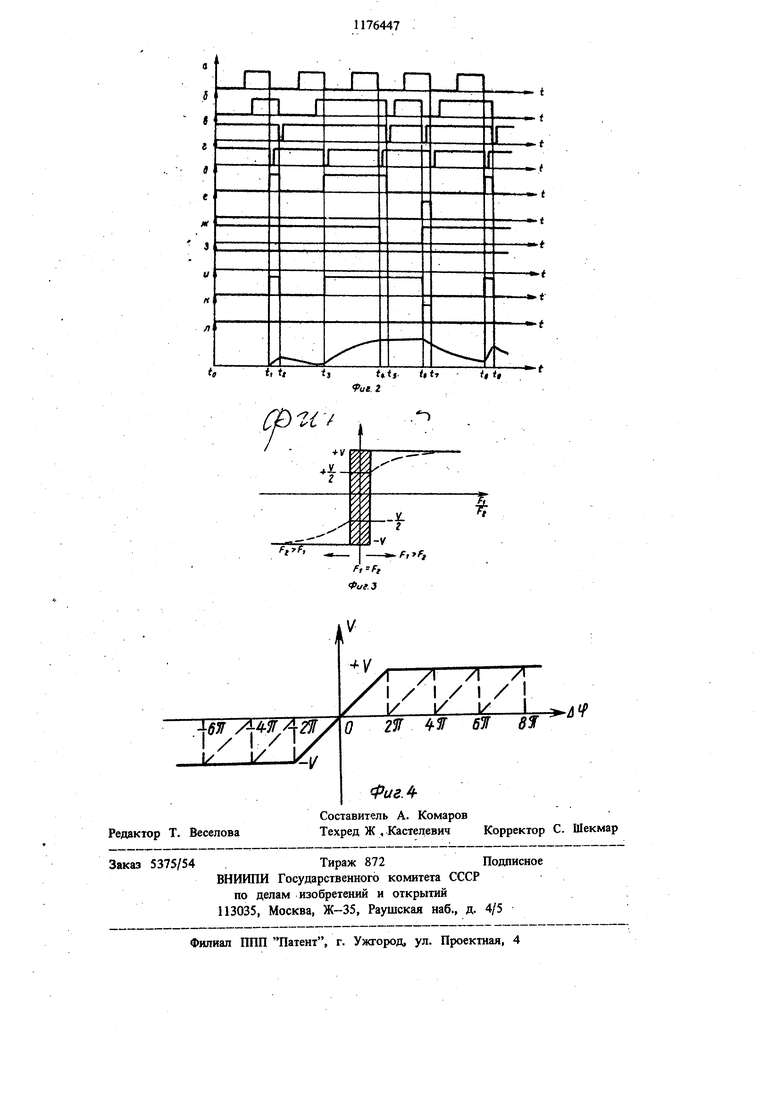

На фиг. 4 приведена фазовая характеристика устройства (непрерывная Л1шия), зависимость выходного напряжения сумматора-вычитателя 7 от фазового сдвета входных сигналов, фазовая характеристика известного устройства (пунктирная линия).

ЕШ

| название | год | авторы | номер документа |

|---|---|---|---|

| ДУБЛИРОВАННАЯ СИСТЕМА С ДИНАМИЧЕСКОЙ ЗАДЕРЖКОЙ | 1999 |

|

RU2153786C1 |

| ПРОЦЕССОР БЫСТРОГО ПРЕОБРАЗОВАНИЯ СИГНАЛОВ ПО УОЛШУ С УПОРЯДОЧЕНИЕМ ПО АДАМАРУ | 1991 |

|

RU2025772C1 |

| ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 2006 |

|

RU2300170C1 |

| СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ВРАЩЕНИЯ ВАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2017156C1 |

| Управляемый делитель частоты с дробным коэффициентом деления | 1989 |

|

SU1677870A1 |

| Устройство для измерения сдвига фаз | 1985 |

|

SU1267284A2 |

| СПОСОБ УПРАВЛЕНИЯ ДУБЛИРОВАННОЙ СИСТЕМОЙ С ЗАДЕРЖКОЙ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1999 |

|

RU2147162C1 |

| Декодер кода линии | 1988 |

|

SU1510094A1 |

| Электронные цифровые весы | 1987 |

|

SU1597591A1 |

| Устройство для регулирования расхода | 1984 |

|

SU1171759A1 |

ЦИФЮВОЙ ФАЗОЧАСТОТНЫЙ ДЕТЕКТОР, содержащий первый и второй Dтриггеры, первый и второй дифференциаторы, выходами соединенные с входами R первого .и второго I) -триггеров соответственно, причем вход первого дифференциатора соединен с входом С второго D -триггера и с вторым входом устройства, вход- второго дифференш1атора - с входом С первого D триггера и с первым входом устройства, инверсный выход первого D -триггера соединен с входом D второго В -триггера, а инверсный выхо); второго В -триггера соединен с входом D первого D -триггера, а также первый и второй фильтры низкой частоты, выходами соединенные с прямым и инверсным входами сумматора-вычитателя соответственно, выход которого соединен с выходом устройства, отличающийс я тем, что, с целью расширения функциональных возможностей за счет выдачи информации о точном равенстве частот, введень1 первый и второй 0 -триггеры, входы С которых соединены с входами С соответственно,, а входы к с прямыми выходами первого и второго Г -триггеров соответственно, первьш и второй элементы И-НЕ, выходами соединенные с входами первого и второго фильтров низкой частоты соответственно, причем первые входы первого и второго элементов И-НЕ соединены с прямыми выходами первого и второго JK (Л триггеров соответственно, второй вход первого элемента И-НЕ с инверсным выходом первого D -триггера, второй вход второго элемента И-НЕ соединен с инверсным выходом второго D -триггера, входы и первого и второго ЭК -триггеров соединены с обшей шиной, входы 5 первого и второго J К -триггеров соединены с входами О) D соответственно первого и второго триг геров. . 4iib sl

F, F,

| Фишел М | |||

| Г | |||

| Простой фазометр на К/МОП ЙС | |||

| - Электроника, 1971, № 9 | |||

| Патент США If 4333055, кл | |||

| Способ переработки сплавов меди и цинка (латуни) | 1922 |

|

SU328A1 |

Авторы

Даты

1985-08-30—Публикация

1984-03-30—Подача