Изобретение относится к автоматике и может быть использовано для построения дискретных устройств повышенной надежности.

Известна схема резервирования логических цепей (см. Г.А. Кейджан. Прогнозирование надежности микроэлектронной аппаратуры на основе БИС-М.: Радио и связь, 1987, с. 131, рис. 5.7), где в качестве анализатора резервируемых логических цепей используется элемент ИЛИ.

Недостатком этого устройства является невозможность определения неисправной логической цепи.

Наиболее близким по своей технической сущности к заявленному устройству является дублированная система с задержкой, описанное в авторском свидетельстве SU N1660231 A 1, 30.06.91 устройство содержит первое и второе резервированные устройства, входы которых объединены и соединены с входной шиной, а выходы соединены соответственно с управляющими входами первого и второго регистров сдвига, выходы которых подключены к первым входам соответственно первого и второго элементов И, выходы которых подключены к первым входам соответственно первого и второго элементов И, выходы которых являются соответствующими входами первого элемента ИЛИ, выход сумматора по модулю два подключен к первому информационному входу первого JK-триггера, вторые информационные входы первого и второго JK-триггеров подключены к корпусной шине, входная шина синхронизации дублированной системы с динамической задержкой соединена с синхронизирующими входами первого и второго JK-триггеров, синхронизирующий вход D-триггера подключен к выходу первого резервированного устройства, а его информационный вход соединен с выходом одновибратора, вход которого подключен к выходу сумматора по модулю два, прямой выход D-триггера соединен со вторым входом третьего элемента И, первый выход блока установки соединен с первыми установочными инверсными входами первого, второго JK-триггеров и D-триггера, вторые установочные инверсные входы которых подключены ко второму выходу блока установки, прямой и инверсный выходы второго JK-триггера соединены соответственно с первыми и вторыми входами элемента ИЛИ-НЕ, инверсный выход которого является выходом сигнализации упомянутой дублированной системы с задержкой, прямой выход первого JK-триггера соединен с первым входом третьего элемента И, выход которого подключен к первому информационному входу второго JK-триггера.

Это устройство по сравнению с описанным аналогом обеспечивает устойчивую работу устройства, выявление неисправного резервируемого устройства, быстрое восстановление работоспособного состояния.

Однако устройство-прототип имеет недостатки:

большое время задержки сигнала на время анализа работоспособности резервируемых устройств, при исправном состоянии этих устройств;

неустойчивую работу дублированной системы с задержкой при поступлении длительной последовательности логических "0".

Целью изобретения является разработка дублированной системы с динамической задержкой, позволяющей уменьшить время задержки передачи цифровой последовательности при исправном состоянии всех элементов дублированной системы с задержкой.

Поставленная цель достигается тем, что в известной дублированной системе с динамической задержкой, содержащей первый и второй резервированные устройства, входы которых объединены и соединены со входной шиной, а выходы соединены соответственно с управляющими входами первого и второго регистров сдвига, выходы которых подключены к первым входам соответственно первого и второго элементов И, выходы которых являются соответствующими входами первого элемента ИЛИ, выход которого является выходом дублированной системы с динамической задержкой, выход сумматора по модулю два подключен к первому информационному входу первого JK-триггера, прямой выход которого соединен с первым входом третьего элемента И, выход которого подключен к первому информационному входу второго JK-триггера, вторые информационные входы первого и второго JK-триггеров подключены к корпусной шине, синхронизирующие входы первого и второго JK-триггеров соединены со входной шиной синхронизации дублированной системы с динамической задержкой, синхронизирующий вход D-триггера подключен к выходу первого резервированного устройства, а его информационный вход соединен с выходом одновибратора, вход которого подключен к выходу сумматора по модулю два, прямой выход D-триггера соединен со вторым входом третьего элемента И, первый выход блока установки соединен с первыми установочными инверсными входами первого, второго JK-триггеров и D-триггера, вторые установочные инверсные входы которых подключены ко второму выходу блока установки, прямой и инверсный выходы второго JK-триггера соединены соответственно с первым и вторым входами элемента ИЛИ-НЕ, инверсный выход которого является выходом сигнализации дублированной системы с динамической задержкой, дополнительно введены четвертый, пятый, шестой, седьмой, восьмой и девятый элементы И, элемент НЕ и второй элемент ИЛИ, причем первый элемент ИЛИ выполнен трехвходовым и его третий вход подключен к выходу девятого элемента И. Выходы первого и второго резервированных устройств подключены к первым входам соответственно второго элемента ИЛИ и четвертого элемента И, выходы которых соединены соответственно с первым и вторым входами сумматора по модулю два. Выход сумматора по модулю два подключен к первым входам пятого, шестого, седьмого и восьмого элементов И. Вторые входы пятого и шестого элементов И подключены соответственно к прямому и инверсному выходам второго JK-триггера, а вторые входы седьмого и восьмого элементов И подключены к входной шине синхронизации дублированной системы с динамической задержкой. Выходы пятого и шестого элементов И соединены со вторыми входами соответственно первого и второго элементов И, а выходы седьмого и восьмого элементов И подключены к входам синхронизации соответственно первого и второго регистров сдвига. Прямой выход первого JK-триггера подключен ко второму входу второго элемента ИЛИ и ко входу элемента НЕ, инверсный выход которого подключен ко вторым входам четвертого и девятого элементов И. Первый вход девятого элемента И подключен к выходу второго резервированного устройства.

Перечисленная новая совокупность существенных признаков позволяет уменьшить время задержки передачи цифровой последовательности за счет введения шести элементов И и одного элемента ИЛИ, что позволяет не проводить анализ работоспособности резервированных устройств при исправном состоянии всех элементов дублированной системы с задержкой, а также исключить ложное срабатывание системы при передаче длинных последовательностей, состоящих из одних логических "0".

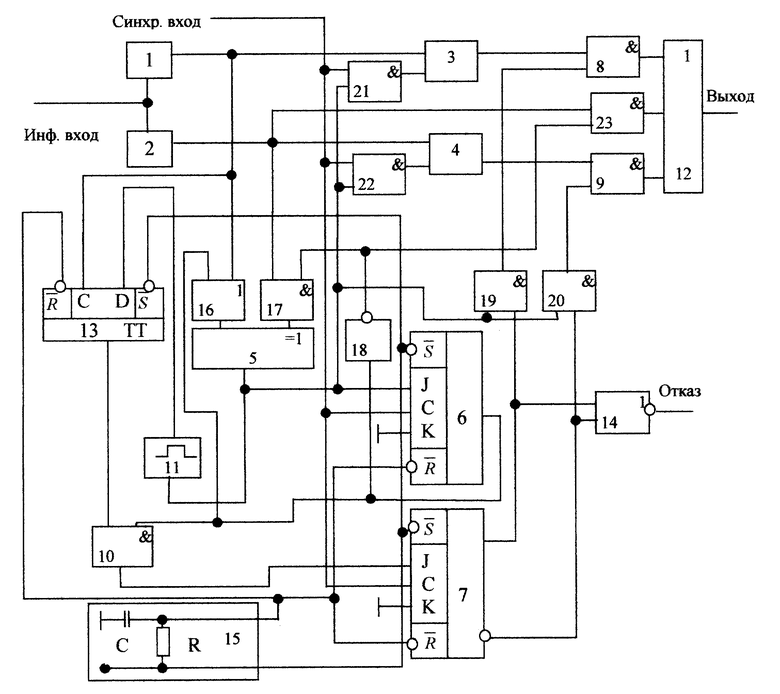

Заявленное устройство, представленное на фиг. 1, состоит из первого 1 и второго 2 резервированного устройства, первого 3 и второго 4 регистров сдвига, сумматора по модулю два 5, первого 6 и второго 7 JK- триггеров, первого 8, второго 9, третьего 10, четвертого 17, пятого 19, шестого 20, седьмого 21, восьмого 22 и девятого 23 элементов И, одновибратора 11, первого элемента ИЛИ 12, D-триггера 13, элемента ИЛИ-НЕ 14, блока установки 15, второго элемента ИЛИ 16, элемента НЕ 18.

Входы первого 1 и второго 2 резервированных устройств объединены и соединены со входной шиной, а выходы соединены соответственно с управляющими входами первого 3 и второго 4 регистров сдвига, выходы которых подключены к первым входам соответственно первого 8 и второго 9 элементов И, выходы которых являются соответствующими входами первого элемента ИЛИ 12, выход которого является выходом дублированной системы с динамической задержкой. Выход сумматора по модулю два 5 подключен к первому информационному входу первого JK-триггера 6, прямой выход которого соединен с первым входом третьего элемента И 10, выход которого подключен к первому информационному входу второго JK-триггера 7. Вторые информационные входы первого 6 и второго 7 JK-триггеров подключены к корпусной шине. Синхронизирующие входы первого 6 и второго 7 JK-триггеров соединены со входной шиной синхронизации дублированной системы с динамической задержкой. Синхронизирующий вход D-триггера 13 подключен к выходу первого резервированного устройства 1, а его информационный вход соединен с выходом одновибратора 11, вход которого подключен к выходу сумматора по модулю два 5. Прямой выход D-триггера 13 соединен со вторым входом третьего элемента И 10. Первый выход блока установки 15 соединен с первыми установочными инверсными входами первого 6, второго 7 JK-триггеров и D-триггера 13, вторые установочные инверсные входы которых подключены ко второму выходу блока установки 15. Прямой и инверсный выходы второго JK-триггера 7 соединены соответственно с первым и вторым входами элемента ИЛИ-НЕ 14, инверсный выход которого является выходом сигнализации дублированной системы с динамической задержкой. Третий вход первого элемента ИЛИ 12 подключен к выходу девятого элемента И 23. Выходы первого 1 и второго 2 резервированных устройств подключены к первым входам соответственно второго элемента ИЛИ 16 и четвертого элемента И 17, выходы которых соединены соответственно с первым и вторым входами сумматора по модулю два 5. Выход сумматора по модулю два 5 подключен к первым входам пятого 19, шестого 20, седьмого 21 и восьмого 22 элементов И. Вторые входы пятого 19 и шестого 20 элементов И подключены соответственно к прямому и инверсному выходам второго JK-триггера 7, а вторые входы седьмого 21 и восьмого 22 элементов И подключены к входной шине синхронизации дублированной системы с динамической задержкой. Выходы пятого 19 и шестого 20 элементов И соединены со вторыми входами соответственно первого 8 и второго 9 элементов И, а выходы седьмого 21 и восьмого 22 элементов И подключены к входам синхронизации соответственно первого 3 и второго 4 регистров сдвига. Прямой выход первого 6 JK-триггера подключен ко второму входу второго элемента ИЛИ 16 и ко входу элемента НЕ 18, инверсный выход которого подключен ко вторым входам четвертого 17 и девятого 23 элементов И. Первый вход девятого элемента И 23 подключен к выходу второго резервированного устройства 2.

Блок установки, показанный на фиг. 1, представляет собой RC-цепочку, в которой первый вывод резистора R соединен с первой обкладкой конденсатора C и является вторым выходом блока установки 15, при этом вторая обкладка конденсатора C соединена с корпусной шиной. Второй вывод резистора R соединен с шиной питания (блок питания не показан) и является первым выходом блока установки 15. Параметры элементов R и C определяются временем задержки, которое зависит от конкретного типа выбранных интегральных микросхем. Порядок выбора времени задержки известен и описан, например, в справочнике В.Л.Шило. Популярные цифровые микросхемы С.13-15.

Схемы одновибраторов известны и описаны, например, в книге: А.С.Партина, В. Г. Борисова Введение в цифровую технику - М.: Радио и связь, 1987, с. 14, рис.13,а. В частности, такая схема может быть реализована на микросхемах серии 155. Используемые в заявленном устройстве сумматор по модулю два, элементы НЕ, ИЛИ, ИЛИ-НЕ, JK-триггеры, D-триггеры, регистры сдвига, трехвходовый элемент ИЛИ известны и описаны, например, в справочнике В.Л.Шило. Популярные цифровые микросхемы: сумматор по модулю 2 - с. 56, рис. 1.34,в и может быть выполнен на микросхеме К155ЛП5; элементы НЕ с. 27, рис. 1.12,а и могут быть выполнены на микросхемах К155ЛН1; элементы ИЛИ - с. 48, рис. 1.27,з и могут быть выполнены на микросхемах К155ЛЛ1; элемент ИЛИ-НЕ - с. 48, рис. 1.27,б и может быть выполнен на микросхемах К155ЛЕ1; JK-триггеры - с. 83, рис. 1.60,в и могут быть выполнены на микросхемах К555ТВ9; D-триггер - с. 76, рис. 1.54 и может быть выполнен на микросхеме К155ТМ2; регистры сдвига - с. 106, рис. 1.75 и могут быть выполнены на микросхемах К155ИР1; трехвходовый элемент ИЛИ - с. 48, рис. 1.27,е и может быть выполнен на микросхемах К155ЛЕ4. Схемы элементов И известны и описаны, например, в книге: Микросхемы и их применение / Батушев В. А. ,. В.Н.Вениаминов, Ковалев В.Г. и др. -М.: Энергия, 1978. С.142 - 147.

Устройство работает следующим образом: при включении питания первый 6, второй 7 JK-триггеры и D-тригер 13 устанавливаются в "0" состояние благодаря подаче на вторые установочные инверсные входы  сигнала высокого уровня с первого выхода блока установки 15, а на первые установочные инверсные входы

сигнала высокого уровня с первого выхода блока установки 15, а на первые установочные инверсные входы  сигнала низкого уровня со второго выхода блока установки 15, так как конденсатор С блока установки 15 разряжен. По мере заряда конденсатора С, через зарядный резистор R блока установки 15, первый 6, второй 7 JK-триггеры и D-тригер 13 подготавливаются к работе по информационным входам (на первых и вторых установочных инверсных входах

сигнала низкого уровня со второго выхода блока установки 15, так как конденсатор С блока установки 15 разряжен. По мере заряда конденсатора С, через зарядный резистор R блока установки 15, первый 6, второй 7 JK-триггеры и D-тригер 13 подготавливаются к работе по информационным входам (на первых и вторых установочных инверсных входах  появляется сигнал

появляется сигнал  ). Установившийся логический "0" на прямом выходе первого JK-триггера 6 в свою очередь подготавливает первый и второй вход сумматора по модулю два 5 для анализа сигналов с выхода первого 1 и второго 2 резервируемых устройств, этот же сигнал через элемент НЕ 18 подготавливает девятый элемент И 23 к возможности ретрансляции сигналов от второго резервируемого устройства на выход дублированной системы с динамической задержкой, обозначенной на схеме "Выход".

). Установившийся логический "0" на прямом выходе первого JK-триггера 6 в свою очередь подготавливает первый и второй вход сумматора по модулю два 5 для анализа сигналов с выхода первого 1 и второго 2 резервируемых устройств, этот же сигнал через элемент НЕ 18 подготавливает девятый элемент И 23 к возможности ретрансляции сигналов от второго резервируемого устройства на выход дублированной системы с динамической задержкой, обозначенной на схеме "Выход".

В нормальном режиме работы, когда первые 1 и вторые 2 резервированные устройства исправны, на выходе сумматора по модулю два 5 будет логический "0", что поддерживает первый и второй JK-триггеры 6,7 в нулевом состоянии, и запрещает продвижение информации через первый 3 и второй 4 регистры сдвига, так как в этом случае синхронизирующие входы первого 3 и второго 4 регистров сдвига будут блокированы логическим "0", который поступает с выхода седьмого 21 и восьмого 22 элементов И. Информация на выход дублированной системы с динамической задержкой будет проходить от второго резервируемого устройства 2 через девятый элемент И 23 и первый элемент ИЛИ 12, так как на первых и вторых входах первого элемента ИЛИ 12 будут логические "0", при этом на вторых входах первого 8, второго 9 элементов И и на первых входах пятого 19 и шестого 20 элементов И будет логический "0".

В случае отказа второго резервированного устройства 2 "обрыв" или "короткое замыкание", которое приводит к появлению устойчивой информации на его выходе в виде логических "0" или "1" на выходе сумматора по модулю два 5 появляется логическая "1", которая по спаду импульса со входа синхронизации ("Синхр. вход") записывается по первому информационному J-входу первого JK-триггера 6, разрешая прохождение логической "1" с прямого выхода D-триггера 13 на первый информационный J-вход второго JK-триггера 7 через третий элемент И 10 и запрещая прохождение информации от первого 1 и второго 2 резервированных устройств, на первый и второй вход сумматора по модулю два 5 (в этом случае на втором входе второго элемента ИЛИ 16 постоянно логическая "1", а на втором входе четвертого элемента И 17, после элемента НЕ 18, постоянно логический "0", что обеспечивает поддержание на выходе сумматора по модулю два 5 устойчивой логический "1", этот же сигнал, инвертированный элементом НЕ 18 (логический "0"), запрещает прохождение информации непосредственно от второго резервированного устройства 2 через девятый элемент И 23 на выход дублированной системы с задержкой, одновременно логическая " 1 " на выходе сумматора по модулю два 5 поступает на первые входы пятого 19 и шестого 20 элементов И и по сигналу логической " 1 " на синхронизирующем входе первого 3 и второго 4 регистров сдвига открывает их управляющие входы, при этом в первом 3 и втором 4 регистре сдвига происходит последовательная запись обрабатываемой информации по заданному фронту импульсов с шины "Синхр. вход", т.е. осуществляется накопление резерва времени, необходимое для принятия решения.

Логическая "1" на выходе сумматора по модулю два 5 запускает одновибратор 11, на выходе которого формируется импульс длительности меньше резерва времени, создаваемого с помощью первого 3 и второго 4 регистров сдвига, который определяется по максимально возможной серии последовательностей "1" и "0" на выходе первого 1 и второго 2 резервированных устройств. С выхода одновибратора 11 логическая "1" подается на информационный вход DD триггера 13 и в момент спада (т.е. на срезе) импульса на выходе первого резервированного устройства 1 переводит D-триггер 13 в единичное состояние. В результате на выходе третьего элемента И 10 появляется логическая "1", которая через первый информационный J-вход второго JK-триггера 7 и шестой элемент 20 осуществляет подачу логического "0" на второй вход второго элемента И 9, чем обеспечивается прохождение информации с выхода исправного первого резервированного устройства 1.

При отказе первого резервированного устройства 1, проявляющегося в виде устойчивой ложной информации на его выходе - 1 логического "0" или логическая "1", первый JK-триггер 6 установится в единичное состояние, на выходе одновибратора 11 сформируется одиночный импульс таким же образом, как при отказе второго резервированного устройства 2, однако на прямом выходе D-триггера 13 логической "1" не будет, так как на его синхронизирующем входе C не будет спада импульса с выхода первого резервированного устройства 1, а D-триггер 13 срабатывает по срезу импульса на синхронизирующем входе C.

Следовательно, на выходе третьего элемента И 10 сохранится логическая "0" и второй JK-триггер 7 сохранит нулевое состояние и информация на выход дублированной системы с динамической задержкой будет передаваться с выхода исправного второго резервированного устройства 2 через второй регистр сдвига 4 и второй элемент И 9 и первый элемент ИЛИ 12. Элемент ИЛИ-НЕ 14 фиксирует отказ второго JK-триггера 7 (логический "0" на его прямом и инверсном выходах, что приводит к появлению логической "1" на инверсном выходе элемента ИЛИ-НЕ 14 "Отказ"), приводящий к отказу всего устройства, что позволяет сократить среднее время восстановления работоспособного состояния дублированной системы с динамической задержкой.

Литература:

1. В.Л.Шило. Популярные цифровые микросхемы: Справочник.- 2-е издание., исправленное.-М.: Радио и связь, 1989.- 352 с.,ил.

2. В.Н.Вениаминов, О.Н.Лебедев, А.И.Мирошниченко. Микросхемы и их применение: Справочное пособие.-3-е издание., переработанное и дополненное.-М.: Радио и связь, 1989.- 200 с.,ил.

3. М.А.Розенблат. Магнитные элементы автоматизации и вычислительной техники.-М.: Наука, 1974.

4. Справочник по интегральным микросхемам.-2-е издание, переработанное и дополненное - М: Энергия, 1980.-816 с., ил. под редакцией Б.В.Тарабрина.

5. А. С. Партин, В.Г.Борисов Введение в цифровую технику - М.: Радио и связь, 1987.

6. Г. А. Кейджан Прогнозирование надежности микроэлектронной аппаратуры на основе БИС-М.: Радио и связь, 1987.

7. Микросхемы и их применение / Батушев В.А., В.Н.Вениаминов, Ковалев В. Г. и др. - М.: Энергия, 1978. 208с. (Массовая радиобиблиотека; Вып.967).

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ УПРАВЛЕНИЯ ДУБЛИРОВАННОЙ СИСТЕМОЙ С ЗАДЕРЖКОЙ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1999 |

|

RU2147162C1 |

| УСТРОЙСТВО АДАПТИВНОГО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2001 |

|

RU2194366C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2000 |

|

RU2179787C1 |

| УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ РАДИОПЕРЕДАТЧИКА С ДИНАМИЧЕСКОЙ ЗАДЕРЖКОЙ | 2002 |

|

RU2221332C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2002 |

|

RU2216869C1 |

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1999 |

|

RU2149419C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2002 |

|

RU2233038C1 |

| УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2001 |

|

RU2207616C2 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1999 |

|

RU2173877C2 |

| УСТРОЙСТВО ПОДКЛЮЧЕНИЯ ИСТОЧНИКОВ ИНФОРМАЦИИ К ОБЩЕЙ МАГИСТРАЛИ | 2001 |

|

RU2194301C2 |

Изобретение относится к автоматике и может быть использовано для построения дискретных устройств повышенной надежности. Техническим результатом является уменьшение времени задержки передачи цифровой последовательности при исправном состоянии всех элементов дублированной системы с динамической задержкой. Для этого дублированная система с динамической задержкой состоит из резервированных устройств, регистров сдвига, сумматора по модулю два, JK-триггеров, элементов И, одновибратора, элементов ИЛИ, D-триггера, элемента ИЛИ-НЕ, блока установки и элемента И-НЕ. 1 ил.

Дублированная система с динамической задержкой, содержащая первый и второй резервированные устройства, входы которых объединены и соединены с входной шиной, а выходы соединены соответственно с управляющими входами первого и второго регистров сдвига, выходы которых подключены к первым входам соответственно первого и второго элементов И, выходы которых являются соответствующими входами первого элемента ИЛИ, выход которого является выходом дублированной системы с динамической задержкой, выход сумматора по модулю два подключен к первому информационному входу первого JK-триггера, прямой выход которого соединен с первым входом третьего элемента И, выход которого подключен к первому информационному входу второго JK-триггера, вторые информационные входы первого и второго JK-триггеров подключены к корпусной шине, синхронизирующие входы первого и второго JK-триггеров соединены с входной шиной синхронизации дублированной системы с динамической задержкой, синхронизирующий вход D-триггера подключен к выходу первого резервированного устройства, а его информационный вход соединен с выходом одновибратора, вход которого подключен к выходу сумматора по модулю два, прямой выход D-триггера соединен с вторым входом третьего элемента И, первый выход блока установки соединен с первыми установочными инверсными входами первого, второго JK-триггеров и D-триггера, вторые установочные инверсные входы которых подключены ко второму выходу блока установки, прямой и инверсный выходы второго JK-триггера соединены соответственно с первым и вторым входами элемента ИЛИ-НЕ, инверсный выход которого является выходом сигнализации дублированной системы с динамической задержкой, отличающаяся тем, что дополнительно введены четвертый, пятый, шестой, седьмой, восьмой и девятый элементы И, элемент НЕ и второй элемент ИЛИ, причем первый элемент ИЛИ выполнен трехвходовым и его третий вход подключен к выходу девятого элемента И, выходы первого и второго резервированных устройств подключены к первым входам соответственно второго элемента ИЛИ и четвертого элемента И, выходы которых соединены соответственно с первым и вторым входами сумматора по модулю два, выход сумматора по модулю два подключен к первым входам пятого, шестого, седьмого и восьмого элементов И, вторые входы пятого и шестого элементов И подключены соответственно к прямому и инверсному выходам второго JK-триггера, а вторые входы седьмого и восьмого элементов И подключены к выходной шине синхронизации дублированной системы с динамической задержкой, выходы пятого и шестого элементов И соединены с вторыми входами соответственно первого и второго элементов И, а выходы седьмого и восьмого элементов И подключены к входам синхронизации соответственно первого и второго регистров сдвига, прямой выход первого JK-триггера подключен ко второму входу второго элемента ИЛИ и ко входу элемента НЕ, инверсный выход которого подключен ко вторым входам четвертого и девятого элементов И, первый вход девятого элемента И подключен к выходу второго резервированного устройства.

| Дублированная система с задержкой | 1989 |

|

SU1660231A1 |

| Дублированное отказоустойчивое устройство | 1989 |

|

SU1626476A1 |

| RU 2058679 C1, 20.04.1996 | |||

| УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ РАДИОПЕРЕДАТЧИКА | 1995 |

|

RU2099872C1 |

| СТАНОК ДЛЯ БУРЕНИЯ СКВАЖИН | 0 |

|

SU324381A1 |

| СПОСОБ АБСОРБЦИИ ФТОРИСТЫХ ГАЗОВ | 0 |

|

SU347069A1 |

| ВИНТОВОЙ ДОМКРАТ^СЕССгОЗНАН Iшшт-гвш'шщ_^__[^';^;HOTCKA_J | 0 |

|

SU327128A1 |

Авторы

Даты

2000-07-27—Публикация

1999-01-15—Подача