(/)

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофункциональное счетное устройство | 1979 |

|

SU819969A2 |

| Устройство для регулирования расхода | 1984 |

|

SU1171759A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| Цифровой синтезатор частот | 1990 |

|

SU1748251A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Формирователь трапецеидальных импульсов | 1982 |

|

SU1077045A1 |

| Способ измерения фазового сдвига между двумя гармоническими сигналами и устройство для его осуществления | 1988 |

|

SU1596272A1 |

| Умножитель частоты следования импульсов | 1977 |

|

SU705657A1 |

| Быстродействующий управляемый делитель частоты | 1989 |

|

SU1707762A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и в синтезаторах частоты Цель изобретения - повышение быстродействия при одновременном повышении надежности работы - обеспечивается путем введения в устройство ЗК-триггера 4, инвертора 9, элемента ИЛИ-НЕ 10, D-триггера 11 и образования новых функциональных связей. Кроме того, делитель частоты содержит счетчик 1 импульсов, элемент И 3, накапливающий сумматор 2, шины 7,5,6 и 8 входную, первую кодовую, вторую кодовую и выходную соответственно, 2 ил.

о

4J

VI 00 XJ

О

Фиг.1

Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и синтезаторах частоты.

Цель изобретения - повышение быстродействия при одновременном повышении надежности работы,

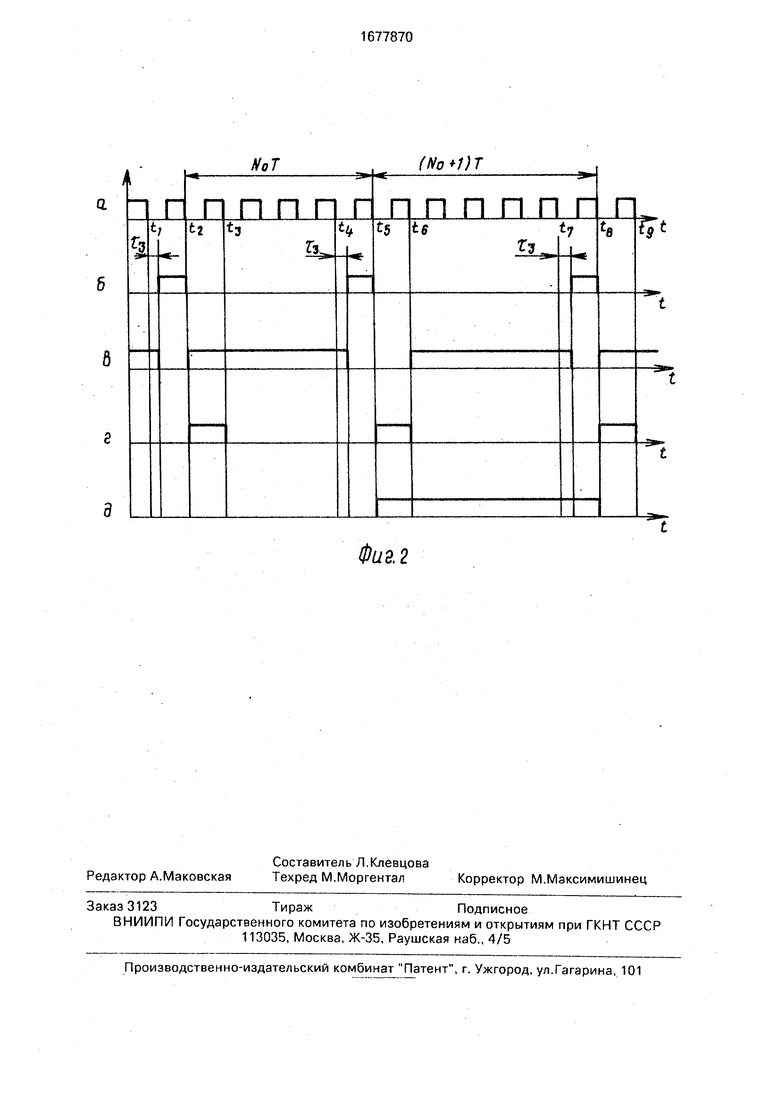

На фиг.1 приведена электрическая структурная схема делителя; на фиг.2 - временные диаграммы, поясняющие его работу (2а - временная диаграмма частоты входного сигнала, поступающего на вход 7 делителя; 26 -.временная диаграмма на выходе JK-триггера 4; 2 в - то же, на С-входе записи параллельного кода счетчика 1; 2г то же, прямого выхода D-триггера 11; 2д - то же, на выходе накапливающего сумматора 2).

Управляемый делитель частоты с дробным коэффициентом деления содержит счетчик 1 импульсов, накапливающий сумматор 2, выход переполнения которого соединен с первым входом элемента И 3, JK-триггер 4, первую и вторую кодовые шины 5 и 6, входную шину 7, выходную шину 8, инвертор 9, элемент ИЛИ-НЕ 10, D-триггер 11; счетный вход счетчика 1 импульсов соединен с входной шиной 7 и входом инвертора 9, выход которого соединен с С-входом D-триггера 11, информационные входы счетчика 1 импульсов соединены с первой кодовой шиной 5, вход разрешения записи - с выходом элемента ИЛИ-НЕ 10, первый вход которого соединен с прямым выходом J К-триггера 4 и D-входом D-триггерз 11, инверсный выход которого соединен cj-вхо- дом и R-входом JK-триггера 4, С-вход которого соединен с выходом переноса счетчика 1 импульсов, прямой выход D-триггера 11 соединен с вторым входом элемента И 3, К-входом JK-триггера 4, выходной шиной 8 и тактовым входом накапливающего сумматора 2, информационные входы которого соединены с второй кодовой шиной 6; выход элемента И 3 соединен с вторым входом элемента ИЛИ-НЕ 10.

Делитель работает следующим образом.

Под действием импульсов (фиг.2а), поступающих по входной шине 7 на счетный вход СТ счетчика 1, осуществляется обычный их пересчет в режиме сложения. После пересчета N импульсов счетчик 1 устанавливается в единичное состояние, и в момент времени ti на его выходе CR переноса появляется нулевой уровень, который воздействует на С-вход синхронизации JK-триггера 4, устанавливая его выход в единичное состояние (фиг.2б). Этот сигнал поступает на элемент ИЛИ-НЕ 10, с выхода которого воздействует в виде нулевою уровня (фиг 2в)на

С-Г5ХОД записи параллельного кода счетчика 1. Параллельный код, равный коэффициенту пересчета К, поступает HaD-входы счетчика 1 по кодовой шине 5. Двоичный код коэффициента пересчета К, соответствующий устанавливаемому коэффициенту деления целой части No, определяется следующим выражением;

К 2m - No,

0 где m - число разрядов счетчика.

На фиг.2 приведены временные диаграммы деления частоты при No 5.

После окончания следующего импульса входного сигнала в момент времени г осу5 ществляется установка прямого выхода D- триггера 11 в 1 (фиг.2г), а инверсного - в О. Нулевой уровень инверсного выхода D- триггера 11 воздействует на инверсный R- вход и J-вход JK-триггера 4, его выход

0 устанавливается в О. Одновременно прекращается запись параллельного кода в счетчик 1 и с этого момента вновь осуществляется пересчет входных импульсов, поступающих на счетный вход СТ счетчика 1.

5Единичный уровень прямого выхода Dтриггера 11 с момента времени t2 поступает на выходную шину 8 и тактовый вход накапливающего сумматора 2, имеющего емкость М. Содержимое накапливающего суммато0 ра 2 увеличивается с каждым тактом на величину а поступающего по кодовой шине 6 установки дробной части коэффициента деления.

После окончания следующего импульса

5 входного сигнала в момент времени t3 выключается D-триггер 11 (фиг.2г), т.е. на его прямом выходе появляется нулевой, а на инверсном - единичный уровень. Одновременно с выключением D-триггера 11 пре0 кращается формирование импульса выходного сигнала. Путем пересчета импульсов на интервале te-ts) осуществляется деление входной части на целую часть коэффициента деления, равного значению дйо5 ичного кода No, поступающего по кодовой шине 5 на D-входы счетчика 1. Длительность интервала (t2, ts) равна NoT, где Т - период входной частоты.

Если очередное значение 0 , записыва0 емое в накапливающий сумматор 2, равно или превышает емкость М сумматороа, он переполняется коэффициент деления устройства становится равным Na+1 на время одного цикла деления.

5 Так, например, после пересчета осуществляется последовательное взведение JK- триггера 4 в момент времени ТА затем D-триггера 11 в момент времени ts, единичный уровень которого, воздействуя на тактовый вход накапливающего сумматора 2, вызывает его переполнение и появление единичного уровня на его выходе (фиг.2д). При этом в результате совпадения единичных уровней с прямого выхода D-триггера 11 и с выхода накапливающего сумматора 2 на интервале (t5,te) происходит увеличение длительности отрицательного импульса на С-входе записи параллельного кода счетчика 1 (фиг.2в) на время, равное периоду вход- ной частоты. Коэффициент деления на интервале (ts,te) становится равным Мо+1. Длительность интервала (ts.te) равна (No+1J х Т. После пересчета No+1 импульсов вновь осуществляется последовательное возведе- ние в момент времени tvJK-триггера 4, а в момент времени te -D-триггера 11, единичный уровень которого, воздействуя на тактовый вход накапливающего сумматора 2, вызывает занесение в накапливающий сум- матор 2 значения вь qi + а М. В этом случае число ф , записываемое в накапливающий сумматор 2, не вызывает его переполнения и на его выходе устанавливается нулевой уровень (фиг.2д). С приходом следу- ющего импульса входного сигнала в момент времени tg происходит выключение D-триггера 11 (фиг.2г), т.е. на его прямом выходе появляется нулевой, а на инверсном - единичный уровень.

В момент т,5 переполнения накапливающего сумматора 2 (фиг.2д) фактически записываемое в него число qi $ -М , т.е. оно меньше предыдущего значения, равного $- а , на величину М-а. Дальнейшее измене- ние кода в накапливающем сумматоре 2 происходит начиная со значения qi.

Так как из М циклов деления а раз устанавливается коэффициент No+1 и (М-а) раз - коэффициент No, средний коэффициент деления равен (М0 + 1 )-а+М0(М-а) м .а

т ил

N

М

М

Если М 2 . где п - целое число, равное

количеству разрядов, накапливающего сум- матора 2, то N представляет собой двоичную дробь.

Предлагаемый делитель, обладающий повышенными быстродействием и стабильностью работы, может быть построен на

51015 20 25 30

35

40

45 50

низкочастотных элементах, так как время задержки гз импульса переноса на выходе CR счетчика 1, а следовательно, и срабатывание JK-триггера 11 может достигать более половины периода входной частоты (фиг.26) без нарушения работы делителя.

Дробность в предлагаемом делителе достигается путем коррекции выходной частоты с помощью дополнительного воздействия D-триггера 11 и накапливающего сумматора 2 через элементы И 3 и ИЛИ-НЕ 10 на С-вхо д записи параллельного кода счетчика 1. Эти особенности предлагаемого делителя обеспечивают значительное повышение быстродействия и стабильности его работы.

Формула изобретения Управляемый делитель частоты с дробным коэффициентом деления, содержащий счетчик импульсов, накапливающий сумматор, выход переполнения которого соединен с первым входом элемента И, первый триггер, первую и вторую ходовые шины, входную и выходную шины, отличающий ся тем, что, с целью повышения быстродействия при одновременном повышении надежности работы, в качестве первого триггера используется JK-триггер и введены инвертор, эле мент ИЛИ-НЕ, второй триггер, в качестве которого используется D-триггер, причем счетный вход счетчика импульсов соединен с входной шиной и входом инвертора, выход которого соединен с С-входом второго триггера, информационные входы счетчика импульсов соединены с первой кодовой шиной, вход разрешения записи - с выходом элемента ИЛИ-НЕ, первый вход которого соединен с прямым выходом первого триггера и D-входом второго триггера, инверсный выход которого соединен с J-BXO- дом и R-входом первого триггера, С-вход которого соединен с выходом переноса счетчика импульсов, прямой выход второго триггера соединен с вторым входом элемента И, К-входом первого триггера, выходной шиной и тактовым входом накапливающего сумматора, информационные входы которого соединены со второй кодовой шиной, а выход элемента И соединен с вторым входом элемента ИЛИ-НЕ.

Фиг 2

| Делитель частоты с переменным коэффициентом деления | 1985 |

|

SU1298908A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Делитель частоты следования импульсов | 1976 |

|

SU656216A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-09-15—Публикация

1989-06-12—Подача