вый вход пятого приемопередающего буфера соединен с вторым выходом адаптера, третья группа входов кото рого соединена с группой входов-выходов четвертого приемопередающего буфера, первая группа входов которо го соединена с первой группой выходов второго приемопередающего буфера, вторая группа входов - с груп пой выходов блока формирования адреса соответственно, группа выходов четвертого приемопередающего буфера соединена с первой группой входов второго приемопередающего буфера, входы-выходы которого соединены с второй группой входов программного вычислительного блока, вторая группа выходов которого соединена с груйпой входов третьего приемопередающего буфера, выход которого соединен с первым входом программного вычислительного блока, второй вход которого соединен с выходом блока сравнения, первая группа выходов второго приемопередающего буфера соединена с первой группой входов блока управления, вторая группа вх дов которого соединена с первой группой входов блока формирования адреса и с второй группой выходов 3 второго приемопередающего буфера, вход которого соединен с первым выходом блока управления, второй,третий и четвертый выходы которого соединены соответственно с первым входом третьего приемопередающего буфера, с входом четвертого приемопередающего буфера и с вторым входом пятого приемопередающего буфера, третья группа входов блока управления соединена с группой выходов третьего приемопередающего буфера, четвертая группа входов блока управления соединена с группой выходов регистра вывода, первая и вторая группы выходов блока управления соединены соответственно с второй группой входов блока формирования ад,реса и с первой группой входов блока преобразования управляющих сигналов, вторая группа входов которого соединена с группой выходов третьего приемопередающего буфера, вход блока преобразования управляющих сигналов соединен с выходом пятого приемопередающего буфера, второй вход третьего приемопередающего буфера соединен с выходом блока преобразования управляющих сигналов .

| название | год | авторы | номер документа |

|---|---|---|---|

| МУЛЬТИПЛЕКСОР ТЕЛЕКОММУНИКАЦИОННЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ | 2004 |

|

RU2269154C1 |

| МИКРОЭВМ | 1994 |

|

RU2108619C1 |

| МИКРОЭВМ | 1991 |

|

SU1819017A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО МЕЖМАШИННОГО ПРЯМОГО ДОСТУПА К ПАМЯТИ | 2021 |

|

RU2775703C1 |

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СИСТЕМА СБОРА СЕЙСМИЧЕСКИХ ДАННЫХ | 2003 |

|

RU2244945C1 |

| СЕТЬ ДЛЯ МАРШРУТИЗАЦИИ СООБЩЕНИЙ | 1996 |

|

RU2115162C1 |

| УСТРОЙСТВО КОНТРОЛЯ ПАРАМЕТРОВ | 1996 |

|

RU2106679C1 |

| Устройство для автоматического контроля больших интегральных схем | 1985 |

|

SU1249518A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ ЭВМ С ОБШИМ КАНАЛОМ СВЯЗИ | 1995 |

|

RU2103730C1 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ УПРАВЛЯЮЩАЯ СИСТЕМА | 2008 |

|

RU2387000C1 |

1. УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ ПЕЧАТНЫХ УЗЛОВ, содержащее программный вычислительный блок, регистр вывода, регистр ввода,блок управления контрольными точками, блок сравнения, первый приемопередающий буфер, релейную матрицу, адаптер, первая группа выходов программного вычислительного блока соединена с соответствующими входами регистра вывода, выкоды котороге соединены соответственно с входами блока управления контрольными, точками, первая группа выходов которого соединена с группой входов первого приемопередающего буфера соответственно и с первой группой входов блока сравнения, вторая группа выходов блока управления контрольными точками соединена с первой группой входов релейной матрицы, третья и четвертая группы выходов блока управления контрольными точками соединены соответственно с второй и третьей группами входов блока сравнения, выход блока управления контрольными точками соединен с входом синхронизации регистра ввода, объединенные входы-выходы первого приi емопередающего буфера соединены соответственно с второй группой (Л входов релейной матрицы, выходы которой соединены с первой группой входов адаптера, первый выход которого соединен с клеммой для под- ключения объекта контроля, группа выходов первого приемопередающего буфера соединена с четвёртой группой входов блока сравнения, группа выходов которого соединена с группой входов регистра ввода, выходы которого соединены с первой группой го входов программного вычислительного Рд блока, отличающеес.я тем, Од что, с целью повьшения быстродействия устройства, в него введены второй, третий, четвертый и пятьйприемопередающие буферы, блок формирования адреса, блок управления, блок преобразования управляющих сигналов, первая группа выходов которого .соединена с группой входов пятого приемопередающего буфера, группа выходов которого соединена с второй группой входов адаптера, пер

Изобретение относится к вычислительной технике, а точнее к устройствам для контроля цифровых печатных узлов и диагностики неисправностей.

Целью изобретения является повышение быстродействия системы путем обеспечения возможности контроля печатных узлов матриц полупроводниковой памяти на частоте их рабочего быстродействия.

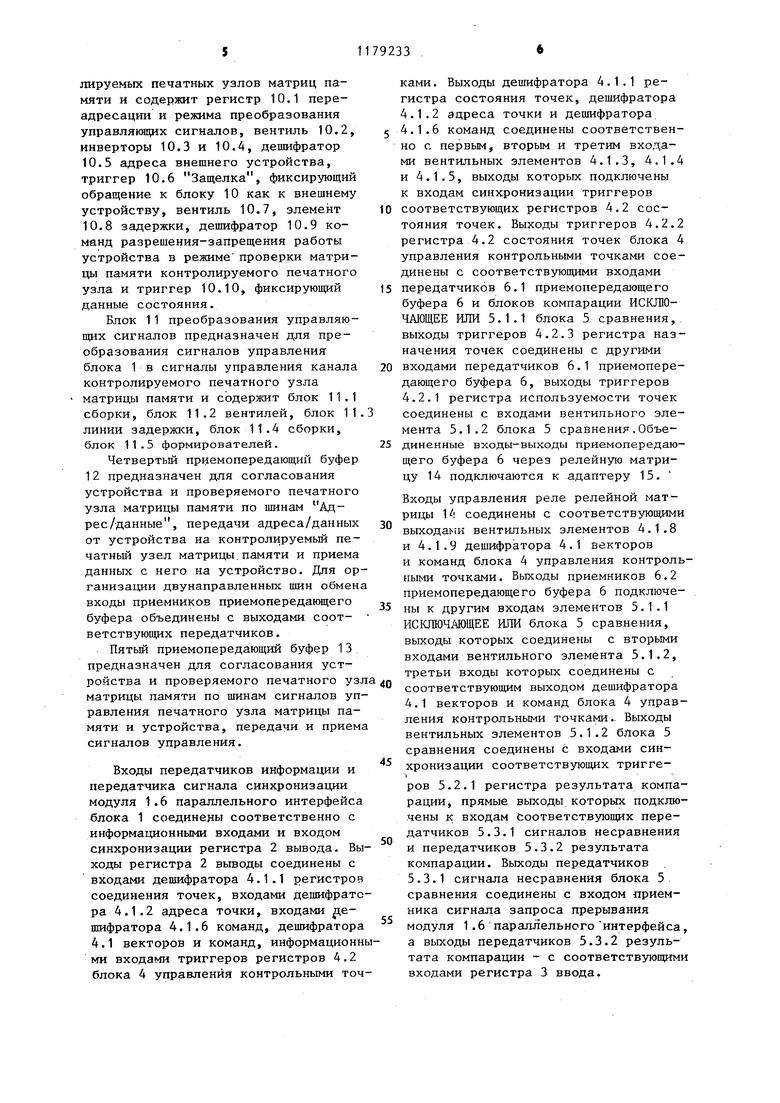

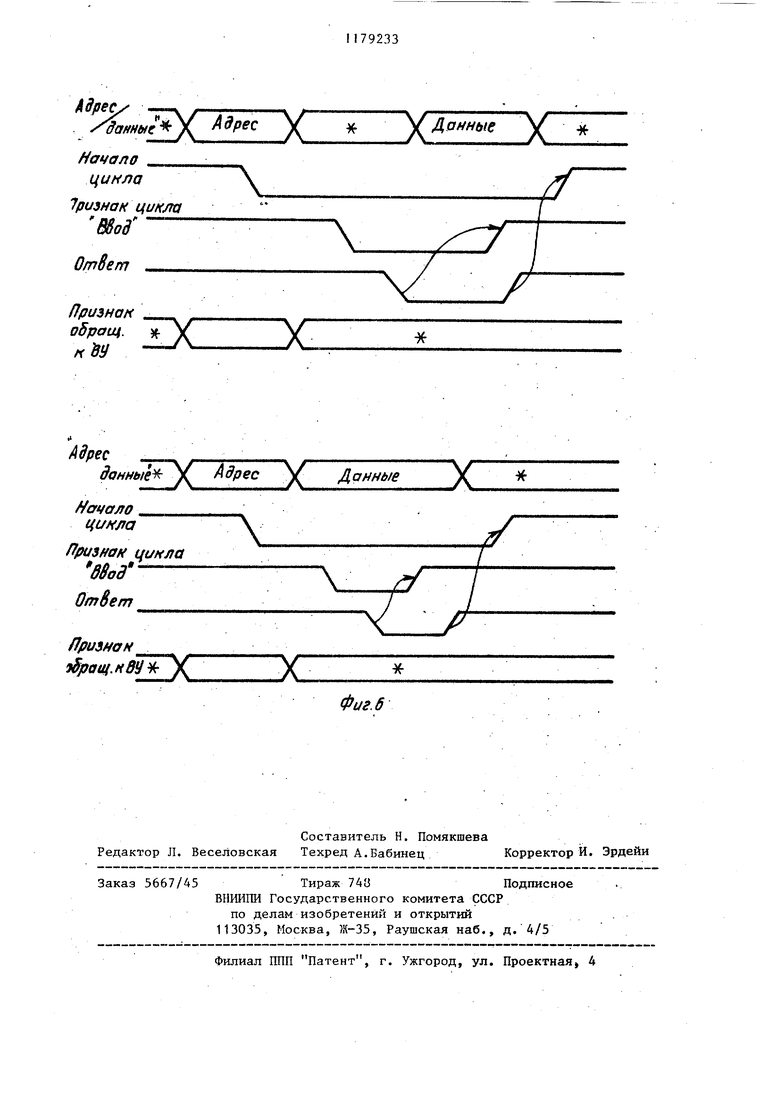

На фиг.1 представлена блок-схема устройстваi на фиг.2 - структурная схема программного вычислительного блока , на фиг.З - функциональная схема блоков устройства, реализующих функции управления, компарации и приема-передачи для одной . контрольной точки, на фиг.4 - функциональная схема блоков устройства

реализующих функции контроля матрицы памяти, а именно блока управления; блока формирования адреса, блока преобразования управляющих

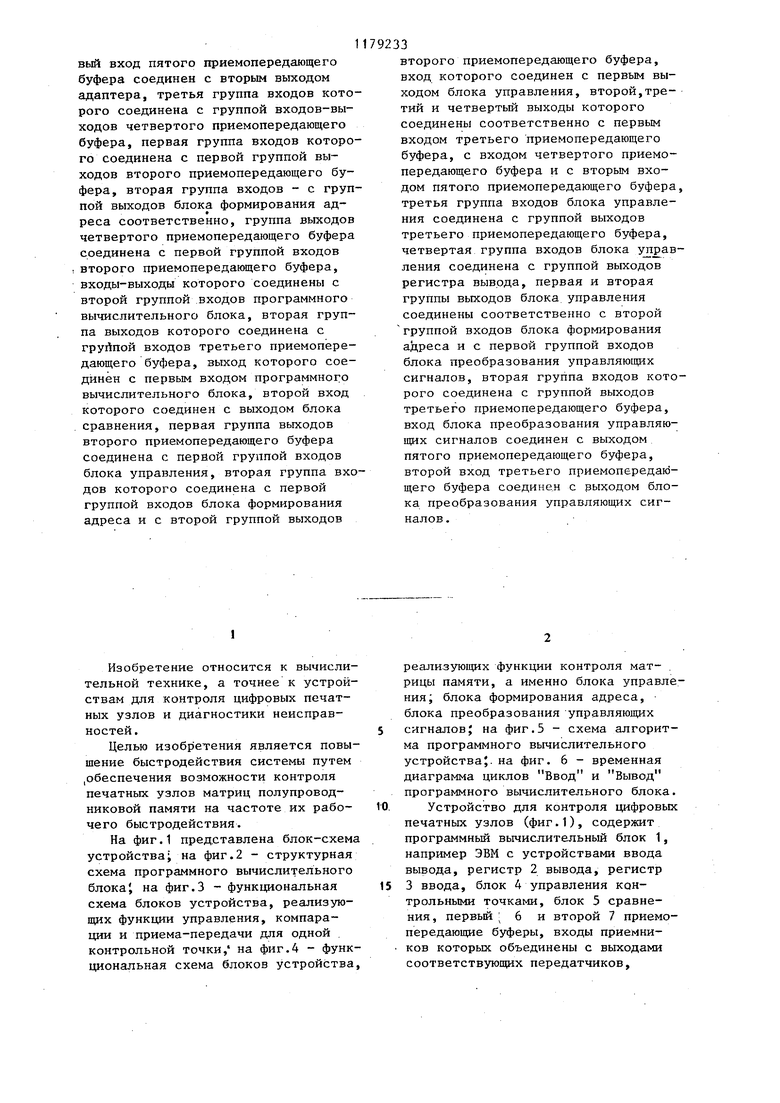

сигналов; на фиг.З - схема алгоритма программного вычислительного устройства;, на фиг. 6 - временная диаграмма циклов Ввод и Вывод программного вычислительного блока.

Устройство для контроля цифровых печатных узлов (фиг.1), содержит программный вычислительный блок 1, например ЭВМ с устройствами ввода вывода, регистр 2 вывода, регистр

3 ввода, блок 4 управления контрольными точками, блок 5 сравнения , первый 6 и второй 7 приемопередающие буферы, входы приемников которых объединены с выходами соответствующих передатчиков, 3 третий приемопередающий буфер 8, блок 9 формирования адреса, блок 1 управления, блок 11 преобразования управляющих сигналов, четвертый приемопередающий буфер 12, входы приемников которого объединены с в ходами соответствующих передатчико пятый приемопередающий буфер 13, релейную матрицу 14, адаптер 15, проверяемый печатный узел 16 (объек контроля). программный вычислительный блок с устройствами ввода-вывода являетс основньм управляющим блоком устройства и выполняет функции хранения и вьщачи в соответствии с алгоритмом Контроля векторов тестовой последовательности, анализа результата несовпадения реакции испытуемого узла с эталоном, выдачи диагностических сообщений и результата контроля на устройство вьшода. Программный вычислительный блок (фиг.2) содержит центральный процессор 1.1, приемопередатчики 1,2 шин Адрес/данные канала, приемопередатчики 1.3 шин управления каналом, модуль 1.4 оперативного запоминающего устройства, модуль 1 управления устройствами ввода-вывода, модуль 1-.6 параллельного интерфейса. Регистр 2 вывода предназначен дл приема векторов и команд тестовой последовательности, вьщаваемых блоком 1, и хранения их на время реали зации. Регистр 3 ввода предназначен для приема и хранения результата несовпадения реакции испытуемого печатного узла с эталоном. Блок 4 управления контрольными точками предназначен для настройки каждой контрольной точки по уровню, используемости, приему реакции или вьщаче воздействия, подключения или отключения соответственно векторам тестовой последовательности, реализации команд сравнения реакции проверяемого узла с эталоном и вьщачи результата несовпадения для анализа в блок 1. Блок 4 содержит дешифратор 4.1 векторов и команд, состоя щий из дешифратора 4.1.1 регистра состояния, дешифратора 4.1.2 адреса контрольной точки, вентильных элементов 4,1.3, 4.1.4 и 4.1.5, дешифратора 4.1.6 команд, вентильных 334 элементов 4,1.7, 4.1.8 и 4,1.9 и передатчиков 4.1.10, регистры 4,2 состояния точек, состоящие из регистра используемости - триггера 4,2.1, регистра состояния уровнятриггера 4,2.2, регистра назначениятриггера 4,2.3. Блок 5 сравнения предназначен для сравнения реакции проверяемого печатного узла с эталоном, фиксации результата сравнения и содержит блок 5,1 компарации, состоящий из блока 5.1.1 ИСКЛЮЧАЮЩЕЕ ИЛИ и вентильного элемента 5.1.2, регистр 5,2 результата компарации, построенньш на триггере 5,2,1, блок 5.3,состоящий из передатчиков 5.3.1 и 5.3.2 сигнала прерывания и результата компарации соответственно. Приемопередающий буфер 6 предназначен для согласования уровней сигналов устройства и проверяемого печатного узла, передачи испытательных воздействий на проверяемый печатный узел и приема реакции от него, Выходы передатчиков объединены с . входами приемников. Бторой приемопередающий буфер 7 предназначен для согласования нагрузки ишн Адрес/данные блока 1, приема и передачи сигналов шин Адрес/данные. Для организации двунаправленных шин обмена входы приемников приемопередающего буфера соединены с выходами соответствующих передатчиков , Третий приемопередающий буфер 8 предназначен для согласования нагрузки шин управления блока 1, приема и передачи сигналов управления блока 1. Блок 9 формирования адреса (фиг,4) предназначен для формироания адреса проверяемой области амяти контролируемого печатного узла атрицы-Ламяти и содержит аппарат- о-перестраиваемый дешифратор 9,1 дреса области адресуемой физически озможной, но реально не существуюей области памяти блока 1, триггер .2 Защелка, фиксирующий обращение адресуемой, но реально не сущетвующей области памяти, вентильные лементы 9.3 и 9.4 и блок 9.5 сбори, реализующие логику переадресации. Блок 10 управления предназначен ля управления работой устройства ри проверке матриц памяти контролируемых печатных узлов матриц памяти и содержит регистр 10.1 переадресации и режима преобразования управлякицих сигналов, вентиль 10,2, инверторы 10.3 и 10.4, дешифратор 10.5 адреса внешнего устройства, триггер 10.6 Защелка, фиксирующий обращение к блоку 10 как к внешнему устройству, вентиль 10.7, элемент 10.8 задержки, дешифратор 10.9 команд разрешения-запрещения работы устройства в режиме проверки матрицы памяти контролируемого печатного узла и триггер 10.10, фиксирующий данные состояния. Блок 11 преобразования управляющих сигналов предназначен для преобразования сигналов управления блока 1 в сигналы управления канала контролируемого печатного узла матрицы памяти и содержит блок 11.1 сборки, блок 11.2 вентилей, блок 11 линии задержки, блок 11.4 сборки, блок 11.5 формирователей. Четвертый приемопередающий буфер 12 предназначен для согласования устройства и проверяемого печатного узла матрицы памяти по шинам Адрес/данные, передачи адреса/данных от устройства на контролируемый печатный узел матрицы.памяти и приема данных с него на устройство. Для организации двунаправленных шин обмена входы приемников приемопередающего буфера объединены с выходами соответствующих передатчиков. Пятый приемопередающий буфер 13 предназначен для согласования устройства и проверяемого печатного узл матрицы памяти по шинам сигналов управления печатного узла матрицы памяти и устройства, передачи и приема сигналов управления. Входы передатчиков информации и передатчика сигнала синхронизации модуля 1.6 параллельного интерфейса блока 1 соединены соответственно с информационньми входами и входом синхронизации регистра 2 вывода. Вы ходы регистра 2 выводы соединены с входами дешифратора 4.1.1 регистров соединения точек, входами дешифрато ра 4.1.2 адреса точки, входами р,ешифратора 4.1.6 команд, дешифратора 4.1 векторов и команд, информационн ми входами триггеров регистров 4.2 блока 4 управления контрольными точ ками. Выходы дешифратора 4.1.1 регистра состояния точек, дешифратора 4.1.2 адреса точки и дешифратора 4.1.6 команд соединены соответственно с первым, вторым и третим входами вентильных элементов 4.1.3, 4.1.4 и 4.1.5, выходы которых подключены к входам синхронизации триггеров соответствующих регистров 4.2 состояния точек. Выходы триггеров 4.2.2 регистра 4.2 состояния точек блока 4 управления контрольными точками соединены с соответствующими входами передатчиков 6.1 приемопередающего буфера 6 и блоков компарации ИСКЛЮЧАЮЩЕЕ ИЛИ 5.1.1 блока 5 сравнения, выходы триггеров 4.2.3 регистра назначения точек соединены с другими входами передатчиков 6.1 приемопередающего буфера 6, выходы триггеров 4.2.1 регистра используемости точек соединены с входами вентильного элемента 5.1.2 блока 5 сравнения.Объединенные входы-выходы приемопередающего буфера 6 через релейную матрицу 14 подключаются к адаптеру 15. Входы управления реле релейной матрицы 14 соединены с соответствующими выходами вентильных элементов 4.1.8 и 4.1.9 дешифратора 4.1 векторов и команд блока 4 управления контрольными точками. Выходы приемников 6.2 приемопередающего буфера 6 подключены к другим входам элементов 5.1.1 ИСКЛЮЧАЮЩЕЕ ИЛИ блока 5 сравнения, выходы которых соединены с вторыми входами вентильного элемента 5.1.2, третьи входы которых соединены с соответствующим выходом дешифратора 4.1 векторов и команд блока 4 управления контрольными точками.. Выходы вентильных элементов 5.1.2 блока 5 сравнения соединены с входами синхронизации соответствующих триггеров 5.2.1 регистра результата компарации, прямые выходы которых подключены к входам Соответствуюш х передатчиков 5.3.1 сигналов несравнения и передатчиков 5.3.2 результата компарации. Выходы передатчиков 5.3.1 сигнала несравнения блока 5 сравнения соединены с входом приемника сигнала запроса прерывания модуля 1.6параллельного интерфейса, а выходы передатчиков 5.3.2 результата компарации - с соответствующими входами регистра 3 ввода.

Выходы вентилей 4.1.7 дешифратора 4.1 векторов и команд блока 4 управления контрольными точками соединены с вторыми входами передачиков 5.3.2 результата компарации блока 5 сравнения, входами установки триггеров 5.2.1 регистра 5.2 результата компарации и входами передатчиков 4.1.10 сигнала синхронизации, выходы которых подключены к входу синхронизации регистра 3 ввода,выходы которого соединены с входами приемников модуля 1.6 параллельного интерфейса блока 1. Выходы приемопередатчиков 1.2 шин Адрес/данные (фиг.2) -подключены к объединенным входам-выходам второго приемопередающего буфера 7. Выходы приемников приемопередающего буфера 7 подключены к входам дешифратора 10.5 адреса внешнего устройства и входам р,егистра 10.1 переадресации и режима преобразования управляющих сигналов блока 10 управления, выходы приемНИКОВ шин, определяющих адрес внутри области адресуемой памяти,подключены к входам передатчиков четвертого приемопередающего буфера 12, а выходы приемников, определяющих область адресуемой памяти, - к входам аппаратно-перестраиваемого дешифратора 9.1 адреса адресуемой области памяти и входам вентилей 9.3 блока 9 формирования адреса. Выходы блока 9 формирования адреса соединены с соответствующими входами передатчиков четвертого приемопередающего буфера 12, объединенные входы-выходы которого подключены к адаптеру 15. Выходы приемников четвертого приемопередающего буфера 12 соединены с выходами передатчиков второго приемопередающего буфера 7. Выходы передатчиков 1.3 шин управляющих сигнало канала подключены к входам приемников третьего приемопередающего буфера 8, выходы которых подключены к соответствующим входам вентилей 10.2 и 10.7, триггера 10.6 Защелка,инвертора 10.4 блока 10 управления и вентилям 11.2 блока 11 преобразовани управляющих сигналов, выходы которог соединены с входами передатчиков пятого приемопередающего буфера 13.

Выходы передатчиков и вход приемника пятого приемопередающего буфера 13 подключены к адаптеру 15, а

выход приемника соединен с входом блока 11.1 сборки блока 11 преобразования управляющих сигналов,выход которого соединен с входом передатчика третьего приемопередающего буфера 8. Выход передатчика третьего приемопередающего буфера подключен к входу приемника 1.3 канала блока Выходы блока 10 управления соединены соответственно с входом управления четвертого приемопередающего буфера 12, входом блока 9 формирования адреса, входом управления второго приемопередающего буфера 7, входом управления третьего приемопередающего буфера 8, входом блока 11 преобразования управляющих сигналов,входом управления пятого приемопередающего буфера 13.

Устройство работает следуюш м образом..

В соответствии с алгоритмом контроля, схема которого приведена на фиг.5, устройство осуществляет вначале контроль произвольной логики (схемы управления) печатного узла матрицы памяти, а затем при верно работающей схеме управления переходи непосредственно к контролю матрицы, памяти. Согласно алгоритму блок 1 производит выдачу фрагментов тестовой последовательности программы контроля, реализуемых блоками устройства, осуществляющих выдачу тестовых воздействий на испытуемый узел и прием реакций от него. Фрагмент тестовой последовательности : представляет собой последовательност векторов, заканчивающуюся командой i сравнг;ния принятой реакции с эталоном .

Векторы и команды тестовой последовательности представляют собой машинные слова, в определенных разрядах которых закодирована информация, определяющая адрес, регистр состояния, значение состояния контрольной точки и действия по отношению к ней.

После выдачи фрагмента в случае наличия несравнения реакции с эталоном, вызывающего прерывание от интерфейса, блок 1 переходит к выдаче команд передачи с блока 5 сравнения результата компарации и приему его через интерфейс в память блока 1. Принятая таким образом информация результата компарации анализируется с

целью установления места неисправности и выдачи на регистр 2 вывода диагностической информации. В случае отсутствия прерывания, .т.е. при совпадении принятой реакции с эталоном, производится анализ на наличие в программе контроля признака конца контроля произвольной логики печатного узла матриц) памяти. При отсутстВИИ его производится дальнейшая выдача фрагментов тестовой последователькости, а при наличии, т.е. при полностью проверенной и правильно работающей схеме управления печатного узла матрицы памяти, блок 1 переходит к выдаче команд подготовки блоков устройства к контролю матрицы памяти печатрого узла. После подготовки блоков устройства к контролю матрицы памяти печатного узла блок 1 производит вьщачу тестовой последовательности в соответствии с алгоритмом функционального тестирования матриц памяти. Выбор алгоритма тестирования матриц памяти определяется особенностями их принципиальных схем и топологии. После окончания контроля матрицы памяти на регистр 2 вывода вьщается информация о его результате.

Блоки устройства при реализации данного алгоритма работают следующим образом.

В исходном состоянии регистр 2 вывода и регистр 3 ввода обнулены. Контрольные точки находятся в состоянии приема, высокого -уровня, используемости и отключены релейной матрицей 14 от адаптера 15. Работа второго,- пятого приемо-передающих буферов 7, 8, 12 и 13 запрещена. Объединенные входы-выходы второго приемопередающего буфера 7 и четвертого приемопередающего буфера -12 и выходы третьего приемопередающего буфера 8 и пятого приемопередающего буфера 13 находятся в высокоимпедансном состоянии.

В соответствии с программой контро1ПЯ векторы тестовой последовательноети поступают через модуль 1.6 параллельного интерфейса блока 1 и регистр 2 вывода (фиг.4) на дешифраторы регистра 4.1.1, адреса точки 4.1.2 и команд 4.1.6 блока управления контрольными точками 4 (фиг.5). Соответственно векторам дешифраторы через

вентильные элементы 4.1.3, 4.1.4 и

вентильными элементами 4.1.9 и 4.1.10. ...

Таким образом работает устройство при контроле произвольной логики (схем управления) печатных узлов матриц памяти.

Устройство в режиме контроля непосредственно матриц .полупроводниковой памяти работает следующим образом (см. фиг. 4 и 6). По окончании проверки произвольной логики печатного узла матрицы п мяти блок 1 в соответствии с алгори мом контроля вьщает через модуль 1. параллельного интерфейса и регистр вывода на блок 10 управления команду разрешения работы устройства в режиме внешнего устройства по отношению к блоку 1, Команда поступает на дешифратор 10.9 команд и устанавливае триггер 10.10 в единичное состояние Сигнал с нулевого выхода триггера 10.10 разрешает работу второго 7 и третьего 8 приемопередающих буферов и устанавливает приемник третьего приемопередающего буфера 8 в состояние приема, а передатчик - в состояние передачи. При отсутствии в канале блока 1 активного сигнала признака обращения Ввод низкий уровень с выхода прием ника этого сигнала третьего приемопе редающего буфера 8 поступает на вход инвертора 10.4 блока 10 управления, высокий уровень с выхода которого ус танавливает второй приемопередающий буфер 7 в состояние приема. Далее блок 1 организует цикл обращения к блоку 10 управления как квнешнему устройству и передает на него соответственно рабочей программе контрол информацию о нижней границе адреса контролируемой области матрицы памяти, начале контроля матрицы памяти и режиме преобразования, сигналов управления каналом блока 1 в сигналы управления контролируемого печатного узла матрищ 1 памяти. Это реализуется следую1дим образом. Адрес внешнего устройства, в адресной части цикла обращения,через приемопередатчики 1.2 канала блока 1 поступает на приемники второго приемопередающего буфера 7 и далее на вход дешифратора 10.5 адреса внешнего устройства блока 10 управ ле.ния. Работа дешифратора разрешает- ся сигналом сопровождения адреса внешнего устройства, поступающим на него соответственно циклу обращения блока 1 к внешнему устройству с выхода приемника третьего приемопередающего буфера 8. С выхода дешифратора сигнал поступает на информацион ный вход триггера 10,6 Защелка, фиксирующего обращение к блоку 10 управления как к внешнему устройству. Сигнал начала цикла, поступающий соответственно циклу обращения с выхода приемника третьего приемопередающего буфера 8 на вход синхронизации триггера, защелкивает состояние информационного входа, подготавливая схему к приему информации. В информационной части цикла обращения информация через приемники второго приемопередающего буфера 7 поступает на входы регистра 10.1 блока 10 управления. Сигнал признака обращения Вывод поступает с приемника третьего приемопередающего буфера 8 на вход вентиля 10.7 блока 10 управления, сигнал с выхода которого синхронизирует занесение передаваемой информации в регистр и через элемент 10.8 задержки и блок 11.1 сборки формирует сигнал ответа о приеме информации, который через передатчик третьего приемопередающего буфера 8 поступает на вход приемника 1.3 канала блока 1. По этому сигналу блок 1 заканчивает цикл обращения. Соответственно принятой в регистр 10.1 информации разрешается работа дешифратора 9.1 адреса области адресуемой памяти, четвертого приемопередающего буфера 12, пятого приемопередающего буфера 13, приемники которого устанавливаются в состояние приема, а передатчики в состояние передачи. Устанавливается режим преобразования (длительность задержки для обеспечения временных параметров) сигналов управления циклом обращения проверяемого печатного узла матрицы памяти в блоке 11 преобразования управляющих сигналов. Затем блок 1 соответственно програм ме контроля, реализующей алгоритм тестовой процедуры проверки матрицы памяти, организует циклы обращения к своей- физической возможной, но реально не существующей памяти. При осуществлении цикла вывода (записи тестовой информации в контролируемую матрицу памяти) устройство работает следуницим образом. В адресной части цикла обращения адрес физически возможной, но ; реально не существующей памяти блока 1 поступает через приемопередатчики 1.2 канала на приемники второго

приемопередающего буфера 7. Разряды адреса, определяющие область адресуемой памяти, с выхода прмемников второго приемопередающего буфера 7 поступают на дешифратор 9.1 и вентильный элемент 9.3 блока 9 формирования адреса. При отсутствии в канале активного сигнала признака обращения Вывод работа вентильного элемента 9.3 запрещена. С выхода дешифратора 9.1 сигнал поступает на информационный вход триггера 9.2 Защелка. Сигнал начала цикла, поступающий с выхода передатчика приемопередатчиков 1.3 канала блока 1 через соответствующий приемник третьего приемопередающего буфера 8 на вход синхронизации триггера, защелкивает наличие обращения, разрешая Прохо кдение с регистра 10.1 разрядов определяющих нижнюю границу области контролируемой памяти, через вентильный элемент 9.4 и блок 9.5 сборки на вход передатчиков приемопередающего буфера 12. Разряды адреса, определяющие адрес ячейки внутри адресуемой оСмасти памяти, с выхода приемников второго приемопередающего буфера 7 поступают на входы передатчиковчетвертого приемопередающего буфера 12 без изменения. Такимобразом, полностью сфо мированный адрес контролируемой памяти .поступает с выхода передатчиков приемопередающег буфера 12 на адаптер 15 и далее на проверяемый печатный узел 16 матрицы памяти.

В информационной части цикла обращения активный сигнал признака обращения Вывод поступает с выхода передатчика приемопередатчиков 1.3 канала блока 1 через приемник третьего приемопередающего буфера 8 и вентиль 10.2 на вентильный элемент 9.3 и разрешает прохождение информации через вентильный элемент 9.3 и блок 9.5 сборки на входы передатчиков четвертого приемопередающего буфера 12J а через инвертор 10.3 запрещает прохо кдение сигналов через вентильны элемент 9.4 с регистра 10,1. Информация по остальным разрядам поступает непосредственно на вход передатчиков четвертого приемопередающего буфера 12. Далее через адаптер 15 информаци поступает на контролируемый печатный узел матрицы памяти 16.

Сигналы управления циклом обращения, поступающие с выходов соответствyюш x передатчиков приемопередатчи.ков 1.3 шин управления каналом через приемники третьего приемопередающего буфера 8, приходят на блок 11.2 вентилей, управление работой которых осуществляется в соответствии с режимом, заданным в регистр 10.1. Сигналы с выходов блока 11.2 вентилей поступает на соответствующий блок 11.3 линии задержки с различными временами длительности задержки для формирования сигрталов с нужными временными параметрами. С выходов линий задержки сигналы поступают на соответствующиеблоки 11.4 сборки и далее через блок 11.5 формирователей,передатчики пятого приемопередающего буфера 13 и адаптер 15 - на проверяемый печатный узел 16 матрицы памяти. Проверяемыр печатный узел 16 матрицы памяти после поступления управляющих сигналов, приема адреса и информации формирует ответный сигнал, который через приемник пятого приемопередающего буфера 13 поступает на блок 11.1 сборки и далее через передатчик третьего приемопередающего буфера 8 - на вход соответствующего приемника приемопередатчиков 1.3 шин управления каналом. Блок 1 принимает этот сигнал и заканчивает цикл обращения.

При осуществлении цикла ввода (чтения) записанной в контролируемую матрицу памяти тестовой информации устройство работает следующим образом.

В адресной части цикла обращения устройство рабеч -ает как описано выше В информационной части цикла активньш сигнал признака цикла Ввод переводит второй приемопередающий буфер 7 в состояние передачи, а четвертьй приемопередающий буфер 12 - в состояние приема. В ответ на поступившие сигналы управления циклом ввода и адреса, проверяемый печатный узел матрицы памяти выставляет данные и формирует сигнал ответа, информирующий об этом. Данные через адаптер 15, приемники четвертого приемопередающего буфера 12, передатчики второго приемопередающего буфера 7 поступают через приемники приемопередатчиков 1,2 канала шин Адрес/ данные в блок 1. Цепь прохождения г мгнала ответа описана выше. По сигналу ответа блок 1 принимает данные н заканчивает цикл обращения. Согласно тестовой процедуре блок 1 сравнивает значения записанной и считанной из контролируемой матрицы памяти информации и в случае несравнения значений идентифицирует .неисправный элемент. После окончания контроля матрицы памяти блок 1 сбраJ сывает установленный режим работы и осуществляет вывод на устройство вывода результата контроля.

«VI

о другие точки

10

±:Г

4/3

Ш

4/.4

«7.5

3

M.S

Hijw

Нд другие

US тпочни

О

ВыхоЗы mpffda tfuftoS ct/eifo/ta CI/H x3&ftu3. друг1гж imoveff

Выходы fK/ftffom4uf(o9 cusnajta tffcoSnaffeffit/t ff/M/st/x /почем

I5J

ч

«)

п

5

&|:

« .

Г 52

521

5/г

yiL

( I1

ft/

«j tl 1$

/4

От eжef4 упрвблемиЛ; ож« ffflytttx mffttfit

« 3

t/g.4

Начало

выдача фрагмента тесто бой последо8ате/7д//ос ти программы 1 онтроля произВо/7ьной логики

ffb/ocff a ffOMuHO nepeffai/u с устройства и прием результата несоВпаВения peaffcfuLf с

Анализ

несоопаае/ ия и иаентифи ация неисправного элемента

8ь1дача на устройство Вы8о да duaeMOCffiut/ecMOSD сообщения и результата /контроля

Ноне ц

Фи.§

выдача команд подготовки yicmpoucmffo

/f ffoнmpoл матриц памяти

db/ffava тестовой последовательности в соотBemcmStju с ал е о ритмом фyи fцuoнcfJ7tfHoг0 тестирования памяти t djpsc/ -.-I-п., )( Адрес )( Начало цинла 7ризнан цикла

-7

X

г/г

A у Даннь(е )( yV

| ATE, Test Techniques for ; Microprocessor, P | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Boarols, Electronic packaging and Production, September, 1977, p | |||

| Прибор для равномерного смешения зерна и одновременного отбирания нескольких одинаковых по объему проб | 1921 |

|

SU23A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Махалин Б.Н | |||

| Реализация аппаратной части систем тестового диагноза | |||

| Электронная техника, сер | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1985-09-15—Публикация

1983-10-03—Подача