Фиг1 я

Изобретение относится к области вычислительной техники и может быть использовано при построении арифметических устройств ЭВМ с жесткими ограничениями на массога- баритные характеристики и энергопотребление. Сомножители могут быть представлены к любой позиционной системе счисления.

Целью изобретения является расширение функциональных возможностей устройства за счет умножения чисел в дополнительном коде.

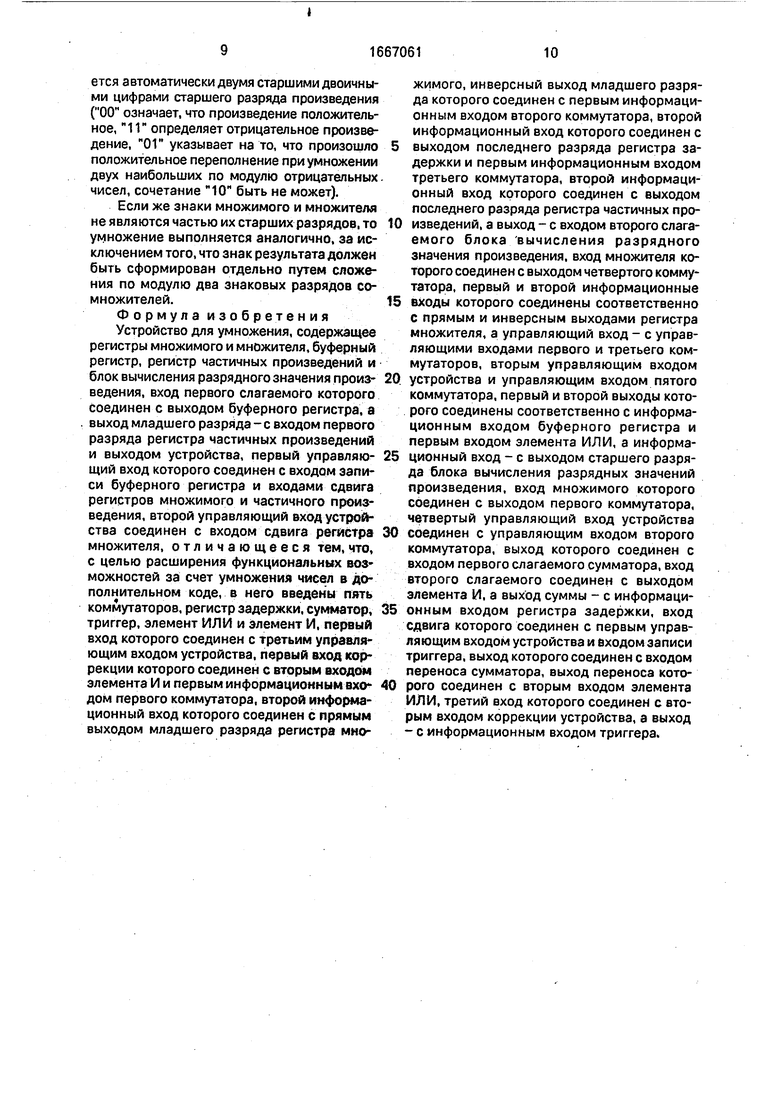

На фиг. 1 представлена функциональная схема устройства для умножения; на фиг. 2 - временная диаграмма работы устройства для случая я- 4.

Устройство (фиг. 1) содержит регистр 1 множимого, регистр 2 множителя, буферный регистр 3, регистр 4 частичных произведений, блок 5 вычисления разрядного значения произведения, регистр б задержки, сумматор 7, триггер 8, коммутаторы 9 - 13, управляющие входы 16-19 устройства, первый 20 и второй 21 входы коррекции устройства, выход 22 устройства.

Рассмотрим функциональное назначение и реализацию узлов и блоков устройства.

Регистр 1 множимого предназначен для хранения значения n-разрядного множимого и представляет собой (л + 1)-разрядный сдвиговый регистр с кольцевым переносом (п разрядов множимого+один разряд информации в виде обратного кода нуля для использования на(п+ 1)-м такте каждого цикла). Регистр 2 множителя сдвиговый предназначен для хранения значения п-разряд- ного множителя.

Буферный регистр 3 предназначен для хранения значения старшего разряда произведения, формируемого в блоке 5.

Регистр 4 частичного произведения п- разрядный сдвиговый предназначен для хранения разрядов сумм частичных произведений, используемых как промежуточная информация при работе устройства.

Регистр 6 задержки n-разрядный сдвиговый предназначен для хранения информации, используемой для введения коррекции по знакам множимого и множителя в случае умножения отрицательных чисел в дополнительном коде.

Блок 5 вычисления разрядного значения произведения предназначен для вычисления значения разрядного произведения сомножителей с учетом поступающих на его входы первого и второго слагаемых. Этот блок комбинационного типа и может быть реализован любыми известными способами, обеспечивающими выполнение функции F А В + С + D, где А, В, С, D - одноразрядные числа.

Сумматор 7 предназначен для формирования коррекции по знакам множимого и

множителя и представляет собой комбинационный сумматор, реализованный любым из известных способов, например в виде сумматора с параллельным переносом. Триггер 8 предназначен для хранения

0 единицы коррекции в случае умножения чисел в дополнительном коде при отрицательном множителе, а также переносов, возникающих при работе сумматора 7 и на выходе коммутатора 12.

5 Коммутаторы 9, 10, 11 и 13 предназначены для передачи информации соответственно на входы множителя, множимого, второго слагаемого блока 5 и первого слагаемого сумматора 7.

0 Коммутатор 12 предназначен для передачи информации блока 5 на вход регистра, 3 (в первые п тактов каждого цикла, когда в блоке 5 формируются старшие разряды разрядных произведений) или на вход триггера

5 8 через элемент ИЛИ 15 (при введении коррекции в случае отрицательного множимого, когда в блоке 5 возможно возникновение переноса из младшего разряда в старший, в результате чего в младшей цифре информа0 ции на выходе старшего разряда блока 5 по окончании (п+1)-го такта отсутствует 1, которую необходимо учитывать на последующих шагах введения коррекции).

Элемент И 14 предназначен для выдачи

5 на вход второго слагаемого сумматора 7 единицы коррекции с входа 20 устройства при умножении чисел в дополнительном коде и отрицательном множимом под управлением потенциала на входе 19 устройства.

0 Элемент ИЛИ 15 предназначен для передачи на вход триггера 8 информации с выхода переноса сумматора 7, второго выхода коммутатора 12, а также сигнала первоначальной установки триггера 8 в 1 с

5 входа 21 устройства при введении коррекции в случае умножения в дополнительном коде при отрицательном множителе.

Устройство работает следующим образом.

0 В исходном состоянии в регистре 1 хранится n-разрядное множимое и обратный код нуля в его (п+1)-м разряде, в регистре 2 хранится п-разрядный множитель, регистры 3, 4, 6 и триггер 8 обнулены.

5 Умножение в устройстве выполняется за п циклов, каждый из которых реализуется за п+1 тактов. В течение одного цикла в устройстве формируется частичное произведение множимого на один разряд множителя, а также осуществляется подсуммирование

этого частичного произведения к ранее накопленной сумме частичных произведений, хранящейся в регистре 4 частичного произведения, и введение коррекции по знакам множимого и множителя, выполняющейся в (п+1}-м такте каждого цикла.

При перемножении положительных сомножителей на входы 19, 20 и 21 устройства в течение всего периода работы подается нулевая информация, а на вход 18 - потен- циал, настраивающий коммутатор 13 на передачу информации с выхода регистра 6 на вход первого слагаемого сумматора 7. Таким образом, в течение всей работы устройства на всех входах сумматора 7 (следователь- но, и на его выходах и в регистре 6) присутствует нулевая информация,

В каждом из п первых тактов каждого цикла в блоке 5 осуществляется умножение соответствующего разряда множителя, по- ступающего на его вход множителя через коммутатор 9 с выхода младшего разряда регистра 2, на соответствующий разряд множимого, поступающий на вход множимого блока 5 через коммутатор 10 с выхода младшего разряда регистра 1 и прибавление к младшему разряду получившегося при этом произведения двух одноразрядных слагаемых, поступающих на входы первого и второго слагаемых блока 5 соответствен- но с выхода регистра 3 и через коммутатор 11 с выхода регистра 4. В конце каждого такта по сигналу на входе 16 устройства старший разряд сформированного блоком 5 произведения с его выхода записывается в регистр 3, младший разряд произведения - в регистр 4, этим же сигналом производится сдвиг информации в регистрах 1 и 4 на один разряд.

В (п+1)-м такте каждого цикла на вход 17 устройства подается сигнал, настраивающий коммутаторы 9, 10, 11 на введение коррекции. При этом на вход множителя блока 5 подается обратный код соответствующего разряда множителя с выхода регист- ра 2, на вход множимого блока 5 - нулевая информация с входа 20 устройства, на вход первого слагаемого - содержимое регистра 3, представляющее старший разряд суммы частичных произведений, а на вход второго слагаемого нулевая информация с выхода регистра 6.

В конце (п+1)-го такта каждого цикла по сигналу на входе 16 устройства с выхода младшего разряда блока 5 в регистр 4 запи- сывается старший разряд суммы частичных произведений, а также осуществляется сдвиг информации в регистрах 1 и 4. Одновременно с этим на вход 17 устройства подается сигнал, перенастраивающий

коммутаторы 9, 10, 11 на прием следующих разрядов множимого и множителя и по заднему фронту этого сигнала производится сдвиг информации в регистре 2, в результате чего на его выходе появляется очередной разряд множителя.

Аналогичным образом выполняются все п циклов работы устройства Следует отметить, что результат умножения сомножителей выводится по одному разряду в каждом первом такте каждого цикла (младшие п разрядов) и в каждом такге п- го цикла (старшие п разрядов) через выход 22 устройства. Старшие п разрядов произведения хранятся также в регистре 4.

Отличие в работе устройства при перемножении отрицательных чисел заключается только во введении в (п + 1)-м такте каждого цикла коррекции по знакам множимого и множителя, которая определяется информацией на входах 19 20 и 21 устройства, а также управляющим сигнзпом на входе 18 устройства.

Пусть множимое , а множитель . Тогда перед началом работы на вход 21 устройства подается сигнал, усонавливаю- щий триггер 8 в 1, а на вход 18 - сигнал, настраивающий коммутатор 13 на передачу разрядов обратного кода множимого с инверсного выхода регистра 1 на вход первого слагаемого сумматора 7. На ч А одах 19 и 20 устройства присутствует нулевая информация, обеспечивающая пути на информационном входе коммутатора 10 и на входе второго слагаемого сумматора 7.

В первом цикле работы устройства в регистр 6 записывается дополнительный код множимого, младший разряд которого на (п+1)-м такте первого цикла при перенастройке коммутаторов 9, 10, 11 с выхода регистра 6 через коммутатор 11 подается на вход второго слагаемого блока 5, где суммируется с содержимым регистра 3 для дальнейшего участия в формировании (пН)-то разряда результата. С выхода младшего разряда блока 5 значение этого разряда записывается в регистр 4.

По окончании (п-Н)-го такта первого цикла на вход 18 устройства подается потенциал, настраивающий коммутатор 13 на передачу информации с выхода регистра 6 на вход первого слагаемою сумматора 7, обеспечивая перезапись разрядов дополнительного кода множимого, начиная со второго, снова в регистр 6

Таким образом, в (гн 1) м такге каждого цикла при перенастройке коммутаторов 9, 10, 11 в блок 5 вводится соответствующий разряд дополнили него кода мк .чимого, а подача в этом же такге iui р ч 1Р устройства управляющего сигнала обеспечивает запрет перезаписи данного разряда коррекции в регистр 6, исключая его дальнейшее использование. После выполнения п(п+1) тактов получаем скорректированное произведение множителей,

В случае, когда , a на (п+1)-м такте каждого цикла вводится соответствующий разряд дополнительного кода множителя, для чего на вход 20 устройства подается код единицы в данной системе счисления, а на вход 19 - сигнал, разрешающий прохождение 1 с входа 20 устройства на вход второго слагаемого сумматора 7. На вход 21 устройства подается нулевая информация, а на вход 18 - сигнал, настраивающий коммутатор 13 на передачу информации с выхода регистра 6 на вход первого слагаемого сумматора 7. Таким образом, в первом такте работы устройства в первый разряд регистра 6 запишется код 1. По окончании первого такта работы устройства на его вход 19 подается нулевая информация, запрещающая прохождение 1 с входа 20 устройства на вход первого слагаемого сумматора 7 и в последующих тактах первого цикла работы устройства на выходе суммы сумматора 7 присутствует нулевая информация.

В (п+1)-м такте первого цикла работа устройства при перенастройке коммутатора 9, 10, 11 на передачу информации с их вторых информационных входов, на входы блока 5 поступает следующая информация: на вход множителя обратный код младшего разряда множителя с выхода регистра 2, на вход множимого 1 с входа 20 устройства, на вход первого слагаемого содержимое регистра 3, на вход второго слагаемого 1 с выхода регистра 6. В данном такте в блоке 5 осуществляется умножение обратного кода младшего разряда множителя, поступающего на его вход множителя, на 1, поступающую на его вход множимого, и прибавление 1, поступающей на его вход второго слагаемого (таким образом, получается младший разряд дополнительного кода множителя), а также прибавление содержимого регистра 3, поступающего на вход первого слагаемого блока 5.

Сформированный на выходе младшего разряда блока 5 ( разряд частичного произведения с введенной коррекцией записывается по сигналу на входе 16 устройства в конце (п+1)-го такта в регистр 4.

Дальнейшая коррекция заключается во введении соответствующих разрядов обратного кода множителя на (п+1)-м такте каждого цикла в блок 5, при этом отметим, что перенастраивая на данном такте коммутатор 13 на передачу информации с выхода

регистра 1, на котором в этот момент присутствует нулевая информация, на вход первого слагаемого сумматора 7, обеспечивается нуль в регистре 6.

В случае перемножения отрицательных

чисел ( и ) необходимо введение двух корректирующих поправок, что и производится в устройстве аналогично рассмотренным алгоритмам. На вход 20 устройств

0 подается код единицы в данной системе счисления, на вход 21 сигнал, устанавливающий триггер 8 перед началом работы устройства в 1, на вход 19 сигнал, разрешающий прохождение в первом такте работы устройства

5 1 с входа 20 устройства на вход второго слагаемого сумматора 7, на вход 18 сигнал, настраивающий коммутатор 13 на передачу информации с выхода регистра 1 на вход первого слагаемого сумматора 7, Таким об0 разом, в первом цикле работы устройства в регистре 6 формируется первый поправочный член, проедставляющий проинвертиро- ванное множимое + 2 в данной системе счисления. Вторым поправочным членом

5 является проинвертированный множитель. Как и в описанных случаях работы устройства, коррекция вводится по одному разряду в (п+1)-м такте каждого цикла, причем разряды первого поправочного члена вводятся

0 через вход второго слагаемого блока 5, а разряды второго поправочного члена - через вход множителя блока 5 с последующим умножением на 1, поступающую на вход множимого блока 5.

5 Следует отметить, что в некоторых случаях введение коррекции (при и , a также при Х 0 и Y 0) в результате суммирования трех слагаемых в блоке 5 возможно возникновение переноса в старший разряд

0 (1 в младшей цифре информации на выходе старшего разряда блока 5), который с выхода блока 5 через коммутатор 12 в конце (п+1)-го такта записывается в триггер 8 и в следующем цикле суммируется с соответст5 вующим разрядом первого поправочного члена (в случае , ) или просто записывается в регистр 6 для участия в очередном шаге коррекции.

В устройстве для умножения использу0 ется алгоритм умножения чисел в дополнительном коде с двумя явными коррекциями, причем введение коррекции поразрядно в (п+1)-м такте каждого цикла позволяет вычислять произведение сомножителей прак5 тически с тем же быстродействием, что и известное, расширив при этом его функциональные возможности.

Следует особо отметить, что если знаки множимого и множителя входят в их стар- шие разряды, то знак результата определяется автоматически двумя старшими двоичными цифрами старшего разряда произведения (00 означает, что произведение положительное, 11 определяет отрицательное произведение, ОГ указывает на то, что произошло положительное переполнение при умножении двух наибольших по модулю отрицательных чисел, сочетание 10 быть не может).

Если же знаки множимого и множителя не являются частью их старших разрядов, то умножение выполняется аналогично, за исключением того, что знак результата должен быть сформирован отдельно путем сложения по модулю два знаковых разрядов сомножителей. Формула изобретения Устройство для умножения, содержащее регистры множимого и множителя, буферный регистр, регистр частичных произведений и блок вычисления разрядного значения произ- ведения, вход первого слагаемого которого соединен с выходом буферного регистра, а выход младшего разряда - с входом первого разряда регистра частичных произведений и выходом устройства, первый управляю- щий вход которого соединен с входом записи буферного регистра и входами сдвига регистров множимого и частичного произведения, второй управляющий вход устройства соединен с входом сдвига регистра множителя, отличающееся тем, что, с целью расширения функциональных воз можностей за счет умножения чисел в дополнительном коде, в него введены пять коммутаторов, регистр задержки, сумматор, триггер, элемент ИЛИ и элемент И, первый вход которого соединен с третьим управляющим входом устройства, первый вход коррекции которого соединен с вторым входом элемента И и первым информационным вхо- дом первого коммутатора, второй информационный вход которого соединен с прямым выходом младшего разряда регистра множимого, инверсный выход младшего разряда которого соединен с первым информационным входом второго коммутатора, второй информационный вход которого соединен с выходом последнего разряда регистра задержки и первым информационным входом третьего коммутатора, второй информационный вход которого соединен с выходом последнего разряда регистра частичных произведений, а выход - с входом второго слагаемого блока вычисления разрядного значения произведения, вход множителя которого соединен с выходом четвертого коммутатора, первый и второй информационные входы которого соединены соответственно с прямым и инверсным выходами регистра множителя, а управляющий вход - с управляющими входами первого и третьего коммутаторов, вторым управляющим входом устройства и управляющим входом пятого коммутатора, первый и второй выходы которого соединены соответственно с информационным входом буферного регистра и первым входом элемента ИЛИ, а информационный вход - с выходом старшего разряда блока вычисления разрядных значений произведения, вход множимого которого соединен с выходом первого коммутатора, четвертый управляющий вход устройства соединен с управляющим входом второго коммутатора, выход которого соединен с входом первого слагаемого сумматора, вход второго слагаемого соединен с выходом элемента И, а выход суммы - с информационным входом регистра задержки, вход сдвига которого соединен с первым управляющим входом устройства и входом записи триггера, выход которого соединен с входом переноса сумматора, выход переноса которого соединен с вторым входом элемента ИЛИ, третий вход которого соединен с вторым входом коррекции устройства, а выход - с информационным входом триггера.

4J

5

e

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1988 |

|

SU1654814A2 |

| Устройство для умножения | 1986 |

|

SU1399729A1 |

| Устройство для умножения | 1989 |

|

SU1635176A1 |

| Устройство для умножения чисел | 1988 |

|

SU1658147A1 |

| Устройство для умножения чисел | 1988 |

|

SU1536374A1 |

| Устройство для умножения | 1988 |

|

SU1529215A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения | 1989 |

|

SU1714593A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Устройство для умножения | 1988 |

|

SU1529216A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке арифметических устройств ЭВМ с жесткими ограничениями на массогабаритные характеристики и энергопотребление. Целью изобретения является расширение функциональных возможностей устройства за счет умножения чисел в дополнительном коде. Устройство содержит регистры множимого 1 и множителя 2, блок 5 вычисления разрядного значения произведения, буферный регистр 3, регистр 4 частичного произведения и нововведенные регистр 6 задержки, сумматор 7, триггер 8, пять коммутаторов 9 - 13, элемент И 14 и элемент ИЛИ 15. 2 ил.

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения чисел | 1988 |

|

SU1575173A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-07-30—Публикация

1989-10-11—Подача