11

1

Изобретение относится к технике передачи данных и может быть использовано в телеметрических и других информационно-измерительных системах в которых измерительная информация передается по каналам связи.

Цель изобретения - повышение надежности устройства путем уменьшения аппаратурных затрат при сохранении высокого быстродействия передачи данных и малой вероятности их потерь.

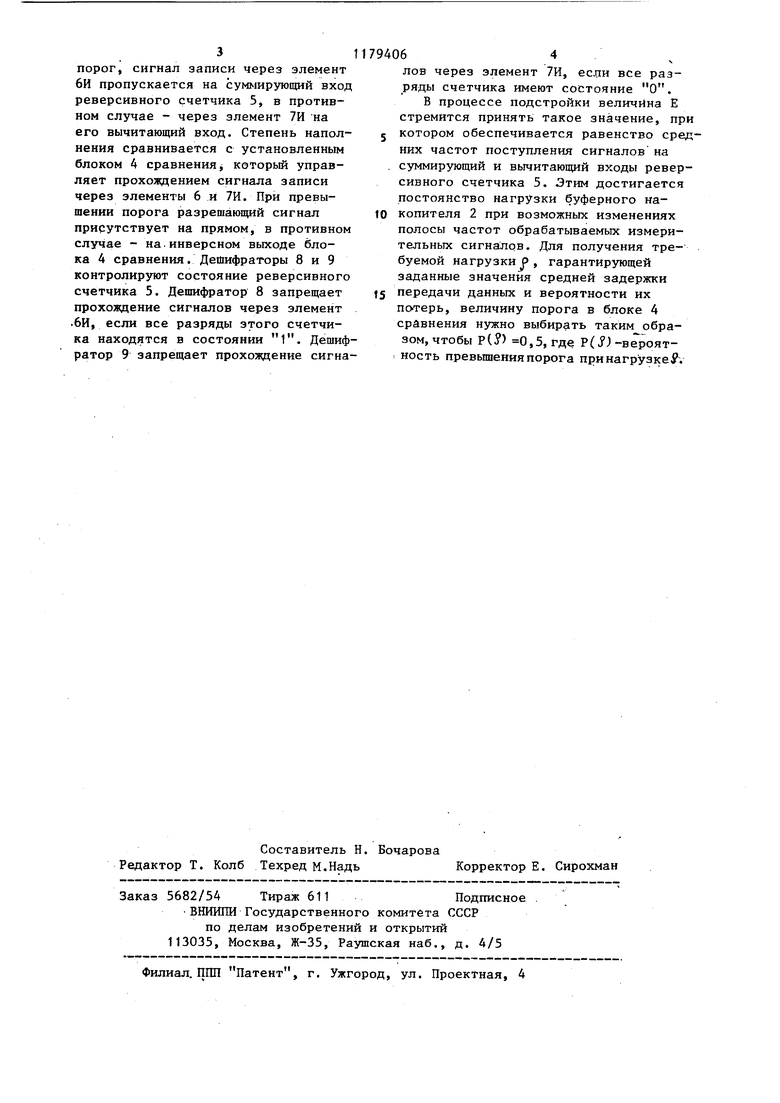

На чертеже представлена блоксхема предлагаемого устройства.

Устройство содержит арифметический блок 1, буфер})ый накопитель 2, запоминающий блок 3 контрольных величин, блок А сравнения, реверсивный счетчик 5, элемент 6И, элемент 7И, дешифраторы 8 и 9, информационный 10, адресный 11, считывающий 12 входы и выход 13 устройства.

Устройство производит адаптивное табулирование -измерительных сигна/100, поступающих от нескольких истоников (датчиков), основанное на контроле тюгреинюсти их приближения полирюмами заданного потока данных в регулярный. Точность табулирования выбирается автоматически.

Устройство работает следующим образом.

На информационный вход 10 устройства подаются цифровые отсчеты измерительных сигналов, которые поступают на первый вход арифметического блока 1. Номер измерительного сигнала, которому принадлежит текущий цифровой отсчет, подается на адресный вход 11 устройства и поступает на адресный вход запоминающего блока 3 контрольных величин. В арифметическом блоке 1 на основании поступившего цифрового отсчета и информации, хранящейся в запоминающем блоке 3 контрольных величин, вычисляется текущее значение погрешности аппроксимации обрабатываемого сигнала полиномом заданного вида, которое сравнивается с ее допустимой величиной. Например, при аппроксимации измерительных сигналов зкст.раполяционными полиномами нулевой степени поступивший цифровой отсчет А;, i-ro измерительного сигнала сравнивается в арифметическом блоке 1 с храняищмся по адресу i в запоминающем блоке 3 контрольных величин последним

94062

переданным в буферный накопитель 2 отсчетом В этого сигнала. Если разность значе шй А и В| не выходит за допустимые пределы iE, то А отбрасывается, а значение В используется для последующего сравнивания. В противном случае, когда или +Е, отсчет AV в качестве очередного табличного значения

0 i-ro измерительного сигнала передается в буферный накопитель 2, а в качестве контрольной величины записывается по адресу i в запоминающий блок 3. Под воздействием сигнала,

5 сформированного на управляющем выходе арифметического блока 1, производится запись нового табличного значения в буферный накопитель 2.

0 Буферный накопитель 2 согласует во времени обмен данными между арифметическим блоком 1 и потребителем ит1формации (например, передатчиком канала связи), подключаемым к выходу 13 устройства. Чтение данных из буферного накопителя 2 производится при поступлении на считывающий вход 12 устройства внешнего тактового сигнала, формируемого потребителем информации.

Автоматический выбор точности табулирования осуществляется путем адаптивной подстройки пределов Е допусков в арифметическом блоке 1.

5 Мгновенное значение Е определяется подаваемым на управляющий вход этого блока содержимым S реверсивного счетчика 5. При этом , где - постоянный масштабный множитель. Для упрощения технической реализации удобно, в частности, принять (,1,2 ...), поскольку умножение на такой множитель реализуется сдвигом кода S на п разрядов

5 вправо при передаче его на управляющий вход арифметического блока 1. Изменение содержимого реверсивного счетчика 5 происходит при поступлении сигналов на его входы: сигнал

0 на суммирующем входе увеличивает, а на вычитающем v eньшaeт содержимое на единицу. Формирование сигналов, подаваемых на суммирующий и вычитающий входы, производится в моменты записи данных в буферный накопитель 2. Если наполнение (число занятых ячеек памяти) буферного накопителя 2 превышает установленный

3

порог, сигнал записи через элемент 6И пропускается на суммирующий вход реверсивного счетчика 5, в противном случае - через элемент 7И на его вычитающий вход. Степень наполнения сравнивается с установленным блоком А сравненияj который управляет прохоящением сигнала записи через элементы 6 и 7И. При превышении порога разрешающий сигнал присутствует на прямом, в противном случае - на.инверсном выходе блока 4 сравнения. Дешифраторы 8 и 9 контролируют состояние реверсивного счетчика 5. Дешифратор 8 запрещает прохолщение сигналов через элемент бИ, если все разряды этого счетчика находятся в состоянии 1. Дешифратор 9 запрещает прохождение сигна794064

лов через элемент 7И, есди все разряды счетчика имеют состояние О.

В процессе подстройки величина Е стремится принять такое значение, при 5 котором обеспечивается равенство средних частот поступления сигналовна . суммирующий и вычитающий входы реверсивного счетчика 5. Зтим достигается постоянство нагрузки буферного наfO копителя 2 при возможных изменениях полосы частот обрабатываемых измерительных сигналов. Для получения требуемой нагрузки р, гарантирующей заданные значения средней задержки

15 передачи данных и вероятности их потерь, величину порога в блоке 4 сравнения нужно выбирать таким образом, чтобы Р(5) 0,5, где P(j)-вероятность превьшгенияпорога принагруэке.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сокращения избыточности данных | 1982 |

|

SU1023377A1 |

| Вычислительное устройство для сокращения избыточности измерительных данных | 1974 |

|

SU506862A1 |

| Устройство для передачи сигналов | 1980 |

|

SU920808A1 |

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

| Устройство для связи процессора с запоминающим устройством | 1983 |

|

SU1083196A1 |

| Устройство для адаптивного сжатия информации | 1986 |

|

SU1383428A1 |

| Многоканальное устройство для регистрации | 1985 |

|

SU1322156A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU970475A1 |

| УСТРОЙСТВО ДЛЯ СЕЛЕКЦИИ ИЗОБРАЖЕНИЙ ОБЪЕКТОВ | 1990 |

|

RU2032218C1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1264243A1 |

УСТРОЙСТВО ДЛЯ СОКРАЩЕНИЯ ИЗБЫТОЧНОСТИ ДАННЫХ, содержащее ариф метический блок, первый информационный вход которого соединен с информационным входом устройства, первый информационный и управляющий выходы арифметического блока соединены соо ветственно с информационным и первым управляющим входами буферного накопителя, второй управляющий вход кот рого подключен к считьгаающему входу ; устройства, информационный выход к выходу устройства, выход состояния - к входу блока сравнения, прямой выход которого соединен с первым входом первого элемента И, второй / / вход которого подключен к управляющему выходу арифметического блока, выход первого элемента И подключен к суммирующему входу реверсивного счетчика, вычитающий вход которого соединен с выходом второго элемента И, выход реверсивного счетчика соединен с входами дешифраторов и с . управляющим входом арифметического блока, вторые информационные выход и вход которого соединены соответственно с информационными входом и выходом запоминающего блока контрольных величин, адресный вход которого соединен с адресным входом устройства, выход первого дешифратора соединен с третьим входом первого элемента И, выход второго дешифратора соединен с-первым входом второго элемента И, отличающееся тем, что, с целью повьш1ения надежности устройства, управляющий выход арифметического блока соединен с вторым входом второго элемента И, третий вход которого подключен к инверсному выходу блока сравнения.

| Воздушно-космическая телеметрия Под ред. | |||

| К.Н, Трофимова, - М,: Воениздат, 1968, с, 199-207, рис, 4.16 | |||

| Устройство для сокращения избыточности данных | 1982 |

|

SU1023377A1 |

Авторы

Даты

1985-09-15—Публикация

1984-04-16—Подача