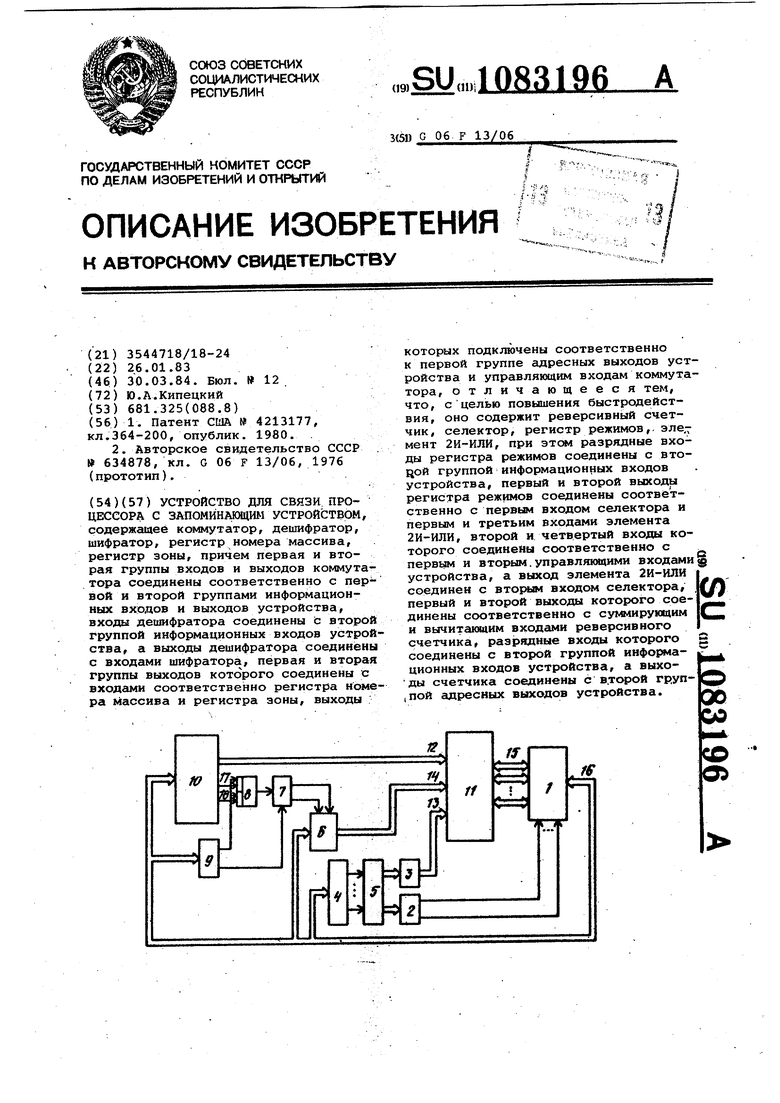

Изобретение относится к вычислительной технике, в частности к устройствам для связи процессора (микропроцессора I и запоминающего устро ства, и может быть использовано при построении систем обработки данных на базе микро-ЭВМ. Известно устройство, позволяющее .связывать процессор и память, содер жащее плату процессора, по меньшей мере две платы памяти, матрицу памя ти, соединительные элементы и соеди нительную плату Cl3. Недостаток указанного устройства состоит в том, что формат данных па мяти должен соответствовать формату данных процессора и для формировани адресов данных требуется программная модификация адресов яч«ек данных, которая уменьшает пропускную способность устройства. Наиболее близким по технической сущности к предлагаемому является устройство для связи запоминающего и арифметического устройства, содержащее коммутатор, дешифратор, шифратор, регистр номера массива, регистр зоны, причем первая и вторая группы входов и выходов коммутатора соединены соответственно с первой и второй группами информационных входов и выходов устройства, входы дешифратора соединены с второй группой информационных входов устройства, а выходы дешифратора соединены с входа ми шифратора, первая и вторая группы выходов которого соединены с входами соответственно регистра номера масси ва и регистра зоны, выходы которых подключены соответственно к первой группе адресных входов устройства и управляющим входам коммутатора L2. Недостаток известного) устройства заключается в том, что перед каждым обращением процессора в память данных требуется прог Ьаммная модификация адреса (формирование и запись фиксированного адреса или арифметическая операция над текущим адресом Кроме того, отсутствие соответствия между значением адреса отсчета двумерного сигнала в памяти и реальным значением пространственных координат отсчета создает неудобства для программиста при разработке программ цифровой обработки многомерных сигна лов, например сигналов изображения. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем/ что в устройство, содержгицее коммутатор, дешифратор, шифратор, регистр номера массива, регистр зоны, причем первая и вторая группы входов и выходов коммутатора соедине ны соответственно с первой и второй группами информационных входов и выходов устройства, входы дешифратора соединены с второй группой информационных входов устройства, а выходы дешифратора соединены с входами шифратора, первая и вторая группы выходов которого соединены с входами соответственно регистра номера массива и регистра зоны, выходы которых подключены соответственно к первой группе адресных выходов устройства и к управляющим входаи коммутатора, введены реверсивный счетчик, селектор, регистр режимов, элемент 2И-ИЛИ, при этом разрядные входы регистра режимов соединены с второй группой информационных входов устройства, первый и второй выходы регистра режимов соединены соответственно с первым входом селектора и первым и третьим входами элемента 2И-ИЛИ, второй и четвертый входы которого соединены соответственно с первым и вторьзм управляющими входами устройства, а выход элемента 2И-ИЛИ соединен с вторым входом селектора, первый и второй выходы которого соединены соответственно с су «мирующим и вычитающим входами реверсивного счетчика, разрядные входа которого соединены с второй группой информационных входов устройства, а выходы счетчика соединены с второй группой адресных выходов устройства. На чертеже приведена структурная схема предлагаемого устройства. Устройство для связи процессора с запоминающим устройством содержит коммутатор 1, регистр 2 зоны, регистр 3 массива, дешифратор 4, шифратор 5, реверсивный счетчик 6, селектор 7, элемент 2И-ИЛИ 8, регистр 9 режимов, процессор 10, запоминакяцее устройство 11, адресную шину 12 прогцессора, первую 133 и вторую 14 группы сщресных выходов устройства, первую 15 и вторую 16 группы информационных входов и выходов устройства, 17 и второй 18 управляющие входы устройства. Устройство работает следующим образом. Адресные выходы.запоминающего устройства (ЗУ) 11 разделены на три группы 12, 13 и 14. Первая группа 13 адресных выходов устройства подключена к регистру 3 массива, разрядность которого определяет количество массивов, содержащихся в ЗУ. Вторая группа 14 адресных выходов устройства представляет собой выходы реверсивного счетчика 6 и адресует ячейки подмассива информации, относящиеср к определенному значению адреса. Объем подмассива определяется разрядностьюmсчётчика и составляет 2 ячеек памяти, сформированных процессором. Третья группа адресных входов запоминающего устройства 11 подключена к адресной шине процессора 10, которая адресует ячеек памяти, принадлежащих определенному массиву ЗУ (п -разрядность шины адреса процессора 10 ). По разрядам информации запоминающее устройство 11 разделено на зоны выбор которых определяется состоянием регистра 2 зоны. Зонная организация ЗУ позволяет подключить к шине данных процессора требуемую зону, разрядность которой соответствует разрядности шины данных процессора. Значения сигналов на выходах регистра 2 зоны управляют работой коммутатора 1, который подключает первую группу 15 входов и выходов ЗУ через вторую группу 16 входов и выходов устройства к двунаправленной шине данных процессора 10. Группы 15 и 16 входов и выходов устройства представ ляют собой единые двунаправленные линии обмена даннымк. Коммутатор 1 выполнен по схеме с использованием буферных усилителейг например, типа589ИК12, которые включены встречно друг другу. Такая структура коммутатора позволяет сбглассзвать формат данных процессора (группа 16 входов и выходов ) с форматом информационных входов и выходов 15 запоминающего устройства. Принадлежность считываемой из памяти или записываемой в память инфор мации к зоне или массе учитывается: при программировании работы процессора . Для процессора группа элементов 2-5 является портом вывода, информация в который поступает .от процессора по двунаправленной шине данных при выполнении им команды Вывод {ОИТ ). При этом информация, котОрая определяет номер массива и зону Памяти, записывается в регистры 2 и 3 зоны и массивов, проходя через дешифратор 4 и шифратор 5. Таким обр зом, командой Вывод подготавливаются значения первой группы 13 адрес ных. выходов устройства и управляющих сигналов на входах коммутатора 1 для последующих обращений процессора 10 в ЗУ 11. Для изменения номера массиг ва или зоны в регистры 2 и 3 записывдается новая информация, т.е. выполняется новая команда Вывод. Установка адреса определенной ячейки памяти, содержащейся в прдмас сиве, и режима модификации адресов в пределах данного подмассива осуществляется в процессе записи йнформации в двухразрядный регистр 9 и счетчик 6, которые являются портами вывода процессора. Значение записыБаемой информации учитывается при составлении прогрс1мМы и засылается в портВ процессе выполнения коман ды Выв.од. Состояние выхода первого разряда регистра 9 подается науправ ляющий вход селектора 7 и определиется режим работы реверсивного счетчика 6 .Если на первом выходе регистра 9 присутствует логическая 1, то селектор 7 пропускает импульс со сгвоего входа на суммирующий вход счетчика 6, если на первом выходе регистра 9 сформирован логический О, то счетные импульсы подаются на вычитающий вход счетчика 6„ Счетные импульсы формируются во время выполнения операции обращения процессора 10 в ЗУ 11 и представляют собой управляющие сигналы процессора 10, например, Запись и Прием, которые поступают с первого 17 и второго 18 управляющих входов устройства на второй и четверть1й входы элемента 2И-ИЛИ 8. Прохождение импульсов чере элемент 2И-ИЛИ 8 может блокироваться соответствующим значением на втором выходе регистра 9 режимов. В режимах суммирования или вычитания модификация счетчика произвол дится по завершен-ию обращения процессора 10 к ЗУ 11, т.е. по Заднему фронту управляющих сигналов Прием и Запись. Таким образом, для последующего обращения процессора 10 в ЗУ 11 не требуется программной модификации адреса. Кроме того, сочетание суммирующего и вычитающего режимов работы счетчика позволяет оперативно изменять адрес памяти в сторону увеличения или уменьшения. Рассмотрим работу устройства на конкретном примере с использованием микропроцессора К580ИК80. Пусть в ЗУ 11 хранятся оцифрованные значения двумерной функции, например , изображения в картинной плоскости. Каждому массиву, определяемому значением регистра 3 массивов, соответствует один кадр изображения в памяти форматом ХУ, где Х,У - пространственные координаты в прямоугольной системе координат. Адрес отсчета изображения ХУ определяется значением шины 12 адреса процессора. Каждый отсчет изображения состоит из трех байтов и соответствует цифровым значениям трех цветоделенных составляющих: красной R, зеленой Q. и синей В. Пусть адресация точки изображения осуществляется значением пары регистров общего назначения процессора НЦ. Выборку значений R, G и В на регистры процессора А,Д и Е, а также их засылку в память в те же ячейки после обработки можно произвести по следующей программе процессора: LX1 Н, ХУ - загрузка регистровой пары Н значе1 ием сщреса ХУ; MV1 А - загрузка аккумулятора и вывод в регистр 9. ОИТ режимов и счетчик 6 информации, соответствующей режиму Суммирование, и нулевое состояние счетчика 6}

V А, М - передача содержимого

ЗУ 11, соответствующего значению красной цветоделенной состав- 5 ляницей R , в регистр А;

V л, М - передача значения Q в регистр D ;

V Е, М - передача значения В 10 в регистр Е

- команды обработки значений R, Q и В;

V М, А - передача значения R

в . 15

V М, D - передача значения Q в ЗУ,

МО V М, Е - передача значения В в ЗУ.

Данный пример подтверждает преимущество предлагаемого устройства по сравнению с известным. Для шести обращений в память не требуется программной модификации адреса перед кажпым обращением, что исключает затрату времени на ее выполнение. Использование изобретения значительно повышает пропускную способность устройства свя§и.

Положительный эффект изобретения достигается за счет повышения пропускной способности предлагаемого устройства путем управления формиро.ванием адресов памяти данных.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для связи запоминающего и арифметического устройств | 1976 |

|

SU643878A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| Медианный фильтр | 1988 |

|

SU1562902A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1983 |

|

SU1119065A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Устройство управления процессора | 1988 |

|

SU1670686A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1989 |

|

SU1605279A2 |

| Устройство буферизации команд процессора | 1983 |

|

SU1092506A1 |

| Устройство для диагностирования оперативной памяти | 1990 |

|

SU1785042A1 |

УСТРОЙСТВО ДЛЯ СВЯЗИ ПРОЦЕССОРА С ЗАПОМИНАЮЩИМ УСТРОЙСТВОМ содержащее кс 1мутатор, дешифратор, шифратор, регистр номера массива, регистр зоны, причем первая и вторая группы входов и выходов коммута тора соединены соответственно с пер вой и второй группами информационных входов и выходов устройства, входы дешифратора соединены с второ группой информационных входов устро ства, а выходы дешифратора соединен с входами шифратора, первая и втора группы выходов которого соединены с входс1ми соответственно регистра ном ра Массива и регистра зоны, выходы которых подключены соответственно к первой группе адресных выходов устройства и управляющим входам коммутатора, отличающееся тем, что, с целью повышения быстродействия, оно содержит реверсивный счетчик, селектор, регистр режимов,, элемент 2И-ИЛИ, при этом разрядные входы регистра режимов соединены с втодой группой информационных входов устройства, первый и второй выходы регистра режимов соединены соответственно с первым входом селектора и первым и третьим входами элемента 2И-ИЛИ, второй и четвертый входы которого соединены соответственно с первым и вторым.управляющими входамиg устройства, а выход элемента 2И-ИЛИ соединен с вторым входом селектора, первый и второй выходы которого соединены соответственно с суммирующим и вычитакицим входами реверсивного счетчика, разрядные входы которого соединены с второй группой информационных входов устройства, а выходы счетчика соединены с в, групПой адресных выходов устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США 4213177, кл.364-200, опублик | |||

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Установка для пайки деталей | 1977 |

|

SU634878A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-03-30—Публикация

1983-01-26—Подача