t

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам (ЗУ), и может быть использовано для построения ЗУ с высокой надежностью работы.

Цель изобретения - повьшение быстродействия устройства.

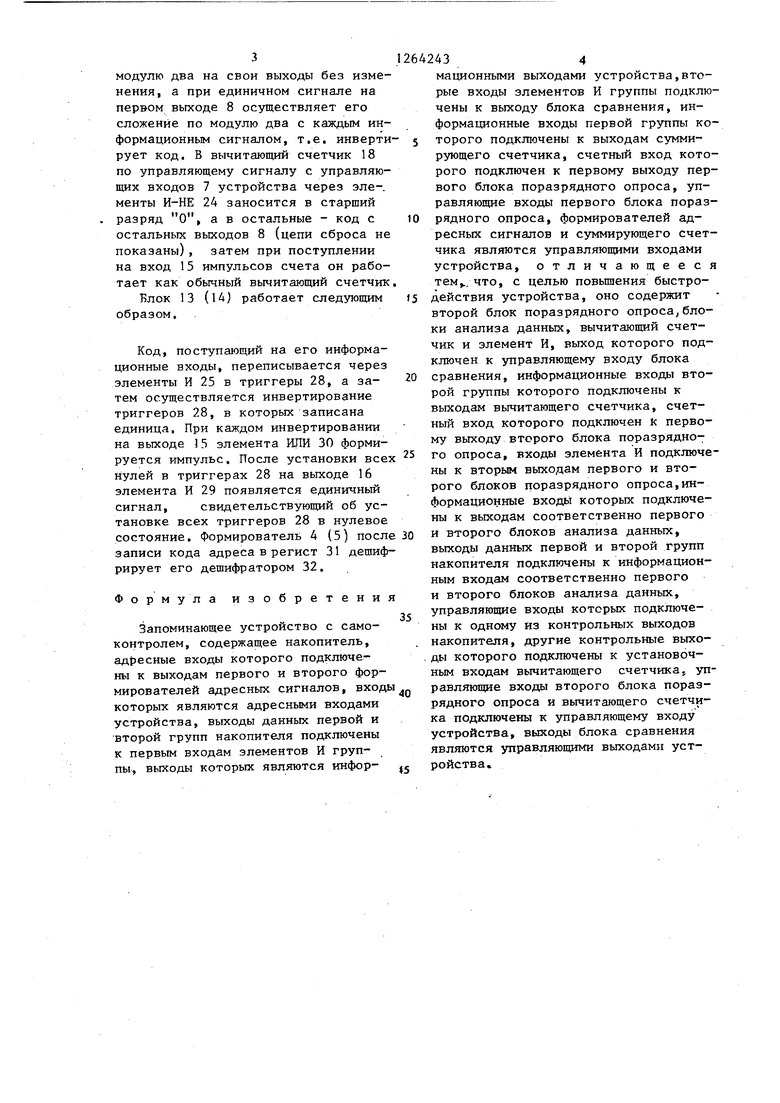

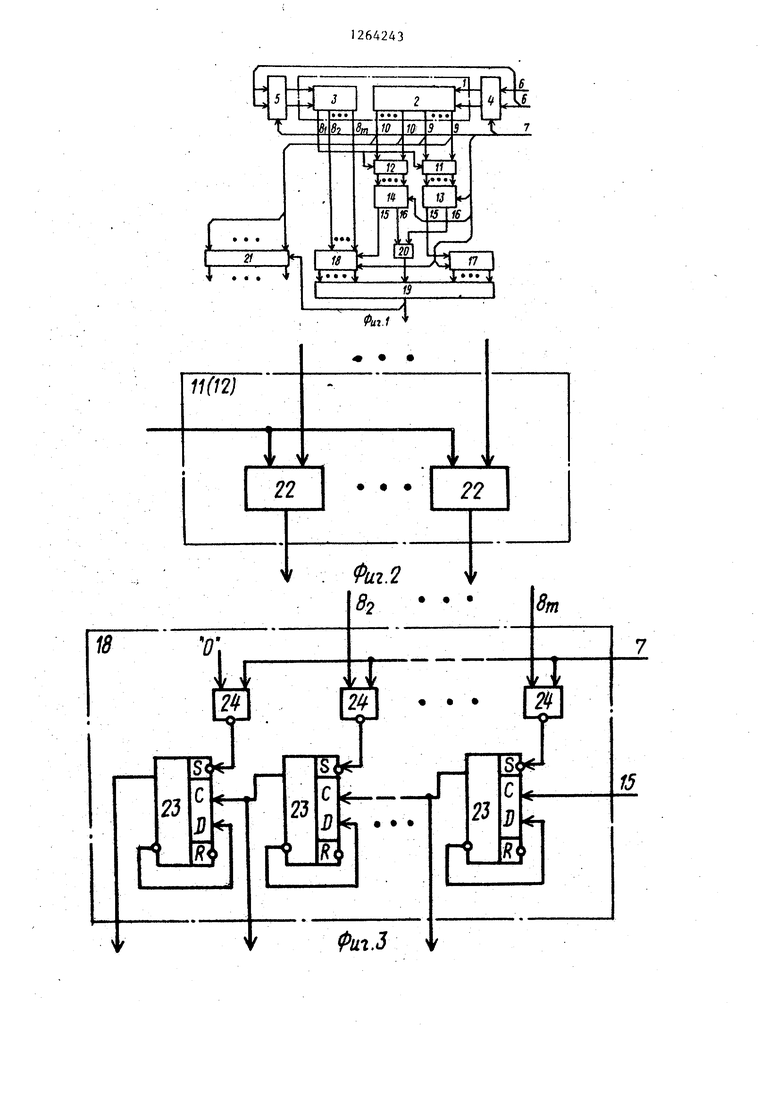

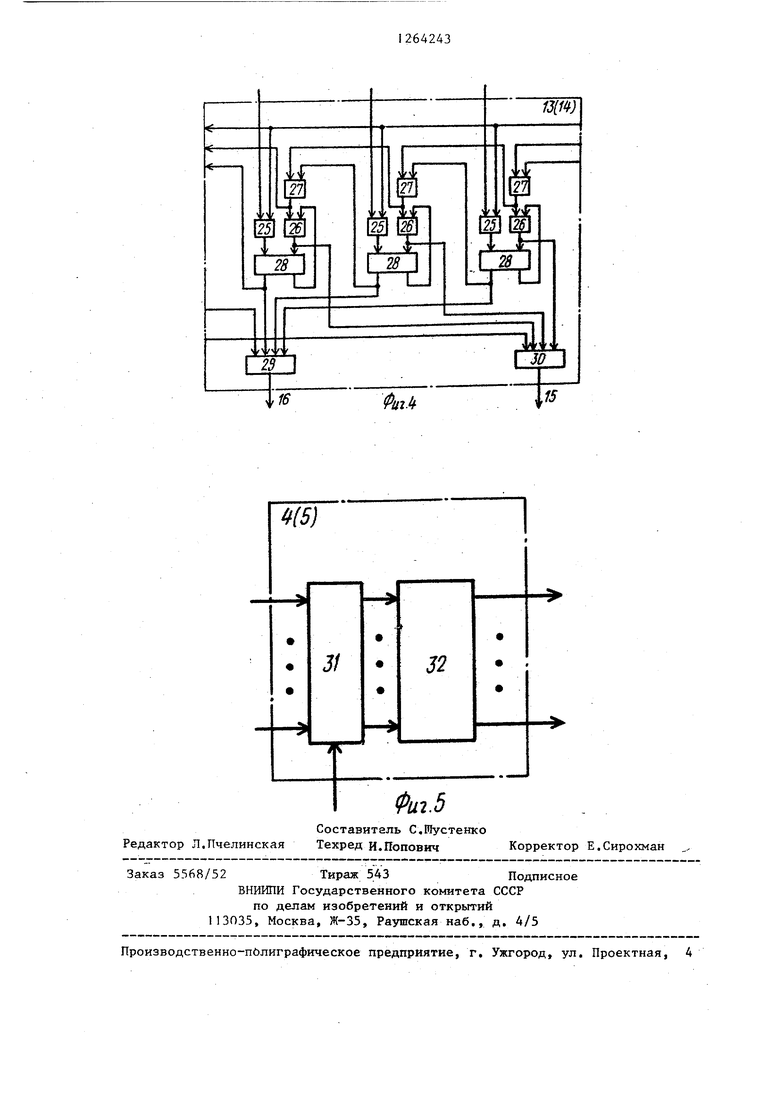

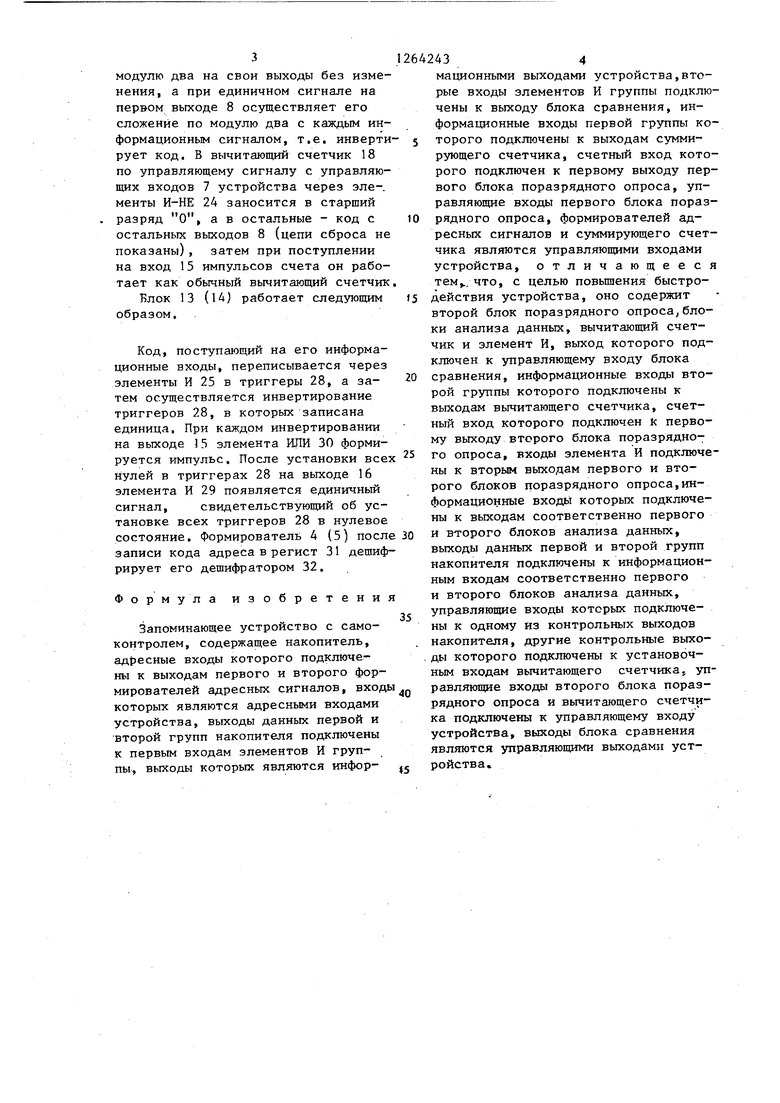

На фиг. 1 представлена структурная схема ЗУ с самоконтролем; на фиг. 2 - схема блока анализа данных; на фиг. 3 - схема вычитающего счетчика-, на фиг, 4 - схема блока поразрядного опроса (ддя трех разрядов); на фиг. 5 - схема формирователя адресных сигналов,

ЗУ с самоконтролем содержит накопитель 1, разбитый на две зоны: информационную 2 и контрольную 3, формирователи 4 и 5 адресных сигналов, адресные входы 6 устройства, управляющие входы 7 устройства, контрольные выходы 8лакопителя, первую 9 и вторую 10 группы информационных выходов накопителя, блоки 11 и 12 анализа данных, блоки 13 и 14 поразрядного опроса с выходами 15 и 16, суммирующий счетчик 17, вычитающий счетчик 18, блок 19. сравнения, элемент И 20 и группу элементов И 21,

Блок 11 (12) анализа образуют сзп маторы 22 по модулю два.

Вычитающий счетчик 18 состоит из триггеров 23 и элементов И-НЕ 24,

Блок 13 (14) поразрядного опроса содержит группы элементов И 25-27, триггеры 28, элемент И 29 и элемент ИЛИ 30.

Формирователь 4 (5) адресных сигналов образуют регистр 31 ад-t реса и дешифратор 32.

Предлагаемое ЗУ работает следующим образом.

По адресу и управляющим сигналам подаваемым на входы устройства из внешней ЦВМ блоки 4 и 5 осуществляют выборку соответствующего информационного слова из информационной зоны 2 и выборку контрольного кода.из контрольной зоны 3 накопителя 1, Контрольный код формируется следующим образом. Если число единиц в информационном слове меньше или равно

5 (п - число разрядов информа;дионного слова), то в первом контрольном разряде (на первом выходе 8) содержится нуль, а в остальньк контроль642432

ных разрядах - код числа единиц в информационном слове. Если же число единиц в информационном слове

п

больше г , то в первом контрольном

разряде содержится единица, а в остальных контрольных разрядах - код числа нулей в информационном слове. Информация с выходов 9 и 10 нако10 пителя 1 подается на входы элементов И 21 и, пройдя через блоки 11 и 12, записывается в блоки 13 и 14 в прямом или инверсном коде в зависимости от сигнала на первом вьпсоде 8,

15 одновременно контрольный код с остальных выходов 8 записывается в счетчик 18, а в старший разряд этого счетчика записывается нуль. Затем осуществляется установка счетчи20 ка 17 в исходное нулевое состояние, а в блоках 13 и 14 осуществляется одновременное инвертирование единичных разрядов. При каждом инвертировании единичного разряда на

выходе 15 блока 14 (13) формируется импульс, который вычитает из содержимого счетчика 18 единицу (прибавляет к содержимому счетчика 17 единицу , т.е. счетчик 17 подсчитьшает

30 количество единиц, записанных в блок 13, а от содержимого счетчика 18 вычитается число единиц, записанных в блок 14. После установкивсех нулей в триггерах блоков 13 и 14 на

35 выходах 6 появляются единичные

сигналы, которые, пройдя через элемент И 20, разрещает прохождение на выход блока 19 результата сравнения счетчиков 17 и 18, При равенстве ко40 дов на входах блока 19 на его выходе формируется сигнал Ощибки нет, который разрешает передачу информации через элементы И 21 на выходы устройства и разрешает формирование

45 следующего адреса, после чего цикл работы повторяется. При каждом неравенстве кодов на входах блока 19 на его выходе вырабатывается сигнал ошибки, который запрещает выдачу

50 информации и запрещает формирование следующего адреса. При четном числе информационных выходов накопителя 1 число выходов 9 и 10 одинаково, при нечетном - число выходов одной

55 из групп 9 или 10 на единицу больше другой, Влок 11 (12) при нулевом сигнале с первого выхода 8 пропуска-, ет информацию через сумматоры 22 по

модулю два на свои выходы без изменения, а при единичном сигнале на первом выходе 8 осуществляет его сложение по модулю два с каждым информационным сигналом, т.е. инверти рует код. В вычитающий счетчик 18 по управляющему сигналу с управляющих входов 7 устройства через эле-, менты И-НЕ 24 заносится в старший разряд О, а в остальные - код с остальных выходов 8 (цепи сброса не показаны), затем при поступлении на вход 15 импульсов счета он работает как обычный вычитающий счетчик

Блок 13 (14) работает следующим образом. .

Код, поступающий на его информационные входы, переписывается через элементы И 25 в триггеры 28, а затем осуществляется инвертирование триггеров 28, в которых записана единица. При каждом инвертировании на выходе 15 элемента ИЛИ 30 формируется импульс. После установки всех нулей в триггерах 28 на выходе 16 элемента И 29 появляется единичный сигнал, свидетельствующий об установке всех триггеров 28 в нулевое состояние, формирователь 4 (5) после записи кода адреса врегист 31 дешифрирует его дешифратором 32.

Форм у л а изобретения

Запоминающее устройство с самоконтролем, содержащее накопитель, адресные входы которого подключены к выходам первого и второго формирователей адресных сигналов, входы которых являются адресными входами устройства, выходы данных первой и второй групп накопителя подключены к первым входам элементов И группы, выходы которых являются информационными выходами устройства,вторые входы элементов И группы подключены к выходу блока сравнения, информационные входы первой группы которого подключены к выходам суммирующего счетчика, счетный вход которого подключен к первому выходу первого блока поразряднспго опроса, управляющие входы первого блока поразрядного опроса, формирователей адресных сигналов и суммирующего счетчика являются управляющими входами устройства, отличающеес тем,., что, с целью повьпления быстродействия устройства, оно содержит второй блок поразрядного опроса,блоки анализа данных, вычитающий счетчик и элемент И, выход которого подключен к управляющему входу блока сравнения, информационные входы второй группы которого подключены к выходам вычитающего счетчика, счетный вход которого подключен к первому выходу второго блока поразрядного опроса, входы элемента И подключены к вторым выходам первого и второго блоков цоразрядного опроса,информационные входь которых подключены к выходам соответственно первого и второго блоков анализа данных, выходы данных первой и второй групп накопителя подключены к информационным входам соответственно первого и второго блоков анализа данных, управляющие входы которьгх подключены к одному из контрольных выходов накопителя, другие контрольные выходы которого подключены к установочным входам вычитающего счетчика управляющие входы второго блока поразрядного опроса и вычитающего счетчика подключены к управляющему входу устройства, выходы блока сравнения являются управляющими выходами устройства.

б

ti

Ш

WL

tf

Ч .. .

16

15

« ,yr--X

Ш

iiiJfcrZ 1 4«.

1Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1980 |

|

SU928423A1 |

| Динамическое запоминающее устройство с самоконтролем | 1982 |

|

SU1022224A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1363312A1 |

| Оперативное запоминающее устройство с самоконтролем | 1982 |

|

SU1042081A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1104588A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1100638A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1188784A1 |

| Запоминающее устройство с коррекцией ошибок | 1980 |

|

SU942160A2 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1094071A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249592A1 |

Изобретение относится к запоминающим устройствам и может быть использовано в запоминающих устройствах с высокой достоверностью функционирования . Цель изобретения повьшение быстродействия устройства. Запоминающее устройство с самоконтролем содержит накопитель, два формирователя адресных сигналов, группу элементов И, два блока анализа и инвертирования, два блока поразрядного опроса, счетчик, вычитакшцш счетчик, элемент И и схему сравнения, информационные выходы накопителя делятся на две одинаковые группы и подаются через блоки анализа и инвертирования в прямом или инверсном виде в зависимости от первого контрольного выхода на блоки поразрядного опроса. Группа контрольных выходов накопителя, кроме первого выхода, соединена с входами вычитающего счетчика, первые выходы первого и второго блоков поразрядного опроса соединены соответственно со (Л счетным входом счетчика и вычитающего счетчика, выходы которых соединены с входами схемы сравнения. Данное устройство благодаря блокам анализа и инвертирования блокам поразрядного опроса и вычитающему счетчику позволяет повысить быстродействие устройства в два раза. 5 ил.

J/

J2

| Авторское свидетельство СССР № 922877, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU928423A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-10-15—Публикация

1985-05-17—Подача