Изобретение относится к запоминающим устройствам.

Известно запоминающее устройство, содержащее главную память, блок контроля данных и дополнительную память, где неисправные ячейки главной памяти обнаруживаются блоком контроля данных, который присваивает им адреса замещения в дополнительной памяти, причем обращение по этим адресам происходит каждый раз при обращении к соответствующим ячейкам главной Пс1мяти, а использование данных на выходе главной и дополнительной памяти определяет вентильная схема .в зависимости от адресного обращения к работающей или неисправной ячейке главной памяти 1.

Недостатком этого устройства является низкая надежность, вследствие одновременного обращения к главной и дополнительной памяти при отказе ячейки главной памяти и отсутствия контроля и защиты данных, запомненных в дополнительной памяти, а также увеличение затрат машинного времени вследствие одновременного обращения к главной и дополнительной памяти.

Наиболее близким к изобретению является запоминающее устройство с контролем данных, содержащее блок управления, арифметический блок, блок обнаружения и коррекции ошибок, первый, второй и третий регистры, причем вход блока обнаружения и коррекции ошибок соединен со входом устройства, первый выход - с первым

10 входом третьего регистра, второй выход - со входом блока управления и первым входом арифметического блока, второй вход которого подключен к первому выходу блока управления, третий

15 вход; -к выходу третьего регистра, первый выход - ко входу первого ре-, гистра, выход которого соединен с первым выходом устройства (. 2j.

Недостатками этого устройства

20 являются низкая его надежность в свя зи с необ одимостью проведения коррекции одной и той же ошибки при каждом обращении по адресу, содержащему ошибку, и кроме того, увеличен25ные затраты машинного времени.

Цель изобретения - повышение надежности запоминающего устройства.

Поставленная цель достигается тем, что в запоминающее устройство

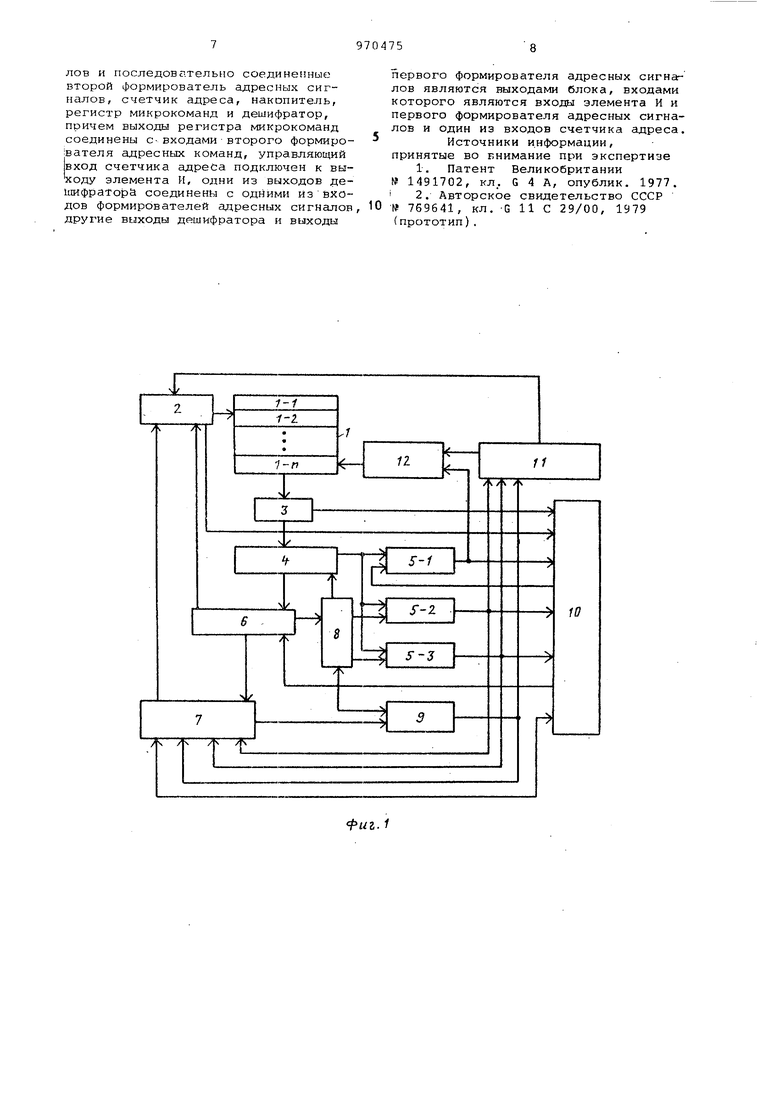

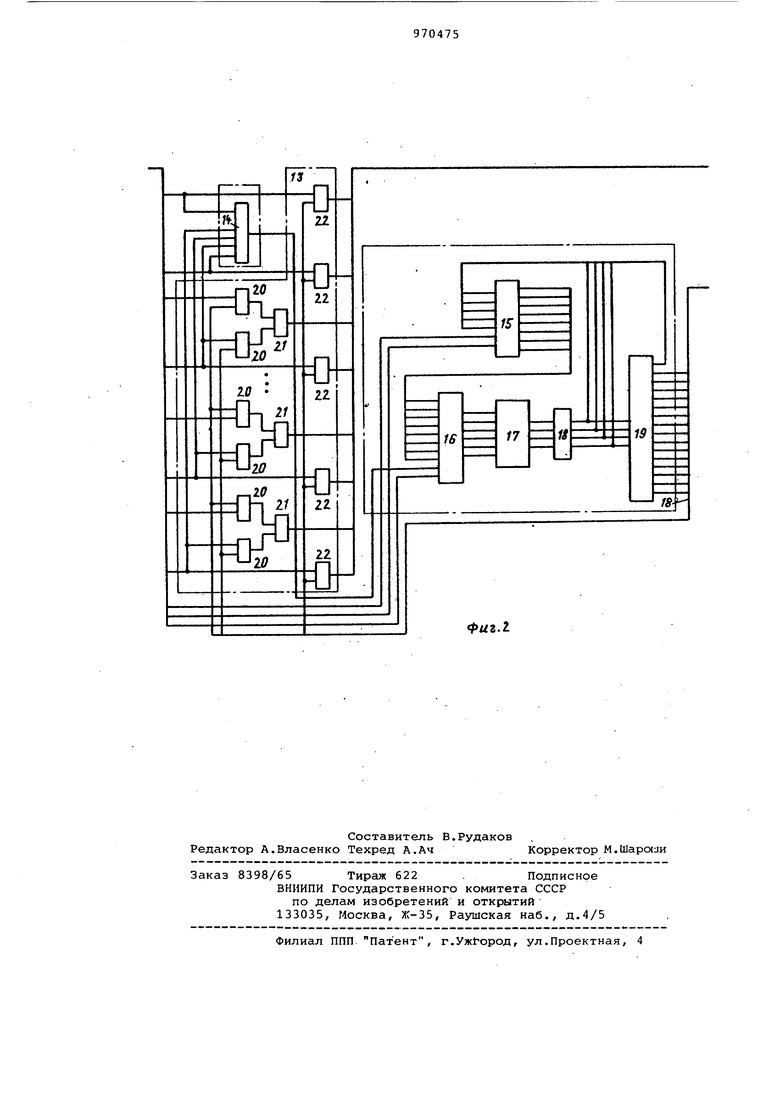

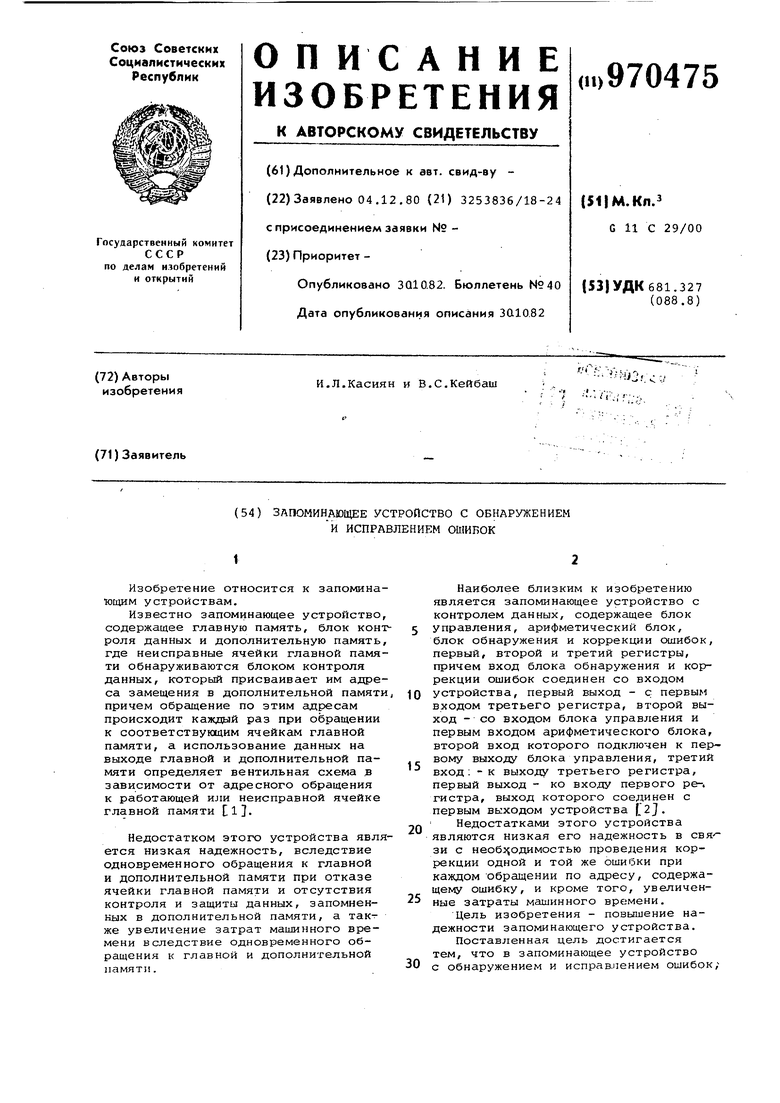

30 с обнаружением и исправлением ошибок; содержащее регистр адреса, накопитель, выходной регистр, блок обнаружения ошибок, буферные регистры и арифметический блок, причем выходы регистра адреса подключены к одним из входов накопителя, информационные выходы которого подключены ко входам выходного регистра, первый выход которого сое.динен с первым входом блока обнаружения ошибок, одни из входов арифметического блока подключены соответственно ко второму выходу выходного регистра и выходам буферных регистров, первые входы которых соединены с первым выходом блока обнаружения ошибок, один из выходов арифметического блока соединен со вторым входом первого буферного регистра, введены селектор, счетчик ошибок, счетчик циклов, блок местного управления, формирователь сигналов блокировки и формирователь сигналфв записи, причем первый вход селектора соединен со вторым выходом блока обнаружения ошибок, второй вход которого подключен к одному из выходов счётчика оишбок, другие выходы которого соединены со вторыми входами второго и третьего буферных регистров, входы регистра адреса подключены к первым выходам селектора, блока местного управления и формирователя сигналов Ь окировки,второй и третий выходы селектора соединены соответственно с первым входом счетчика ошибок и одним из входов блока местного управления, второй вы ход которого соединен с первым входом счетчика циклов, третий выход блока местного управления подключен к другому, входу арифметич€;ского блока, другой выход которого соединен со вторыми входами счетчика циклов, счетчика ошибок и селектора, второй выход формирователя сигналов блокировки подключен к первому входу фор: ;лирователя сигналов записи, второй вход которого соединен с выходом первого буферного регистре, а выход подключен к другому входу накопителя, выходы второго и третьего буфер ных регистров и счетчика циклов сое динены соответственно со входами формирователя сигналов блокировки и другими Входами блока местного управления. Блок местного управления содер:;,ит элемент И, первый формирователь адресных сигналов и последовательно соединенные второй формирователь ад ресных сигналов, счетчик адреса, накопитель, регистр микрокоманд и дешифратор, причем выходы регистра микрокоманд соединены со входами вт рого формирователя адресных команд, управляюи1Ий вход счетчика адреса по ключен к выходу элемента И, одни из выходов дешифратора соединены с одними из входов формирователей адресных сигналов, другие выходы дешифратора и выходы первого формирователя адресных сигналов являются выходами блока, входами которого являются входы элемента И и первого формирователя адресных сигналов и один из входов счетчика адреса. На фиг.1 изображена структурная электрическая схема запоминающего устройства с обнаружением и исправлением ошибок; на фиг.2 - структурная электрическая схема блока местно го управления. Устройство (фиг.1) содержит накопитель 1, состоящий из нескольких зон 1-1, 1-2, 1-п (где п - целое число), одна из которых резервная, регистр 2 адреса, выходной регистр 3, блок 4 обнаружения ошибок, первый 5-1, второй 5-2 и третий 5-3 буферные регистры, селектор б, блок 7 местного управления, счетчик 8 ошибок, счетчик 9 циклов, арифметический блок 10, формирователь 11 сигналов блокировки, формирователь 12 сигналов лаписи. Блок 7 местного управления (фиг.2) содержит первый формирователь 13 адресных сигналов, элемент И 14, второй формирователь 15 адресных сигналов, счетчик адреса 16, накопитель 17, регистр 18 микрокоманд и дешифратор 19. Формирователь 13 содержит, в свою очередь, элементы И 20, элементы ИЛИ 21 и элементы И 22. Устройство работает следующим образом. Накопитель 1 выполнен в виде нескольких зон 1-1, 1-2, 1-п, каждая из которыхсодержит определенное число слов и имеет контрольный код, запомненный по фиксированному адресу, а по разрядам контрольных кодов в свою очередь определяется их контрольный код и также запоминается по фиксированному адресу. Одна из зон памяти выполнена резервной, емкость резервного поля памяти определяется по интенсивности отказов элементов памяти и периода машинного времени между вмешательствами извне (например, замена отказавших элементов при технологических обслуживаниях) или всего требуемого фонда Мсцаинного времени, если вмешательства извне невозможны. При отсутствии ошибки в считанном слове блок 4 обнаружения ошибок не возбуждается, и слово с выходного регистра 3 через арифметический блок 10 поступает по назначению программы. При обнаружении ошибки в считанном слове блок 4 запоминает адрес ошибочного слова в регистре 5-2 и передает управление селектору 6, который принимает решение о х.л; актгре ошибки - сбой или отказ, например многократным считыванием.

В случае отказа селектор 6 устана ливает счетчик 8 ошибок в положение один и передает управление блоку 7 который осуществляет считывание контрольного кода именно той зоны памяти где произошел отказ, помещает его в регистр 5-1, устанавливает содержимое счетчика 9 циклов 4, равное числу слов зоны (0), и поочередно в порядке возрастания (убывания) считывает все слова зоны.

Арифметический блок 10 вычитает содержимое выходного регистра 3 из содержгмого регистра 5-1 и результат Помещает в регистр 5-1. Перед чтением слова арифметический блок 10 сравнивает адрес слова с содержпнием регистра 5-2 (адрес ошибочного слова и в случае их совпадения изменяет адрес очередного слова на единицу в порядке возрастания (убывания) адресов. Таким образом, обраицение по адресу ошибочного слова не происходит . Содержимое сметчика 9 циклов изменяется в порядке убывания (возрастания) и при считывании всех слов в зоне и их вычитании из контрольног кода в регистре 5-1 находится правильное значение ранее ошибочного считанного слова, т.е. восстановленное слово. При этом по содержимому счетчика 9 циклов управление передается формирователю 11, который через формирователь 12 разрешает запись содержимого регистра 5-1 (восстановленного слова) в резервной зоне памяти, присваивает ему гщрес отказавшего слова, блокирует дальнейшее обращение по отказавшему адресу в зоне памяти и передает управление приостановленной программы.

В случае обнаружения ошибок при считывании одного из контрольных кодов , селектор б точно также определяет характер ошибки - сбой или отказ, и в случае отказа устанавливает счетчик 8 ошибок в состояние два ошибка в контрюльном коде, адрес ошибочного контрольного кода при этом запоминается в регистре 5-3, и передает управление блоку 7. Последний организует точйо такой же процесс, с отличительной разницей считывания контрольного кода контрольных кодов и устанавливает счетчик9 циклов равным числу контрольньох кодов. После восстановления контрольного кода счетчик 8 ошибок устанавливается в состояние один, счетчик 9 циклов равным числу слов в зоне (0 и выполняется процесс восстановления

слова.

Технико-экономическое преимущество предлагаемого устройства состоит в том, что оно способно исправлять столько обнаруженных ошибочных слов.

сколько их можно запомнить в резервной sowe памяти.

Формула изобретения

1.Запоминающее устройство с обнаружением и исправлением ошибок, содержащее регистр адреса, накопитель, выходной регистр, блок обнаружения .ибок, буферные регистры и

0 арифметический блок, причем выходы регистра адреса подключены к одним из входов накопителя, информационные выходы которого подключены к входам выходного регистра, первый выход которого соединен с первым входом бло5ка обнаружения ошибок, одни из входов арифметического блока подключены соответственно к второму выходу выходного регистра и выходам буферных регистров, первые входы которых

0 соединены с первым выходом блока обнаружения ошибок, один из выходов арифметического блока соединен с вторым входом первого буферного регистра, отличающееся тем,

5 что, с целью повышения надежности, в него введены селектор, счетчик ошибок, счетчик циклов, блок местного управления, формирователь сигналов блокировки и формирователь сигналов

0 записи, причем первый вход селектора соединен с вторым выходом блока обнаружения ошибок, второй вход которого подключен к одному из выходов счетчика схиибок, другие выходы кото5рого соединены с вторыми входами второго и третьего буферных регистров , входы регистра адреса подключены к первым выходам селектора, блока местного управления и формирователя

0 сигналов блокировки, второй и третий выходы селектора соединены соответственно с первым входом счетчика ошибок и одним из входов блока местгного управления, второй выход которого соединен с первым входом счетчи5ка циклов, третий выход блока местного управления подключен к другому входу арифметического блока, другой выход которого соединен с вторыми входами счетчика циклов, счетчика

0 ошибок и селектора, второй выход формирователя сигналов блокировки подключен к первому входу формирова.-. теля сигналов записи, второй вход которого соединен с выходом первого

5 буферного регистра, а выход подключен к другому входу накопителя, выходы второго и третьего буферных регистров и счетчика циклов соединены соответственно с входами формиро0вателя сигналов блокировки и другими входами блока местного управления.

2.Устройхгтво ПОП.1, отличающееся тем, что блок местного управления содержит элемент И,

5 первый формирователь адресных сигналов и последовательно соединенные второй формирователь адресных сигналов, счетчик адреса, накопитель, регистр микрокоманд и дешифратор, причем выходы регистра микрокоманд соединены с-входами второго формиро1вателя адресных команд, управляющий вход счетчика адреса подключен к выходу элемента И, одни из выходов деишфратора соединены с одними Изйходов формирователей адресных сигналов другие выходы дешифратора и выходы

первого формирователя адресных сигнаг лов являются выходами блока, входами которого являются входы элемента И и первого формирователя адресных сигналов и один из входов счетчика адреса.

Источники информации,

принятые во внимание при эксперти:зе

1. Патент Великобритании 1491702, кл,. G 4 А, опублик. 1977. 2. Авторское свидетельство СССР

№ 769641, кл. -С 11 С 29/00, 1979 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с коррекцией ошибок | 1980 |

|

SU942160A2 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| УСТРОЙСТВО ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ ЦИФРОВОЙ ИНФОРМАЦИИ | 1992 |

|

RU2039382C1 |

| Устройство для коррекции ошибок в информации | 1986 |

|

SU1372365A1 |

| Устройство для обнаружения и коррекции ошибок | 1986 |

|

SU1372367A1 |

| Устройство для сопряжения памяти с процессором | 1982 |

|

SU1136176A1 |

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

| Процессор с микропрограммным управлением | 1975 |

|

SU525956A1 |

Авторы

Даты

1982-10-30—Публикация

1980-12-04—Подача