СО

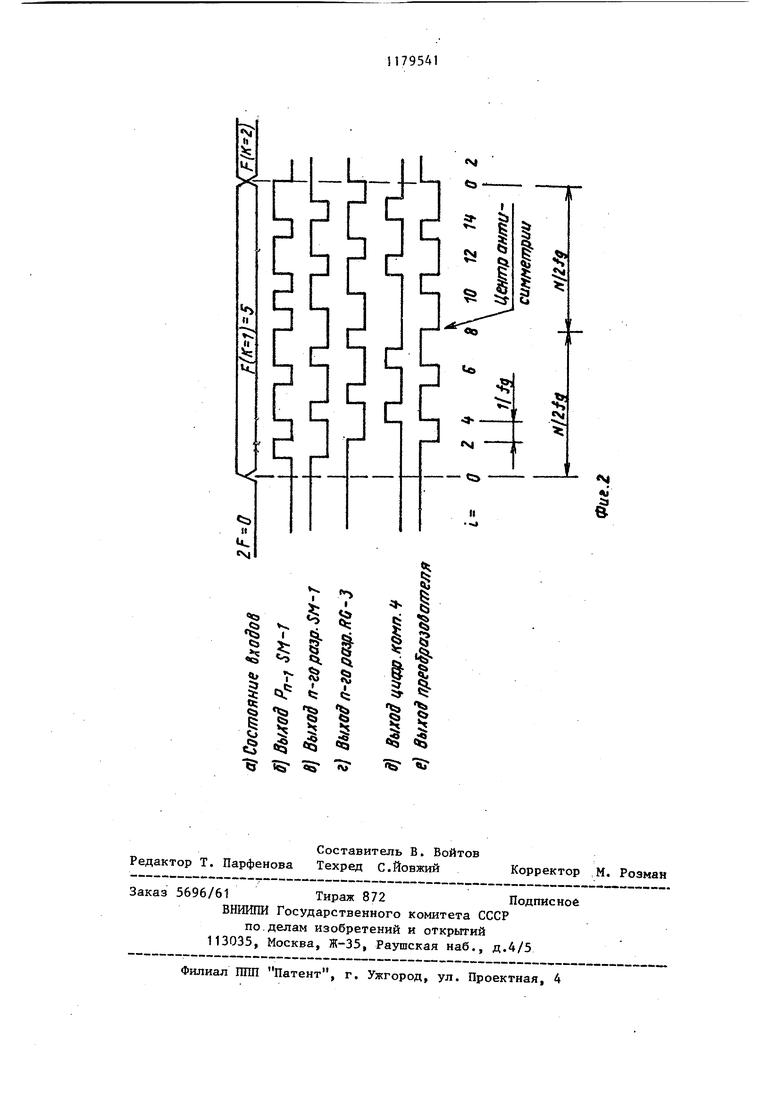

Stijroff. 1 Изобретение относится к вычис- лительной технике и может быть использовано при построении устройст для формирования бинарньЬс сигналов с частотной манипуляцией и нулевой начальной фазой импульсных посьток Цель изобретения .- повьпиение точности. Поставленная цель достигается при формировании сложных сигналов за счет привязки нулевой фазы к началу частотной посылки. На фиг. 1 изображена структурна схема преобразователя; на фиг. 2 временные диаграммы, поясняющие ег работу. Преобразователь содержит комбинационный сумматор 1, п-1 входов первой группы (А). которого подклю чены к соответствующим входным шинам 2 , а п входов второй группы (В) - к соответствующим выходам регистра 3. Входы регистра 3 подключены к соответствующим выходам комбинационного сумматора 1. Вход переноса младшего разряда (С) ком бинационного сумматора 1 подключен к общей шине. Выход переноса (п-1)-го разряда комбинационного сумматора 1 подключен к входу разрешения,сравн ния цифрового компаратора 4, выход которого подключен к первому входу сумматора 5 по модулю два, второй вход которого соединен с выходом п-го разряда регистра 3, с тактовой шиной 6, а выход является выходной шиной 7. п-1 входов первой группы (А) цифрового комапартора подключен к соответст вующим выходам комбинационного сум матора 1, каждый i-ый вход второй группы (В), где i 1,2, . .. ,п-2 к соответствующему (1+1)-му входу первой группы комбинационного сумматора 1, (п-1)-ый вход второй группы - к общей шине, а вход разрешения сравнения (С) - к выходу переноса (п-1)-го разряда (Pj. ) комбинационного сумматора 1, вход переноса младшего разряда (CQ) которого подключен к общей шине, п-ы вход первой группы - к шине логиче кой единицы 8. Преобразователь работает следую щим образом. В исходном положении на такто вую шину 6 Поступают импульсы с 12 частотой следования fд.. На входных шинах,2 установлен нулевой код. Выходы комбинационного сумматора 1 и регистра 3 не изменяют своего состояния и устойчиво удерживается двоичное число (1,0,0,...,0). Выход переноса п-1 разряда находится в нулевом состоянии, и цифровой компаратор 4 закрыт. В некоторый момент времени на входных шинах 2 устанавливается некоторое нечетное число, что соответствует установке числа F-1 на входах А компаратора 4, при этом под действием тактовых импульсов по каждому шагу состояние выходов комбинационного сумматора 1 увеличивается на число F. В тот момент, когда состояние выходов комбинационного сумматора (1+i)F превысит величину 2 , где i - порядковый номер следования импульсов с момента установки числа F, на выходе переноса (п-1)-го разряда Р f, устанавливается единица, открывающая цифровой компаратор 4, п-ый разряд комбинационного сумматора 1 переходит в нулевое состояние, и цифровой компаратор 4 сравнивает число (1-i-i)F-2 определенное п-1 разрядами входов А с числом установленным на входах В. Если число на входах А больше числа на входах В цифрового компаратора 4, то его выход устанавливается в единичное состояние, и на выходе сумматора 5 в результате получается состояние, противоположное состоянию вь1ходного п-го разряда регистра 3. Если же число на входах А меньше или равно числу на входах В цифрового компаратора 4, . то, соответственно, его выход устанавливается в нулевое состояние, и jHa выходе сумматора 5 получаем состояние, совпадающее с состоянием выходного п-го разряда регистра 3. По (1+2)-му импульсу выход переноса (п-1)-го разряда Р,,/) устанавливается в нулевое состояние и цифровой компаратор 4 запирается, а на выходной шине 7 устанавливается нулевой потенциал, соответствующий состоянию п-го разряда регистра 3. Далее Состояние комбинационного сумматора 1 снова увеличивается до

появления единицы переноса (п-1)-г6 разряда; при этоМ состояние п-го разряда комбинационного сумматора 1 изменяется на противоположное и цифровым компаратором 4 производится коррекция смены состояния по выходу преобразователя. После про хождения 2 импульсов состояние комбинационного сумматора 1 равно исходному, и при смене кодй на входных шийах 2 новая бинарнаяпоследовательность начинается с нулевой фазы.

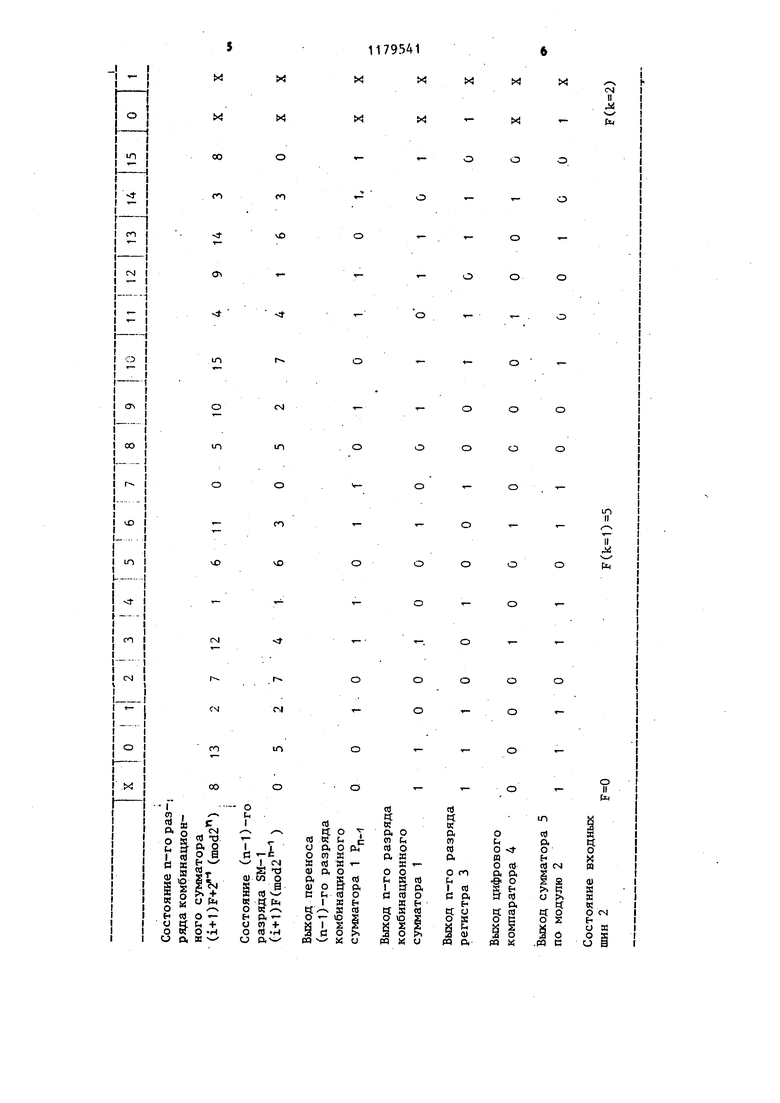

Пример. В таблице приведены состояние выходов прёобразователя, по данйым которой построены временные диаграммы работы устройства (фиг. 2).

Как-ВИДНО из диаграммы фиг. 2е, выходнай бинарная последовательность характеризуется нечетной симметрией

. , i . ,N-1. у(.) -у(),

-% в то время как на фиг. 2г бинарная пocлeдoвaтehьнocть, получаемая в

случае использования устр&йства-прототипа, асимметрична. -

Преобразование Фурье такой последовательности (фиг. 2е) Имеет только синусоидальные составляюн(ие, слтедовательно, начало импульсной посыпки соответствует нулевой фазе. При этом амплитуда частотной составfп F/2 может быть сшляющей fp ределена из формулы

2

где N - наибольший общий делитель

F и N.

Как видно из формулы, если F и И числа взаимно простые, то есть F нечетное число и N 1, при S(f5) практически не зависит от F,

и паразитная амплитудная модуляция отсутствует.

Если F четное, на входах А компаратора 4 устанавливается число F/2, и амплитуда основной составляющей

«

уже при |,

4 отличается от всего на 3%.

vi

«и

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь | 1979 |

|

SU974570A1 |

| Цифровой фазовый модулятор | 1983 |

|

SU1184081A1 |

| Генератор псевдослучайных узкополосныхСигНАлОВ | 1979 |

|

SU840897A1 |

| Преобразователь код-частота | 1984 |

|

SU1233285A1 |

| Устройство для умножения | 1981 |

|

SU1024906A1 |

| Аналого-цифровой преобразователь последовательного приближения | 1985 |

|

SU1248067A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1117655A1 |

| Устройство для вычисления выражения вида @ | 1989 |

|

SU1644135A1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1991 |

|

SU1826835A1 |

| Преобразователь код-частота | 1981 |

|

SU966890A1 |

ПРЕОБРАЗОВАТЕЛЬ КОД - ЧАСТОТА, содержащий комбинационный сумматор, п-1 входов первой группы которого являются соответствующими входными шинами, а п входов второй группы подключены к соответствующим п выходам регистра, вход синхронизации которого подключен к тактовой шине, отличающийся тем, что, с целью повьшения точности, в него введены цифровой компаратор и сумматор по модулю два, выход которого является выходной шиной, а входы подключены соответственно к п-му выходу регистра и к выходу цифрового компаратора, п-1 входов первой группы которого подключены к соответствующим п-1 выходам комбинационного сумматора, каждьй т-й вход второй группы, где i 1,2,...,п-2, объединен с соответствующим (i+1)-M входом первой группы комбинационного сумматора, ()-й вход второй группы подключен к общей шине, а вход разрешения сравнения - к выхоа 9 ду переноса (n-l)-ro разряда комбинационного сумматора, вход (О реноса младшего разряда которого подключен к общей шине, п-й вход первой группы - к шине логической единицы, а t выходов - к соответствующим г входам регистра.

| Орнатский run | |||

| Автоматические измерения и приборы | |||

| Киев, 1980, с | |||

| ДВОЙНОЙ ГАЕЧНЫЙ КЛЮЧ | 1920 |

|

SU288A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Преобразователь код-частота | 1981 |

|

SU966890A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

Авторы

Даты

1985-09-15—Публикация

1983-10-03—Подача