Изобретение относится к вычислительной технике и предназначено для использования в системах цифровой обработки информации.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения вычислений при нечетном значении числа коэффициентов.

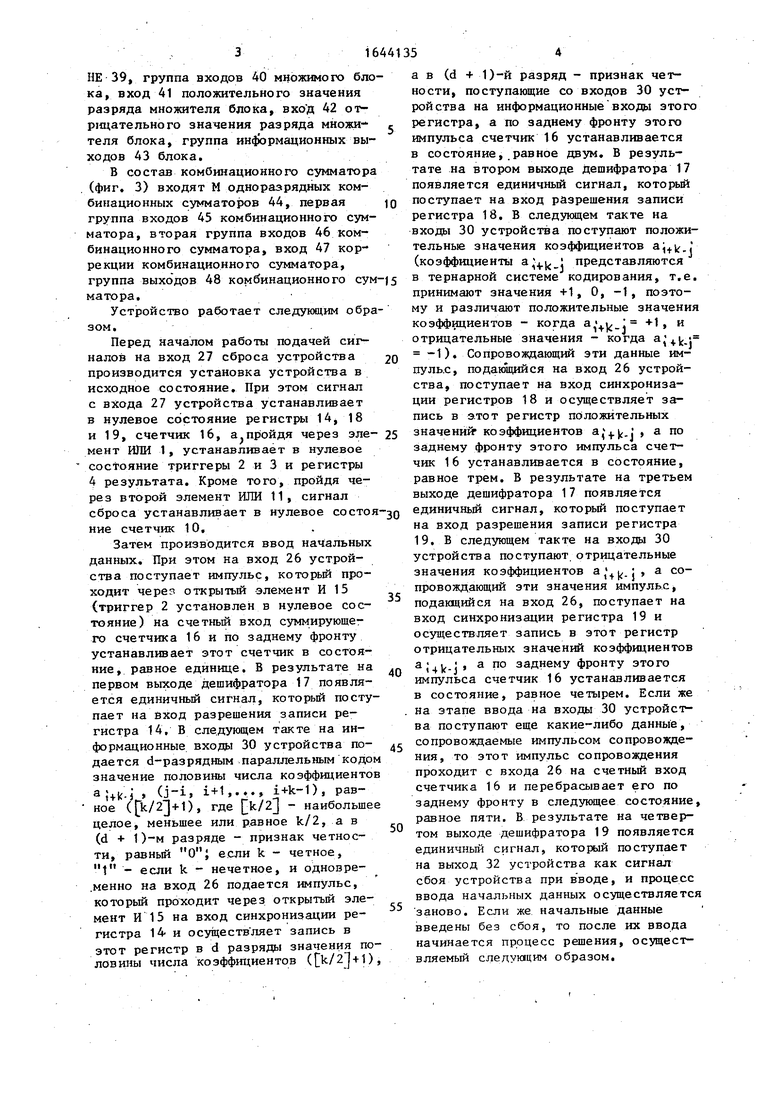

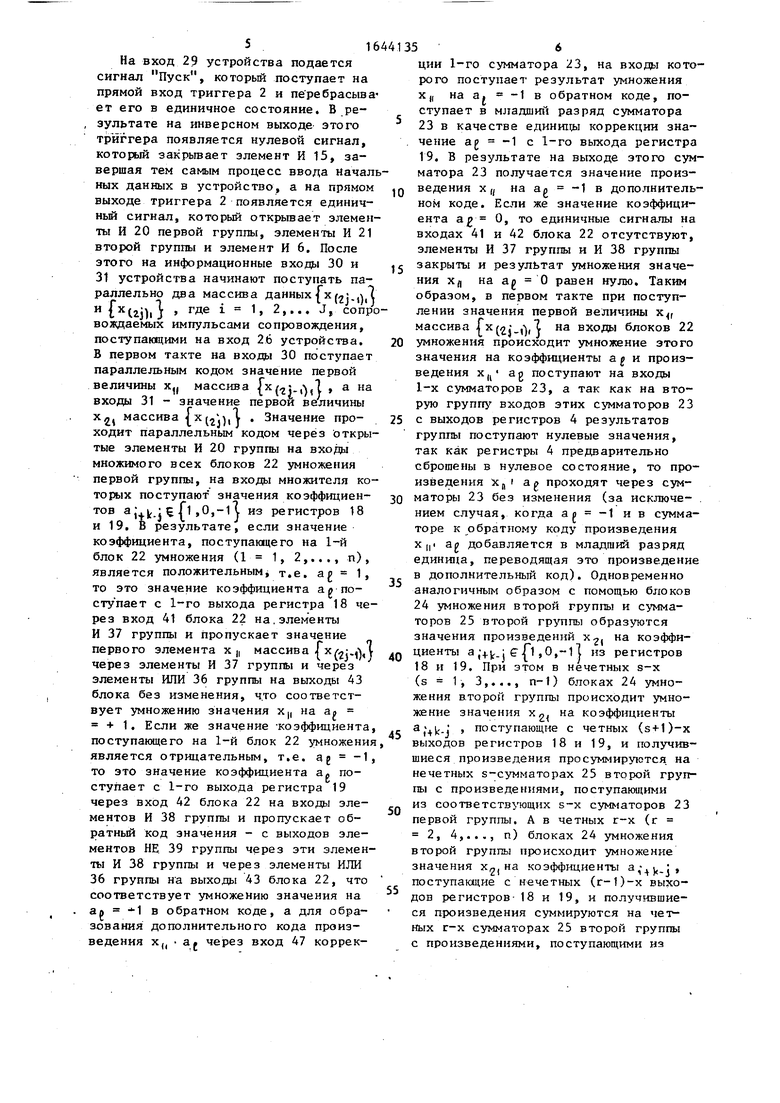

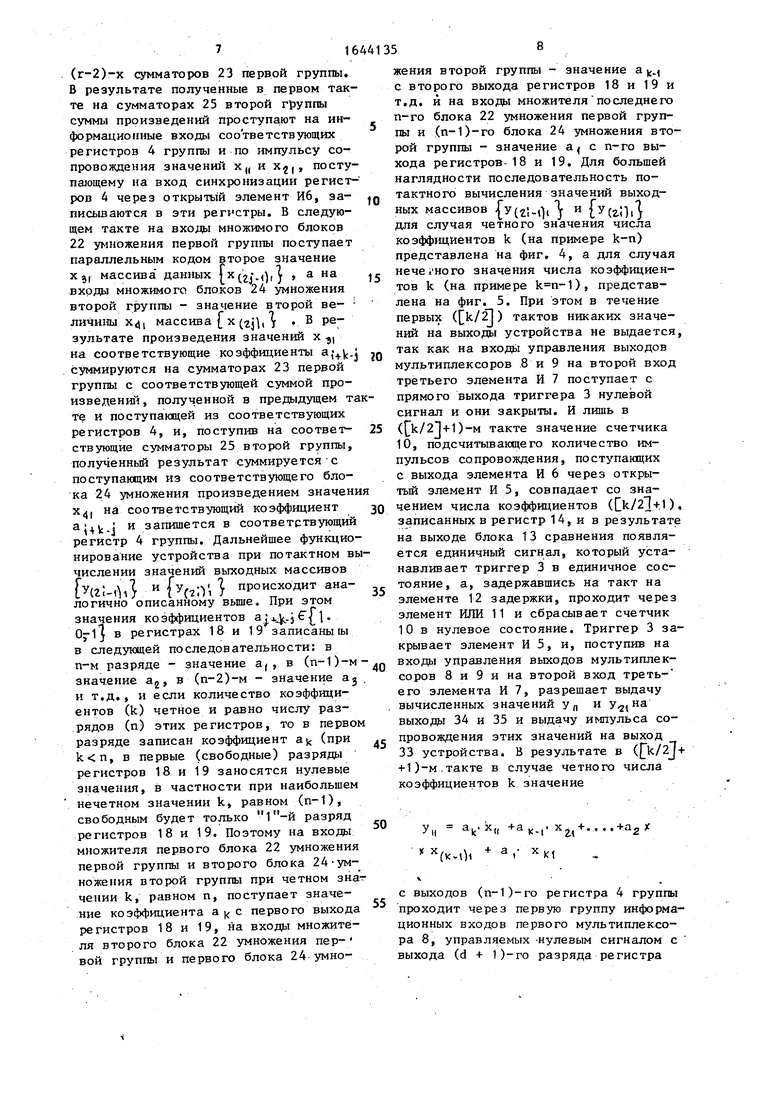

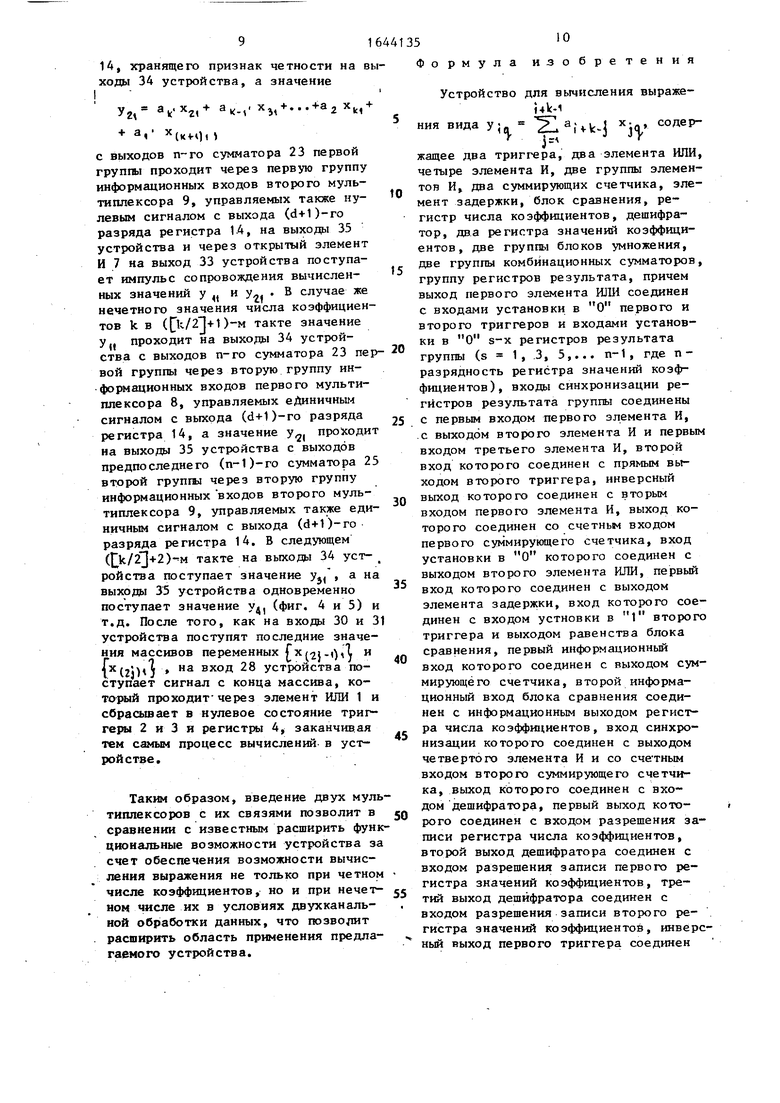

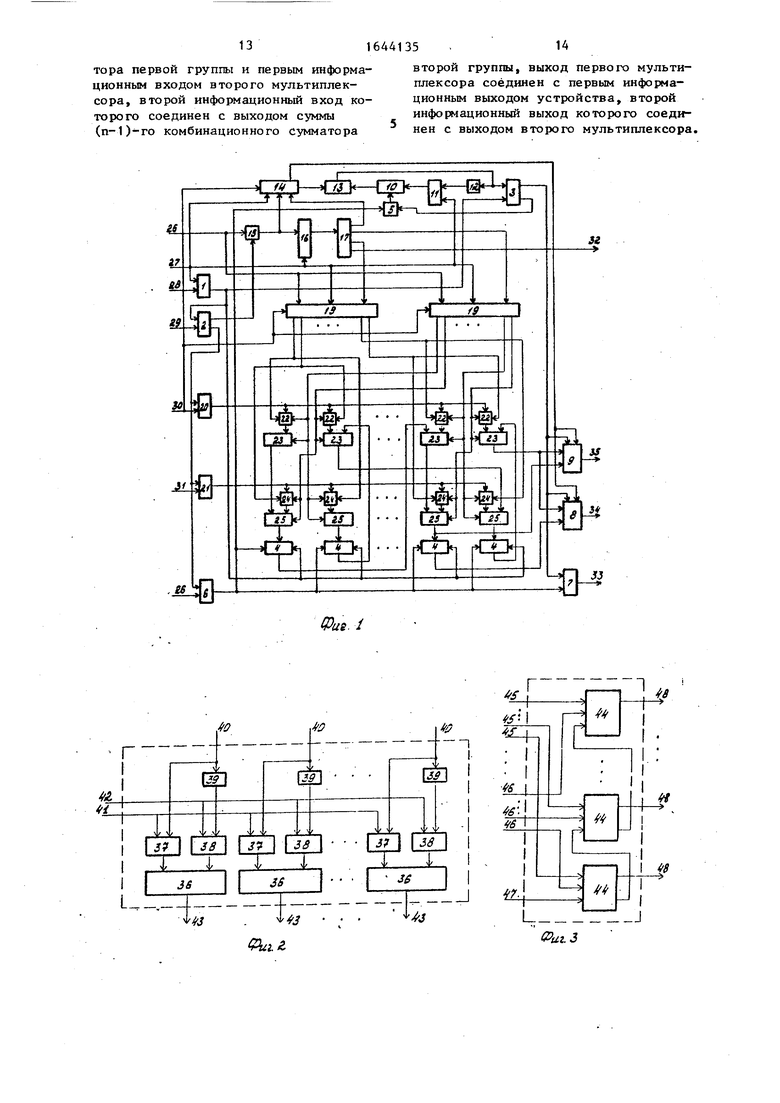

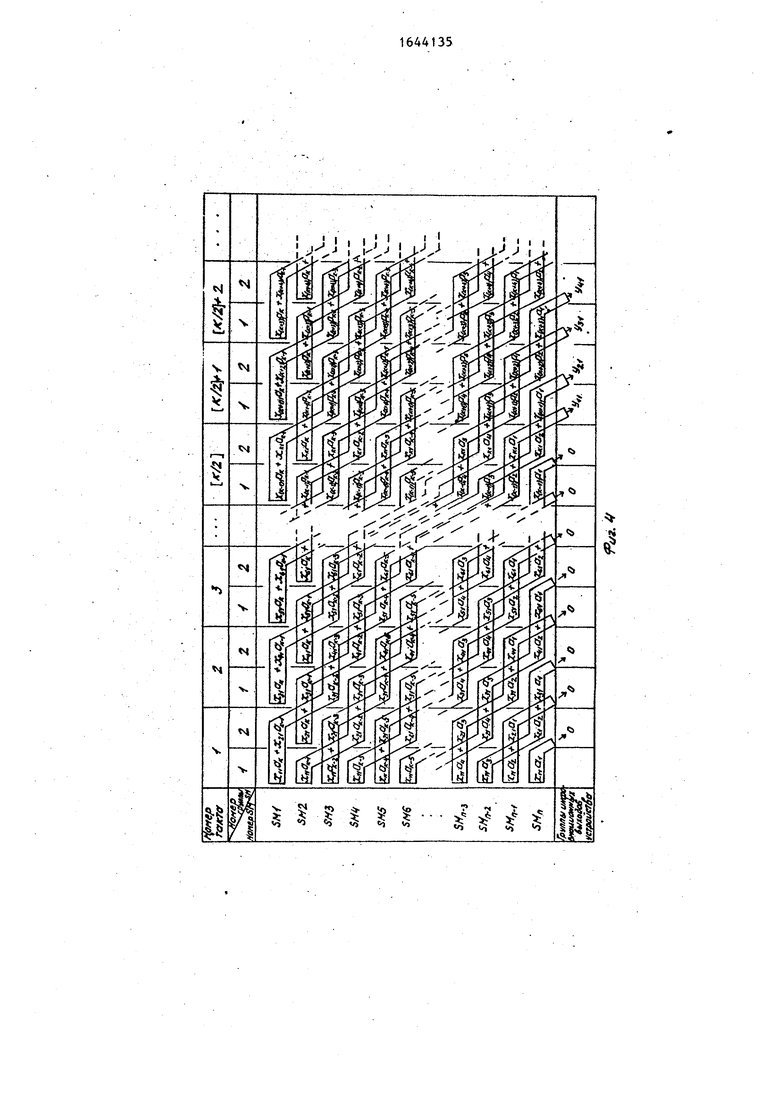

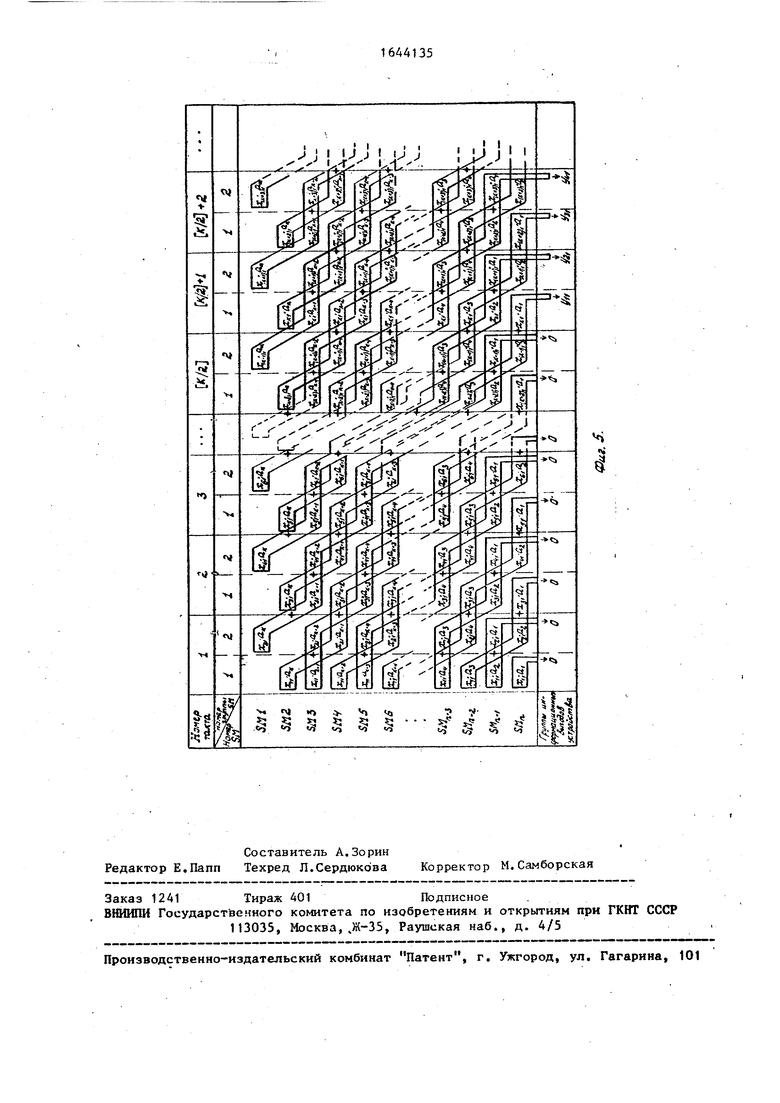

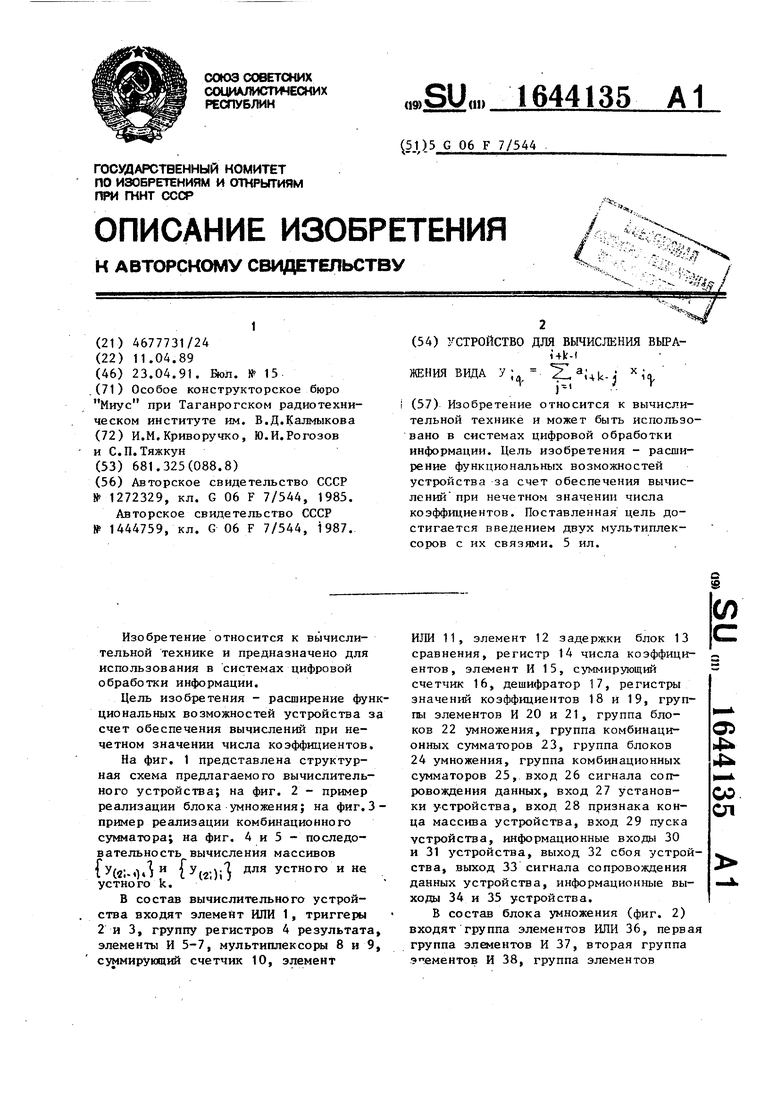

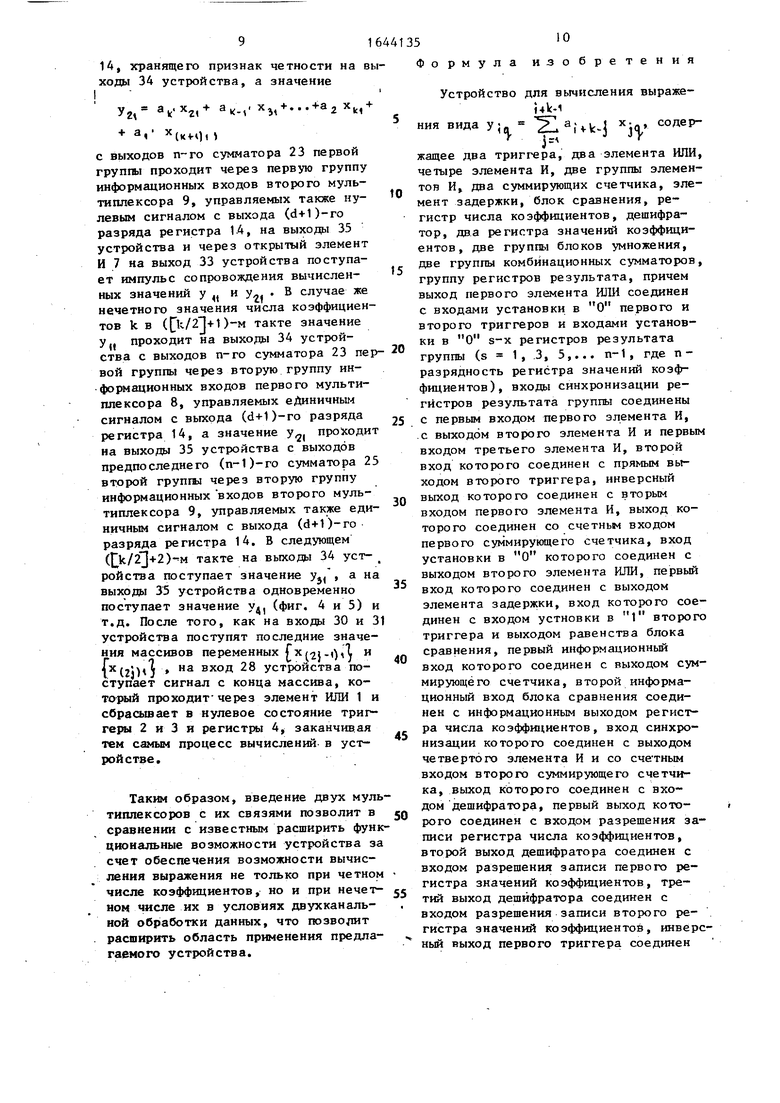

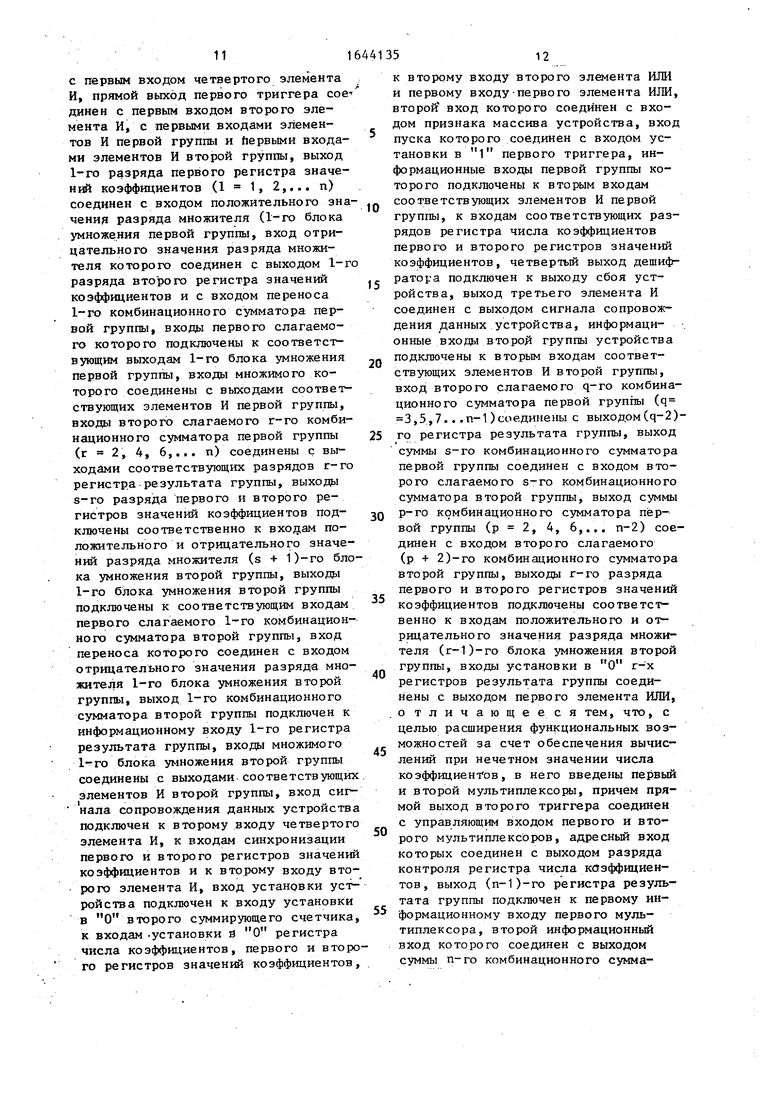

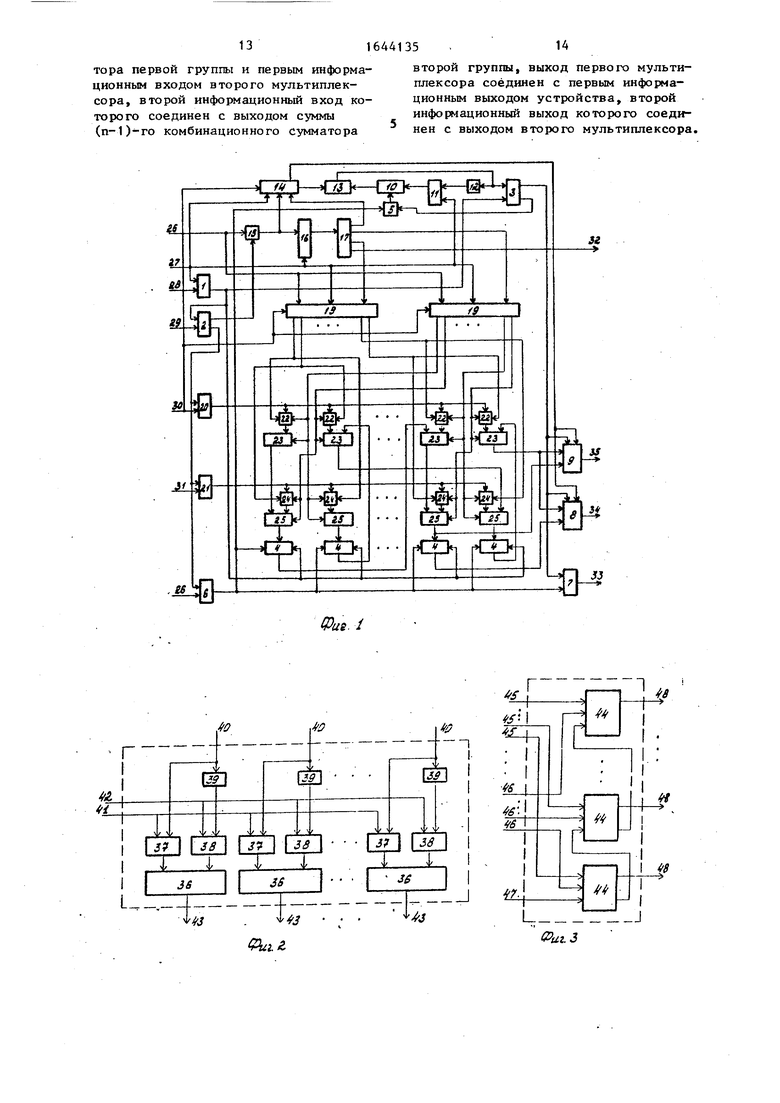

На фиг. 1 представлена структурная схема предлагаемого вычислительного устройства; на фиг. 2 - пример реализации блока умножения; на фиг.З- пример реализации комбинационного сумматора; на фиг. 4 и 5 - последовательность вычисления массивов

{У(в:..)Ли fy(2-,)i яля УСТНОГО и не

устного k.

В состав вычислительного устройства входят элемент ИЛИ 1, триггеры 2 и 3, группу регистров 4 результата, элементы И 5-7, мультиплексоры 8 и 9, суммирующий счетчик 10, элемент

ИЛИ 11, элемент 12 задержки блок 13 сравнения, регистр 14 числа коэффициентов, элемент И 15, суммирующий счетчик 16, дешифратор 17, регистры значений коэффициентов 18 и 19, группы элементов И 20 и 21, группа блоков 22 умножения, группа комбинационных сумматоров 23, группа блоков 24 умножения, группа комбинационных сумматоров 25, вход 26 сигнала сопровождения данных, вход 27 установки устройства, вход 28 признака конца массива устройства, вход 29 пуска устройства, информационные входы 30 и 31 устройства, выход 32 сбоя устройства, выход 33 сигнала сопровождения данных устройства, информационные выходы 34 и 35 устройства.

В состав блока умножения (фиг. 2) входят группа элементов ИЛИ 36, первая группа элементов И 37, вторая группа элементов И 38, группа элементов

оэ

4ь Јь

GO СП

НЕ 39, группа входов 40 множимого блока, вход 41 положительного значения разряда множителя блока, вхо д 42 отрицательного значения разряда множи- теля блока, группа информационных выходов 43 блока.

В состав комбинационного сумматора (фиг, 3) входят М одноразрядных комбинационных сумматоров 44, первая группа входов 45 комбинационного сумматора, вторая группа входов 46 комбинационного сумматора, вход 47 коррекции комбинационного сумматора, группа выходов 48 комбинационного сум матора.

Устройство работает следующим образом.

Перед началом работы подачей сигналов на вход 27 сброса устройства производится установка устройства в исходное состояние. При этом сигнал с входа 27 устройства устанавливает в нулевое состояние регистры 14, 18 и 19, счетчик 16, а пройдя через эле- мент ИЛИ 1, устанавливает в нулевое состояние триггеры 2 и 3 и регистры 4 результата. Кроме того, пройдя через второй элемент ИЛИ 11, сигнал сброса устанавливает в нулевое состоя ние счетчик 10,

Затем производится ввод начальных данных. При этом на вход 26 устройства поступает импульс, который проходит через открытый элемент И 15 (триггер 2 установлен в нулевое состояние) на счетный вход суммирующего счетчика 16 и по заднему фронту устанавливает этот счетчик в состояние, равное единице, В результате на первом выходе дешифратора 17 появляется единичный сигнал, который поступает на вход разрешения записи регистра 14, В следующем такте на информационные входы 30 устройства по- дается d-разрядным параллельным кодом значение половины числа коэффициентов aj+fc.; , (j-i, i+1,.. i+k-1), равное (), где k/2 - наибольшее целое, меньшее или равное k/2, а в (d + 1)-м разряде - признак четности, равный если k - четное, t - если k - нечетное, и одновременно на вход 26 подается импульс, который проходит через открытый элемент И 15 на вход синхронизации регистра 14- и осуществляет запись в этот регистр в d разряды значения половины числа коэффициентов ( + 1),

5

0 5

« $

5

а в (d -f 1)-й разряд - признак четности, поступающие со входов 30 устройства на информационные входы этого регистра, а по заднему фронту этого импульса счетчик 16 устанавливается в состояние, равное двум. В результате на втором выходе дешифратора 17 появляется единичный сигнал, который поступает на вход разрешения записи регистра 18, В следующем такте на входы 30 устройства поступают положительные значения коэффициентов a}fi/ , (коэффициенты представляются в тернарной системе кодирования, т.е. принимают значения +1, О, -1, поэтому и различают положительные значения коэффициентов - когда , +1, и отрицательные значения - когда -1). Сопровождающий эти данные импульс, подающийся на вход 26 устройства, поступает на вход синхронизации регистров 18 и осуществляет запись в этот регистр положительных значений коэффициентов .: , а по заднему фронту этого импульса счетчик 16 устанавливается в состояние, равное трем. В результате на третьем выходе дешифратора 17 появляется единичный сигнал, который поступает на вход разрешения записи регистра 19, В следующем такте на входы 30 устройства поступают отрицательные значения коэффициентов at +,, , а сопровождающий эти значения импульс, подающийся на вход 26, поступает на вход синхронизации регистра 19 и осуществляет запись в этот регистр отрицательных значений коэффициентов

af4k-j а по заДнемУ Фронту этого импульса счетчик 16 устанавливается в состояние, равное четырем. Если же на этапе ввода на входы 30 устройства поступают еще какие-либо данные, сопровождаемые импульсом сопровождения, то этот импульс сопровождения проходит с входа 26 на счетный вход счетчика 16 и перебрасывает его по заднему фронту в следующее состояние, равное пяти. В результате на четвертом выходе дешифратора 19 появляется единичный сигнал, который поступает на выход 32 устройства как сигнал сбоя устройства при вводе, и процесс ввода начальных данных осуществляется заново. Если же начальные данные введены без сбоя, то после их ввода начинается процесс решения, осуществляемый следующим образом.

На вход 29 устройства подается сигнал Пуск, который поступает на прямой вход триггера 2 и перебрасывает его в единичное состояние. В результате на инверсном выходе этого триггера появляется нулевой сигнал, который закрывает элемент И 15, завершая тем самым процесс ввода Начальных данных в устройство, а на прямом выходе триггера 2 появляется единичный сигнал, который открывает элементы И 20 первой группы, элементы И 21 второй группы и элемент И 6. После этого на информационные входы 30 и 31 устройства начинают поступать параллельно два массива данных . л Л

и fxUj)i} где 1 J сопровождаемых импульсами сопровождения, поступающими на вход 26 устройства. В первом такте на входы 30 поступает параллельным кодом значение первой величины х„ массива fx(-zj-0 l а на входы 31 - значение первой величины ХЈ, массива . Значение проходит параллельным кодом через открытые элементы И 20 группы на входы множимого всех блоков 22 умножения первой группы, на входы множителя которых поступают значения коэффициентов а Ј11,0,-lX из регистров 18 и 19. В результате, если значение коэффициента, поступающего на 1-й блок 22 умножения (1 1, 2,..., п), является положительным, т.е. ag 1, то это значение коэффициента ар поступает с 1-го выхода регистра 18 через вход 41 блока 22 на.элементы И 37 группы и пропускает значение первого элемента х ц массива .л, у через элементы И 37 группы и через элементы ИЛИ 36 группы на выходы 43 блока без изменения, что соответствует умножению значения Х|( на а + 1. Если же значение -коэффициента,

15

20

25

30

35

40

ции 1-го сумматора 23, на входы которого поступает результат умножения х „ на а, -1 в обратном коде, поступает в младший разряд сумматора

23в качестве единицы коррекции значение ag -1 с 1-го выхода регистра 19. В результате на выходе этого сумматора 23 получается значение произJQ ведения х (/ на а -1 в дополнительном коде. Если же значение коэффициента аЈ 0, то единичные сигналы на входах 41 и 42 блока 22 отсутствуют, элементы И 37 группы и И 38 группы закрыты и результат умножения значения хя на ар 0 равен нулю. Таким образом, в первом такте при поступлении значения первой величины массива ГХ( на входы блоков 22 умножения происходит умножение этого значения на коэффициенты aj и произведения х(( ag поступают на входы 1-х сумматоров 23, а так как на вторую группу входов этих сумматоров 23 с выходов регистров 4 результатов группы поступают нулевые значения, так как регистры 4 предварительно сброшены в нулевое состояние, то произведения xn i ag проходят через сумматоры 23 без изменения (за исключением случая, когда ар -1 ив сумматоре к обратному коду произведения Хц1 ар добавляется в младший разряд единица, переводящая это произведение в дополнительный код). Одновременно аналогичным образом с помощью блоков

24умножения второй группы и сумматоров 25 второй группы образуются значения произведений х, на коэффициенты a j-j-if.: е-П 0,-1 j из регистров 18 и 19. При этом в нечетных s-x

(s 1, 3,..., п-1) блоках 24 умножения второй группы происходит умножение значения х2 на коэффициенты a(i+k : , поступающие с четных (s + 1)-x поступающего на 1-й блок 22 умножения, выходов регистров 18 и 19, и получив5

0

5

0

5

0

ции 1-го сумматора 23, на входы которого поступает результат умножения х „ на а, -1 в обратном коде, поступает в младший разряд сумматора

23в качестве единицы коррекции значение ag -1 с 1-го выхода регистра 19. В результате на выходе этого сумматора 23 получается значение произQ ведения х (/ на а -1 в дополнительном коде. Если же значение коэффициента аЈ 0, то единичные сигналы на входах 41 и 42 блока 22 отсутствуют, элементы И 37 группы и И 38 группы закрыты и результат умножения значения хя на ар 0 равен нулю. Таким образом, в первом такте при поступлении значения первой величины массива ГХ( на входы блоков 22 умножения происходит умножение этого значения на коэффициенты aj и произведения х(( ag поступают на входы 1-х сумматоров 23, а так как на вторую группу входов этих сумматоров 23 с выходов регистров 4 результатов группы поступают нулевые значения, так как регистры 4 предварительно сброшены в нулевое состояние, то произведения xn i ag проходят через сумматоры 23 без изменения (за исключением случая, когда ар -1 ив сумматоре к обратному коду произведения Хц1 ар добавляется в младший разряд единица, переводящая это произведение в дополнительный код). Одновременно аналогичным образом с помощью блоков

24умножения второй группы и сумматоров 25 второй группы образуются значения произведений х, на коэффициенты a j-j-if.: е-П 0,-1 j из регистров 18 и 19. При этом в нечетных s-x

(s 1, 3,..., п-1) блоках 24 умножения второй группы происходит умно

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1984 |

|

SU1180883A1 |

| Вычислительное устройство | 1985 |

|

SU1320804A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2022339C1 |

| Вычислительное устройство | 1985 |

|

SU1272329A1 |

| Программируемый цифровой фильтр | 1986 |

|

SU1374244A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| Вычислительное устройство | 1985 |

|

SU1269124A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1994 |

|

RU2097828C1 |

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки информации. Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения вычислений при нечетном значении числа коэффициентов. Поставленная цель достигается введением двух мультиплексоров с их связями. 5 ил.

является отрицательным, т.е. ag -1, то это значение коэффициента а. поступает с 1-го выхода регистра 19 через вход 42 блока 22 на входы элементов И 38 группы и пропускает обратный код значения - с выходов элементов НЕ 39 группы через эти элементы И 38 группы и через элементы ИЛИ 36 группы на выходы 43 блока 22, что соответствует умножению значения на а в обратном коде, а для образования дополнительного кода произведения х(| а через вход 47 коррек0

5

шиеся произведения просуммируются на нечетных s-сумматорах 25 второй группы с произведениями, поступающими из соответствующих s-x сумматоров 23 первой группы. А в четных r-х (г 2, 4,..., п) блоках 24 умножения второй группы происходит умножение значения х2, на коэффициенты а,-.:, поступающие с нечетных (г-1)-х выходов регистров 18 и 19, и получившиеся произведения суммируются на четных r-х сумматорах 25 второй группы с произведениями, поступающими из

16

(r-2)-x сумматоров 23 первой группы. В результате полученные в первом так- те на сумматорах 25 второй группы суммы произведений проступают на информационные входы соответствующих регистров 4 группы и по импульсу сопровождения значений х(( и х(, поступающему на вход синхронизации регистров 4 через открытый элемент Иб, записываются в эти регистры. В следующем такте на входы множимого блоков 22 умножения первой группы поступает параллельным кодом второе значение х$| массива данных 1х()Л , а на входы множимого блоков 24 умножения второй группы - значение второй величины x(j1 массива х п, у . В результате произведения значений х , на соответствующие коэффициенты a;+.i суммируются на сумматорах 23 первой группы с соответствующей суммой произведений, полученной в предыдущем тате и поступающей из соответствующих регистров 4, и, поступив на соответ- ствующие сумматоры 25 второй группы, полученный результат суммируется с поступающим из соответствующего блока 24 умножения произведением значени х4| на соответствующий коэффициент а:,; и запишется в соответствующий регистр 4 группы. Дальнейшее функционирование устройства при потактном вычислении значений выходных массивов У( и У(71ГЛ происходит ана- логично описанному выше. При этом значения коэффициентов . 0-1 в регистрах 18 и 19 записаны ы в следующей последовательности: в n-м разряде - значение а( , в (n-l)-M значение ае, в (п-2)-м - значение а$ и т.д., и если количество коэффициентов (k) четное и равно числу разрядов (п) этих регистров, то в первом разряде записан коэффициент а (при , в первые (свободные) разряды регистров 18 и 19 заносятся нулевые значения, в частности при наибольшем нечетном значении k, равном (п-1), свободным будет только разряд регистров 18 и 19. Поэтому на входы множителя первого блока 22 умножения первой группы и второго блока 24-умножения второй группы при четном значении k, равном п, поступает значение коэффициента а « с первого выхода регистров 18 и 19, на входы множителя второго блока 22 умножения пер- вой группы и первого блока 24 умно

o

5

1

Q 50 5 Q

5

358

жения второй группы - значение а с второго выхода регистров 18 и 19 и т.д. и на входы множителя последнего n-го блока 22 умножения первой группы и (п-1)-го блока 24 умножения второй группы - значение a с n-го выхода регистров 18 и 19. Для большей наглядности последовательность по- тактного вычисления значений выходных массивов {У(г.ф1г и {У(г;}, для случая четного значения числа коэффициентов k (на примере k-n) представлена на фиг. 4, а для случая нечетного значения числа коэффициентов k (на примере ), представлена на фиг. 5. При этом в течение первых () тактов никаких значений на выходы устройства не выдается, так как на входы управления выходов мультиплексоров 8 и 9 на второй вход третьего элемента И 7 поступает с прямого выхода триггера 3 нулевой сигнал и они закрыты. И лишь в ())-м такте значение счетчика 10, подсчитывающего количество импульсов сопровождения, поступающих с выхода элемента И 6 через открытый элемент И 5, совпадает со значением числа коэффициентов (Ck/21-H), записанных в регистр 14, и в результате на выходе блока 13 сравнения появляется единичный сигнал, который устанавливает триггер 3 в единичное состояние, а, задержавшись на такт на элементе 12 задержки, проходит через элемент ИЛИ 11 и сбрасывает счетчик 10 в нулевое состояние. Триггер 3 закрывает элемент И 5, и, поступив на входы управления выходов мультиплексоров 8 и 9 и на второй вход треть- его элемента И 7, разрешает выдачу вычисленных значений уп и у, на выходы 34 и 35 и выдачу импульса сопровождения этих значений на выход 33 устройства. В результате в (Јk/2j+ +1)-м такте в случае четного числа коэффициентов k значение

УК + акм. ....+а2х

х

(K-Ol

+ а

х

М

с выходов (п-1)-го регистра 4 группы проходит через первую группу информационных входов первого мультиплексора 8, управляемых нулевым сигналом с выхода (d + 1)-го разряда регистра

14, хранящего признак четности на выходы 34 устройства, а значение

+ а,

av.xz,+ ак,. хм + ...+а2 хи +

Х(К4-0(

с выходов n-го сумматора 23 первой группы проходит через первую группу информационных входов второго мультиплексора 9, управляемых также ну- левым сигналом с выхода (d-H )-го разряда регистра 14, на выходы 35 устройства и через открытый элемент И 7 на выход 33 устройства поступает импульс сопровождения вычислен- ных значений у м и у. . В случае же нечетного значения числа коэффициентов k в ()-M такте значение у., проходит на выходы 34 устройства с выходов n-го сумматора 23 пер вой группы через вторую группу информационных входов первого мультиплексора 8, управляемых единичным сигналом с выхода (d+1)-го разряда регистра 14, а значение у( проходит на выходы 35 устройства с выходов предпоследнего (n-l)-ro сумматора 25 второй группы через вторую группу информационных входов второго мультиплексора 9, управляемых также единичным сигналом с выхода (d+1)-ro разряда регистра 14. В следующем ()-M такте на выходы 34 уст- t ройства поступает значение , а на выходы 35 устройства одновременно

поступает значение уд( (фиг. 4 и 5) и т.д. После того, как на входы 30 и 3 устройства поступят последние значения массивов переменных Гх(2}-оЛ и {Xt2j)3 на ВХ°Д 28 устройства поступает сигнал с конца массива, который проходит через элемент ИЛИ 1 и сбрасывает в нулевое состояние триггеры 2 и 3 и регистры 4, заканчивая тем самым процесс вычислений в устройстве.

Таким образом, введение двух мультиплексоров с их связями позволит в 50 сравнении с известным расширить функциональные возможности устройства за счет обеспечения возможности вычисления выражения не только при четном числе коэффициентов, но и при нечет- 55 ном числе их в условиях двухканаль- ной обработки данных, что позволит расширить область применения предла- . гаемого устройства.

ы164413510

Формула изобретения

5

0

О 5

0 .

Устройство для вычисления выражеMk-1

ния вида у- - a|4k х- содержащее два триггера, два элемента ИЛИ, четыре элемента И, две группы элементов И, два суммирующих счетчика, элемент задержки, блок сравнения, регистр числа коэффициентов, дешифратор, два регистра значений коэффициентов, две группы блоков умножения, две группы комбинационных сумматоров, группу регистров результата, причем выход первого элемента ИЛИ соединен с входами установки в О первого и второго триггеров и входами установки в О s-x регистров результата группы (s 1, 3, 5,... п-1, где п- разрядность регистра значений коэффициентов), входы синхронизации регистров результата группы соединены с первым входом первого элемента И, с выходом второго элемента И и первым входом третьего элемента И, второй вход которого соединен с прямым выходом второго триггера, инверсный выход которого соединен с вторым входом первого элемента И, выход которого соединен со счетным входом первого суммирующего счетчика, вход установки в О которого соединен с выходом второго элемента ИЛИ, первый вход которого соединен с выходом элемента задержки, вход которого соединен с входом устновки в 1 второго триггера и выходом равенства блока сравнения, первый информационный вход которого соединен с выходом суммирующего счетчика, второй информационный вход блока сравнения соединен с информационным выходом регистра числа коэффициентов, вход синхронизации которого соединен с выходом четвертого элемента И и со счетным входом второго суммирующего счетчика, выход которого соединен с входом дешифратора, первый выход которого соединен с входом разрешения записи регистра числа коэффициентов, второй выход дешифратора соединен с входом разрешения записи первого регистра значений коэффициентов, третий выход дешифратора соединен с входом разрешения записи второго регистра значений коэффициентов, инверсный выход первого триггера соединен

с первым входом четвертого элемента И, прямой выход первого триггера соеинен с первым входом второго элеента И, с первыми входами элементов И первой группы и первыми входаи элементов И второй группы, выход 1-го разряда первого регистра значений коэффициентов (1 1, 2,... п) соединен с входом положительного значения разряда множителя (1-го блока умножения первой группы, вход отриательного значения разряда множителя которого соединен с выходом 1-го разряда второго регистра значений коэффициентов и с входом переноса 1-го комбинационного сумматора первой группы, входы первого слагаемого которого подключены к соответствующим выходам 1-го блока умножения первой группы, входы множимого которого соединены с выходами соответствующих элементов И первой группы, входы второго слагаемого r-го комбинационного сумматора первой группы (г 2, 4, 6,... п) соединены с выходами соответствующих разрядов г-го регистра результата группы, выходы s-ro разряда первого и второго регистров значений коэффициентов подключены соответственно к входам положительного и отрицательного значений разряда множителя (s + 1)-го блока умножения второй группы, выходы 1-го блока умножения второй группы подключены к соответствующим входам первого слагаемого 1-го комбинационного сумматора второй группы, вход переноса которого соединен с входом отрицательного значения разряда множителя 1-го блока умножения второй группы, выход 1-го комбинационного сумматора второй группы подключен к информационному входу 1-го регистра результата группы, входы множимого 1-го блока умножения второй группы соединены с выходами соответствующих элементов И второй группы, вход сиг- нала сопровождения данных устройства подключен к второму входу четвертого элемента И, к входам синхронизации первого и второго регистров значений коэффициентов и к второму входу второго элемента И, вход установки устройства подключен к входу установки в О второго суммирующего счетчика, к входам -установки S О регистра числа коэффициентов, первого и второго регистров значений коэффициентов,

5

0

5

0

5

0

5

0

5

к второму входу второго элемента ИЛИ и первому входу-первого элемента ИЛИ, второй вход которого соедин-ен с входом признака массива устройства, вход пуска которого соединен с входом установки в 1 первого триггера, информационные входы первой группы которого подключены к вторым входам соответствующих элементов И первой группы, к входам соответствующих разрядов регистра числа коэффициентов первого и второго регистров значений коэффициентов, четвертый выход дешифратора подключен к выходу сбоя устройства, выход третьего элемента И соединен с выходом сигнала сопровождения данных устройства, информационные входы второй группы устройства подключены к вторым входам соответствующих элементов И второй группы, вход второго слагаемого q-ro комбинационного сумматора первой группы (q 3,5,7...п-1)соединены с выходом(я-2)- го регистра результата группы, выход суммы s-ro комбинационного сумматора первой группы соединен с входом второго слагаемого s-ro комбинационного сумматора второй группы, выход суммы р-го комбинационного сумматора первой группы (р 2, 4, 6,... п-2) соединен с входом второго слагаемого (р + 2)-го комбинационного сумматора второй группы, выходы r-го разряда первого и второго регистров значений коэффициентов подключены соответственно к входам положительного и отрицательного значения разряда множителя (г-1)-го блока умножения второй группы, входы установки в О г-х регистров результата группы соединены с выходом первого элемента ИЛИ, отличающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения вычислений при нечетном значении числа коэффициентов, в него введены первый и второй мультиплексоры, причем прямой выход второго триггера соединен с управляющим входом первого и второго мультиплексоров, адресный вход которых соединен с выходом разряда контроля регистра числа коэффициентов, выход (п-1)-го регистра результата группы подключен к первому информационному входу первого мультиплексора, второй информационный вход которого соединен с выходом суммы п-го комбинационного сумматора первой группы и первым информационным входом второго мультиплексора, второй информационный вход которого соединен с выходом суммы (n-l)-ro комбинационного сумматора

Фие 1

второй группы, выход первого мультиплексора соединен с первым информационным выходом устройства, второй информационный выход которого соединен с выходом второго мультиплексора.

M Л

M

cj Ъ § Ј s| §

J J I

7 ч 5f

5j Ј o

т

Ч

«J

$

| Вычислительное устройство | 1985 |

|

SU1272329A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительное устройство | 1987 |

|

SU1444759A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-04-23—Публикация

1989-04-11—Подача