2. Устройство по п. 1, от п и ч аю щ в е с я тем, что блок суммирования в избыточной системе счисления содержит два сумматора, регистр, элемент ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и преобразователь прямого кода в аоподнительный, причем вход переноса соединен с входом переноса первого сумматора, первые входы разрядов которого соединены с информационными входами блока, управляющий вход которого подключен,к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вькоды разрядов первого сумматора подключены к входам разрядов регистра, выходы переноса и старшего разряда первого сумматора подключены к входам элемента ИЛИ, выход которого соединен с входом переноса второго сумматора, первые входы разрядов, которого соединены с выходами разрядов регистра, первый вход знакового разряда второго сумматора соединен с выходом : старшего разряда регистра, выходы разрядов второго сумматора соединены с информационными входами преобразователя прямого кода в дополнительный, управляющий вход которого соединен с выходом знакового разряда второго сумматора и вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы всех разрядов первого и второго сумматоров подключены к нулевой шине блока, вьЪсоды преобразователя прямого кода в дополнительный -и зпемента ИСКЛЮЧА-.,

ЮШЕЕ ИЛИ. являются выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1981 |

|

SU997030A1 |

| Устройство для умножения | 1981 |

|

SU999043A1 |

| Устройство для умножения | 1981 |

|

SU1013946A1 |

| Устройство для умножения | 1979 |

|

SU960804A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1020818A1 |

| Устройство для умножения | 1982 |

|

SU1059566A1 |

| Устройство для умножения в избыточной четверичной системе счисления | 1983 |

|

SU1160399A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для умножения | 1981 |

|

SU1005035A1 |

| Арифметическое устройство | 1978 |

|

SU711570A1 |

1. УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ, содержащее блок анализа знака, блок умножения, блок суммирования в азбыточной системе счисления, регистр | езультата и регистр множителя, вхоцы разрядов которого соединены с входами шюжвтеля устройства, входы блока ана пиза знака подключены к входам знаков множителя и множимого устройства, входы множимого устройства соединены с первой группой входов блока умножения, вторая группа входов которого соединена с выходами разрядов регистра множителя, выходы старших разрядов регистра результата соединены с информационными входами блока суммирования в избыточной системе счисления, о т л и ч а to ш е « е с я тем, что, с целью повышения быстродействия устройства, в него вве цен комбинационный сумматор, входы первой группы которого соединены с выходами блока умножения, -выходы младших разрядов регистре результата подклк чены к входам второй группы комбинационного сумматора, выходы разрядов ко Ш торого соединены с входами разрядов регистра результ 1та, а выход переноса с входом переноса блока суммирования в избыточней системе счисления, управляющий Бход которого соединен с выходом блока анализа знака, а выходы - с выходами устройства.

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении специализированных устройств.

Известно устройство для умножения, содержаиве регистры, сумматор, матрицу модулей и блок анализа. Данное уст ройство предназначено для вычисления произведений только полгакительных чисел 1.

Известно устройство для умножения, содержащее регистр. множимого и множителя, сумматор, матрицу модулей сложения, блок анализа знака, блоки элементов И и блок элементов 2И-ИЛИ 2

Недостатком этого устройства являет ся невысокое быстродействие, которое связано с невозможностью получения результата старшими разрядами вперед.

Наиболее близким к изобретению является устройство для умножения, содержащее регистр ножителя, регистр MHCV жимого, блок анализа знака, блок элементов И, информацт4онные входы которого соединены с выходами регистра мно- жимого, коммутатор, управляющий вход которого соединен с выходом блока анаядиза зюака, многовходовой последовательный сумматор в избыточной двоичной системе счисления и два регистра результата. Выход регистра множителя соединен с управляющим входом блока элементов И, вьЪсоды которого соединены с информационными входами коммутатора, первая и вторая группы выходов которого соединены соответственно с положительными и отрицательными входами многовходового последовательного сумматора в избыточной двоичной системе. счисления, положительный и отрицательны выходы которого подключены к входам младшгос разрядов соответственно первого и второго регистров результата, выходы старших разрядов которьк соединены с (fl+D-M положительным и {1Л-Ы)-м отрицательным бходами многовходового последовательного сумматора в избЬ1точной двоичной системе счисления (VI - число разрядов множителя) 3 .

Недостатком этого устройства Является недостаточное быстродействие, так как за один такт производится умножение только Одного разряда аргументов.

.

Целью изобретения .является повьшение бьютродействия устройства.

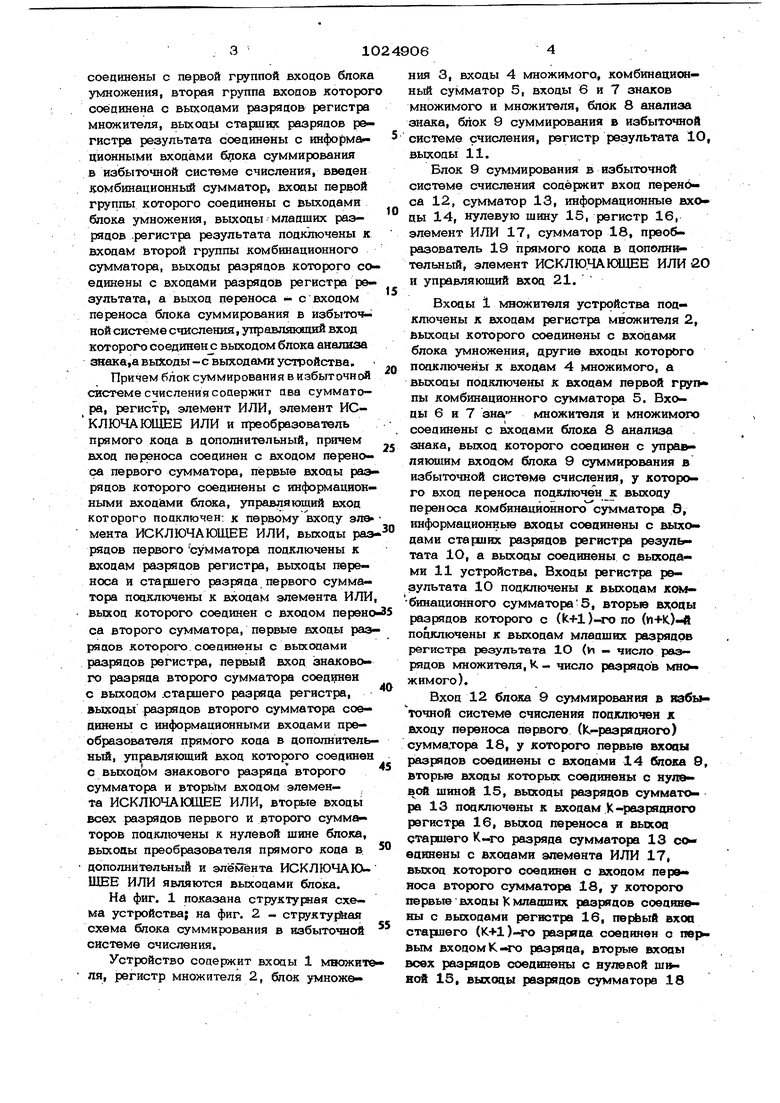

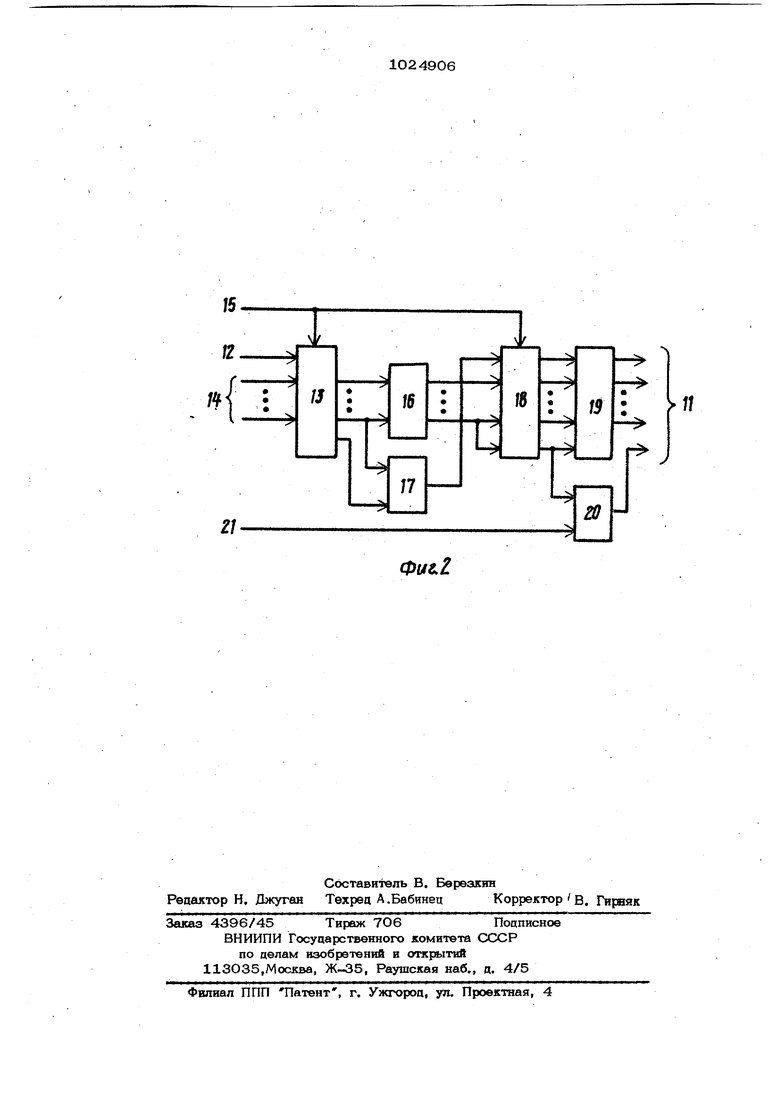

Лля достижения поставленной цели в устройство для умножения, содержащее блок анализа знака,блок умножения, блок суммирования в избьггочной системе счисления, регистр результата и регистр множителя, входы разрядов которого соединены с входами множителя устройства, ды блока анализа знака подключены к входам знаков множителя и множимого устройства, входы множимого устройства соединены с первой группой вхоцов блока умножения, вторая группа входов которог соединена с выходами разрядов регистра множителя, Bbtxoabi старших разрядов регистра результата соединены с информационными входами суммирования в избыточной системе счисления, введен комбинационный сумматор, входы первой группы которого соединены с выходами блока умножения, выходы младших разрядов .регистра результата подключены к входам втх)рой группы комбинационного сумматора, выходы разрядов которого со единены с входами разрядов регистра результата, а выход переноса - с входом переноса блока суммирования в избыточ-i ной системе счисления, управляющий вход которого соединен с выходом блока анализа знака.а выходы-с выходами устройства. Причем блок суммирования в избыточной системе счисления сопержиг ава сумматора, регистр, элемент ИЛИ, элемент ИСКЛЮЧАЮШЕЕ ИЛИ и преобразователь прямого кода в дополнительный, причем вход переноса соединен с входом переноса первого сумматора, первые входы раз рядов которого соединены с информационными вход)ами блока, управляющий вход которого подключен: к первому вхоцу зламента ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы раэ рядов первого сумматора подключены к входам разрядов регистра, выходы переноса и старшего разряда первого сумматора подключены к входам элемента ИЛИ выход которого соединен с входом nepeHO са второго сумматора, первые входы раз рядов которого, соединены с выходами разрядов регистра, первый вход знакового разряда второго сумматора соедщ1еи с выходом .старшего разряда регистра, выходы разрядов второго сумматора соединены с информационными входами преобразователя прямого кода в дополнительный, управляющий вход которого соединен с выходЬм знакового разряда второго сумматора и вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входь всех разрядов первого и второго сумматоров подключены к нулевой шине блока, выходы преобразователя прямого кода в, дополнительный и элемента ИСКЛЮЧАЮи ШЕЕ ИЛИ являются выходами блока. На фиг. 1 показана структурная схема устройства; на фиг. 2 - структурная схема блока суммирования в избыточной системе счисления. Устройство содержит входы 1 множите ля, регистр множителя 2, блок умножения 3, входы 4 множимого, комбинацисжный сумматор 5, входы 6 и 7 знаков множимого и множителя, блок 8 анализа знака, блок 9 суммирования в избыточной системе счисления, регистр результата 1О, выходы 11. Блок 9 суммирования в избыточной системе счисления содержит вход перенбса 12, сумматор 13, информационные вхо цы 14, нулевую шину 15, регистр 16, элемент ИЛИ 17, сумматор 18, преобразователь 19 прямого кода в дополнительный, элемент ИСКЛЮЧАКШ1ЕЕ ИЛИ i2O и управляющий вход 21. Входы 1 множителя устройства подключены к входам регистра множителя 2, выходы которого соединены с входами блока умножения, другие вкоды которого подключены к входам 4 множимого, а выходы подключены к входам первой группы комбинационного сумматора 5. Входы 6 и 7 зна множителя и множимого соединены с входами блока 8 анализа знака, выход которого соединен с управляющим входом блока 9 суммирования в избыточной системе счисления, у которого вход переноса подключен к выходу переноса комбинационного сумматора Э, информационные вхоцы соеаинены с выходами старших разрядов регистра резуль тата 1О, а выходы соединены с выходами 11 устройства. Входы регистра результата 10 подключены к выходам ком бинационного сумма тора-5, вторые вх/оаы разрядов которого с (( («+К.)-Й подключены к выходам младших разрядов регистра результата 1О (vi - число peia- рядов множителя, К - число разрядов множимого). Вход 12 блока 9 суммирования в избыточной системе счисления пoдJUIючвн я входу переноса первого (К.-разрядного) сумма,тора 18, у которого первые входы разрядов соединены с входами 14 блока 9, вторью входы которых соединены с нулевой шиной 15, выходы разрядов сумматора 13 подключены к входам К-разрядного регистра 16, вьосод переноса и выход старшего К-го разряда сумматора 13 соединены с входами элемента ИЛИ 17, выход которого соединен с входом переноса второго сумматора 18, у которого первью входы К младших разрядов соединены с выходами регистра 16, перЬый вхоа старшего (К-И)-го разряда соединен с перым входом К нсч) разряда, вторые входы сех разрядов соединены с нулевой шиой 15, выходы разрядов сумматора 18

с первого по К-и поцключены к информационным вхоаам преобразователя 19, управляющий вход которого соединен с вьгходом (К+1)-го разряда сумматора 18 и с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 20, вторым входом соединенного с входом 21 блока 9, выходы 11 блока подключены к выходам преобразователя 19 и элемента ИСКЛЮЧАЮЩЕЕ или 20.

Устройство работает слеаующим образом.

В начале цикла умножения регистр результата 10 сбрасывается в нулевое состояние, в регистр множителя 2 с входов 1 устройства заносится значение множителя параллельным двоичным кодом. Входами 6 и 7 в блок 8 анализа знака подаются значения знаков множителя и множимого. Значение произведения знаков множимого.и множителя с выхода блока 8 анализа знака подается на вход 21 блока 9. Вкаждом такте работы с входов 4 устройства значения К, разрядов множимого, начиная со старших разрядов, подаются на входы бло умножения 3, который осуществляет перемножение К разрядов множимого на Vi разрядов множителя. Результаты каждого .такта перемножения с выходов блока 3 .умножения подаются на первые входы разрядов комбинационного сумматора 5, на вторьте входы разрядов которого с (К+1 )-го по (И+К)-Й с выходов регист ра результата 10 подаются значения младших разрядов частичного результата, полученного в предыдущем такте ра- боты. Значения (M-fk) разрядов аанного час гичного результата заносятся в регистр результата 1О с выходов сумм комбинационного сумматора 5 . Значение {и+ К+ 1)-го разряда частичного результата с выхода переноса комбинационного сумматора 5 и гранения К раэ рядов предыдущего частичного реэульгата с выходов К старши;с разрядов регистра результата 10 подаются на входы 12 и 14 блока 9 суммирования в избьтточной системе счисления с основанием р 2 ,

Сумматор 13 суммирует значения (и-HC-f 1)-го разряда частичного результата, поступающего с входа 12 блока 9 на вход переноса, и К старших разрядов предыдущего частичного результата, поступающего на первые входы разрядов сумматора 13 со входов 14 блока 9, С выходов сумматора 13 значения К младших разрядов полученной суммы заносятся в регистр 16 и, кроме того, значения VL-ro и (К+1 )-го разрядов суммы через элемент ИЛИ 17 подаются на вход переноса сум матора 18. На выходе элемента ИЛИ 17 имеем значение переноса.

Значение суммы заносится в регистр 16 в дополнительном коде.

Сумматор 18 суммирует значения суммы и переноса, при этом знаковый разряд результата формируется старшим К- разрядом суммы. Полученный на выходах сумматора 18 результат в дополнительном коде поступает в преобразователь 19 я преобразуется в прямой код. Модуль результата подается с выходов преобразо вателй 19 на вы)DЦЫ 11 устройства, а знак результата пол;Иавтся на выходе элемен« та ИСКЛЮЧАЮЩЕЕ ИЛИ 20, на входы которого подаютхзя знак произведения с Ерсода 21 блоков 9 и знак результата с выхода старшего (K+lV-ro разряда сумматора 18, Результат умножения выдается на выходы 11 устройства последовательным кодом в избыточно системе счисления с основанием р « 2, старшими разрядами вперед. Число тактов работы устройства определяется числом разрядов мяожимого и необходимой точностю вычисления.

Таким образом, достигается увеличение бьютроцействия устройства в К раз. При этом блок умножения значительно проше блоков умножения параллельных устройств и может быть выполнен яа основе постоянного запоминающегчэ устройства или на основе ВИС.

/

fl

Фиг. I

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления сумм произведений | 1975 |

|

SU551643A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для сортировки каменного угля | 1921 |

|

SU61A1 |

Авторы

Даты

1983-06-23—Публикация

1981-08-14—Подача