счетчика и вторым входом iвторого .триггера, инверсный выход которого coeAHHerf с вторым входом четвертого элемента И, а прямой выход с вторым входом пятого элемента И, выход которог о является выходом преобразователя единичного импульса в серию,

3.Устройство по П.1, от л ичающееся тем, что каждый делитель с регулируемым коэффициентом деления содержит счетчик, счетный вход которого является входом делителя с регулируемым коэффициентом деления, блок переключателей и блок совпадения, первый информа- ционный вход которого подключен

к информационному выходу счетчика, второй информационньй вход - к информационному вьпсоду блока переключателей, а выход соединен со сбросовым входом счетчика и является выходом делителя с регулируемым коэффициентом деления.

4.Устройство по П.1, отличающееся тем, что блок вычитания содержит два инвертора, два триггера, элемент И-НЕ и элемент И, выход которого является выходом блока вычитания, выход первого инвертора подключен к первому входу первого триггера, инверс ый выход которого подключен

к первому входу элемента И-НЕ, второй вход которого соединен с входом первого инвертора и является первым входом блока вычитания , второй вход первого триггера является вторым входом блока вычитания, выход элемента И-НЕ соединен с первым входом второго триггера, второй вход которого является третьим входом блока вычитания, инверсный выход второго триггера подключен к первому входу элемента И, выход элемента И-НЕ через второй

инвертор связан с вторым элементом И, третьи входы первого и второго триггеров подключены к проводнику логического нуля.

5.Устройство по п.2, о т л ичающееся тем, что каждый дешифратор преобразователя единичного импульса в серий содержит элемент И, входы которого образуют информационный вход дешифратора,

а выход элемента И является выходом дешифратора.

6.Устройство по пп. 2 и 3, отличающееся тем, что блок совпадения каждого преобразователя единичного импульса в серию и каждого делителя с регулируемым коэффициентом деления содержит ряд элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, ряд инверторов, элемент И и две информационные шины, причем первые входы .каждого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ

образуют первую информационную шину, .которая связана с первым информационным входом блока совпадения, вторые I входы каждого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ образуют вторую информационную ш ну, которая связана с вторым информационным входом блока совпадения, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ через соответствующие инверторы подключены к соответствующим входам элемента И,, выход которого является выходом блока.совпадения.

7.Устройство по пп. 2 и 3, отличающееся тем, что блок переключателей содержит ряд переключателей,имеющих по три клеммы каждый,. первые клеммы переключателей подключены к информационному выходу блока переключателей,соединенные вместе вторые клеммы переключателей подключены к проводнику логической единццы а соединенные вместе, третьи клеммы переключателей подключены к проводнику логического нуля.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции числа импульсов по параметру | 1984 |

|

SU1228118A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1983 |

|

SU1129625A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ШКАЛЫ ВРЕМЕНИ | 1995 |

|

RU2082216C1 |

| Цифроаналоговый измеритель средней частоты | 1991 |

|

SU1775678A1 |

| Устройство для коррекции шкалы времени | 1990 |

|

SU1709268A1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

| Функциональный преобразователь | 1984 |

|

SU1211756A1 |

| Функциональный генератор | 1980 |

|

SU902022A1 |

| Устройство для линеаризации характеристик измерительных преобразователей | 1981 |

|

SU982007A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

1. УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ЧИСЛА ИМПУЛЬСОВ ПО ВХОДНОМУ ПАРАМЕТРУ по авт.рв. № 334544, отличающееся тем, .что, с целью повышения точности коррекции числа импульсов по входному параметру, в него дополнительно введены последовательно соединенные второй преобразователь единичного импульса в серию и второй делитель с регулируемым коэффициентом деления, подключенный выходом к третьему входу блока вычитания, причем первый вход второго преобразователя единичного импульса в серию соединен с выходом датчика параметра,а второй вход с выходом первого делителя с регулируемым коэффициентом деления. 2. Устройство по П.1, о т л ичающееся тем, что каждый преобразователь единичного импульса в серию содержит мультивибратор, пять элементов И, три счетчика, два дешифратора, два триггера, элемент НЕ, блок совпадения и блок пе-.реключателей, причем выход мультивибратора подключен к первому входу первого элемента И, выход которого соединен со счетным входом первого счетчика, информационный вход первого дешифратора связан с информационным выходом первого счетчика, а выход - с соединенными вместе сбросовым входом первого счетчика и первым входомпервого триггера, выход которого подкйючен к первому входу второго элемента И, выходом связанного с соединенными вместе вторым входом первого элемента И и первым входом третьего элемента И, второй вход которого является первым входом преобразователя единичного импульса в серию, выход элемента НЕ (Л подключен к второму входу второго элемента И,а вход соединен с вторым входом первого триггера и является вторым входом преобразователя единичного импульса в серию, первые входы четвертого и пятого элементов И соединены вместе и подключены 00 к выходу третьего элемента И, вто рой счетчик подключен счетным входом к выходу четвертого элемента 4 И, а информационньм выходом - к ON информационному входу второго дешифратора выход которого связан с соединенными вместе сбросовым входом второго счетчика и первым входом второго триггера, третий счетчик подключен счетным входом к выходу пятого элемента И, а информационным выходом - к первому информационному входу блока совпадения, второй информационный вход которого подключен к информационному выходу блока переключателей, выход блока совпадения связан с соединенными вместе сбросовым входом третьего

1

Изобретение относится к средствам автоматизации, вычислительной и и мерительной технике и может использоваться в системах автомати

iecKoro контроля и измерения расхода нефти, нефтепродуктов, сжиженных газов и газовых конденсатов ,а также в цифровых системах контроля и управления,

3

Цель изобретения - повышение точности корректировки числа импульсов по входному параметру.

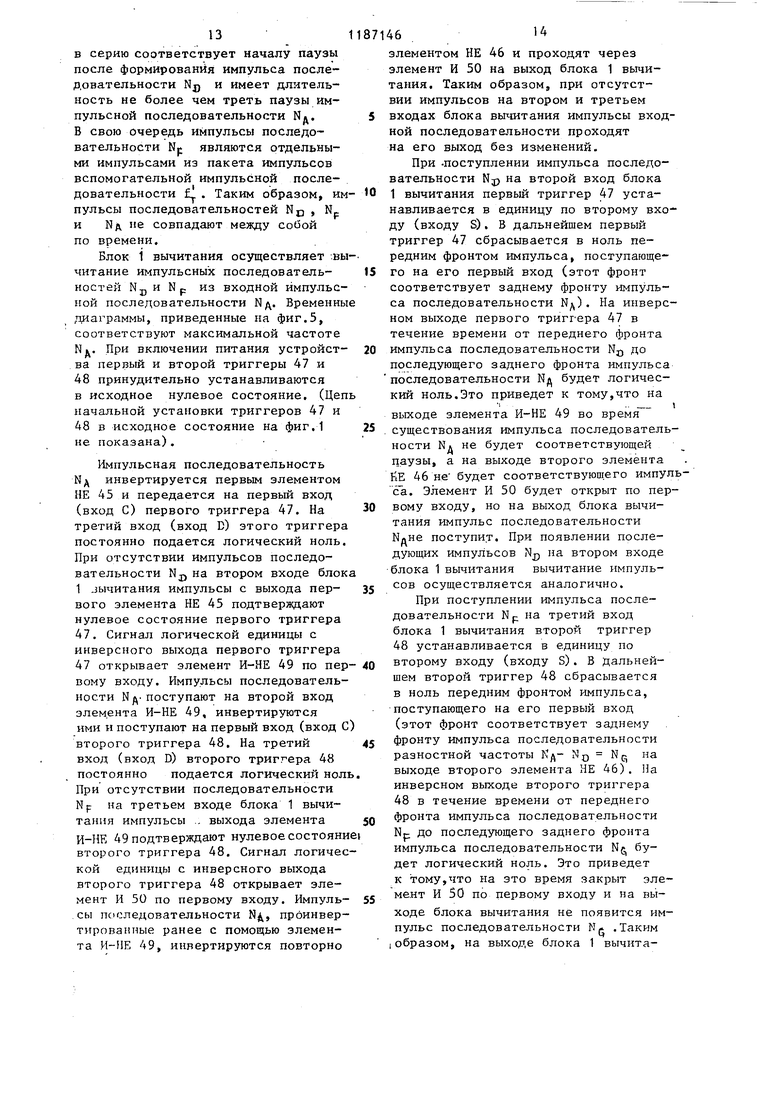

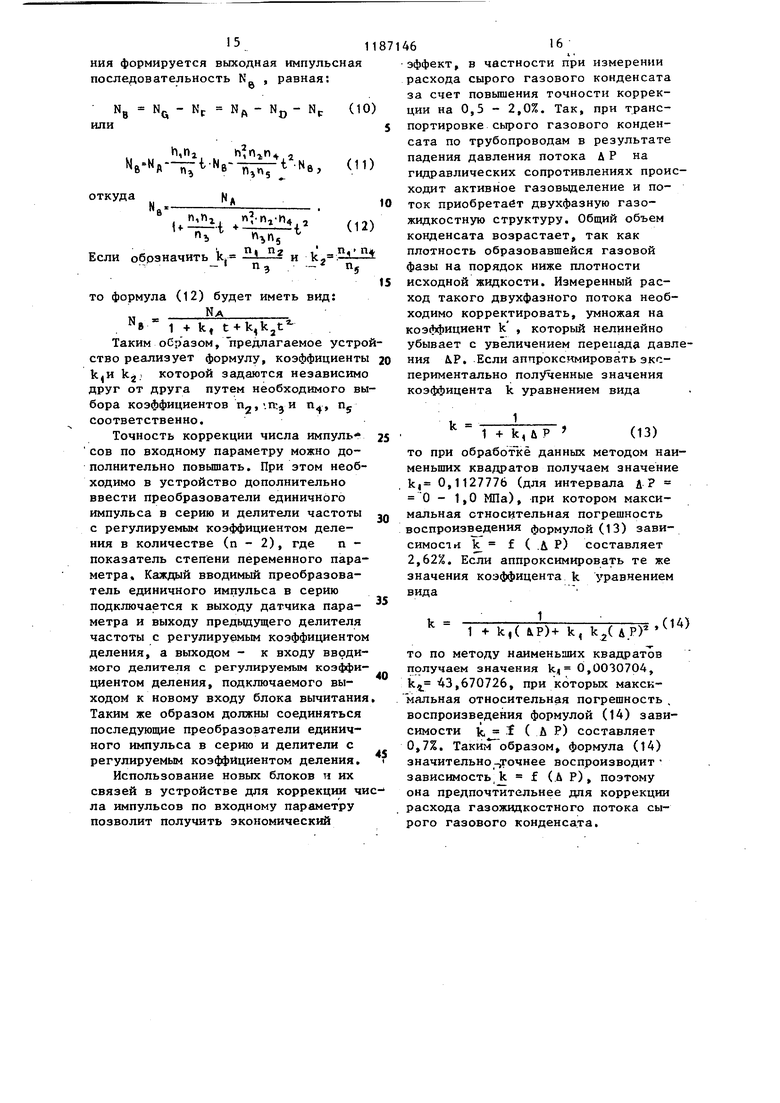

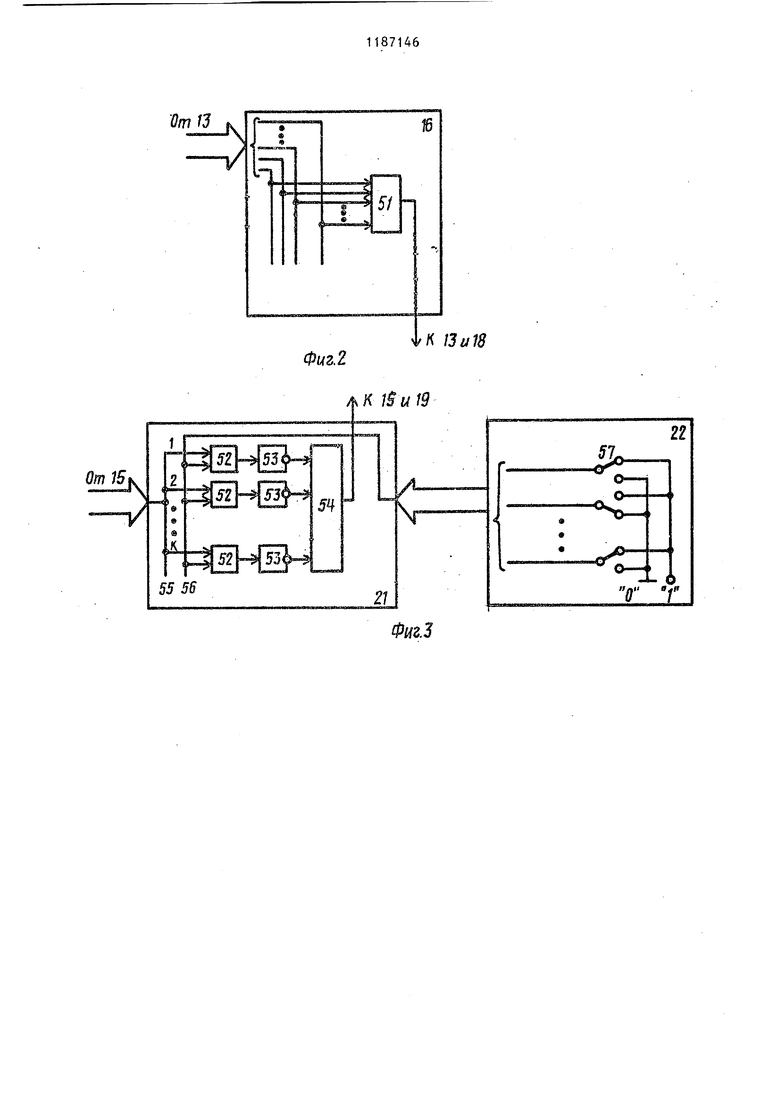

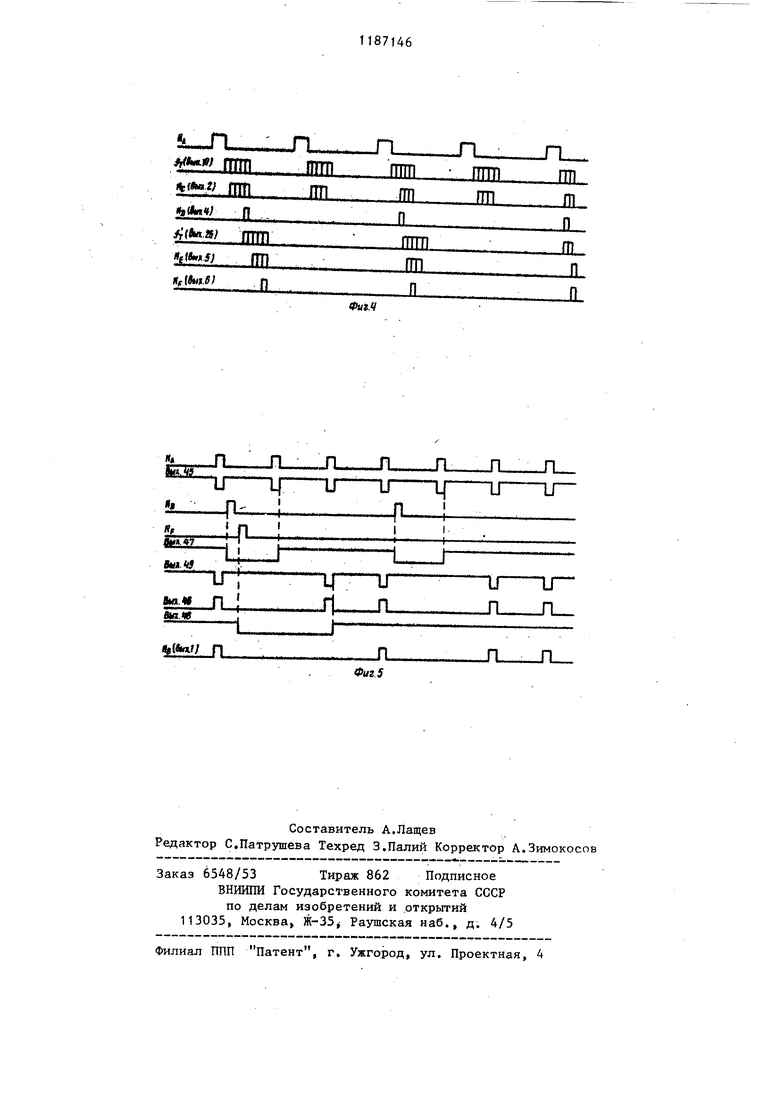

На фиг.1 приведена структурная

схема предлагаемого устройста; на фиг.2 - структурная схема дешифратора преобразователей единичного импульса в серию; на фиг. 3 - структурная схема блока совпадения и блока переключателей преобразователей единичного импульса в серию и делителей с регулируемым коэффициентом деления; на фиг.4 - временные диаграммы формирования импульсных последовательностей N и Мр; на фиг.5 - временные диаграммы работы блока вычитания.

Устройство состоит из блока 1 вычитания, первого преобразователя 2 единичного импульса в серию, датчика 3 параметра, первого делителя 4 с регулируемьм коэффициентом деления, второго преобразователя 5 единичного импульса в серию и второго делителя 6 с регулируемым коэффициентом деления. Первый вход .блока 1 вычитания является входом устройства, а его выход - выходЪм устройства. Датчик 3 параметра, первый преобразователь 2 единичного импульса в серию и первьй делитель 4 с регулируемым коэффициентом деления соединены последовательно. Первый делитель 4 с регулируемым коэффициентом деления подключен выходом к второму входу блока 1 вычитания, выход которого связан с вторым входом первого преобразователя 2 единичного импульса в серию.

Второй преобразователь 5 единичного импульса в серию соединен выходом с входом второго делителя 6 с регулируемым коэффициентом деления, выход которого подключен к третьему входу блока 1 вычитания. Второй преобразователь 5 единичного импульса в серию входом подключен к выходу датчика 3 параметра, а вторым входом - к выходу первого делитля 4 с регулируемым коэффициентом деления.

Первый преобразователь 2 -единичного импульса в серию содержит мультивибратор 7, первый, второй, третий, четвертый, пятый элементы И 8 - 12, первый, второй, третий счетчики 13 - 15, первый и второй деишфраторы 16 и 17, первый и второ

71464

триггеры 18 и 19, элемент НЕ 20, блок 21 совпадения и блок 22 переключателей, причем выход мультивибратора 7 подключен к первому входу 5 первого элемента И 8, выход которого- соединен с счетным входом первого счетчика 13, информационный вход первого дешифратора 16 связан с информационным выходом первого

10 счетчика 13, а выход - с соединенными вместе сбросовым входом первого счетчика 13 и первым входом первого триггера 18, выход которого подключен к первому входу

f5 второго элемента И 9, выходом связанного с соединенными вместе вторым входом первого элемента И 8 и первым входом третьего элемента И 10. Второй вход третьего элемента И 10 является первым входом преобразователя 2 единичного импульса в серию.

Выход элемента НЕ 20 подключен к второму входу второго элемента И 9, а вход соединен с вторым входом первого триггера 18 и является вторым входом преобразователя 2 единичного импульса в серию. Первые входы четвертого и пятого элементов И 11

и 12 соединены вместе и подключены к выходу третьего элемента И 10. Второй счетчик 14 подключен счетным входом к выходу четвертого элемента И 11, а информационным выходом - к информационному входу

второго дешифратора 17, выход которого связан с соединенными вместе сбросовым входом второго счетчика 14 и . первым входом второго триггера 19.

Третий счетчик 15 подключен счетным входом к выходу пятого элемента И 12, а информационным выходом - к первому информационному входу блока 21 совпадения, второй информационный

вход которого подключен, к информационному выходу блока 22 переключателей. Выход блока 21 совпадения связан с соединенными вместе сбросовым входом третьего счетчика 15 и вторым

входом второго триггера 19, инверсный выход которого соединен с вторым входом четвертого элемента И 11, а прямой выход - с вторым входом пятого элемента И 12, выход которого

является выходом преобразователя 2 единичного импульса в серию.

Второй преобразователь 5 единичного импульса в серию выполнен аналогично преобразователю 2 единичног импульса в серию и содержит мультивибратор 23, первый, второй, третий четвертый, пятый эльменты И 24 - 28 первый, второй, третий счетчики 2931, первый и второй дешифраторы 32 и 33, первый и второй триггеры 34 и 35, элемент НЕ 36, блок 37 совпадения и блок 38 переключателей. Первый делитель 4 с регулируемым коэффицентом деления содержит счетчик 39, счетный вход которого является входом делителя 4 с регулируемым коэффициентом деления, блок 40 переключателей и блок 41 совпадения, первый информационный вход которого подключен к информационному выходу счетчика 39, второй информационный вход - к информационному выходу блока 40 переключателей, а выход соединен с сбросовым входом счетчика 39 и является выходом делителя 4 с регулируемым коэффициентом деления.

Второй делитель 6 с регулируемьгм коэффициентом деления выполнен анало-гично первому делителю 4 с регулируемым коэффициентом деления и содержит счетчик 42, блок 43 переключателей и блок 44 совпадения.

Блок 1 вычитания содержит первый и второй инверторы 45 и 46 первый и второй триггеры 47 и 48, элемент И-НЕ 49 и элемент И 30, выход которого является выходом блока 1 вычитания, выход первого инвертора 45 подключен к первому входу первого триггера 47, инверсный выход которого подключен к входу элемента ИНЕ 49, второй вход которого соединен с входом первого инвертора 45 и является первым входом блока 1 вычитания, второй вход первого триггера 47 является входом блока 1 вычитания. Выход элемента И-НЕ 49 соединен с первым входом второго триггера 48, второй вход которого является третьим входом блока 1 вычитания. Инверсный выход второго триггера 48 подключен к первому входу элемента И 50,.выход элемента И-НЕ 49 через второй инвертор 46 свяэан с вторым входом элемента И 50. Третьи входы первого и второго триггеров .47 и 48 подключены к проводнику логического нуля.

Первый дешифратор 16 первого преобразователя 2 единичного импуль

са в серию содержит элемент И 51, входы которого образуют информационный вход первого дешифратора 16, а

5 выход элемента И 51 является выходом первого дешифратора 16. Второй дешифратор 17 первого преобразователя 2 единичного импульса в серию, а также первый дешифратор 32 и второй дешифратор 33 второго преобразователя 5 единичного импульса в серию выполнены. аналогично первому дешифратору 16 первого преобразователя 2 единичного импульса в серию.

5 Блок 21 совпадения первого преобразователя 2 единичного импульса в серию содержит ряд элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 52, ряд инверторов 53, элемент И 54, первую и вторую

0 информационные шины 55 и 56, при этом первые входы каждого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 52 образуют первую информационную шину 55, которая связана с первым информационным

Блок 37 совпадения второго преобразователя 5 единичного импульса в серию, а также блоки 41 и 44 совпадения делителей 4 и 6 с регулируемым коэффициентом деления выполнены аналогично блоку 21 совпадения первого преобразователя 2 единичного импульса в серию. Блок 22 переключателей преобразователя 2 единичного - импульса в серию содержит ряд переключателей 57, имеющих по три клеммы каждый, первые клеммы переключателей 57 подключены к информационному в 1ходу блока 22 переключателей, соединенные вместе вторые клеммы переключателей 57 подключены к проводнику логической единицы, а соединенные вместе третьи клеммы переключателей 57 подключены к проводнику логического нуля. Каждый переключатель 57 имеет два рабочих положения, в одном из которых замкнуты первая и вторая клеммы, а в другом - первая и третья клеммы. Блок 71 38 переключателей второго преобразователя 5 единичного импульса в серию, а также блоки 40 и 43 переклю чателей делителей 4 и 6 с регулируемым коэффициентом деления выполнены аналогично блоку 22 переключателей первого преобразователя 2 единичного импульса в серию. Устройство работает следующим образом. Входная импульсная последовательность Мд поступает на первый вход блока 1 вычитания и проходит через него на выход устройства без изменений до тех пор, пока на втором и третьем входах блока 1 вычитания отсутствуют импульсы. На первый вход первого преобразователя 2 единичного импульса в серию поступает частотный сигнал F с выхода датчика 3 параметра, пропорциональный параметру t : F п,. t, где п. - коэф.ициент передачи датчика 3 параметра. На второй вход первого преобразователя 2 единичного импульса в серию поступает выходная импульсная последовательность Ng с выхода блока 1 вычитания. Первы: преобразователь 2 единичного импульса в серию на кажды импульс, поступающий на его второй вход, пропускает на свой выход по п.2 F импульсов, поступающих на его первый вход. На его выходе появляется импульсная последовательность равная NC N, F NB п, п t. Ne, . где Nj - постоянный коэффициент, оп деляемый конструктивными особенностя ми преобразователя 2. Принцип работы преобразователя 2 единичного импульса в серию состоит в следующем. По заднему фронту импульса поступающему на его второй вход, начинает формироваться импульс стандартно длительности Т... Из импульсной .Пос ледовательности F, поступающей на первый вход преобразователя 2 едини ного импульса в серию, формируется вспомогательная последовательность f, состоящая из пакетов импульсов, причем каждый пакет импульсов имеет общую длительность Т,, состоит из ,импульсов последовательности F и 68 начало каждого пакета импульсов соответствует окончанию каждого импульса последовательности, поступающей на второй вход первого преобразователя 2 единичного импульса в серию. Импульсная последовательность f, делится на необходимый коэффициент (в общем случае имеющий целую и дробную части) и получанная в результате деления импульсная последовательность NJ проходит на выход преобразователя 2 единичного импульса -в серию. Передним фронтом импульса последовательности Ng, поступающей на второй вход первого преобразователя 2 единичного импульса в серию, первый триггер 18 устанавливается по второму входу (входу S) -в состояние 1. Сигнал логической единицы с его прямого выхода открывает второй элемент И 9 по первому входу. Импульсы последовательности Ng инвертируются элементом НЕ 20, Во время паузы последовательности N импульс с выхода элемента НЕ 20 проходит через открытый второй элемент И 9 на второй вход первого элемента И 8 и открывает его. В течение времени, когда первый элемент И 8 открыт импульсы опорной частоты .. от мультивибратора 7 проходят на счетный вход первого счетчика 13 и подсчитываются им. Когда число импульсов, подсчитанное первым счетчиком совпадет с числом, заданным первому дешифратору 16, последний выдаст сигнал логической един-ицы. Этот сигнал сбросит в ноль первый счетчик 13 по сбросовому входу и перзый триггер 18 по первому входу (входу R). При этом второй элемент И 9 закроется. В результате работы рассмотренной части преобразователя 2 единичного импульса в серию на выходе второго элемента И 9 будет сформирован импульс, длительность которого Tj, равна: ь т, где h - число импульсов,отсчитанное первым счетчиком 13; Т 1/ff. - период следования импульсов опорной частоты от мультивибратора 7. Передний фронт импульса Т. соответствует заднему фронту импульса последовательности Kg. Длительность

Т., выбирается равной около 1/3 минимального периода следования импульсов входной импульсной последовательности Мд, Импульсы с длительностью Т, поступают с выхода второго элемента И 9 5 на первый вход третьего элемента И Ю и открывагот его.На второй вход этого элемента поступают импульсы последовательности F с первого входа первого преобразователя 2 единичного Ю импульса в серию.На выходе третьего элемента И 10 формируется импульсная последовательность ff- , состоящая из пакетов импульсов, причем каждый ,пакет во времени соответствует пер- 15 Boff трети паузы в последовательности ; д. средняя частота последовательности t равна: т TC-F. N.g %.n,t. Ng (4) Импульсы последовательности f, поступают на первые входы четвертого и пятого элементов И 11 и 12, Второй триггер 19 находится при этом в исх ном нулевом состоянии. Сигналом, логи ческой единицы с его инверсного выхо открыт по второму входу четвертый элемент И 11, который пропускает импульсы последовательности f, на сч ный вход второго счетчика l4. Когда второй счетчик 14 отсчитает , импул сов, второй .дешифратор 17 сформирует На выходе сигнал логической единицы, который сбросит в ноль второй счетчик I4 и установит второй триггер 19 в состояние 1 по первому входу (входу S). При этом четвертый элемент И 11 закроется по второму входу. Сигнал Логической единицы, снимаемый с прямого выхода второго триггера 19, открывает пятый элемент И 15 по второму входу. Последу ощие импульсы последовательности f проходят на счетньй вход третьего счетчика 21 и подсчитываются им. Блоком 22 переключателей задается двоичный код числа а. При достижении количеством импульсов, подсчитанным третьим счетчиком 15, величиныf 2, блок совпадения 21 сформирует сигнал логической единицы, который сбрасывает в ноль третий счетчик 15 и второй триггер 19 по второму входу (входу R). При этом пятый элемент И 12. закрывается по второму вхбду, а четвертый элемент И 11 открывается по второму вх

ду. Работа второй части преобразователя 2 единичного импульса в серию начинает повторяться.с выхода пятого элемента И 12 импульсы проходят на выход преобразователя 2 единичного импульса в серию, образуя им-. пульсную последовательность N, которая формируется из импульсной последовательности f так, что из каждых ( + Лг импульсов пох;ледовательности f последовательность N содержит й импульсов.. При этом частота импульсной -последовательности N равна:

it

N, ЧАЛ07 --, СоответствуюЕца:м: выбором значений Т., /Д, и i2 добиваются необходимого значения п, Принцип работы первого дешифратора 16 состоит в следующем. К информационному входу первого дешифратора 1 б подгазючены выходы тех ячеек первого счетчика 13, которые соответствуют единицам двоичного кода дешифруемого числа h. Поскольку первый счетчик 13 начинает цикл своей работы из начального нулевого состояния, то первое его состояние, при котором на всех входах элемента И 51 первого дешифратора 16 будут присутствовать логические единицы, соответствует коду числа h. Последующий сброс первого счетчика 13 исключает ошибочные срабатывания первого дешифратора 16. Принцип работы второго дешифратора 17 аналогичен принципу работы первого дешифратора 16. Принцип работы блока 2.1 совпадения состоит в следзжзщем. На первый и второ -информационные входы поступают двоичные коды с информационных выходов третьего счетчика 15 и блока 22 .переключателей, проходят по информационным шинам 55 и 56 и подаются на входы ряда элементов ИС1Ш10ЧАЮЩЕЕ РШИ 52. Каждый элемент ИСКЛЮЧАЮЩЕЕ Ш1И соответствует одному разряду числа Ag Когда значения сигналов на входах отдельного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ совпадают, па его выходе формируется сиг.-, нал логического нуля который инвертируется одним из элементов НЕ ряда элементов НЕ 53. Сигнал логической единицы поступает с выхода элемента НЕ на один из входов элемента И 54, Присутствие сигналов логической единицы на всех входах элемента И 5 соответствует совпадению числа, под считанного третьим счетчиком 15, числу Д заданному блоком 22 переключателей. При этом на выходе элемента И 54 формируется сигнал логической единицы, который проходит на выход блока21 совпадения. Принцип работы блока 22 переключателей состоит в следующем. Ряд переключателей 57 состоит из числа переключателей, равного разрядности числаJV Переводя переключатели в первое или второе рабочее полохсение, задают в каждом разряде числа соответственно Импульсная последовательность N. с выхода первого преобразователя 2 единичного импульса в серию поступаетНа вход первого делителя 4 с регулируемым коэффициентом деления и делится им на коэффициент деления п задаваемый вручную. На выходе первого делителя 4 с регу лируемым коэффициентом деления полу чается импульсная последовательност Njj равная: iNc п Пг - t N п Принцип работы блоков 40 и 22 пе реключателей, а также блоков 41 и 21 совпадения взаимно аналогичны. На первый вход второго преобразователя 5 единичного импульса в серию поступает частотный сигнал F с выхода датчика 3 -параметра, а (ria второй вход - импульсная последовательность Мд с выхода первого делителя 4 с регулируемым коэффициентом деления. Второй преобразователь 5 единичного импульса в серию пропускает на каждый импульс последовательности Nj, по импульсов от датчика 3 параметра. При этом на его выходе появляется им- пульсная последовательность Ng , равная: N,n,.F..N где . - постоянный коэффициент, определяемый конструктивными особенностями преобразователя 5 Чаналогично коэффициенту п). Принцип работы второго преобразователя 5 единичного импульса в серию аналогичен принципу работы первого преобразователя 2 единичного импульса в серию. Различие их в работе состоит в том, что на его второй вход поступает импульсная последовательность Np вместо последовательности Ng. При этом начало формирования импульса стандартной длительности Т., совпадает с задним фронтом импульса последовательности NJJ. На выходе этого преобразователя получают импульсную последовательность Ng , равную: м JT , .i . .1 x; r-i-Nn h4n,iN KtTvJ/V (.4Л,, , л;где tl - аналоги коэффициентов , и f соответственно для первого преобразователя 2. Импульсная последовательность NP с выхода второго преобразователя 5 единичного в серию поступает на вход второго делителя 6 с регулируемым коэффициентом деления и делится им на коэффициент деления п, задаваемый вручную. На выходе второго делителя 6 с регулируемым коэффициентом деления получают импульсную последовательность NP , равную: -i- - ,- . Принцип работы второго делителя 6с регулируемым коэффициентом деления аналогичен принципу работы первого делителя 4 с регулируемым коэффициентом деления. Импульсы последовательностей Ыд, NJJ и Np.He совпадают во времени друг с другом при работе устройства (фиг.4). Импульсы последовательности Njj по существу являются отдельными импульсами из пакета импульсов вспомогательной импульсной последовательности f первого преобразователя 2 единичного импульса в серию, а пакет импульсов f соответствует не более чем трети паузы импульсной последовательности Кд. Пакет импульсов вспомогательной импульсной последовательности f JJ. второго преобразователя 5 единичного импульса в серию соответствует началу паузы после формирования импульса последовательности Njj и имеет длительность не более чем треть паузы импульсной последовательности Nд. В свою очередь импульсы последовательности NP являются отдельными импульсами из пакета импульсов вспомогательной импульсной последовательности f . Таким образом, им пульсы последовательностей Нд , Np и Nft не совпадают между собой по времени. Блок 1 вычитания осуществляет вы читание импульсных последовательностей Njj и Np из входной импульсной последовательности Nд. Временны диаграммы, приведенные на фиг.5, соответствуют максимальной частоте Нд. При включении питания устройства первый и второй триггеры 47 и 48 принудительно устанавливаются в исходное нулевое состояние. (Цеп начальной установки триггеров 47 и 48 в исходное состояние на фиг.1 не показана). Импульсная последовательность Ыд инвертируется первым элементом НЕ 45 и передается на первый вход (вход С) первого триггера 47. На третий вход (вход D) этого триггера постоянно подается логический ноль При отсутствии импульсов последовательности NJJ на втором входе блок 1 Jычитaния импульсы с выхода первого элемента НЕ 45 подтверждают нулевое состояние первого триггера 47. Сигнал логической единицы с инверсного выхода первого триггера 47 открывает элемент И-НЕ 49 по пер вому входу. Импульсы последовательности Nft-поступают на второй вход элемента И-НЕ 49, инвертируются ими и поступают на первый вход (вход С второго триггера 48. На третий вход (вход D) второго триггера 48 постоянно подается логический нол При отсутствии последовательности Np на третьем входе блока 1 вычитания импульсы .. выхода элемента И-НЕ 49 подтверждают нулевоесостояни второго триггера 48. Сигнал логичес кой единицы с инверсного выхода второго триггера 48 открывает элемент И 50 по первому входу. Импульсы псюледовательности Nj, проинвертировамные ранее с помощью элемента И-НЕ 49, инвертируются повторно 61 элементом НЕ 46 и проходят через элемент И 50 на выход блока 1 вычитания. Таким образом, при отсутствии импульсов на втором и третьем входах блока вычитания импульсы входной последовательности проходят на его выход без изменений. При -поступлении импульса последовательности Nj) на второй вход блока 1 вычитания первый триггер 47 устанавливается в единицу по второму входу (входу S). В дальнейшем первый триггер 47 сбрасывается в ноль передним фронтом импульса, поступающего на его первый вход (этот фронт соответствует заднему фронту импульса последовательности Нд). На инверсном выходе первого триггера 47 в течение времени от переднего фронта импульса последовательности Мд до последующего заднего фронта импульса последовательности N будет логический ноль.Это приведет к тому,что на выходе элемента И-НЕ 49 во время существования импульса последовательности N не будет соответствующей паузы, а на выходе второго элемента ЙЕ 46 не будет соответствующего импуль са. Элемент И 50 будет открыт по первому входу, но на выход блока вычитания импульс последовательности NflHe поступит. При появлении последующих импульсов на втором входе блока 1 вычитания вычитание импульсов осуществляется аналогично. При поступлении импульса последовательности NP на третий вход блока 1 вычитания второй триггер 48 устанавливается в единицу по второму входу (входу S). В дальнейшем второй триггер 48 сбрасывается в ноль передним фронтой импульса, поступающего на его первый вход (этот фронт соответствует заднему фронту импульса последовательности разностной частоты Кд- NO выходе второго элемента НЕ 46). На инверсном выходе второго триггера 48 в течение времени от переднего фронта импульса последовательности NP до последующего заднего фронта импульса последовательности N( будет логический ноль. Это приведет к тому,что на это время закрыт элемент И 50 по первому входу и на выходе блока вычитания не появится импульс последовательности N( .Таким I образом, на выходе блока 1 вычита5, ния формируется выходная импульсная последовательность N , равная: NB N. - Np N - NO - Np 1, -3 НВ-МА-ТЦ - ЧЦ : откуда I t.--i Если обозначить k.- - и - n 3 TO формула (12) будет иметь вид: в 1 + k, t + k,kjt Таким образом, предлагаемое устро ство реализует формулу, коэффициенты k. которой задаются независимо друг от друга путем необходимого вы бора коэффициентов п-. п, Пу соответственно. Точность коррекции числа импульсов по входному параметру можно дополнительно повышать. При этом необходимо в устройство дополнительно ввести преобразователи единичного импульса в серию и делители частоты с регулируемым коэффициентом деления в количестве (п - 2), где n показатель степени переменного параметра. Каждый вводимый преобразователь единичного импульса в серию подключается к выходу датчика параметра и выходу предьщущего делителя частоты с регулируемым коэффициентом деления, а выходом - к входу вводимого делителя с регулируемым коэффициентом деления, подключаемого выходом к новому входу блока вычитания Таким же образом должны соединяться последующие преобразователи единичного импульса в серию и делители с регулируемым коэффициентом деления. Использование новых блоков и их связей в устройстве для коррекции чи ла импульсов по входному параметру позволит получить экономический 616 I эффект, в частности при измерении расхода сырого газового конденсата за счет повЕ 1шения точности коррекции на 0,5 - 2,0%. Так, при транспортировке сырого газового конденсата по трубопроводам в результате падения давления потока АР на гидравлических сопротивлениях происходит активное газовьщеление и поток приобретает двухфазную газожидкостную структуру. Общий объем конденсата возрастает, так как плотность образовавшейся газовой фазы на порядок ниже плотности исходной жидкости. Измеренный расход такого двухфазного потока необходимо корректировать, умножая на коэффициент k , который нелинейно убывает с увеличением перепада давления ЛР. Если аппроксимировать экспериментально полученные значения коэффицента k уравнением вида 1 + k,&P (13) то при обработке данных методом наименьших квадратов получаем значение k| 0,1127776 (для интервала А 0 - 1,0 Ша), при котором максимальная относительная погрешность воспроизведения формулой (13) зависимости k f ( .А Р) составляет 2,62%. Если аппроксимировать те же значения коэффицента k уравнением вида 1 + k,( ЛР)+ k, k2( АР) то по методу наименьших квадратЪв получаем значения k 0,0030704, k5 A3,670726, при которых максимальная относительная погрешность , воспроизведения формулой (14) зависимости k . (АР) составляет 0,7%. ТакшТ образом формула (14) значительно-,точнее воспроизводит зависимость, f (А Р), поэтому она предпочтительнее для коррекции расхода газожидкостного потока сырого газового конденсата.

OmJl

«

-И

Фмг,2 От

К J3uW

А Я / W /

%г.5 15к

| УСТРОЙСТВО для КОРРЕКЦИИ ЧИСЛА ИМПУЛЬСОВ по ВХОДНОМУ ПАРАМЕТРУ | 0 |

|

SU334544A1 |

Авторы

Даты

1985-10-23—Публикация

1984-08-25—Подача