(54) УСТРОЙСТВО ДЛЯ ЛИНЕАРИЗАЦИИ ХАРАКТЕРИСТИК ИЗМЕРИТЕЛЬНЫХ ПРЕОБРАЗОВАТЕЛЕЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для линеаризации характеристик измерительных преобразователей | 1982 |

|

SU1037266A1 |

| Устройство для линеаризации характеристик измерительных преобразователей | 1982 |

|

SU1056220A1 |

| Устройство для линеаризации характеристик измерительных преобразователей | 1981 |

|

SU991436A1 |

| Устройство для линеаризации характеристик измерительных преобразователей | 1983 |

|

SU1126978A1 |

| Устройство для вычисления функции линеаризации | 1980 |

|

SU905831A1 |

| Устройство для кодирования сигналов частотных датчиков | 1985 |

|

SU1336246A1 |

| Аппроксимирующий функциональный преобразователь | 1983 |

|

SU1160430A1 |

| Многоканальное устройство для обработки первичной информации | 1984 |

|

SU1234851A1 |

| Устройство для измерения давления | 1988 |

|

SU1525503A1 |

| Измерительный функциональный преобразователь | 1981 |

|

SU984042A1 |

Изобретение относится к вычислительной и измерительной технике и предназначено для использования в многокансшьных измерительных системах с различными типагли измерительных преобразователей, имеющих нелинейные передаточные характеристики.

Известно устройство для линеаризации характеристик измерительных преобразователей, содержащее узел вычитания и суммирования импульсов, два счетчика, комг тационную матрицу, дешифратор участков аппроксимации и делитель частоты LlJ.

Известен также специализированный цифровой чистотомер, содержа1.чий линеаризатор измеряемой величины С 2.

Недостатком указанных устройств является то, что казкдое из них работает с однотипными измерительными преобразователями, имеющими одинаковые нелинейные характеристики.

Наиболее близким из известных устройств по технической сущности к изобретению является устройство для линеаризации характеристик измерительных преобразователей, которое содержит блок вычитания и cyi nvmpoв.ания, два счетчика, дешифратор, Де:яитель частоты, ком1-1утируюсдую матрицу и блок выбора характеристик, состоящий из наборного поля и переключателя Цз}.

Недостаток указанного устройства заключается в том, что при увеличении числа типов измерительных преобразователей пропорционально увеличивается число шин участков аппроксимации наборного поля и усложняется переключатель, что приводит к значительному усложнению блока выбора характеристик.

Целью изобретения является упрощение устройства.

Поставленная цель достигается тем, что устройство, содержащее блок вычитания и суммирования, два счетчика, делитель частоты, комг татор, первый и второй выходы которого сое20динены соответственно с первым и вторым входс1ми блока вычитания и суммирования, третий вход которого является информационны / входом устройства, выход блока вычитания и суммиро25вания соединен с входом первого счетчика, первый выход которого соединен с информационным входом коммутс1тора, второй выход первого счетчика соединен со входом делителя частоты, вы30ход которого подключен к входу второго счетчика, содержит постоянный запоминающий блок, младшие разряды адресного входа которого соединены с выходом второго счетчика, выход постоянного запоминающего блока подключен к управляющему входу кoм vтатора, старшие разряды адресного входа постоянного запоглинающего блока соединены с управляющим входо устройства. Блок вычитания и суммирования в устройстве содержит элементы И, ИЛИ, триггеры, причем первые входы первбго и второго элементов И и тактовый вход первого триггера соединены с третьим входом блока, второй вход второго элемента И является вторым входом блока, третий вход второго элемента И подключен к первому выходу первого триггера, второй выход которого подклю1ен к второму входу первог о элемента и к первому входу второго триггера, второй вход которого является лервым входом блока, выход второго триггера соединен с информационным входом первого триггера, выход первого элемента И соединен с входом третьего триггера, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, выход

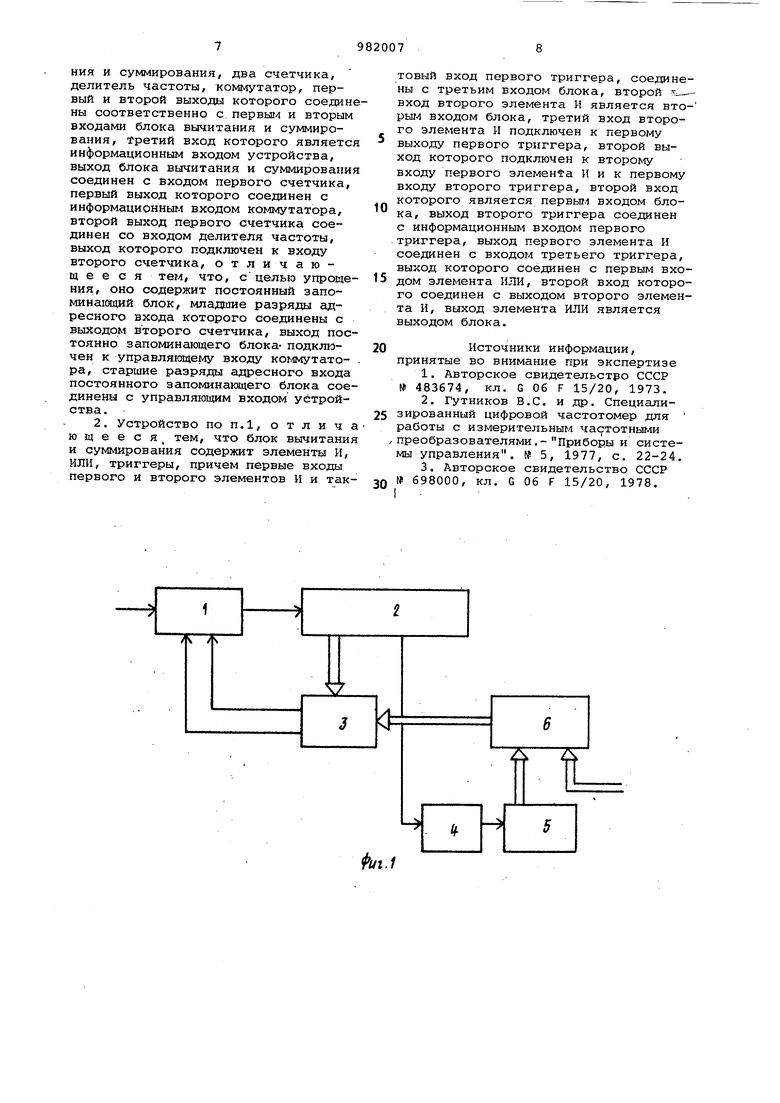

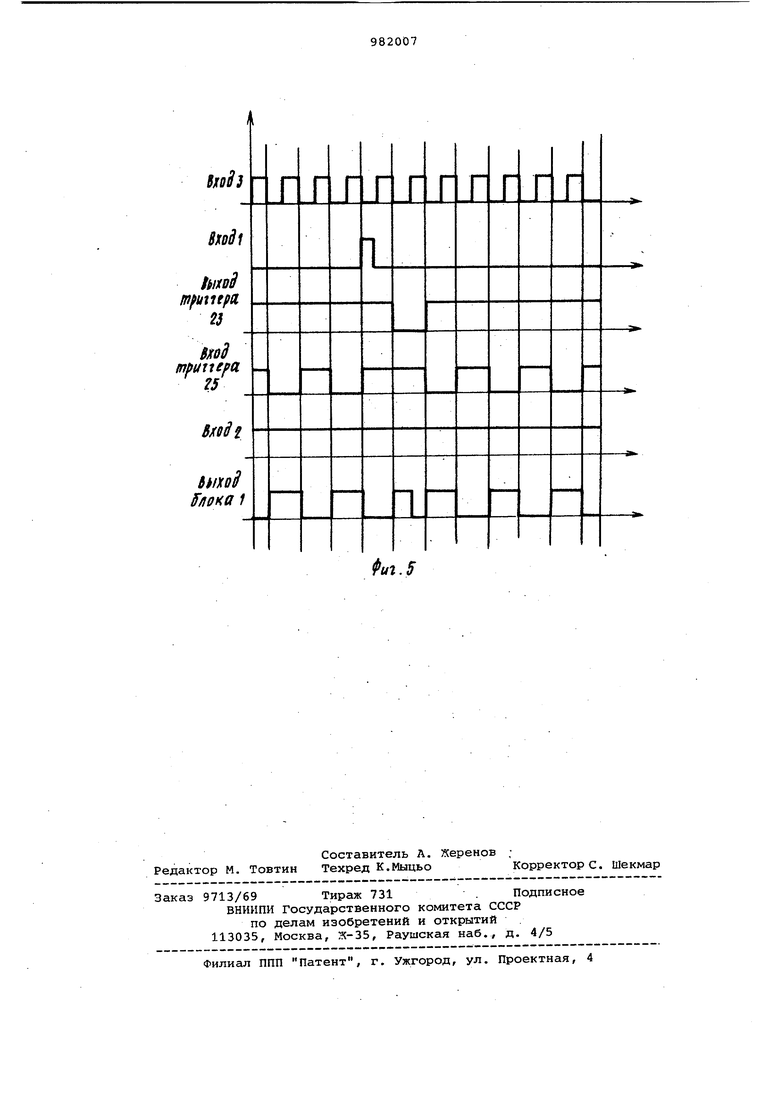

элемента ИЛИ-является выходом блока I...-На фиг, 1 изображена лок-схема устройства; на фиг. 2 - функциональная схема KOi.iMyTaTopa} на фиг. 3 функциональная схема блока вычитания и суммирования; нафиг. 4 и 5 временные диаграмг-и работы блока вычитания и суммирования для режима вычитания и режима суммирования соответственно.

Устройство содержит блок 1 вычитания и суммирования, вход которого соединен с выходом преобразователя параметра в число импульсов (на фигуре не показан), а выход - со входом первого счетчика 2. Выходы счетчика 2 подключены к информационным входам коммутатора 3, причем первый и второй выходы коммутатора 3 соединены спервым и вторым входами блока 1 вычитания и суммирования. К одному из выходов первого счетчика 2 подключен вход делителя частоты 4, выход которого соединен со входом второго счетчика 5, выходы которого соединены с младшими разрядами адресного входа постоянного запоминающего блока 6. Выход постояного запоминающего блока б подключе к управляющим входам ког мутатора 3, причем разряды адресного входа постоянного запог/шнающего блока служат ДЛЯ выбора типа линеаризуемой характеристики.

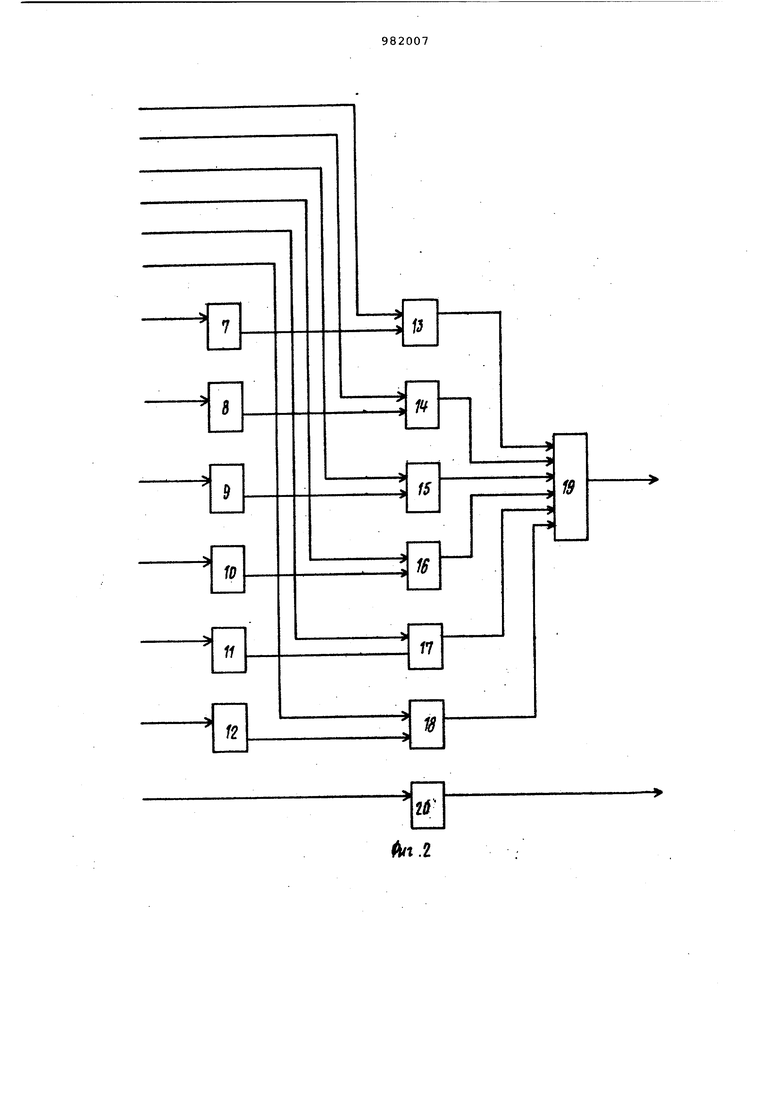

Коммутатор 3 содержит (фиг. 2) группу дифференцирующих цепочек 7-1

входы которых являются информационными входами ког мутатора 3. Выходы дифференцирующих цепочек 7-12 подключены ко входам элементов И 13-18, вторые входы которых являются управляющими входами коммутатора 3. Выходы элементов И 13-18 подключены ко входам элемента ИЛИ 19, выход которого является первым выходом коммутатора 3. Один из управляющих входов коммутатора. 3 подключен к буферному усилителю 20. Выход буферного усилителя 20 является вторым выходом коммутатора 3.

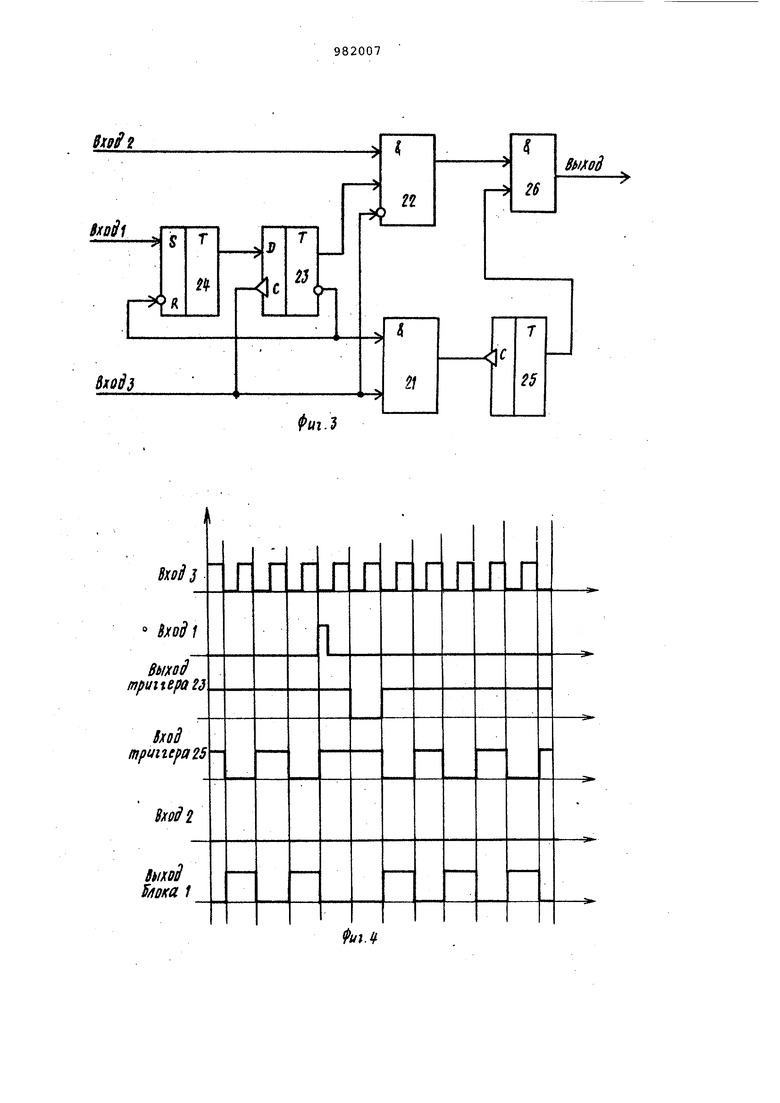

Блок вычитания и суммирования 1

5 содержит (фиг. 3) элемент И 21, один из входов которого соединен с третьим входом блока 1. К третьему входу блока 1 подключены первый вход элемента И 22 и тактовый вход тригге0 Ра 23. Второй вход элемента И 22

является вторым входом блока 1 вычитания и суммирования, а третий вход элемента И 22 подключен к прямому выходу триггера 23. Инверсный выход

5 триггера 23 подключен ко второму входу элемента И 21 и входу триггера 24, другой вход которого является первыгл входом блока 1 вычитания и суммирования 1. Прямой выход триг,„ гера 24 соединен с входом триггера 23. Выход элемент И 21 соединен с тактовым входом триггера 25, выход которого соединен с первым входом элемента ИЛИ 26, второй вход которого соединен с выходом элемента И 22, а выход является выходом блока 1 вычитания и суммирования.

Работа устройства заключается в реализации передаточной функции, осуществляющей кусочно-линейную аппроксимацию функции, обратной линеаризуемой характеристике.

На вход блока 1 вычитания и сурлмирования от преобразователя параметр5 число импульсов (не показан) поступает последовательность импульсов. В зависимости от кода, поданного на старшие разряды адресного входа постоянного запо1-1инающего блока б и текущего состояния счетчика 5 с выхода постоянного запоминающего блока б на управляющие входы коммутатора 3 поступает управляющий код Он разрешает прохождение соответствующего числа импульсов, сформированных на

55 выходах счетчика 2, на входы блока 1 вычитания и суммирования. Это число импульсов добавляется к последовательности импульсов от преобразователя параметр - число импульсов или

60 вычитается из нее на данном участке аппроксимации нелинейной характеристики. В результате на вход счетчика 2 поступает линеаризированная последовательность импульсов. Делитель 4 65 частоты служит для разбивки на участки аппроксимации. Выбор коэффициента деления для делителя 4 частоты а также выбор счетчика 2, к котором подключен делитель 4 частоты, осуществлен исходя из.равенства коэффициента деления последовательности входных импульсов числу, соответствующему величине участка аппроксимации. Таким образом осуществлена разбивка полного диапазона входного параметра на равные по длине участки аппроксимации. Переключение участков аппроксимации производится счетчиком 5, смена состояния в котором происходит при поступлении на вход счетчика-2 определенного числа входных импульсов, соответствующего длине участка аппро ксимации . Н& информационные входы коммутатора 3 поступают с выходов триггеров счетчика 2. По переходу триггеров счетчика 2 в единичное состояние дифференцирующие цепочки 7-12 вырабатывают импульсы, прохождение которых через элемент И 13-18 на входы элемента ИЛИ .19 и на первый выход коммутатора 3 определяется логическими уровнями на соответствую щих управляющих входах коммутатора. При этом число импульсов, которые проходят на первый выход кoм Iyтaтopa 3 за цикл счетчика 2, равно коду, . поступающему на управляющие входы кo 1мyтaтopa 3. К одному из управляющих входов подключен вход буферного усилителя 20. Уровень сигнала, поступающего с буферного усилителя 20 на второй выход коммутатора 3, определяет, будут ли выходные импульсы коммутатора добавляться к входной последовательности -импульсов на блоке 1 вычитания и суммирования или Су дут запрещать прохонутение соответствующего числа импульсов входной последовательности. Работа блока 1 вычитания и суммирования описана по временным диаграммам, приведенны:- на фиг. 4 (режим вычитания) и на фиг.5 (режим суммирования). 1 Перед началом работы устройства необходимо установить триггер 23 в ну левое состояние. На вход блока 1, являющийся информационным входом уст ройства поступает импульсная последовательность от преобразователя параметра в число импульсов, частота которой делится на два триггером 25 и поступает через элемент ИЛИ 26 на выход блока 1. При поступлении на первый вход блока импульса с первого выхода коммутатора 3 триггер 24 уста навливается в единичное состояние. Логическая единица, поступающая на вход триггера 23 с выхода триггера 24, разрешает переключение триггера 23 в единичное состояние. При этом уровень логического нуля, поступающий с инверсного выхода триггера 23 на вход триггера 24, сбрасывает триггер 24 в нулевое состояние. Сформированный на инверсном выходе триггера 23 импульс в течение периода входной частоты запрещает про. хождение одного и 1пyльca с входом блока 1 через элемент И 21 на вход триггера 25. Логический уровень на втором входе блока вычитания и суммирования 1 определяет режим работы блока. Если на втором входе логический нуль (режим вычитания), то сформированная на выходе триггера 25 импульсная последовательность через элемент ИЛИ 26 проходит на выход блока 1. Сформированная на выходе блока 1 последовательность соответствует вычитанию одного импульса из входной последовательности импульсов. Если на втором входе блока 1 логическая единица (режим суг.1мирования, то сформированный на прямом выходе триггера 23 импульс разрешает прохождение на выход элемента И 22 одного импульса входной последовательности. Cфop лиpoвaнный таким образом импульс с выхода элемента И 22 поступает на вход элемента И 26 и добавляется к импульсной последовательности, cфop 1иpoвaнной на выходе триггера 25. Полученная импульсная последовательность поступает на выход блока 1. При отсутствии иьтульсов на первом входе блока 1 вычитания и суммирования независимо от уровня сигнала на втором входе блока 1 импульсная последовательность, поступающая на информационный вход, проходит через элемент И 21, делится на два на триггера 25 и проходит на выход блока 1 через элемент ИЛИ 26. Постоянный запоминающий блок 6 хранит управляющие коды коммутатора для каждого участка аппроксимации всех линеаризуемых характеристик. Выборка управляющего кода осуществляется путем подачи на старише разряды адресного выхода постоянного запоминающего блока 6 кода, соответствующего типу Линеаризуемой характеристики, а на младшие разряды адресного входа - кода участка аппроксимации . Изобретение упрощает схему устройства линеаризации, предназначенного для работы с разнотипными измерительными преобразователями. Формула изобретения 1. Устройство для линеаризации характеристик измерительных преобразователей, содержащее блок вычитания И суммирования, два счетчика, делитель частоты, коммутатор, первый и второй выходы которого соединены соответственно с. первыг/ и вторым входами блока вычитания и суммирования, третий вход которого является информационным входом устройства, выход блока вычитания и суммирования соединен с входом первого счетчика, первый выход которого соединен с информационным входом коммутатора, второй выход первого счетчика соединен со входом делителя частоты, выход которого подключен к входу второго счетчика, отличающееся тем, что, с целью упрощения, оно содержит постоянный запомина1адий блок, младшие разряды адресного входа которого соединены с выходом второго счетчика, выход постоянно запоминающего блока- подключен к управля1още1.1у входу ког/мутатора, старшие разряды адресного входа постоянного запоминающего блока соединены с управляющим входом устройства.

вход второго элемента И является вторы - входом блока, третий вход второго элемента И подключен к первому выходу первого триггера, второй выход которого подключен к втopo 1y входу первого элемента И и к первому входу второго триггера, второй вход которого является первым входом блока, выход второго триггера соединен с информационным входом первого .триггера, выход первого элемента И соединен с входом третьего триггера, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, выход элемента ИЛИ является выходом блока,

0Источники информации,

принятые во внимание при экспертизе

работы с измерительным частотными /преобразователями.- Приборы и системы управления, 5, 1977, с. 22-24.

8шод трипе pa 23

Sxod триггера 25

8шоЗ 5/1 ока 1

8ШоЗ

26

fZ

Фиг.

Авторы

Даты

1982-12-15—Публикация

1981-01-08—Подача