11

Изобретение относится к измерительной технике и может быть использовано в качестве оборудования для автоматизации научных исследований в области ядерной физики, в частноети в ряде физических эксперимеТИтов, использующих время пролетную методику измерений.

Целью изобретения является повы- шение точности измеренит многосто- нового преобразователя временных интервалов в цифровой к,од TiyTeM уменьшения ее зависимости от числа разря дов двоичного счетчика.

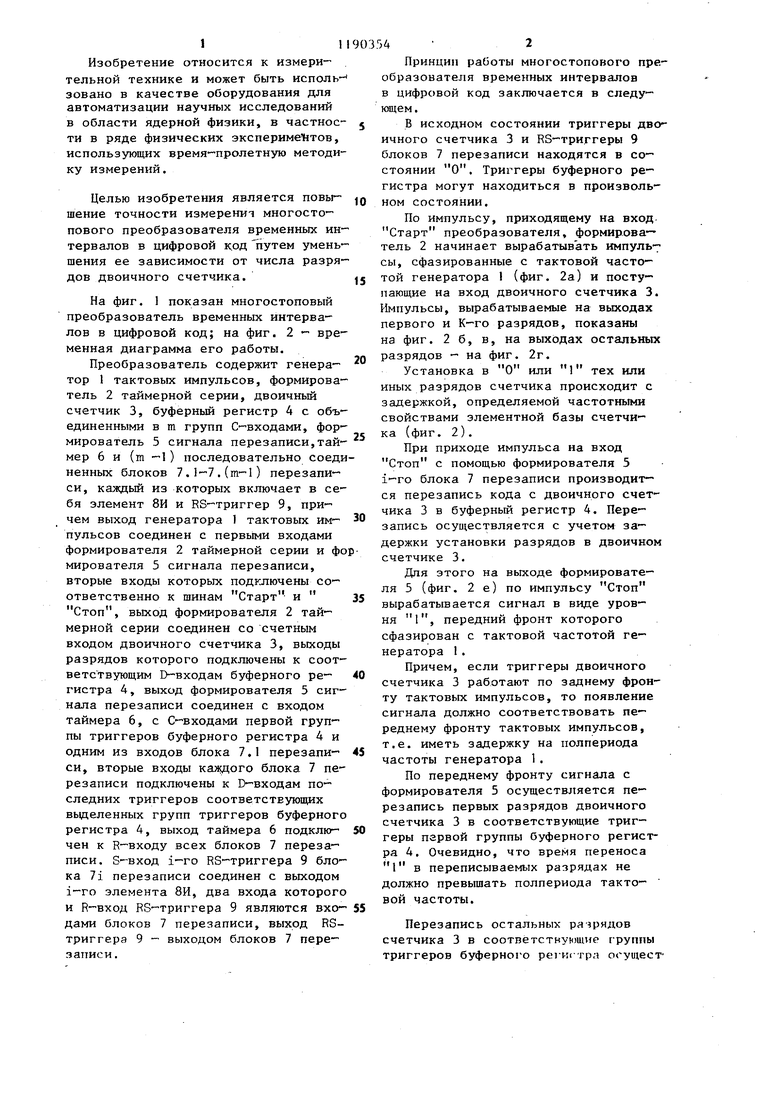

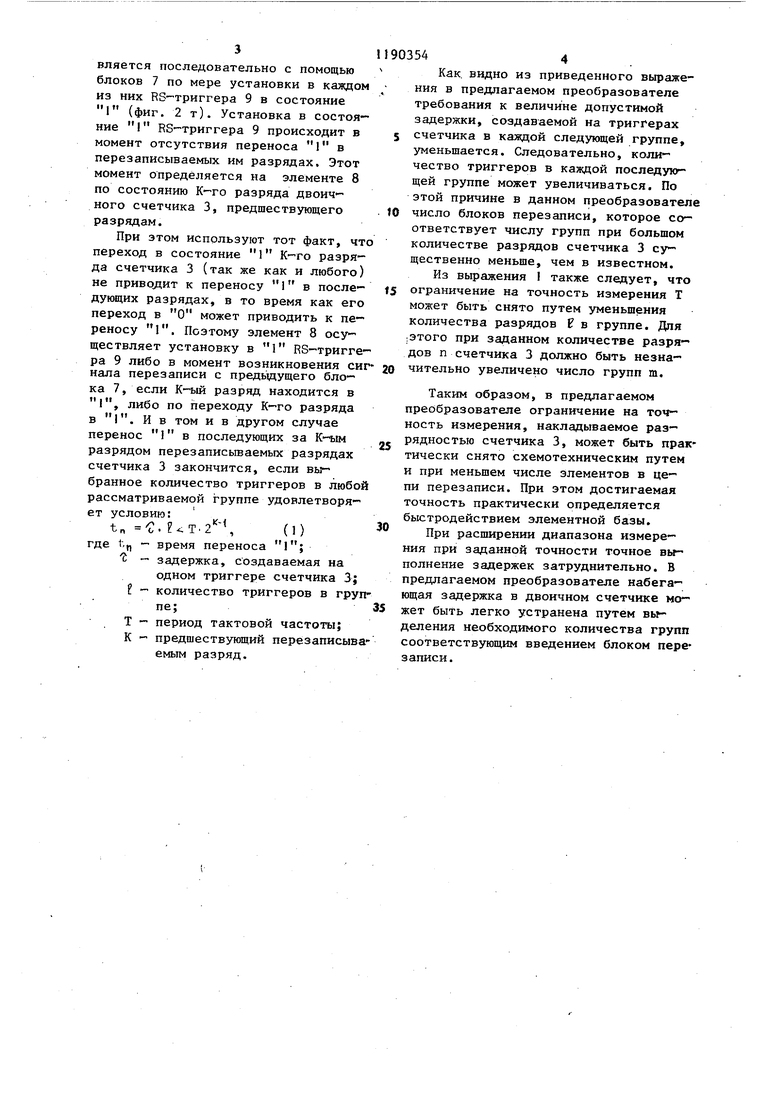

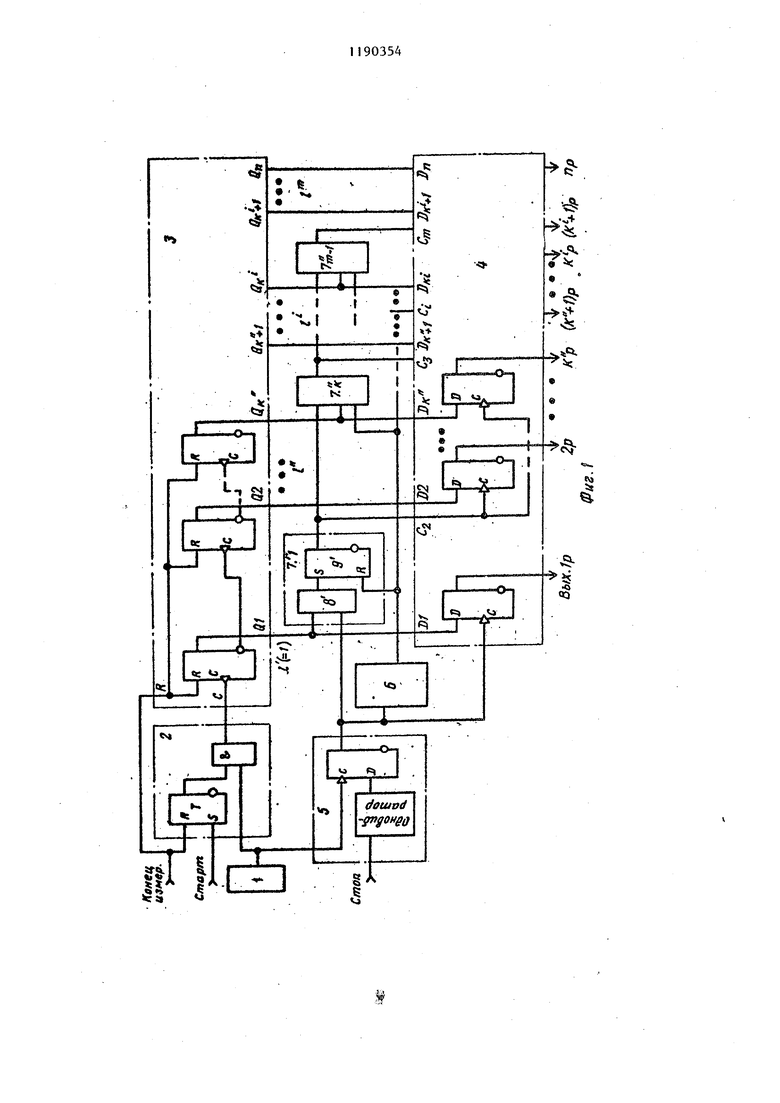

На фиг. 1 показан многостоповый преобразователь временных интерва лов в цифровой код; на фиг. 2 - временная диаграмма его работы.

Преобразователь содержит генера- тор 1 тактовых импульсов, формирователь 2 таймерной серии, двоичный счетчик 3, буферный регистр 4 с объединенными в m групп С-входами, формирователь 5 сигнала перезаписи,таймер 6 и (га 1) последовательно соединенных блоков 7.1-7.(т-1) перезаписи, каждый из которых включает в себя элемент 8И и RS-триггер 9, причем выход генератора 1 тактовых им- пульсов соединен с первь1ми входами формирователя 2 таймерной серии и фомирователя 5 сигнала перезаписи, вторые входы которых подключены соответственно к шинам Старт - и Стоп, выход формирователя 2 тай- мерной серии соединен со счетным входом двоичного счетчика 3, выходы разрядов которого подключены к соответствующим D-входам буферного ре- гистра 4, выход формирователя 5 сих- нала перезаписи соединен с входом таймера 6, с С-входами первой группы триггеров буферного регистра 4 и одним из входов блока 7.1 перезаписи, вторые входы каждого блока 7 перезаписи подключены к D-входам последних триггеров соответствующих выделенных групп триггеров буферного регистра 4, выход таймера 6 подключен к К-входу всех блоков 7 перезаписи. S-вход i-ro RS-триггера 9 блока 7 i перезаписи соединен с вькодом i-ro элемента 8И, два входа которого и R-вход RS-триггера 9 являются вхо- дами блоков 7 перезаписи, выход RSтриггера 9 - выходом блоков 7 перезаписи.

54 2

Принцип работы многостопового преобразователя временных интервалов в цифровой код заключается в следующем.

В исходном состоянии триггеры двоичного счетчика 3 и RS-триггеры 9 блоков 7 перезаписи находятся в состоянии О. Триггеры буферного регистра могут находиться в произвольном состоянии.

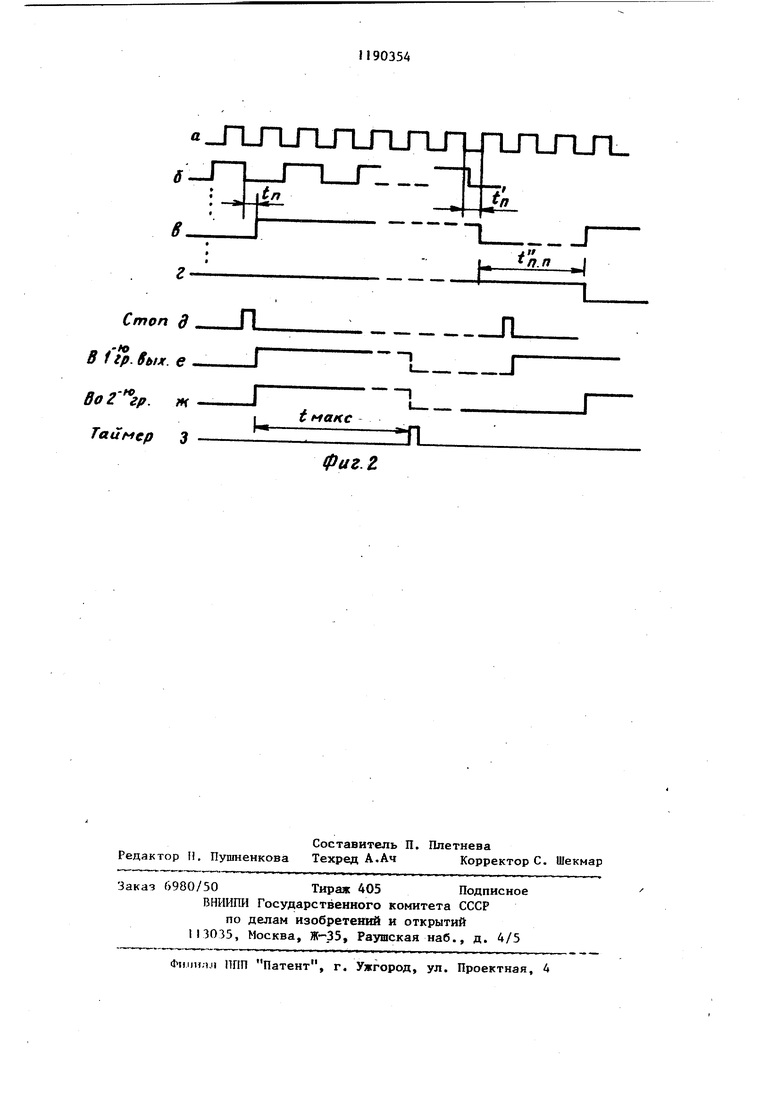

По импульсу, приходящему на вход Старт преобразователя, формирователь 2 начинает вырабатывать импуль-7 сы, сфазированные с тактовой частотой генератора 1 (фиг. 2а) и поступающие на вход двоичного счетчика 3. Импульсы, вырабатываемые на выходах первого и К-го разрядов, показаны на фиг. 2 б, в, на выходах остальных разрядов - на фиг. 2г.

Установка в О или 1 тех или иных разрядов счетчика происходит с задержкой, определяемой частотными свойствами элементной базы счетчика (фиг. 2).

При приходе импульса на вход Стоп с помощью формирователя 5 i-ro блока 7 перезаписи производится перезапись кода с двоичного счетчика 3 в буферный регистр 4. Перезапись осуществляется с учетом задержки установки разрядов в двоичном счетчике 3.

Для этого на выходе формирователя 5 (фиг. 2 е) по импульсу Стоп вырабатывается сигнал в виде уровня 1, передний фронт которого сфазирован с тактовой частотой генератора 1 .

Причем, если триггеры двоичного счетчика 3 работают по заднему фронту тактовых импульсов, то появление сигнала должно соответствовать переднему фронту тактовых импульсов, т.е. иметь задержку на полпериода частоты генератора 1.

По переднему фронту сигнала с формирователя 5 осуществляется перезапись первых разрядов двоичного счетчика 3 в соответствующие триггеры первой группы буферного регистра 4. Очевидно, что время переноса 1 в переписываемых разрядах не должно превышать полпериода тактовой частоты.

Перезапись остальных разрядов счетчика 3 в соответствующие группы триггеров буферного ре)-И(тр.ч огущест вляется последовательно с помощью блоков 7 по мере установки в каждом из них RS-триггера 9 в состояние 1 (фиг. 2 т). Установка в состояние I RS-триггера 9 происходит в момент отсутствия переноса 1 в перезаписываемых им разрядах. Этот момент определяется на элементе 8 по состоянию К-го разряда двоичного счетчика 3, предшествующего разрядам. При этом используют тот факт, чт переход в состояние 1 Кто разряда счетчика 3 (так же как и любого) не приводит к переносу 1 в последующих разрядах, в то время как его переход в О может приводить к переносу 1. Поэтому элемент 8 осуществляет установку в 1 RS-тригге ра 9 либо в момент возникновения си нала перезаписи с предьедущего блока 7, если К-ый разряд находится в |, либо по переходу К-го разряда в I. И в том и в другом случае перенос 1 в последующих за К-ым разрядом перезаписываемых разрядах счетчика 3 закончится, если выбранное количество триггеров в любо рассматриваемой группе удовлетворяет условию: tn . Т.2, (1) где tj, - время переноса ь - задержка, создаваемая на одном триггере счетчика 3; Е - количество триггеров в гру пе; Т - период тактовой частоты; К - предшествующий перезаписыв емым разряд. Как видно из приведенного выражения в предлагаемом преобразователе требования к величине допустимой задержки, создаваемой на триггерах счетчика в каждой следующей группе, уменьшается. Следовательно, количество триггеров в каждой последующей группе может увеличиваться. По этой причине в данном преобразователе число блоков перезаписи, которое соответствует числу групп при большом количестве разрядов счетчика 3 существенно меньше, чем в известном. Из вьфажения I также следует, что ограничение на точность измерения Т может быть снято путем уменьшения количества разрядов f в группе. Для ;этого при заданном количестве разрядов n счетчика 3 должно быть незначительно увеличено число групп т. Таким образом, в предлагаемом преобразователе ограничение на точность измерения, накладываемое разрядностью счетчика 3, может быть прак тически снято схемотехническим путем и при меньшем числе элементов в цепи перезаписи. При этом достигаемая точность практически определяется быстродействием элементной базы. При расширении диапазона измерения при заданной точности точное BW полнение задержек затруднительно. В предлагаемом преобразователе набегающая задержка в двоичиом счетчике может быть легко устранена путем вьгделения необходимого количества групп соответствующим введением блоком перезаписи.

« J JOrLrLrLTLn

LrLTLTLrL

tn

в.

.П 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Многостоповый преобразователь временных интервалов в цифровой код | 1982 |

|

SU1061601A1 |

| Многостоповый преобразователь время - код | 1990 |

|

SU1739363A1 |

| Многостоповый преобразователь временных интервалов в цифровой код | 1987 |

|

SU1483636A1 |

| Устройство для регистрации движущихся транспортных средств | 1983 |

|

SU1129634A1 |

| Устройство с динамическим выбором маршрутов передачи данных | 1987 |

|

SU1587529A1 |

| Измеритель временных интервалов | 1985 |

|

SU1307444A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Многостоповый преобразователь временных интервалов в цифровой код | 1980 |

|

SU938401A1 |

| Многостоповый преобразователь временных интервалов в цифровой код | 1987 |

|

SU1468251A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

МНОГОСТОПОВЬЙ ПРЕОБРАЗОВАТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ В ЦИФРОВОЙ КОД, содержащий генератор тактовых импульсов, выход которого соединен с первыми входами формирователя тай- мерной серии и формирователя сигнала перезаписи, вторые входы которых подключены соответственно к тинам старт- и стоп-импульсов, выход формирователя таймерной серии подключен к счетному входу двоичного счетчика, выходы разрядов которого подключены к соответствующим D-входам буферного регистра, выход формирователя сигнала, перезаписи соединен с входом таймера, отличающийся тем, что, с целью повьшения точности измерения путем уменьшения его зависимости от числа разрядов двоичного счетчика, в него введены т-1 блоков перезаписи, а С-входы буферного регистра объединены в m групп, причем выход первого разряда двоичного счетчика соединен с первым входом первого блока перезаписи, выход формирователя сигнала перезаписи подключен к С-входам первой группы триггеров, буферного регистра и второму входу первого блока перезаписи. С- входы i-ой группы триггеров буферного регистра соединены с выходом i-ro блока перезаписи и первым входом (i+l)-ro блока перезаписи, второй вход i-ro блока перезаписи соi единен с выходом i-ro разряда двоичсл ного счетчика R-входы которого соединены с шиной конца измерения и третьим входом формирователя таймер - ной серии, R-входы всех блоков перезаписи объединены и подключены к .выходу таймера. 2. Преобразователь по п. 1, о тличающийся тем, что блок со перезаписи содержит злемент И и RSо триггер, выход которого является вы:о :л ходом блока, R-вход - R-входом блока, а S-вход соединен с выходом элеfS мента И, первый и второй входы которого являются соответственно первым и вторым входами блока.

Стоп д П

ю

В 1 гр. вых. е

. щ

t макс

Та и 1 ер 3

фаг.1

Г

Л

| ПРЕОБРАЗОВАТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ В ДВОИЧНЫЙ КОД | 0 |

|

SU354567A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Многостоповый преобразователь временных интервалов в цифровой код | 1982 |

|

SU1061601A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-11-07—Публикация

1983-04-04—Подача