Изобретение относится к измерительной технике и может быть использовано для измерения временных интервалов ,

Цель изобретения - повышение точности и быстродействия преобразований.

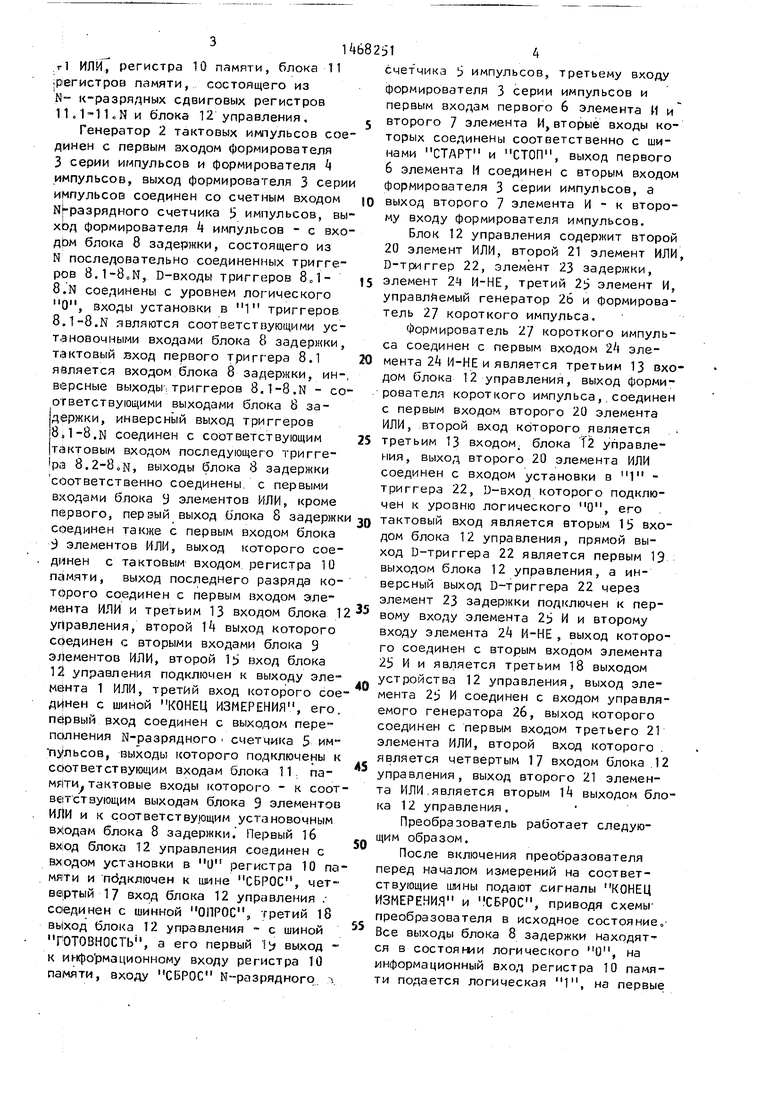

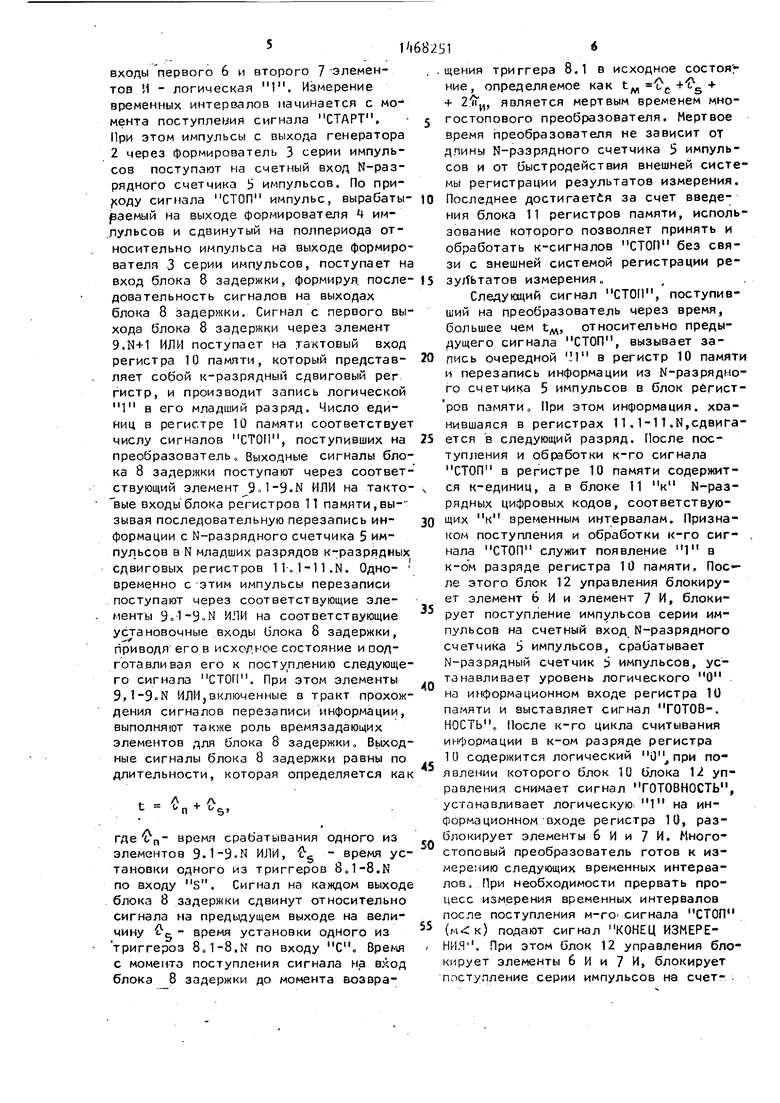

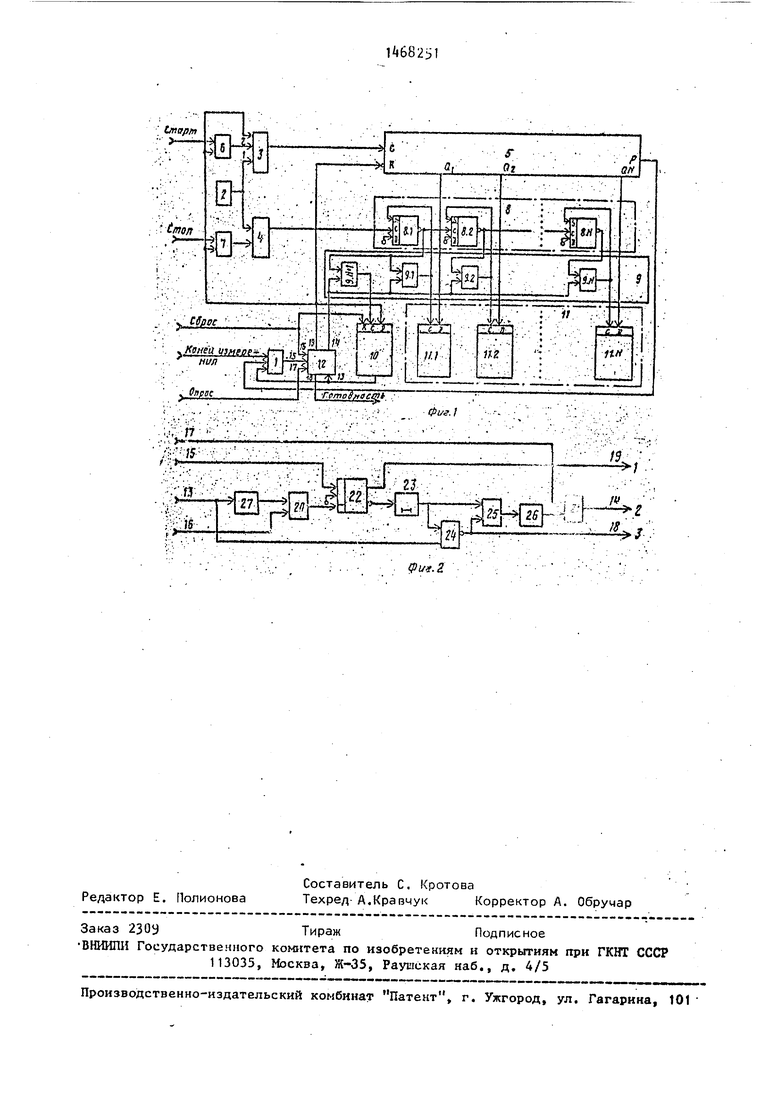

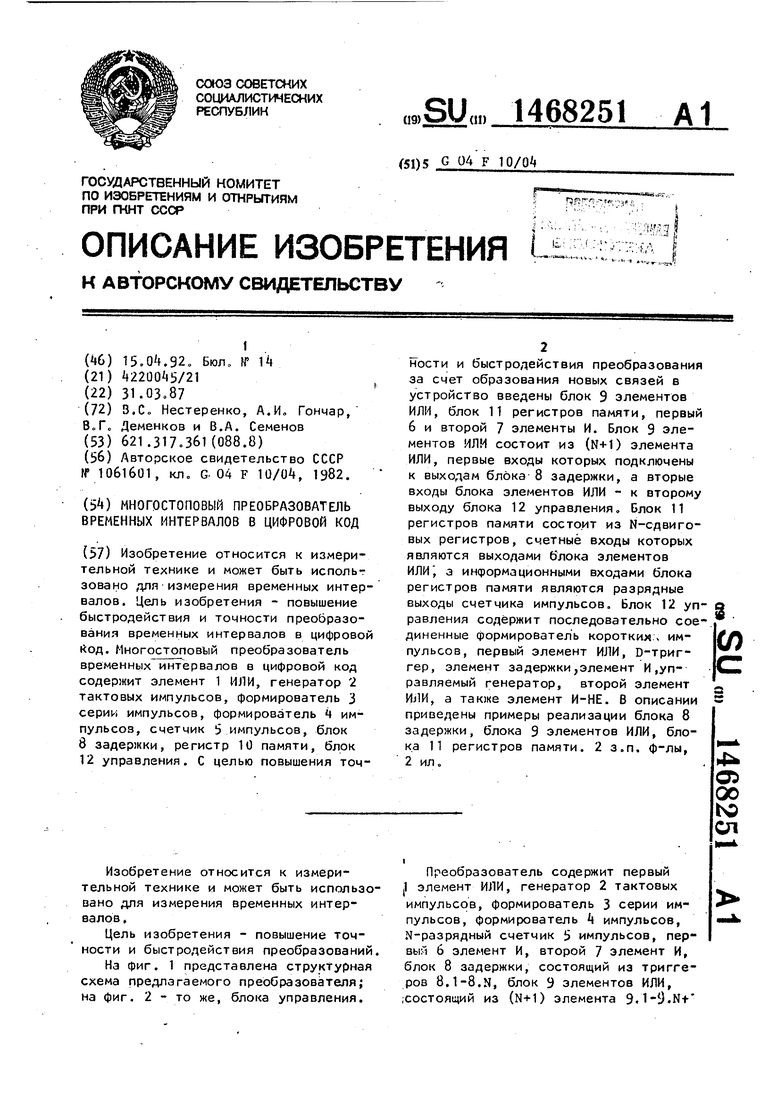

На фиг. 1 представлена структурная схема предлагаемого преобразователя; на фиг. 2 - то же, блока управления.

преобразователь содержит первый j1 элемент ИЛИ, генератор 2 тактовых импульсов, формирователь 3 серии импульсов, формирователь k импульсов, N-разрядный счетчик 5 импульсов, первый 6 элемент И, второй 7 элемент И, блок 8 задержки, состоящий из триггеров 8.1-8.N, блок 9 элементов ИЛИ, ;состоя1ций из (N+I) элемента 9.19.Nt

.r1 или, регистра .р егистроЕ памяти,

10

10 памяти, блока 11

состоящего из

N- к-разрядных сдвиговых регистров 11.1-11oN и блока 12 управления,

Генератор 2 тактовых импульсов соединен с первым входом формирователя 3 серии импульсов и формирователя импульсов, выход формирователя 3 серии импульсов соединен со счетным входом Nl-разрядного счетчика импульсов, вы- хЬд формирователя k импульсов - с вхо- дЬм блока 8 задержки, состоящего из N последовательно соединенных триггеров 8.1-8oN, D-входы триггезров 8„1- B.N соединены с уровнем логического О, входы установки в 1 триггеров 0.1-8.N являются соответствующими установочными входами блока 8 задержки, тактовый вход первого триггера 8.1 является входом блока 8 задержки, ин-, В1&рсные выходы-: триггеров 8.1-8.N - соответствующими выходами блока 8 задержки, инверсный выход триггеров 8«1-8,N соединен с соответствующим тактовым входом последующего тригге- Jpa 8.2-8.N, выходы блока 8 задержки соответственно соединены, с первыми входами блока у элементов ИЛИ, кроме первого, первый выход Ь лока 8 соединен также с первым входом блока элементов ИЛИ, выход которого соединен с тактовым входом регистра 10 памяти, выход последнего разряда которого соединен с первым входом эле- УПоавл и ° 1235 ,,,у ,„

м ° которого входу элемента 2k И-НЕ , выход которо- соединен с вторыми входами блока 9, и uiupu

элементов ИЛИ, второй 1 вход блока

счет чика ti импульсов, третьему входу формирователя 3 серии импульсов и первым входам первого 6 элемента И и второго 7 элемента И,вторые входы которых соединены соответственно с шинами СТАРТ и СТОП, выход первого 6 элемента II соединен с вторым входом формирователя 3 серии импульсов, а выход второго 7 элемента И - к второму ВХОДУ формирователя импульсов.

Блок 12 управления содержит второй 20 элемент ИЛИ, второй 21 элемент ИЛИ, D-триггер 22, элемент 23 задержки, 5 элемент 24 И-НЕ, третий 23 элемент И, управляемый генератор 26 и формирователь 27 короткого импульса.

Формирователь 27 короткого импульса соединен с первым входом 24 элемента 24 И-НЕ и является третьим 13 входом блока 12 управления, выход формирователя короткого импульса,. соединен с первым входом второго 20 элемента ИЛИ, второй вход которого является третьим 13 входом, блока Т2 управления, выход второго 20 элемента ИЛИ соединен с входом установки в 1 - триггера 22, D-БХОД которого подключен к уровню логического О, его за держки 30 тактовый вход является вторым 115 входом блока 12 управления, прямой выход D-триггера 22 является первым 1Э выходом блока 12 управления, а инверсный выход D-триггера 22 через элемент 23 задержки подключен к пер20

25

го соединен с вторым входом элемента 21р И и является третьим 18 выходом

19 v;r,r,, - 1ьяяе(ся третьим о выходом

тнта Гили т °Т ° 40 У--Р°йства 12 управления, выход эле- 1 ..:::..°fl . °-- гь и соединен с входом управля45

дИнен с шиной КОНЕЦ ИЗМЕРЕНИЯ, его. первый вход соединен с выходом переполнения N-разрядного . счетчика 5 им- пульсов, выходы которого подключены к соответствующим входам блока 11. памяти тактовые входы которого - к соответствующим выходам блока 9 элементов и к соответствующим установочным входам блока 8 задержки. Первый 1б вход блока 12 управления соединен с входом установки в О регистра 10 па- МЯ1ТИ и подключен к шине СБРОС, четвертый 17 вход блока 12 управления .- соединен с шинной ОПРОС, третий 18 выход блока 12 управления с шиной ГОТОВНОСТЬ, а его первый 1 выход - к инфо рмационному входу регистра 10 памяти, входу СБРОС М--разрядного. ,

55

соединен с входом управляемого генератора 26, выход которого соединен с первым входом третьего 21 элемента ИЛИ, второй вход которого является четвертым 17 входом блока.12 управления, выход второго 21 элемента ИЛИ.является вторым 14 выходом блока 12 управления.

Преобразователь работает следующим образом.

После включения преобразователя перед началом измерений на соответствующие шины подают .сигналы КОНЕЦ ИЗМЕРЕНИЯ и СБРОС, приводя схемы- преобразователя в исходное состояние. Все выходы блока 8 задержки находятся в состоянии логического О, на информационный вход регистра 10 памяти подается логическая 1, на первые

входу элемента 2k И-НЕ , выход которо- , и uiupu

го соединен с вторым входом элемента 21р И и является третьим 18 выходом

- 1ьяяе(ся третьим о выходом

У--Р°йства 12 управления, выход эле- гь и соединен с входом управляУ--Р°йства 12 управления, выход эле- гь и соединен с входом управля

соединен с входом управляемого генератора 26, выход которого соединен с первым входом третьего 21 элемента ИЛИ, второй вход которого является четвертым 17 входом блока.12 управления, выход второго 21 элемента ИЛИ.является вторым 14 выходом блока 12 управления.

Преобразователь работает следующим образом.

После включения преобразователя перед началом измерений на соответствующие шины подают .сигналы КОНЕЦ ИЗМЕРЕНИЯ и СБРОС, приводя схемы- преобразователя в исходное состояние. Все выходы блока 8 задержки находятся в состоянии логического О, на информационный вход регистра 10 памяти подается логическая 1, на первые

входы первого 6 и второго 7 Элементов И - логическая 1. Измерение

+ Z. ifj,, является мер

временных интервалов начинается с момента поступления сигнала СТАРТ, 5 При этом импульсы с выхода генератора 2 через формирователь 3 серии импульсов поступают на счетный вход N-раз- рядного счетчика ij импульсов. По природу сигнала СТОП импульс, вырабаты- Ю |ваемый на выходе формирователя 4 импульсов и сдвинутый на полпериода относительно импульса на выходе формирователя 3 серии импульсов, поступает на вход блока 8 задержки, формируя, после- 15 зу;ТЬтатов измерения

гостопового преобра время преобразовател длины N-разрядного сов и от быстродейс мы регистрации резу Последнее достигает ния блока 11 регист зование которого по обработать к-сигнал зи с внешней систем

Следующий сигнал ший на преобразоват большее чем t, от дущего сигнала СТО пись очередной и перезапись информа го счетчика 5 импул

довательность сигналов на выходах блока 8 :задержки. Сигнал с первого выхода блока 8 задержки через элемент 9.N+1 ИЛИ поступает на тактовый вход регистра 10 памяти, который представляет собой к-разрядный сдвиговый per гистр, и производит запись логической 1 в его младший разряд. Число единиц в регистре 10 памяти соответствует числу сигналов СТОП, поступивших на преобразователь. Выходные сигналы блока 8 задержки поступают через соответствующий элемент .N ИЛИ на такто- вые входы блока регистров П памяти,вы- зывая последовательную перезапись информации с N-разрядного счетчика 5 им- пул.ьсов в N младших разрядов к-разрядных сдвиговых регистров 11ol-11.N, Одно- време.нно с этим импульсы перезаписи поступают через соответствующие элементы 9.1-ЭоЫ ИЛИ на соответствующие установочные входы блока 8 задержки, приводя его в исходное состояние и под- готавливая его к поступлению следующего сигнала СТОП. При этом элементы 9, ИЛИ,включенные в тракт прохождения сигналов перезаписи информации, выполняют также роль времязадаюцих элементов для блока 8 задержки о Вь1ход- ные сигналы блока 8 задержки равны по длительности, которая определяется как

+ 0.

где с пвремя срабатывания одного из

элементов 9. ИЛИ, г - время установки одного из триггеров 8J-B.N по входу S. Сигнал на каждом выходе блока 8 задержки сдвинут относительно сигнала на предыдущем выходе на величину - время установки одного из триггеров 8o1-8.N по входу С Время с момента поступления сигнала на вход блока 8 задержки до момента возвра8251

. щения триггера 8,1 в исходное состоя;- ние, определяемое как t

0,

м--с Z. ifj,, является мертвым временем мно5Ю15 зу;ТЬтатов измерения

гостопового преобразователя. Мертвое время преобразователя не зависит от длины N-разрядного счетчика 5 импульсов и от быстродействия внешней системы регистрации результатов измерения, Последнее достигается за счет введения блока 11 регистров памяти, использование которого позволяет принять и обработать к-сигналов СТОП без связи с внешней системой регистрации резу;ТЬтатов измерения

Следующий сигнал СТОП, поступивший на преобразователь через время, большее чем t, относительно предыдущего сигнала СТОП, вызывает запись очередной в регистр 10 памяти и перезапись информации из N-разрядного счетчика 5 импульсов в блок рёгист ров памяти, 11ри этом информация, хранившаяся в регистрах 11,1-11,N,сдвигается в следующий разряд. После поступления и обработки к-го сигнала СТОП в регистре 10 памяти содержится к-единиц, а в блоке 11 к N-раз- рядных цифровых кодов, соответствующих к временным интервалам. Признаком поступления и обработки к-го сиг- , нала СТОП служит появление 1 в к-ом разряде регистра 10 памяти. После этого блок 12 управления блокирует элемент 6 И и элемент 7 И, блокирует поступление импульсов серии импульсов на счетный вход N-разрядного счетчика 5 импульсов, срабатывает N-разрядный счетчик 5 импульсов, устанавливает уровень логического О . на информационном входе регистра 10 памяти и выставляет сигнал ГОТОВ-. НОСТЬ, После к-го цикла считывания информации в к-ом разряде регистра 1Q содержится логический по явлении которого блок 10 блока 12 управления снимает сигнал ГОТОВНОСТЬ, устанавливает логическую; 1 на информационном входе регистра 10, разблокирует элементы 6 И и 7 И, Много- стоповый преобразователь готов к измерению следующих временных интервалов. При необходимости прервать процесс измерения временных интервалов после поступления м-го сигнала СТОП () подают сигнал КОНЕЦ ИЗМЕРЕ- НИЯ . При этом блок 12 управления блокирует элементы 6 И и 7 И, блокирует поступление серии импульсов на счет-:

ньий вход N-разрядного счетчика 5 импульсов, сбрасывает N-разрядный i счетчик 5 импульсов, устанавливает логический О на информационном входе регистра 10 памяти и производит сдвиг информации в регистре памяти и в блоке 11 регистров памяти. В момент появления 1 в к-ом разряде регистра Ю памяти сдвиг информации прекращается, блок управления устанавливает сигнал ГОТОВНОСТЬ, начинается пере- aainncb из блока 11 регистров памяти во внешнюю систему регистрации резуль- TajTOB измерения по сигналам ОПРОС. Порле м циклов перезаписи в к-ом райряде регистра 10 памяти появляется логический О, после чего сигнал ГО- TOjBHOCTb снимается, на информацион- ныр вход регистра 10 памяти подается логическая 1, элемент 6 И и эла-. меНт 7 И открываются,, ДеистЕзие сиг- Hajia р-переполнение N-разрядного счетIJL4I/D t. .«.«.п ...

ЧИ1

ся

аналогично действию сигнала КОНЕЦ ИЗ- МЕТЕНИЯ.

Следует отметить, что в блоке 8 за 1ержки использованы триггеры, одно- Гиг|ные с используемыми в N-разрядном счетчике 5 импульсов, при этом достигается равенство времени распрос т- . рамения сигнала по N-разрядному счетчику 5 импульсов с временем распрост- сигнала по блоку 8.задержки тем самым обеспечивается правильность пер)езаписи информации в блок регистров памяти.

;Г1рименение блока регистров 11 памяти |последсйгат.ельно-параллельного дей- ртвия, выполненного в виде N-к -разрядных сдвиговых регистров, обусловлено- получением гарантированного

MSDiT По л-

U682518

; блока задержки, элемент ИЛИ, регистр памяти, блок управления отличи1 ю щ и и с я тем, что, с целью повыше - J ния точности и быстродействия преобразования, в него введены блок элементов ИЛИ, блок регистров памяти и первый и второй элементы И, выходы которых соответственно подключены к вторым вхо- 10 дам формирователя импульсов и формирователя серии импульсов, третий вход последнего соединен с первыми входами первого и второго элементов И, с информационными входами регистра па- J5 мяти, с R-входом счетчика импульсов и с первым выходом блока управления, второй выход которого подключен к первым входам блока элементов ИЛИ, вторые входы которого подключены к отводам 20 блока задержки, выходы блока элементов ИЛИ подключены к счетным входам .регистра памяти и блока регистров памяти соответственно, информационные входы блока регистров памяти подключеЫ1ч1 L/ n Or ciMiti... ..

I..-- -.,,, - J.,f- - - |W J | lSjl( ( 1,Н ti

™ - ™

30

35

мертвого времени t,, не зависящего от длины N-разрядного счетчика 5 им- пуяьсов и от быстродействия внешней системы регистрации результатов изме- РСИМЯ

Формула изобретения

1. Миогостоповый преобразователь временных интервалов в цифровой код, содержащий генератор тактовых импульсов, выходы которого подключены к первым входам формирователя импульсов и формирователя серии импульсов, выход ко торого соединен со счетным входом счетчика импульсов, выход форми роэателя импульсов подключен к входу

сов, выход переполнения которого подключен к первому входу элемента ИЛИ, второй вход которого подключен к выходу регистра памяти и первому входу блока управления, второй вход которого подключен к выхрду элемента ИЛИ, третий вход блока управления соединен с R-входом регистра памяти и шиной СБРОС, третий вход элемента ИЛИ соединен с шиной КОНЕЦ ИЗМЕРЕНИЯ.

2, Преобразователь по п. 1 отличающийся тем, что блок уп- { авления содержит последовательно соединенные формирователь короткого им- пульса, первый элемент ИЛИ, D-триг- - гер, элемент задержки, третий элемент И, управляемый генератор, второй элемент ИЛИ и элемент И-НЕ, п р-вый вход которого соединен с выходом эле- 45 f ;,f . второй вход элемен- з та И-НЕ соединен с входом формирователя короткого импульса и является первым входом блока управления, второй вход первого элемента ИЛИ являет- ся третьим входом блока управления, « выход элемента И-НЕ соединен с вторым входом элемента И, при этом D-ВХОД подключен к шине УСТАНОВКА и , С-вход D-триггера является вторым входом блока управления, пря- -триггера является первым выходом блока управления, выход второго элемента ИЛИ является вторым выходом блока управления.

. tjnapm

Фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Многостоповый преобразователь время - код | 1990 |

|

SU1739363A1 |

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ - КОД | 1991 |

|

RU2027303C1 |

| УСТРОЙСТВО ДЛЯ ЗАДЕРЖКИ СИГНАЛОВ | 1992 |

|

RU2024186C1 |

| ЦИФРОВОЙ ДАЛЬНОМЕР | 1992 |

|

RU2069003C1 |

| Многостоповый преобразователь временных интервалов в цифровой код | 1982 |

|

SU1061601A1 |

| Коррелометр | 1989 |

|

SU1644159A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для считывания информации | 1989 |

|

SU1693617A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

| ИЗМЕРИТЕЛЬ СПЕКТРАЛЬНЫХ ПАРАМЕТРОВ РАДИОСИГНАЛОВ | 2005 |

|

RU2279098C1 |

Изобретение относится к измерительной технике и может быть испольт зовано для-измерения временных интервалов. Цель изобретения - повышение быстродействия и точности преобразования временных интервалов в цифровой йод. МНОГОСТОПОВЫЙ преобразователь временных интервалов в цифровой код содержит элемент 1 ИЛИ, генератор 2 тактовых импульсов, формирователь 3 серии импульсов, формирователь 4 импульсов, счетчик 5 импульсов, блок 8 задержки, регистр 10 памяти, блок 12 управления. С целью повышения точности и быстродействия преобразования за счет образования новых связей в устройство введены блок 9 элементов ИЛИ, блок 11 регистров памяти, первый 6 и второй 7 элементы И. Блок 9 элементов ИЛИ состоит из (N+1) элемента ИЛИ, первые входы которых подключены к выходам блока 8 задержки, а вторые входы блока элементов ИЛИ - к второму выходу блока 12 управления, Блок 11 регистров памяти состоит из Ы-сдвиго- вых регистров, счетные входы которых являются выходами блока элементов ИЛИ , э информационными входами блока регистров памяти являются разрядные выходы счетчика импульсов. Блок 12 управления содержит последовательно соединенные формирователь коротких ч импульсов, первый элемент ИЛИ, р-триг- гер, элемент задержки,элемент И,управляемый генератор, второй элемент ИJlИ, а также элемент И-НЕ. В описании приведены примеры реализации блока 8 задержки, блока 9 элементов ИЛИ, блока 11 регистров памяти. 2 з.п. ф-лы, 2 ил. г (Л GD 00 ГС сл

-Ji,-.

; :Л ,1V

,: is ,

/

| Многостоповый преобразователь временных интервалов в цифровой код | 1982 |

|

SU1061601A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-04-15—Публикация

1987-03-31—Подача