Изобретение относится к вычислительной технике и автоматике и может быть использовано для построения высоконадежных цифровых устройств.

Известно устройство для указания неисправности в дублированных дискретных автоматах, содержащее резервируемые блоки, схему сравнения, блок коммутации и логические схемы управления выходными сигналами, причем выходы резервируемых блоков соединены с входами схемы сравнения блока коммутации и логических схем управления, выход схемы сравнения соединен с входом блока коммутации, выходы блока коммутации соединен с входами логических схем управления 1.

Недостаток данного устройства состоит в том, что при независимой реализации выходных сигналов резервируемых блоков искажение одного выходного сигнала любого из блоков вызывает отключение всего блока. Устройство переходит в неработоспособное состояние при возникновении хртя бы по одному отказу в каждом из резервируемых блоков.

Известно т-акже устройство для предотвращения неправильного срабатывания логических cjjeM, содержащих два идентичных логических Ълока, эталонную схему, детектор несовпадения выходных сигналов логических схем, элементы И, ИЛИ, причем выходы логических схем соединены с входами элементов И и детектора, выход эталонной схемы соединен с входом детектора, выходы детектора соединены с входами элементов И, . выходы которых соединены с входами элемента ИЛИ 2.

Недостаток данного устройства состоит в том, что в случае независимой реализации выходных сигналов в каждой из логических схем оно переходит в неработоспособное состояние, когда при наличии хотя бы одного отказа в одной логической схеме возникает первый отказ в другой логической схеме.

Наиболее близким по технической сущности к предлагаемому является устройство с трехкратным мажоритарным резервированием - троированая мажоритарная структура (ТМС), состоящая из трех идентичных блоков и восстанавливающих органов, причем одноименные выходы резервируемых блоков соединены с входами соответствующего восстанавливающего органа 3.

Недостаток этого устройства состоит в том, что для исправления любых однократных отказов по каждой выходу при независимой реализации выходных функций требуется исходное оборудование.

Недостаток данной структуры состоит в том, что при независимой реализации выходных сигналов она не сохраняет работоспособность при произвольных одиночных отказах в каждом из резервируемых устройств, т. е. после отключения первого устройства любой отказ во второй устройстве приведет к отказу всей структуры, а при наличии отказа во втором устройстве любой отказ в первом устройстве приводит к отказу всей структуры.

Цель изобретения - повыщение надежности устройства для управления переключением резервных блоков.

Поставленная цель достигается тем,- что в устрой.ство для управления переключением резервных блоков, содержащее основной и резервный блоки встроенного контроля, коммутаторы, шину синхронизации, соединенную с синхровходами коммутатора, щину начальной установки, соединенную с входами начальной установки коммутатора,

введены блок контроля по модулю два, первый элемент И, элемент задержки, индикатор отказа устройства. Коммутатор выполнен из подблоков по числу выходов устройства, а каждый подблок коммутатора содержит индикаторы отказов основного и резервного блоков, два триггера, четыре элемента И, элемент ИЛИ и элемент сложения по модулю два, первый вход которого соединен с выходом основного блока, а второй вход - с выходом резервного блока, выходс первым входом второго элемента И и с первым входом третьего элемента И, а второй вход третьего элемента И соединен с инверсным выходом блока контроля по модулю два, прямой выход которого соединен с вторым входом второго элемента И, третьи входы второго и третьего элементов И соединены с щиной синхронизации, выход третьего элемента И соединен с первым входом первого триггера, второй вход которого соединен с щиной начальной установки в «1, первый выход первого триггера соединен с четвертым входом второго элемента И, а второй выход - с входом индикатора отказа резервного блока, выход второго элемента И соединен с первым входом первого триггера, второй вход которого соединен с

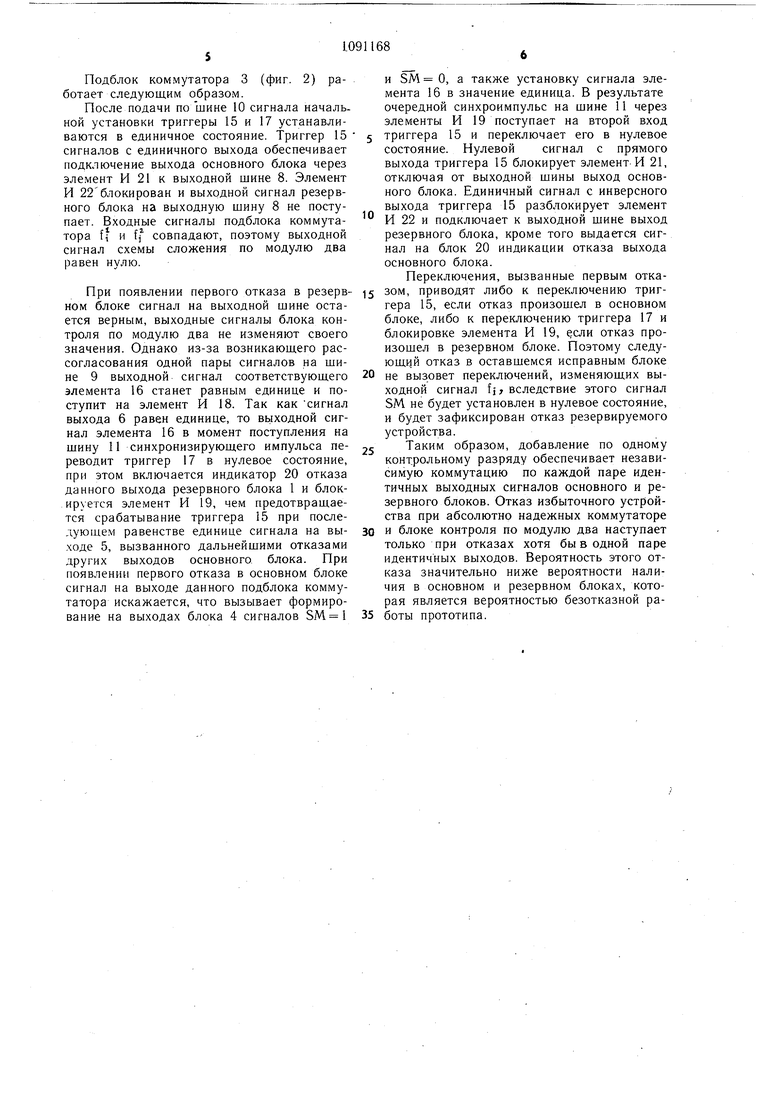

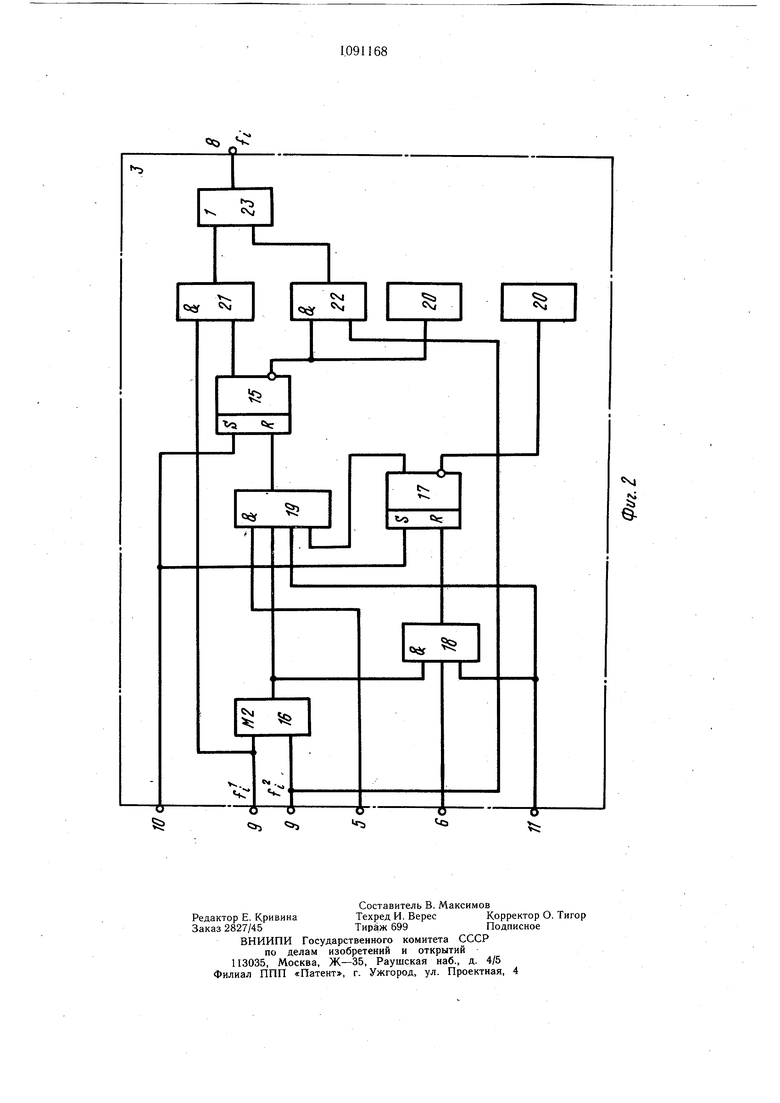

щиной начальной установки в «1, первый выход второго триггера соединен с первым входом четвертого элемента И, второй вход которого подсоединен к выходу основного блока, выход четвертого элемента И соединен с первым входом элемента ИЛИ, второй выход второго триггера соединен с индикатором отказа соответствующего выхода основного блока и с первым входом пятого элемента И, второй вход которого соединен с выходом резервного блока, выход пятого элемента И соединен с вторым входом элемента ИЛИ, ВЫХО.Д которого соединен с соответствующей выходной щиной устройства, щина синхронизации соединена с входом элемента задержки, выход которого соединен с вторым входом первого элемента И, выход которого соединен с входом индикатора отказа устройства, а второй вход - с прямым выходом блока контроля по модулю два. На фиг. 1 приведена блок-схема устройства; на фиг. 2 - подблок коммутатора, функциональная схема. Устройство, (фиг. 1) содержит основной и резервный блоки 1, блоки 2 встроенного контроля, коммутатор 3 (состоящий из подблоков 3i З.П коммутации), блок 4 контроля по модулю два с прямым 5 и инверсным 6 выходами, входные 7 и выходные 8 шины устройства, выходные шины 9 основного и резервного блоков и блоков 2 встроенного контроля, шину 10 начальной установки, шину 11 синхронизации,первый элемент И 12, элемент 13 задержки, индикатор 14 отказа устройства.. Каждый подблок коммутатора 3 (фиг. 2) содержит первый триггер 15, элемент 16 сложения по модулю два, второй триггер 17, второй 18 и третий 19 элементы И, индикаторы 20 отказов основного и резервного блоков, четвертый элемент И 21, пятый элемент И 22 и элемент ИЛИ 23. Выходная функция блока 2 встроенного контроля удовлетворяет условию им fl. + f, +... + fnЕсли блоки 1 являются автоматами без памяти, то функция Г определяется путем указанного выше преобразования над функциями fi, f, ..., fs- Если же блоки 1 являются синхронными автоматами с памятью, то задание на построение блоков 2 сводится к нахождению такого автомата с памятью, выходной сигнал которого был бы равен сумме по модулю два выходных Сигналов блока 1 на всем множестве рабочих входных наборов и множестве допустимых состояний схем, памяти блока 1. При наличии цепей начальной установки такой автомат всегда можно синхронизировать с автоматом блока 1. , На прямой выходе 5 блока 4 контроля .по модулю два реализуется функция SM fi + i 2+- + . .§ йа инверсном выходе 6 - функция SM инверсная функ1цил SM. Предлагаемое устройство строится на на основе известного метода обработки данных, представленных в виде .двух идентичных слоев, каждое из которых имеет информационные разряды и один контрольный разряд контрольной суммы по модулю два, модифицированного с учетом особенности функционирования ненадежных дискретных устройств. Поток отказов является простейшим и, следовательно, обладает свойством ординарности. Допустим, за интервал времени t (при At/t-O, где t - интервал времени, на котором определяется надежность) с вероятностью единицы появляются входные наборы, на которых проявляются все одиночные отказы. Вследствие ординарности потока отказов за малое время д t наиболее вероятным является появление одиночных отказов, что дает возможность обнаруживать и обрабатывать их последовательно. Устройство работает следующим образом. В начальный момент времени основной и резервный блоки 1 являются исправными, по шине 10 первые и вторые триггеры рсех подблоков коммутатора 3 устанавливаются в единичное состояние. В результате начальной установки к выходным шинам 8 подключаются выходы основного блока, так как в исходном состоянии блоки 1 исправны и функций к-цудовлетворяет условию (1), то сигнал SM 0, а сигнал SM 1. Работа устройства синхронизирована, входные сигналы на шинах 7 могут изменяться только в фиксированные моменты времени ti, в моменты времени (ti + 1з). на шину 11 коммутатора поступает синхрониЗирующий сигнал, который синхронизирует переключение триггеров коммутатора. Интервал t3 выбирается достаточным для завершения переходных процессов в блоках 1 и установки новых значений сигналов на выходах 5 и 6 блока 4, что защищает коммутатор от ложных срабатываний. Отказ в основном блоке 1 приводит к искажению одного из выходных сигналов fj, блок 4 контроля по модулю два выявляет ошибку и формирует сигналы SM 1 и SM 0. При поступлении очередного синхроимпульса коммутатор отключает от вь ходной шины 8 отказавший выход основного блока 1 и подключает идентичный выход резервного блока 1. После произведенного пepeключejiия сигнал SM станет равен нулю, а сигнал SM - единице. Если первоначально возникает отказ в резервном блоке 1, вызвавший искажение вы ходного сигнала fi , то сигналы SM и SM не изм-еНяется, так как данный выход резервного блока не подсоединен к выходным шинам. Подблок коммутатора, соединенный с i-ми выходами, основного и, резервного блоков, выявляет рассогласование сигналов f/ и fj блокирует возможное подключение i-ro выхода, резервного блока 1 к выходной шине в случае последующего отказа i-ro выхода основного блока 1. В случае отказа обоих одноименных выходов основного и резервного блоков сигнал SM устанавливается в единицу и не сбрасывается переключением соответствующего подблока коммутатора. Поэтому при появлении на выходе элемента 13 задержанного сигнала синхроимпульса сигнал SM через элемент И 12 включает индикатор 14. Тем самым обнаруживается любой двукратный отказ, приводящий к искажению одноименных выходных сигналов основного и резервного блоков.

Подблок коммутатора 3 (фиг. 2) работает следующим образом.

После подачи по шине 10 сигнала начальной установки триггеры 15 и 17 устанавливаются в единичное состояние. Триггер 15 сигналов с единичного выхода обеспечивает подключение выхода основного блока через элемент И 21 к выходной шине 8. Элемент И 22блокирован и выходной сигнал резервного блока на выходную шину 8 не поступает. Входные сигналы подблока коммутатора fi и ff совпадают, поэтому выходной сигнал схемы сложения по модулю два равен нулю.

При появлении первого отказа в резервном блоке сигнал на выходной шине остается верным, выходные сигналы блока контроля по модулю два не изменяют своего значения. Однако из-за возникаюш,его рассогласования одной пары сигналов на шине 9 выходной сигнал соответствующего элемента 16 станет равным единице и поступит на элемент И 18. Так как сигнал выхода 6 равен единице, то выходной сигнал элемента 16 в момент поступления на шину 11 синхронизирующего импульса переводит триггер 17 в нулевое состояние, при этом включается индикатор 20 отказа данного выхода резервного блока 1 и блокируется элемент И 19, чем предотвращается срабатывание триггера 15 при последующем равенстве единице сигнала на выходе 5, вызванного дальнейщими отказами других выходов основного блока. При появлении первого отказа в основном блоке сигнал на выходе данного подблока коммутатора искажается, что вызывает формирование на выходах блока 4 сигналов SM 1

и SM О, а также установку сигнала элемента 16 в значение единица. В результате очередной синхроимпульс на шине 11 через элементы И 19 поступает на второй вход 5 триггера 15 и переключает его в нулевое состояние. Нулевой сигнал с прямого выхода триггера 15 блокирует элемент-И 21, отключая от выходной шины выход основного блока. Единичный сигнал с инверсного выхода триггера 15 разблокирует элемент И 22 и подключает к выходной щине выход резервного блока, кроме того выдается сигнал на блок 20 индикации отказа выхода основного блока.

Переключения, вызванные первым отка15 зом, приводят либо к переключению триггера 15, если отказ произошел в основном блоке, либо к переключению триггера 17 и блокировке элемента И 19, если отказ произошел в резервном блоке. Поэтому следующцй отказ в оставшемся исправным блоке

20 не вызовет переключений, изменяющих выходной сигнал fjj вследствие этого сигнал SM не будет установлен в нулевое состояние, и будет зафиксирован отказ резервируемого устройства.

25 Таким образом, добавление по одному контрольному разряду обеспечивает независимую коммутацию по каждой паре идентичных выходных сигналов основного и резервного блоков. Отказ избыточного устройства при абсолютно надежных коммутаторе

30 и блоке контроля по модулю два наступает только при отказах хотя бы в одной паре идентичных выходов. Вероятность этого отказа значительно ниже вероятности наличия в основном и резервном блоках, которая является вероятностью безотказной ра35 боты прототипа.

Фиг.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления переключением резервных блоков | 1989 |

|

SU1635186A1 |

| Устройство для управления переключением резервных блоков | 1984 |

|

SU1190557A1 |

| ТРЕХЭЛЕМЕНТНОЕ МАЖОРИТАРНОЕ УСТРОЙСТВО РЕЗЕРВИРОВАНИЯ | 2007 |

|

RU2347264C2 |

| СПОСОБ УПРАВЛЕНИЯ ДУБЛИРОВАННОЙ СИСТЕМОЙ С ЗАДЕРЖКОЙ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1999 |

|

RU2147162C1 |

| Резервированное устройство | 1980 |

|

SU928685A1 |

| Многоканальное устройство для резервирования замещением | 1980 |

|

SU920731A1 |

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ (3 ВАРИАНТА) | 2014 |

|

RU2580791C2 |

| Устройство для контроля и коммутации резервных блоков | 1984 |

|

SU1252782A1 |

| УСТРОЙСТВО для СИГНАЛИЗАЦИИ ОТКАЗОВ РАДИОЭЛЕКТРОННОГО ОБОРУДОВАНИЯ | 1969 |

|

SU247627A1 |

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПЕР ВКЛЮЧЕН И E/VI РЕЗЕРВНЫХ БЛОКОВ, содержащее основной и резервный блоки, блоки встроенного контроля, коммутаторы, шину синхронизации, соединенную с синхровходами коммутатора, шину начальной установки, соединенную с входами начальной установки коммутатора, отличающееся тем,- что, с целью повышения его надежности, в него введены блок контроля по модулю два, первый элемент И, элемент задержки, индикатор отказа устройства. Коммутатор выполнен из подблоков по числу выходов устройства, а каждый подблок коммутатора содержит индикаторы отказов основного и резервного блоков, два триггера, четыре элемента И, элемент ИЛИ и элемент сложения по модулю два, первый вход которого соединен с выходом основного блока, а второй вход - с выходом резервного блока, выход - с первым входом второго элемента И и с первым входом третьего элемента И, а второй вход третьего элемента И соединен с инверсИым выходом блока контроля по модулю два, прямой выход которого содинен с вторым входом второго элемента И, третьи входы второго и третьего элементов И соединены с шиной синхронизации, выход третьего элемента И соединен с первым входом первого триггера, второй вход которого соединен с шиной начальной установки в «1, первый выход первого триггера соединен с четвертым входом второго элемента И, а второй выход - с входом индикатора отказа резервного блока, выход второго элемента И соединен с первым входом первого триггера, второй вход которого содинен с шиной начальной установки в «I, первый выход второго триггера соединен с первым входом четвертого элемента И, второй вход-кото(Л рого подсоединен к выходу основного блока, выход четвертого элемента И соединен с первым входом элемента ИЛИ, второй выход второго триггера соединен с индикатором отказа соответствующего выхода основного блока и с первым входом пятого элемента И, второй вход которого соединен с выходом резервного блока, выход пятого элемента И соединен с вторым входом элесо мента ИЛИ, выход которого соединен с соответствующей выходной шиной устройства, шина синхронизации соединена с входом элемента задержки, выход которого соео: динен с, вторым входом первого элемента И, 00 выход которого соединен с входом индикатора отказа устройства, а второй вход-с прямым выходом блока контроля по модулю два.

«N4

Авторы

Даты

1984-05-07—Публикация

1982-04-06—Подача