соединен с установкой в нуль первого регистра адреса, выход второго регистра адреса соединен с входом третьего дешифратора адреса, выход которого соединен с адресным входом блока памяти копий, отличающееся тем, что, с целью повышения производительности, в устройство взедены второй счетчик адреса, триггер, третий и четвертый блоки элементов И, элемент ИЛИ, шестой и седьмой элементы И и одновибратор, причем информационный вход устройства соединен с единичным входом : триггера снятия копий, единичный выход которого соединен с первым входом пятого элемента И и управляющим входом третьего блока элементов rf, выход которого соединен с информационным входом блока памяти копий, выход окончания выдачи копий блока памяти копий соединен с. вторым выходом устройства и нулевым входом триггера управления, единичный выход которого соединен с первым входом шестого элемента И, выход генератора тактовых импульсов соединен с вторым входом шестого элемента И, выход которого соединен с первым входом элемента И, выход которого соединен с первы1и входом элемента ИЛИ, выход элемента ИЛИ соединен с входом разрешения записи блокс памяти копий, вход кодов логических условий устройства соединен с единичным входом триггера вы,цачи копий и первым входом четвертого блока элементов И, выход которого соединен с информационным входом второго регистра адреса нулевой выход триггера снятия копий соединен с перВЕлм входом седьмого элемента И, выход которого через одновибратор соединен с установочным входом второго счетчика адреса, выход второго счетчика адреса соединен с вторым входом четвертого блока элементов И, выход считывания микрокоманды второго блока памяти соединен с вторым входом элемента ИЛИ, вычитающим входом счетчика микрокоманд и с вторым входом пятого элемента И, выход которого соединен с счетным входом второго счетчика адреса, единичный выход триггера выдачи копий соединен с входом записи второго рег гистра адреса, синхронизирующим входом третьего дешифратора адреса и вторым входом седьмого элемента И, выход окончания микропрограммы второго блока памяти соединен С пepвы;vI выходом устройства, с единичньЕ- входом триггера управления и нулевым входом триггера снятия копий, выход окончгзлия выдачи копий блока памяти копий ссединен с нулевым вХ|Рдом триггера выдачи копий и устаЕЮвочным входом второго регистра адреса, информационный аыход блока хранения копий соединен с вторым выходом устройства .

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1108448A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1115054A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1091158A1 |

| Мультимикропрограммная управляющая система | 1984 |

|

SU1241244A1 |

| Нанопрограммное устройство управления | 1983 |

|

SU1136160A1 |

| Мультимикропрограммная управляющая система с контролем и восстановлением | 1988 |

|

SU1704147A1 |

| Устройство микропрограммного управления | 1982 |

|

SU1086431A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее первый и второй блоки памяти, блок памяти копий, два -регистра адреса, регистр логических условий, буферный регистр, счетчик микрокоманд, первый с четчик адреса, первый, второй и третий дешифраторы адреса, первый и второй блоки ь. элементов И, триггер снятия копий, триггер выдачи копий, генератор тактовых импульсов, пять элементов И, два элемента задержки и элемент НЕ, причем информационный вход устройства соединен с первым информационным входом первого регистра адреса, выход первого регистра адреса соединен с входом первого дешифратора адреса, выход которого соединен с входом первого блока памяти, первый адресный выход первого блока памяти соединен с первым информационным входом буферного регистра, выход кода проверяемых логических условий первого блока памяти соединен с информационным входом регистра логических условий, выход которого соединен с .первым входом первого блока элементов И, выход первого блока элементов И соединен с вторым информационным входом буферного регистра, выход Которого соединен с первым входом второго блока г элементов И, выход которого соединен с вторым информационным входом первого регистра адреса, второй адресный выход первого блока памяти соединен с информационным входом первого счетчика адреса, выход которого соединен с входом второго дешифратора адреса, выход дешифратора адреса соединен с входом второго блока памяти, информационный выход которого соединен с первым информационным выходом устройства, вход кодов логических условий устройства соединен с вторым входом первого блока элементов И, выход кода длины операционной о последовательности первого блока па- S мяти соединен с информационным вхо(Л дом счетчика микрокоманд, нулевые вы ходы которого соединены с входами с первого элемента И, выход первого элемента И соединен с первыми входами второго и третьего элементов И и S входом элемента НЕ, выход генератора тактовых импульсов соединен с первым входом четвертого элемента И и входом первого элемента задержки, выход ( которого соединен с вторым входом третьего элемента И и входом второго ГС СП элемента задержки, выход которого соединен с вторым входом второго о ел элемента И, выход второго элемента И соединен с вторым входом второго блока элементов И, выход элемента НЕ соединен с вторым входом четвертого элемента И, выход которого соединен с синхронизирующим входом второго дешифратора адреса, выход считывания микрокоманды второго блока памяти соединен с счетным входом первого счетчика адреса, выход третьего элемента И соединен с входами установки в нуль первого счетчика адреса, регистра логических условий, буферного регистра и синхронизирующим входом первого дешифратора адреса, управляющий вход первого блока памяти

Изобретение относится к автомати не и вычислительной технике и может быть использовано в качестве устройства микропрограммного управления при построении вычислителг ныгс машин и систем, а также управляющих устройств в автоматиэированнЕлх системах управления технологическими процессами.

Известны микропрограммные устройства управления, содержащие два блока памяти, регистры логических условий, счетчики, дешифраторы, регистры логические элементы И, НЕ, элементы задержки и генератор тактовых импульсов .

Недостатками указанных устройств являются ограниченные функциональные возможности и низкая производительность, которые обусловлены невозможностью управления дв,умя параллельно протекающими аналогичными процессами, один из которых по отношению к другому может быть сдвинут во времени.

Наиболее близким к предлагаемому по технической сущности и достигаемому положительному эффекту является микропрограгдмное устройство, содер5 жащее первый и второй блоки памяти, блок хранения копий, два регистра адреса, регистр логических условий, буферный регистр, счетчик микрокоманд, первый счетчик адреса, первый,

, второй и третий дешифраторы адреса,

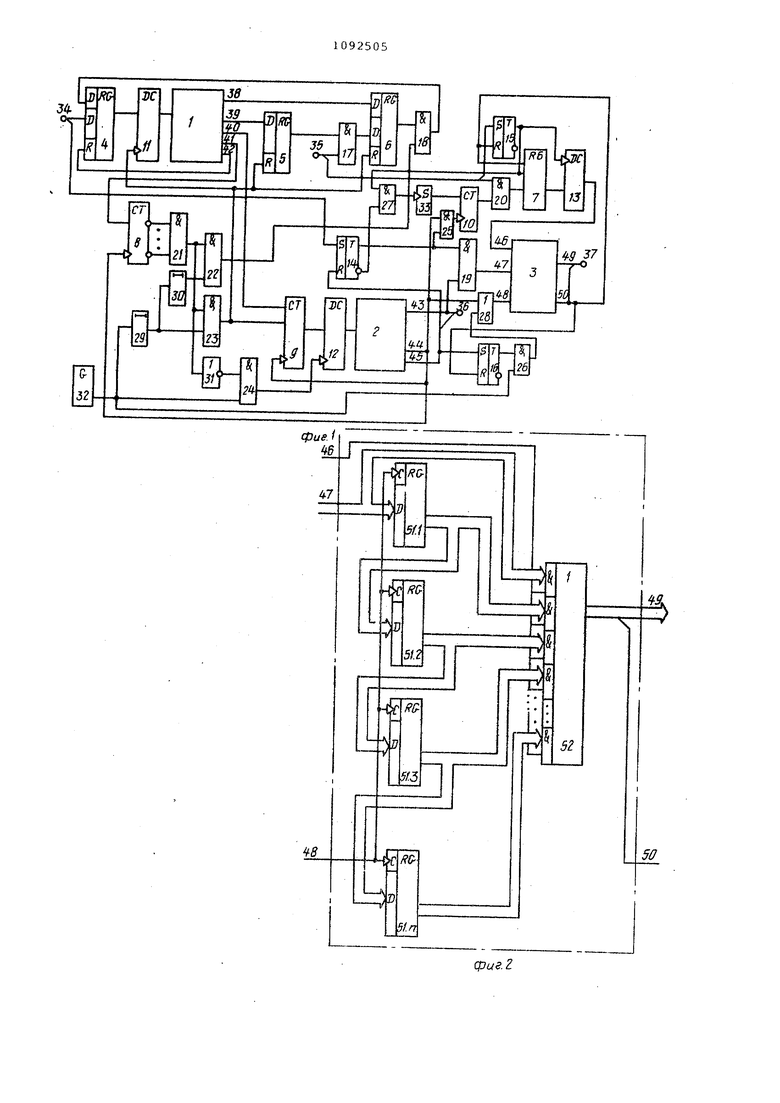

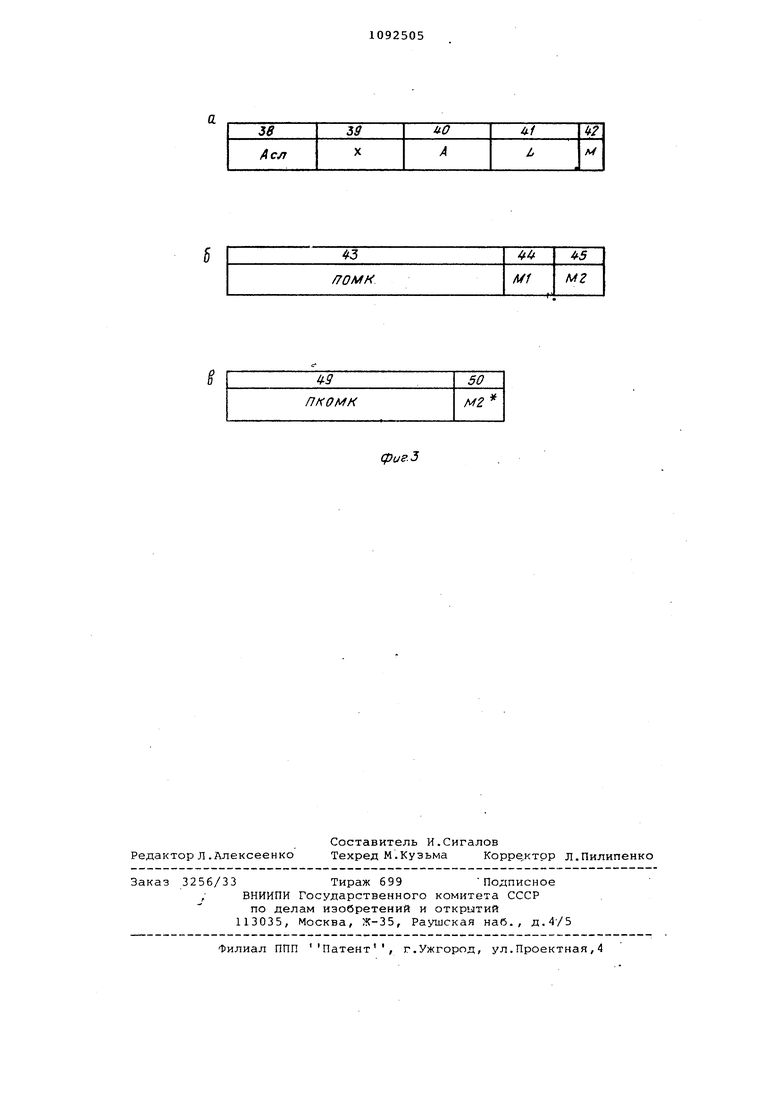

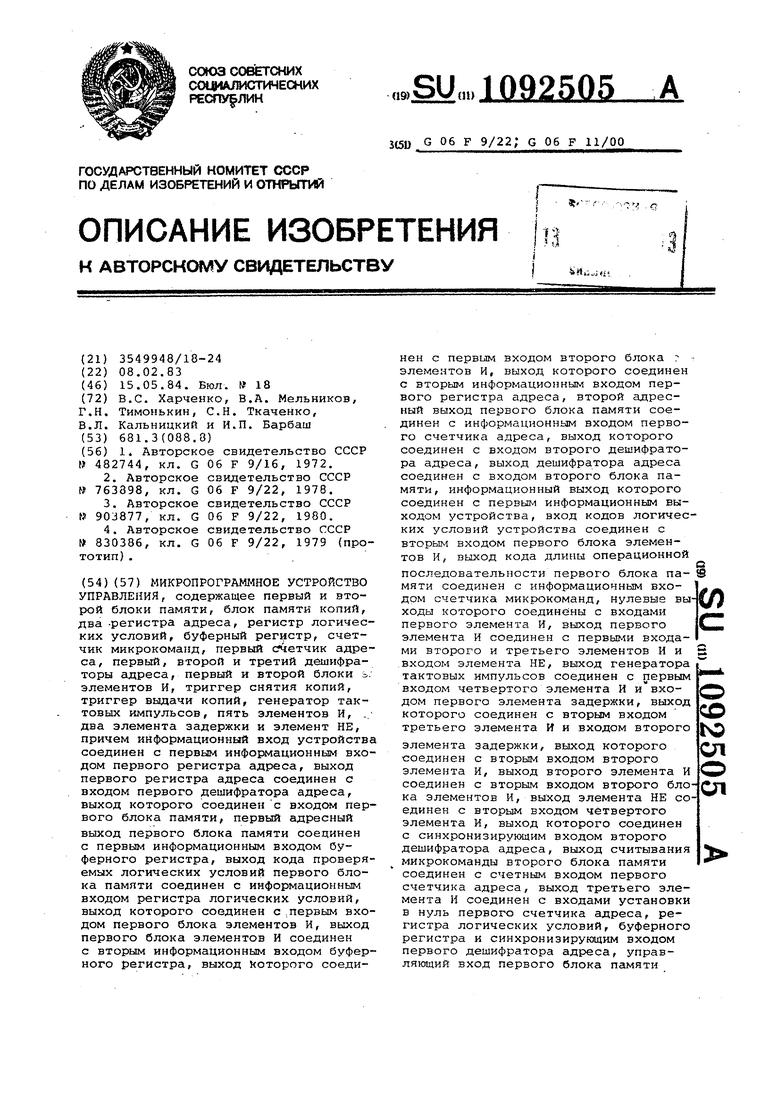

первый и второй блоки злемеЕ1тов И, триггер снятия копии, триггер выдачи копии, генератор тактовых импульсов, пять элементов И, элемент НЕ,. причем первый вход устройства соеди5 нан с nepaiiM информационным входом первого регистра адреса, выход первого регистра адреса соединен с входом первого дешифратора адреса, выход которого соединен с входом перво0 го блока памяти, первый адресный вход первого блока памяти соединен с первым инфopмaциoнны входом буферного регистра, выход кода проверяемых логических условий первого блока памяти соединен с информационным входом регистра логических условий, выход которого соединен с первыми входами первого блока элементов И, выход первого блока элементов И соединен с вторым информационным вхот дом буферного регистра, выход которого соединен с первыми входами вто рого блока элементов И, выход которого соединен с вторым информационным входом первого регистра адреса второй адресный выход первого блока памяти соединен с информационным входом первого счетчика адреса, выход которого соединен с входом второго дешифратора адреса, выход дешифратора адреса соединен с входом второго блока памяти, информационный выход которого соединен с первым выходом устройства, второй вход устройства соединен с вторыми входами первого блока элементов И, выход кода длины операционной последовательности первого блока памяти соединен с ийформационным входом счетчика микрокоманд, нулевые выходы которого соединены ,с входами пер вого элемента И, выход первого элемента И соединен с пepвьDvIи входами йторого и третьего элементов И и входом элемента КЕ, выход генератор тактовых импульсов соединен с первы входом четвертого элемента И и входом первого элемента задержки, выход которого соединен с вторым входом третьего элемента И и входом второго элемента задержки, выход которого соединен с вторым входом второго элемента И; выход второго элемента И соединен с вторыми входами второго блока элементов И, вы|ход элемента НЕ соединен с вторым 1ВХОДОМ четвертого элемента И, выход iKOTOporo соединен с синхронизирую щим входом второго дешифратора адреса, первый управляющий выход второго блока памяти соединен со счетНЕлм входом первого счетчика адреса, выход третьего элемента И соединен с входами установки в нуль первого счетчика адреса, регистра логически условий, буферного регистра и синхр ниэирующим входом первого дешифрато ра адреса, управляющий выход первог блока памяти соединен с входом уста новки в нуль первого регистра адрес выход второго регистра адреса соеди нен с входом третьего дешифратора а реса, выход которого соединен с пер вым управляющим входом блока хранения копий 4 . Недостатком этого устройства явл ется низкая производительность, кот рая обусловлена возможностью управл НИН только одним процессом. На прак тике возможны случаи, когда необходимо организовать контроль и управление двумя (или несколькими) идентичными процессами, начало которых азнесено во времени. Например, упавлять процессом передачи заранее формированного массива кодов для нескольких абонентов при условии, что готовность второго и .последующих абонентов к приему информации будет остигнута до момента окончания ее передачи первому абоненту. В такой ситуации известное устройство может реализовать указанные процессы только в существенно последовательном режиме. Таким образом, это устройство имеет низкую производительность, 067-условленную большими потерями времени на ожидание окончания одного процесса и невозможностью управления параллельным выполнением двумя идентичными процессами, сдвинутыми во времени. Это существенно снижает функциональные возможности устройства и ограничивает область его применения, Цель изобретения - повышение производительности устройства. Поставленная цель достигается тем, что Вустройство, содержащее первый .-и второй блоки памяти, блок По.-шти копий, два регистра.адреса, регистр логических условий, буферный регистр, счетчлк микрокоманд, первый счетчик адреса, первый, второй и третий дешифраторы адреса, первый и второй блоки элементов И, триггер снятия копий,, триггер выдачи копий, генератор тактовых импульсов , два элемента задерх ки и пять элементов И, элемент НЕ, причем информационный вход устройства соединен с первым информационньвл входом первого регистра адреса, выход первого регистра адреса соединен с входом первого дешифратора адреса, выход которого соединен с вхо-.. дом первого блока памяти, первый адресный выход первого блока памяти соединен с первым информационным входом буферного регистра, выход кода проверяемых логических условий первого блока памяти соединен с информационным входом регистра логических условий, выход которого соединен с первым входом первого блока элементов И, выход первого блока элементов И соединен с вторым информационным входом буферного регистра, выход которого соединен с первым входом второго блока элементов И, выход которого соединен с вторым информационным входом первого регистра адреса, второй адресный выход первого блока памяти соединен с информационным входом первого счетчика адреса, выход которого соединен с входом второго дешифратора адреса, выход дешифратора адреса соединен с входом второго блока памяти, информационный выход которого соединен с первым информационным выходом устройства, вход кодов логических условий устройства соединен с вторым входом первого блока элементов И, выход кода длины операционной последовательности первого блока памяти соеди нен с информационным входом счетчика микрокоманд, нулевые выходы которого соединены с входами первого элемента И, выход первого элемента И соединен с первыми входами второго и третьего элементов И и входом элемента НЕ, вы ход генератора тактовых импульсов соединен с первым входом четвертого элемента И и входом первого элемента задержки, выход которого соединен с вторым входом третьего элемента И и входом второго элемента задержки, выход которого соединен с вторым входом второго элемента И, выход вто рого элемента И соединен с вторым входом второго блока элементов И,, вы ход элемента НЕ соединен с вторым входом четвертого элемента И, выход которого соединен с синхронизирующим входом второго дешифратора адреса, выход считывания микрокоманды второго блока памяти соединен со счетнЕлл входом первого счетчика адре са, выход третьего элемента И соединен с входами установки в нуль первого счетчика адреса, регистра логических условий, буферного регистра и синхронизирующим входом первого дешифратора адреса, управляющий вход первого блока памяти соединен с входом установки в нуль первого регистра адреса, выход второго регис тра адреса соединен с входом третье го дешифратора адреса, выход которо го соединен с адресным входом блока памяти копий, введены второй счетчик адреса, триггер, третий и четвертый блоки элементов И, элемент ИЛИ, шестой и седьмой элементы И, одновибратор, причем информационный вход устройства соединен с единичным входом триггера снятия копии, единичный выход которого соединен с первым входом пятого элемента И и управляющим входом третьего блока элементов И, выход которого соединен с информационным входом блока памяти копий, выход окончания выдачи копии блока памяти копий соединен с вторым выходом устройства и нулевым входом триггера управления единичный выход которого соединен с первым входом шестого элемента И, выход генератора тактовых импульсов соединен с вторым входом шестого элемента И, выход которого соединен с первым входом элемента ИЛИ, выход элемента ИЛИ соединен с входом разрешения записи блока памяти копий, вход кодов логических условий устрой ства соединен с единичным входом триггера выдачи копий и первым входом четвертого блока элементов И, вы ход которого соединен с информационным входом второго регистра адреса, нулевой выход триггера снятия копий соединен с первым входом седьмого элемента И, выход которого череэ одновибратор соединен с установочным входом второго с етчика адреса, выход второго счетчика адреса соединен с вторым входом четвертого блока элементов И, выход считывания микрокоманды второго блока памяти соединен с вторым входом элемента ИЛИ, вычитающим входом счетчика микрокоманд и с вторым входом пятого элемента И, выход которого соединен со счетным входом второго счетчика адреса, единичный выход триггера выдачи копий соединен с входом записи второго регистра адреса, синхронизирующим входом третьего дешифратора адреса и вторым входом с€ дьмого элемента И, выход окончания микропрограммы второго блока памяти соединен с первым выходом устройства, с единичньпи входом триггера управления и нулевым входом триггера снятия копий,, выход окончан тя выдачи копий блока памяти копий соединен с нулевым входом триггера выдачи копий и установочным входО|«1 второго регистра адреса, информационный выход блока хранения коПИЙ соединен с вторым выходом устройства. Сущность изобретения состоит в повышении производительности устройства путем оперативного копирования линейных последовательностей микрокоманд первого процесса и использования их копий для управления вторым процессом. Такая задача возникает в случае, когда процессы управления зачастую . описываются нерентабельнглми микропрограммами, что не позволяет одновременно использовать одну и ту же микропрограмму более, чем одному процессу. В случаях, когда реализуемые микропрограммы являются рентабельными, для обеспечения, требуемой надежности управления технологическими процессами, требуется предоставление каждому процессу индивидуальной копии микропрограммы. Общий принцип действия (дисциплина функционирования) предлагаемого устройства состоит в следующем. При выполнении микропрограмм управления процессом П. осуществляется их копирование (перезапись)в специальном оперативном блоке памяти с целью последующего использования для управления идентичным процессом П-. При этом емкость блока хранения копий может определяться самой длинной микропрограммой, реализуемой при выполнении процесса (последовательности процессов) П. Управление процессами П и П организуется следующим образом. При выдаче микропрограммы для управления процессом П осуществляется ее копирование в специальном блоке хранения копий и при поступле нии запроса на управление процессом П. выдается сформированная копия. Отличительными особенностями г редлагаемой дисциплины функциониро вания является использование конвейерного принципа обработки и сущест венно асинхронное взаимодействие (по рядок выполнения) процессов П и П Принцип конвейерной обработки pea лизуется за счет копирования выполняемой микропрограммы и ее последующего использования для управления вторым процессом. При этом априори неизвестен момент прихода заявки на управление процессом П. Поэтому копирование микропрограммы управлени процессом П осуществляется с опреде ленным временным упреждением. Введение второго счетчика адреса и обусловленных им связей необходимо для подсчета выданного количества микрокоманд и задания адреса ячейки в блоке хранения копий, по которому находится первая микрокоманда снятой копии. Введение третьего блока элементов И и обусловленных им связей позволяе управлять передачей операционных мик рокоманд с выхода второго блока памя ти на вход блока хранения копий. Введение триггера управления, шес того элемента И, элемента ИЛИ и обус ловленных ими связей позволяет управ лять считыванием микрокоманд из блока хранения копий в то время, когда выдача линейной последовательности микрокоманд основного процесса из второго блока памяти закончена. Введение четвертого блока элементов И необходимо для перезаписи кода адреса первой микрокоманды в блоке хранения копий при выдаче всей последовательности для управления втоpbff-i процес с ом. ;ВБедение одновибратора, седьмого элемента И и обусловленных ими связей необходимо для организации обну ления счетчика адреса. Введение пятого элемента И и обус ловленных им связей позволяет определить адрес первой микрокоманды при снятии копии. На фиг.1 представлена функциональная схема предлагаемого микропро граммного устройства; на фиг.2 функциональная схема блока хранения копий; на фиг. За,б,в - соответствен но форматы адресной микрокоманды первого запоминающего блока, операционной микрокоманды второго запоминающего блока и операционной микрокоманды блока хранения копий. Микропрограммное устройство управ ления содержит (фиг.1) первый 1 и второй 2 блоки памяти, блок 3 хранения копий, первый регистр 4 адреса, регистр 5 логических условий, буферный регистр 6, второй регистр 7 адреса, счетчик 8 микрокоманд, первый счетчик 9 адреса, второй счетчик 10 адреса, первый 11, второй 12 и третий 13 дешифраторы адреса, триг- гер 14 снятия копий, триггер 15 выдачи копий, триггер 16 управления, первый 17, второй 18, третий 19 и четвертый 20 блоки элементов И, пер-вый 21, второй 22, третий 23, четвертый 24, пятый 25, шестой 26 и седьмой 27 элементы Н, элемент ИЛИ 28, первый 29 и второй 30 элементы задержки, элемент НЕ 31, генератор 32 тактовых импульсов и одновибратор 33, первый 34 и второй 33 входы устройства, первый 36 и второй 37 выходы устройства, первый адресный выход 38, выход 39 кода проверяемых логических условий, второй адресный выход 40, выход 41 кода длины операционной последовательности и управляющий выход 42 первого блока 1 памяти, информационный выход 43, выход 44 считывания микрокоманды, выход 45 окончания MHI POпрограммы второго блока2 памяти, адресный 46, информационный 47, разрешения записи 48 входы, информационный выход 49 и выход 50 окончания выдачи копии блока 3 хранения копий. Блок 3 памяти копий (фиг.2) содержит группу регистров 51.1-51.п, коммутатор 52. Формат адресной микрокоманды (фиг,За) содержит поле кода (номера следующей последовательности (А ), поле кода проверяемых логических условий (X), поле кода начального адреса текущей последовательности микрокоманд (А), поле длины линейной последовательности микрокоманд (L) и поле метки (М) выдачи адресной микрокоманды. Формат операционной микрокоманды второго запоминагадего блока (фиг.Зб) содержит поле операционной микрокоманды (ПОМК), поле метки (идентификатора) считывания очередной микрокоманды (Ml) и поле метки (идентификатора) окончания процесса выдачи операционных микрокоманд (М2). Формат операционной микрокоманды блока хранения копий (фиг.Зв) содержит два поля: в первом поле находится копия операционной микрокоманды (ПКОМК), во втором - метка окончания процесса выдачи операционных микрокоманд (М2) . Рассмотрим назначение элементов устройства. Первый блок 1 памяти устройства предназначен для хранения адресных микрокоманд. В блоке 1 запис ывается адресная часть микрокоманды, которая считывается в следующем виде: с выхода 38 номер следующей последовательности, с выхода 3.9 - код проверяемых логических условий, с выхода 40 - началь ный адрес текущей микрокоманды, с .выхо,ца 4Д - число выполняемых микрокоманд в текущей линейной последова.тельности, с выхода 42 - сигнал сбро са первого адресного регистра 4. Второй блок 2 памяти предназначен для хранения операционных последовательностей микрокоманд. Блок 3 хранения копий предназначен для оперативного хранения и вьща чи на второй выход 37 устро -дства копии первого процесса. Первый регистр 4 адреса и первый дешифратор 11 адреса и соответств уго дие связи предназначены для выборки информации из блока 1, Регистр 5 логических условий пред назначен для хранения кодов лроверяемых логических условий. Первый блок элементов И 17 предназначен для модификации кода очеред ного адреса адресной микрокоманды на буферном регистре б в зависимости от кодов логи1еских условий, поступающи с второго входа 35 устройстваf и код регистра 5 логических условий. Второй блок элементов И 18 предназначен для управления перезаписью кода адреса г сформированного в буфер ном регистре б, в первый регистр 4 адреса. Счетчик 8 микрокоманд предназначяп для загшси числа операционных мггкрокоГТандJ, которые должны быть выданы с выхода второго блока памяти 2 к осу111есгвления контроля их выдачи., ПерБый элемент 29 задерлски и трагий элемент И 23 и соотве ствующие HIM связи предназначены для управлеяия обнулением первого адресного счетч ка 9. регистра 5 логических ус лозкй,- буферного регистра 6; а также формиро зания угфавляюцего c- rnasia на ч:теккэ адресной микрокоман:,::: из перзого блока 1 памяти по адресу,- храч :мо&.1у в первом адресном регистре 4« морой элемент 30 задержки и вто:;;fi элемект И 22 с ооответствующит и ::Бяая,ж предказначекы для упраЕ1ле -:йя через второй блок элементов И 3 8 :iepe3s.nKCbFC инфор «1ацик кэ буферного эегистрг б з первый адресный регистр Генератор 32 тактовых .пульсоБ лредказначен для аырабсткк импульсов такто:асй частоты. Элемент НЕ 31 управляет прохожде-лием через четвертый элемент И 24 тгкТОЕык импульсов для считьгвания из блока 2 операционных микрокоманд по адресу с первого счетчика 9 адреса. Триггер 14 уг;раБЛяет снятием коJJM:;-J первого процесса через третий блок элементов И 19 с выхода блока 2, а также формированием адреса первой микрокоманды снятой копии через пятый элемент И 25. Триггер 15 управляет снятием копии с информационного выхода 49 блока 3 через третий дешифратор 13. Триггеры 14 и 15 являются R-S-триггерами с приоритетом по S-входу, т.е. при одновременном поступлении сигналов на R и S входы этих триггеров они переходят (остаются) в единичном состоянии. Второй счетчик 10 адреса предназначен для указания глубины заполнения операционными микрокомандами блока 3. Второй регистр 7 предназначен для хранения адреса микрокоманды, с которой необходимо начать выдачу копии из блока 3.. Занесение информации и обнуление регистра 7 производится только при нулевом потенциале на его управляющем входе. Триггер 16, шестой элемент И 26, элемент ИЛИ 28 и соответствующие связи предназначены для организации выдачи копии из блока 3 по окончании процесса выдачи последовательности операционных микрокоманд из блока 2. Одновибратор 33, седьмой элемент И 27, соответствующие связи осуществляют приве дение в исходное состоя;ние второго счетчика адреса по окончании снятия копии. Рассмотрим назначение элементов блока 3 памяти копий {фиг.. 2) . Груп:па из п р€;гистров 51. 1-51. п представляет собой сверхоперативную память и служит для хранения операционных микрокоманд, поступающих ка вход 47 блока 3. Коммутатор 52 предназначен для :выдачи операционной микрокоманды с тог-с регистра группы, в котором находр лась микрокоманд:1;а при поступлении эв.проса на выдачу копии. При нулевом коде на входе 46 информация на выходд коммутатора 52 не проходит. При поступлении на.вход 46 кода О, ..,01, который соответствует исходному нулевому состоянию регистра 7; информация на выход коммутатора 52 проходит с входа 47,. при поступлении на вход 46 кода 0,..010 информация на выход комз утатора 52 проходит с регистра 51.1 и т. д. Микропрограммное устройство для контроля и управления двумя процессами может работать в двух режимах: режиме контроля и управления одним процессом и режиме контроля и управления двумя процессами. Режим контроля и управления двумя процессами может осуществляться путем снятия копки первого процесса (в€;дущего) и выдачи копии для управления вторым процессом (ведомым) ли бо путем параллельной вьвдачи управляющей информации на оба процесса,

В исходном состоянии все элементы памяти находятся в нулевом состоянии. Входы начальной установки элементов памяти на фиг.1-3 не показаны.

В режиме контроля и управления одним процессом код (номер) операции поступает через вход 34 устройства в регистр 4 адреса и задает начальный адрес в блоке 1.

Счетчик 8 микрокоманд находится в нулевом состоянии, на нулевых выходах этого счетчика имеются высокие потенциалы, которые поступают на элемент И 21. Сигнал с выхода элемента И 21 поступает на входы элементов И 22 и 23 и разрешает прохождение импульса с выхода генератора 32 через первый элемент 29 задержки на вход обнуления счетчика 9, регистра 5 и буферного регистра б, а также на управляющий вход первого дешифратора 11.

По сигналу, поступающему на управляющий вход первого дешифратора 11, по начальному адресу регистра 4 из блока 1 считывается код (номер следующей выполняемой линейной последовательности) , который с выхода 38 поступает на вход регистра 6. Код номера текущей выполняемой последовательности с выхода 40 блока 1 поступает на информационный вход парно. го счетчика 9 адреса. Код проверяемых логических условий поступает с выхода 39 первого запоминающего блока 1 на вход регистра 5 логических условий. Код длины линейной последовательности микрокоманд поступает на вход счетчика 8 с выхода 41 блока 1. Сигнал с выхода 42 блока 1 производит установку в нуль регистра 4 адреса и подготавливает его для записи очередного адреса адресной микрокоманды.

После считывания адресной части микрокоманды и записи в счетчик 8 кода числа микрокоманд линейной последовательности показания счетчика 8 отличны от нуля. Сигнал на выходе элемента И 21 принимает нулевое значение и через элемент НЕ 31 готовит элемент И 24 к прохождению через него импульсов с выхода генератора 32.

Очередной тактовый импульс с выхода генератора 32 поступает на управляющий вход дешифратора 12 адреса, который производит выборку из блока 2 операционной микрокоманды, начальный адрес которой был записан в счетик 9. С информационного выхода 43 блока 2 считываются операционные микокоманды на выход 36 устройства.

После считывания очередной операционной микрокоманды с выхода 43 блока 2 с выхода 44 импульс считывания микрокоманды поступает на счетный вход счетчика 9 и изменяет (увеличивает) его содержимое на единицу. Одновременно с этим данный импульс считывания поступает на вычитающий вход счетчика 9, уменьшая его содержимое на единицу.

Очередной тактовый импульс с выхода генератора 3 через элемент И 24 поступает ка синхронизирующий вход дешифратора 12 адреса, так как состояние счетчика 8 микрокоманд от.пично от нулевого и на выходе элемента И 21 букет сигнал, который через э.чемент Е 31 разрешает прохождение тактовых импульсов через элемент И 24. ЛР1чифратор 12 адреса производит выо очередной мн рокоманды из а 2 по адресу, сформнров 5нному в лчатчике 9 адреса. Происходит считывы,-t на выход 36 устройства очередно.-; с-терационной микро {Ома;яь5. Аналог}г:;;мм образом происходит считьава И е /-.-ггавшихся операционных микрокоманд линейной последовательности .

По сигналу выдачи последней операционной микрокоманды линейной последовательюсти с выхода 44 блока 2 счетчик 3 микроко 1анд обнуляется, и на выходе элемента И 21 поквляетс.ч сиг:,;., который через э.чемент НЕ 31 запЕ--е цает проуожден:- е тактовых иМпульсгв с выхода т-енерагора 32 на элеме; т И 2Л. Тем самым элемент И 24 запрещает считыван: е операц1 ;окньх ;.1икрокомянд ИЗ блока 2.

Тактовый и шульс генератора 32, ВР4П, для считывания псследкей опера1 ионной микрокоманды линейной последовательности, проходя через первый 29 и Бторой 30 элементы задержки с выхода элемента И 22, поступает на второй вход блока элементон К 18. Адрес очередной линейной последовательности с выхода буферного регистра b через блок элементов И 18 переписмваегея в регистр 4 адре

Код ггдреса бу ферного регистра 6 состоит ит постоянной и переменной частей. Пос:тоянная часть (базовый адрес) записывается в буферный регипчр б с выхода 38 первого блока i памяти. Переменная часть кода является мидифициpye юй частью адреса в зависимости от кода логических услвий, поступаю1д;-1Х с второго входа 35 устройства. Поступающие логические условия модифицируют при ветвлении код косьенного адреса, записанного в буферном регистре 6. Сформированный таким образом код адреса в конце выдачи предыдущей линейной последователькост - микрокоманд пересылается из буферного регистра 6 в регистр 4 адреса. Импульс считывания последней операционной микрокоманды линейной последовательности не успевает обнулит регистр 5 логических условий и буфер ный регистр 6 (обнуление не должно быть проведено до тех пор, пока «е произойдет модификация адреса в конце линейной последовательности), а также осуществить перезапись информа ции из буферного регистра 6 в регист 4 адреса. Это объясняется тем, что . время задержки первого элемента 29 задержки выбрано меньшшч, чем время считывания операционной микрокоманды из блока 2, а время задержки второго элемента 30 задержки выбрано большим времени считывания адресной микрокоманды из блока 1. Очередной тактовый импульс после считывания последней операционной микрокоманды предыдущей линейной последовательности с выхода генератора 32 через первый элемент 29 задержки поступает на второй вход элемента И 23. Сигнал на первом входе элемента И 23, соединенном с выходом элемента И 21 (после выдачи последней микроко манды линейной последовательности со тояние счетчика 8 микрокоманд будет нулевым и на выходе элемента И 21 бу дет высокий потенциал) разрешает прохождение тактового импульса для обнуления регистра 5 логических условий, буферного регистра 6 и первого счетчика 9 адреса. Одновременно с этим данный импульс, поступая на синхронизирующий вход дешифратора 11 адреса, производит считывание очеред ной адресной микрокоманды из блока 1 по адресу, сформированному на регистре 4 адреса. Состояние счетчика 8 микрокоманд становится отличным от нулевого, и с выхода элемента И 21 сигнал запретает обнуление счетчика 9 адреса и перезапи.сь информации из регистра б в регистр 4. Далее работа устройства происходит аналогично. В режиме контроля и управления днумя процессами управление двумя процессами заключается в снятии копии первого процесса (ведущего) и вы Дс1чи ее второму (ведомому) процессу. При этом второй процесс может либо совпадать с первым (осуществляется Псфаллельная выдача двух последовательностей микрокоманд), ли бо не совпадать (осуществляется управление процессами со сдвигом во времени). Для управления первым процессом операционные микрокомандывыдаются с информационного выхода 43 блока 2 и поступают на первый выход 36 устройства. Сигнал на снятие копии первого процесса приходит с поступлением кода операции с входа 34 устройства на единичный вход триггера 14, Единичный выход триггера 14 разрешаетснятие копни (последовательностей операционных микрокоманд) с информационного выхода 43 через блок элементов И 19 на информационный вход 47 блока снятия копий 3 (фиг.2). Идентификатор (метка) выдачи очередной операционной микрокоманды с выхода 44 блока 2, поступая через элемент ИЛИ 28 на синхронизирующие входы регистров 51. 1-51.п, разреша,г: ет запись первой операционной микрокоманды последовательности с входа 47 блока в регистр 51.1 группы регистров. Длительность импульса метки выбирается так, чтобы она не превышала времени срабатывания триггеров регистров 51.1-51,л. Кроме того, метка выдачи операционной микрокоманды с выхода 44 блока 2 через элемент И 25 поступает на счетный вход счетчика 10 адреса и увеличивает его состояние на единицу. Счетчик 10 адреса отслеживает глубину заполнения блока 3, т. е. определяет адрес первой микрокоманды вьщанной последовательности. При выдаче очередной микрокоманды с выхода 43 блока 2 идентификатор выдачи с выхода 44 через элемент ИЛИ 28 поступает на вход 48 блока 3 хранения копий. С входа 48 этот сигнал поступает на синхронизирующие входы группы регистров 51.1-51.п и осуществляет перезапись предыдущей микрокоманды из регистра .1 в регистр 51,2. Поступившая микрокоманда записывается в первый регистр 51.1. Группа регистров 51.1-51.П может .быть выполнена, например, на основе D-триггеров. Аналогичныгл образом блок 3 хранения копий заполняешься операционными микрокомандами по мере их выдачи с выхода 43 блока -2. Счетчик 10 адреса по мере поступления микрокоманд в блок 3 по идентификатору их выдачи считает их количество, определяя тем самым адрес того регистра группы Sl.l-Bl.n, в котором находится первая операционная микрокоманда снятой копии (счетчик 10 адреса в этом случае выполняет роль указателя стекаГ. При необходимости выдать снятую копию первого процесса для управления вторым процессом с входа 35 устройства поступает сигнал на выдачу копии на единичный вход триггера 15 выдачи копий и на вход блока элементов И 20. Переключение триггера 15 по данному сигналу происходит после занесения информации в регистр 7. Это обеспечивается введением задержки срабатывания триггера 15 по входу S. Сигнал на снятие копии разрешает переписать информацию со счетчика 10 адреса в регистр 7 адреса. В этом сл чае регистр 7 адреса определяет чере дешифратор 13 адреса тот регистр группы 51.1-51.п, в котором находитс первая микрокоманда копии. Сигнал с выхода дешифратора 13 ад реса поступает на соответствующий уп равляющий вход коммутатора 52, тем. самым коммутируя с выбранного регист ра группы 51.1-51.п поступающую инфор мацию на выход 37 устройства для управления вторым процессом. В том случае, когда процесс снятия копии закончился, а процесс выдачи, копии продолжается, по метке окончания микропрограммы с выхода 45 блока 2 триггер 16 управления переходит в единичное состояние, разрешив тем самым прохождение тактоьых т тульсов с выхода генератора 32 через элемент и 26 и элемент ИЛИ 28 на синхронизирующие входы группы регистров 51.151.п блока 3 снятия копий. Эти импульсы осуществляют сдвиг информации и выдачу микрокоманд с того- регистра адрес которого был выбран регистром адреса по сигналу вьщачи копии. Кроме того, по мере окончания микропрограммы основного процесса с выход 45 блока 2 происходит обнуление триггера 14. По перепаду потенциала на нулевом выходе триггера 14 снятия коПИЙ на выходе одновибратора 33 появляется импульс. Этот импульс поступа|ет на вход установки в нуль счетчика 10 адреса. Сдвиг между выдачей основной микропрограммы и ее копии не может быть больше N-1 такта (микрокоманд) , где N - длина микропрогрги-пиы. Возможен случай когда до окончария процесса снятия копии необходимо начать выполнение новой микропрограммы для управления первым процессом и снятия копии этой микропрограммы для управления вторым процессом. В этом случае с входа 34 устройства на информационный вход регистра 4 адреса заносится новый код операции, а сигнал на снятие копии поступает на единичный вход триггера 14. Далее работа устройства продолжается аналогичным образом. Однако в этом случае сигнал на выдачу второй копии должен поступить не ранее вьщачи первой 1Лэпии. При поступлении на регистр, с которого считывается инфор мация, микрокоманды, содержащей единичное значение метки М 2, на управляющем выходе 50 блока 3 появляется сигнал, характеризующий окончание вьадачи копии. Сигнал окончания процесса выдачи копии поступает с выхода 50 на нулевой вход триггера 16 управления, на нулевой в:Лэд триггера 15 -выдачи копий и вход установки в нуль регистра 7 адреса. Если при этом на вход 35 поступает сигнал на продолжение копирования следуквдей микропрограммы, то состояние триггера 15 . и регистра 7 не изменяется (триггер 15 имеет приоритет срабатывания по S-входу и запрещает установку исходного кода в регистре 7). Если сигнал на снятие новой копии на вход 35 не поступает, то устройство находится в исходном, состоянии и готово к работе в зависимости от начального кода, поступающего на информационный вход регистра 4 адреса с входа 34 устройства. При - необходимости выдачи копии параллельно с основным процессом сигнал на такой режим работы устройства подается с входом 34 и 35 устрюйства на единичные входы триггера 14 снятия копий и триггера 15 выдачи копий. На выходе дешифратора 13 адреса появляется сигнал. Данный сиг- нал, поступая на соответствующий управляющий вход коммутатора 52, разрешает прохождение операционных микрокоманд с входа 47 блока хранения копий на информационный выход 49 и о него на второй выход 37 устройства .

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство микропрограммного управления | 1972 |

|

SU482744A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-05-15—Публикация

1983-02-08—Подача