1357

ся то, что точность отсчета временного интервала таймером равна одному дискрету отсчета времени и не зависит от .числа одновременно отрабатываемых интервалов, кроме того, имеется возможность оперативного изменения .длительностей отрабатываемых интервалов времени при управлении различными технологическими процессами. Автоматический выбор свободной ячейки позволяет упростить программирование за счет возможности применения макрокоманд высокого уровня, т.к. при за-. писи не требуется информация о занятых и свободных ячейках памяти, и.

1

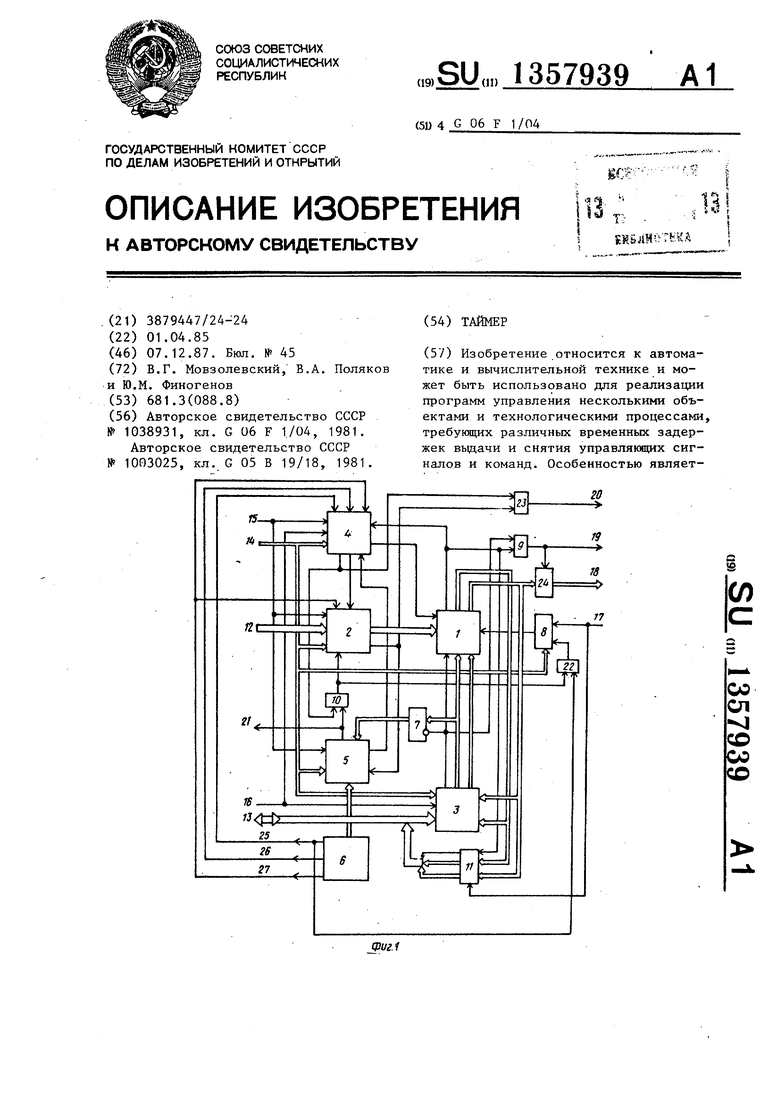

Изобретение относится к автоматике и вычислительной технике и может быть использовано для реализации программ управления несколькими объектами и технологическими процессами, требующих различных временных задержек вьщачи и снятия управляющих сигналов и-команд.

Целью изобретения является расши- рение функциональных возможностей за счет повышения точности отсчета временных интервалов.

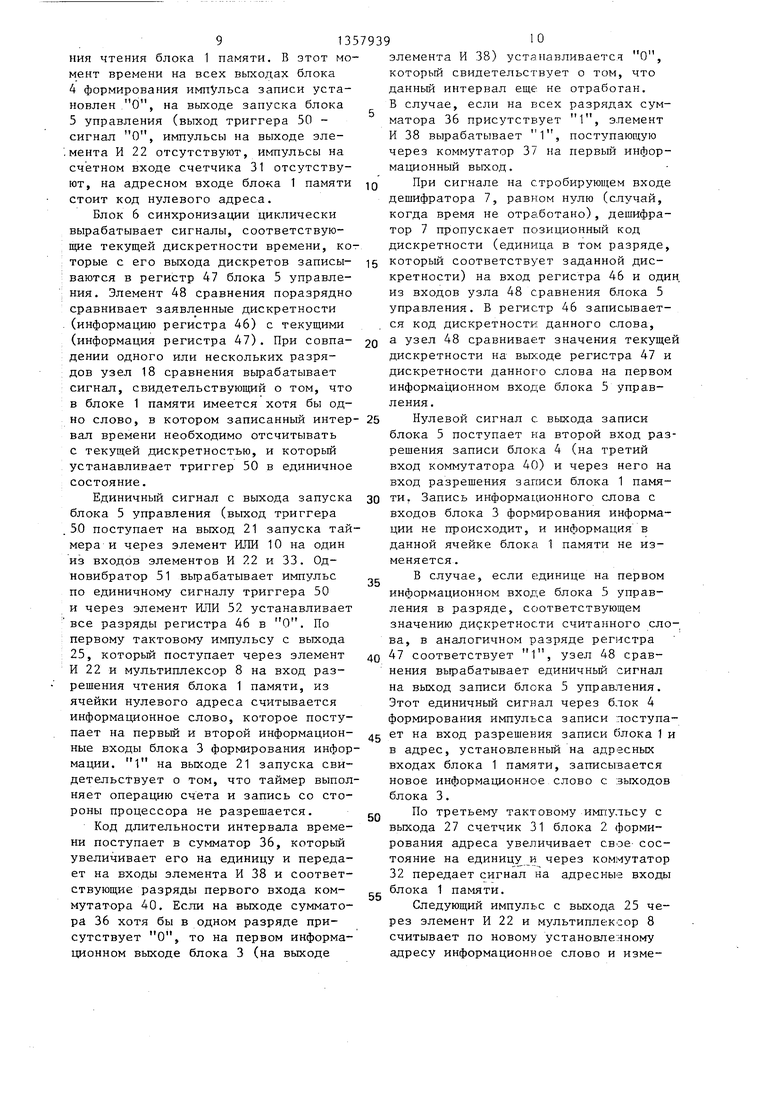

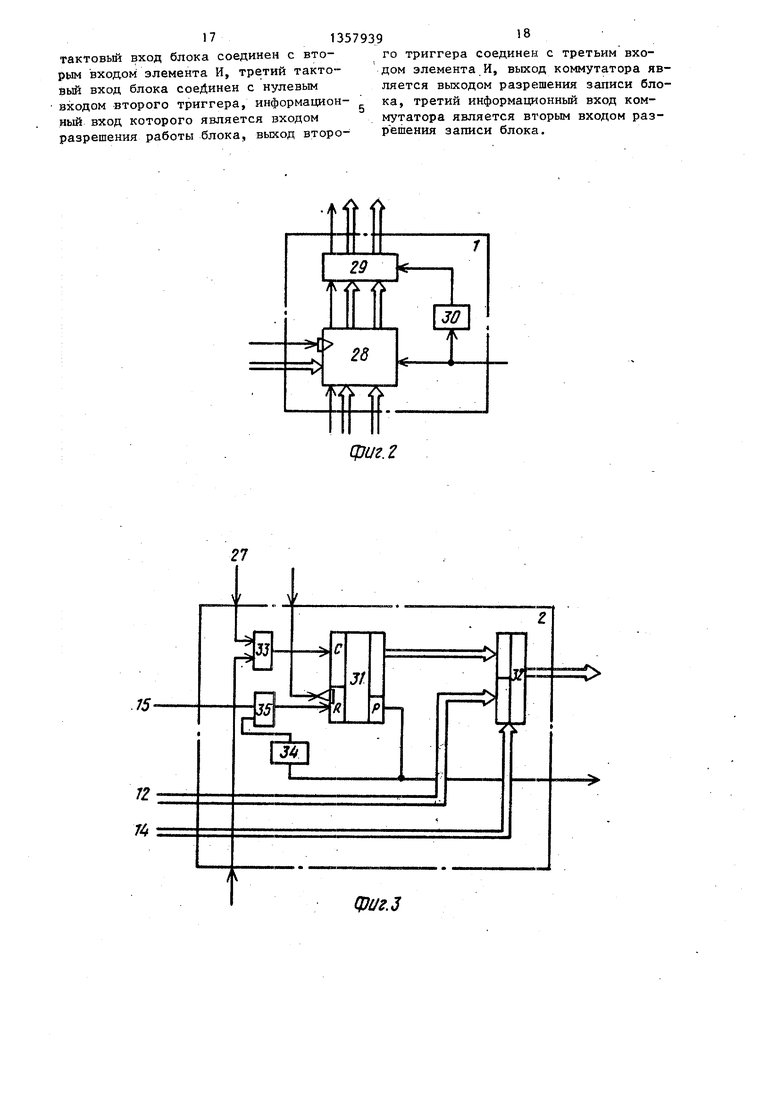

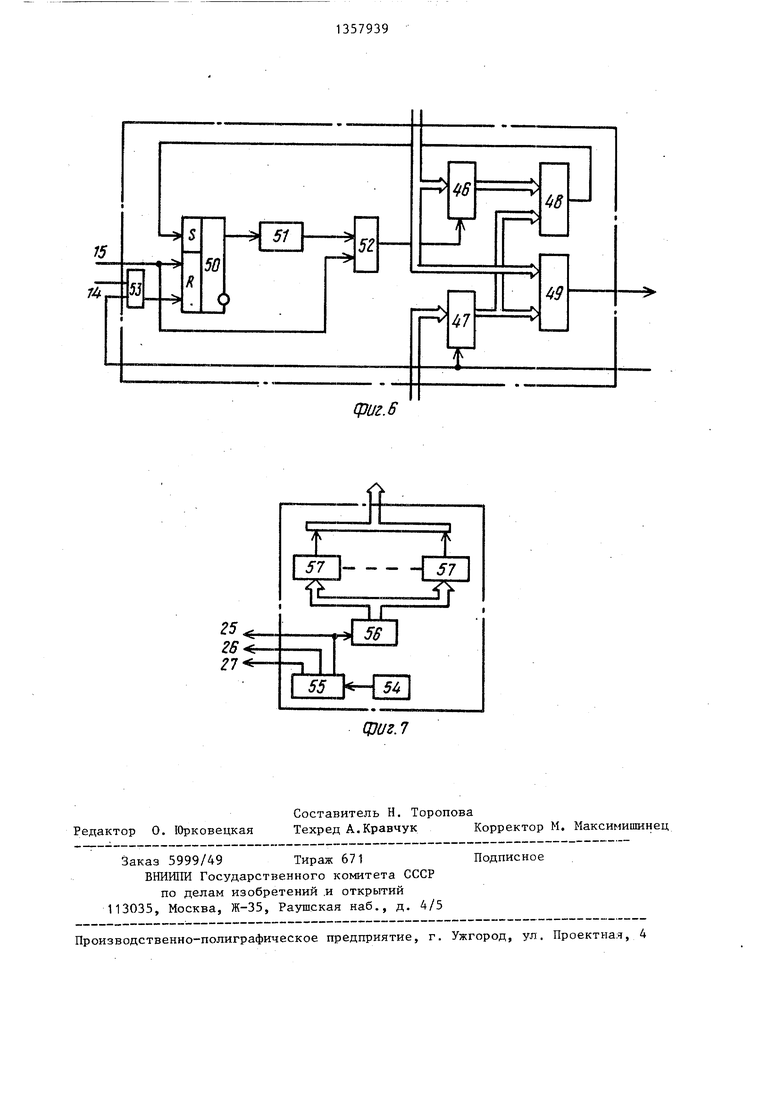

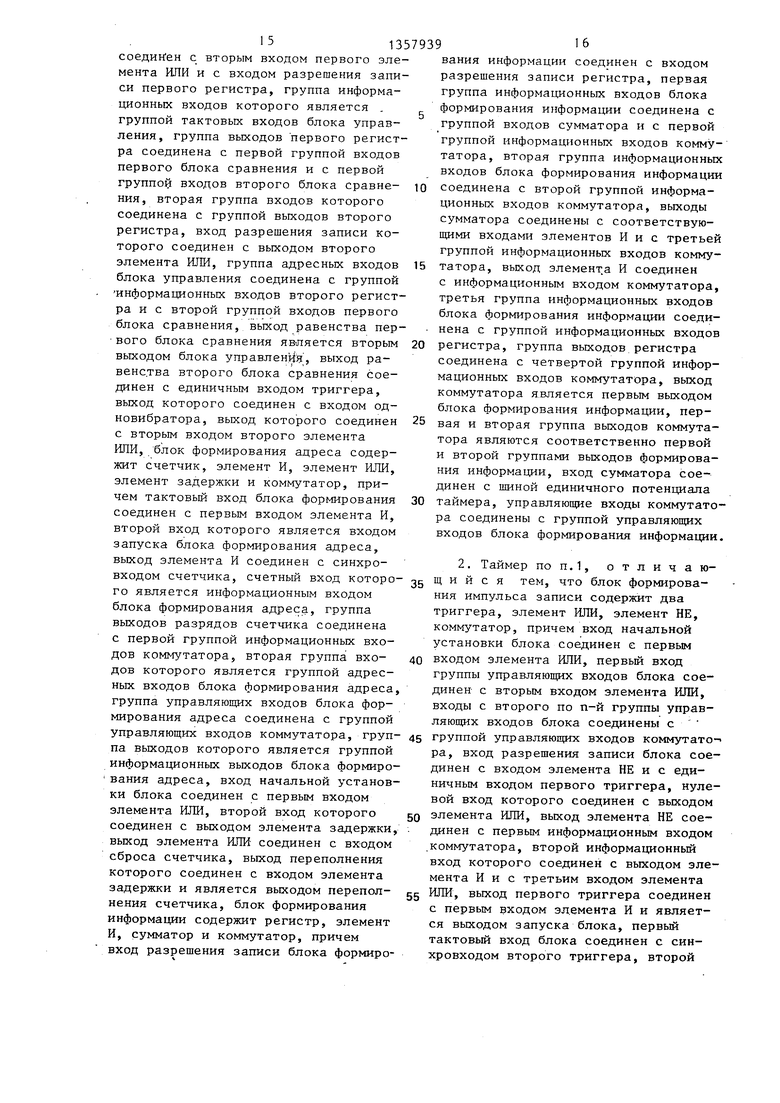

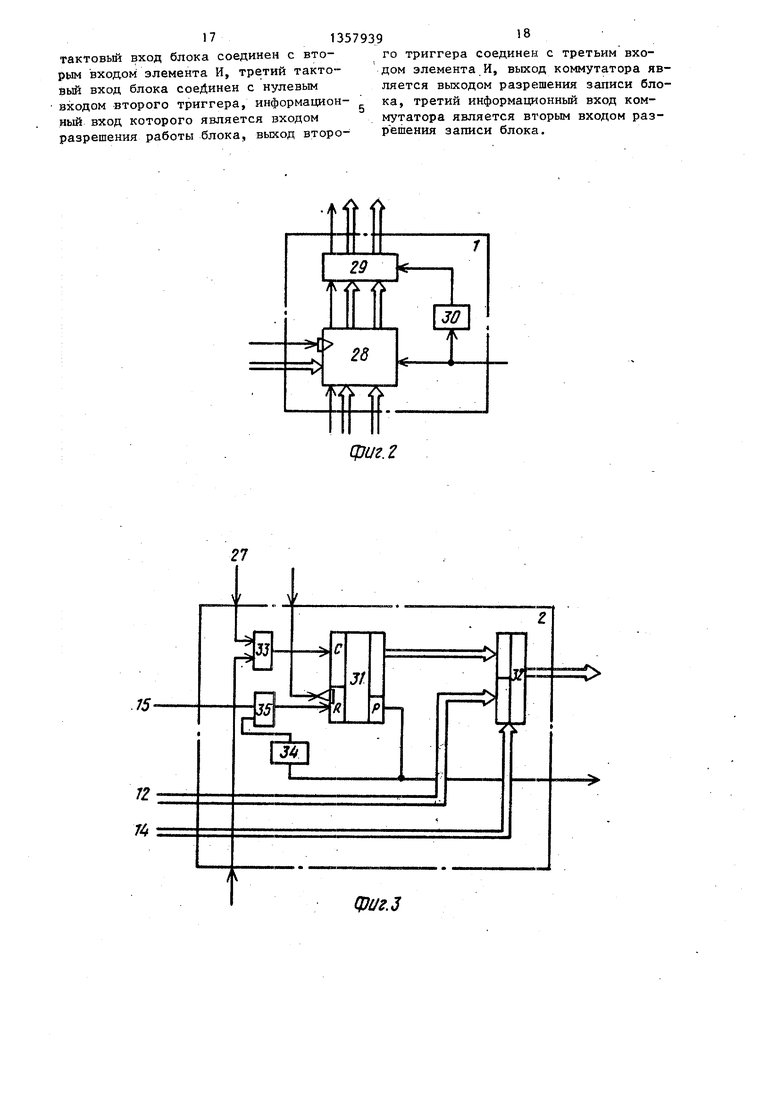

На фиг.1 представлена структурная схема таймера; на фиг.2 - структурная схема блока памяти; на фиг.З - схема блока формирования адреса; на фиг.4 - схема блока формирования информации; на фиг.5 - схема блока формирования импульса записи; на фиг.6 - схема блока управления; на фиг.7 - схема блока синхронизации.

Таймер содержит блок 1 памяти, блок 2 формирования адреса, блок 3 формирования информации, блок 4 фор- мирования импульса записи, блок 5 управления, блок 6 синхронизации, дешифратор 7, мультиплексор 8, элемент И 9, элемент ИЛИ 10, магистральный усилитель 11, группу 12 адресных входов, группу 13 входов временных интервалов, группу 14 входов задания режима таймера, вход 15 начальной ус- тановки, вход 16 разрешения записи, вход 17 разрешения чтения, группу 18 информационных выходов, выход 19

кроме того, уменьшается время работы процессора с таймером, что позволяет повысить скорость работы ЭВМ с временными командами. Целью изобретения является расширение функциональных возможностей за счет повышения точности отсчета временных интервалов. Поставленная цель достигается за счет введения блока 2 формирования адреса, блока 3 формирования информации, блока 4 формирования импульса записи, блока 6 синхронизации, блока 5 управления, магистральных усилителей 11, 24, мультиплексора 8. 1 з.п. ф-лы, 7 ил.

5

5 о

5

строба, выход 20 занятости таймера, выход 21 запуска, элементы И 22 и 23, магистральный усилитель 24 и выходы 25-27 блока 6 синхронизации.

Блок 1 памяти содержит уз ex.: 28 памяти, регистр 29 и элемент 30 задержки.

Блок 2 формирования адреса содержит счетчик 31, ком1чутатор 32, элемент И 33, элемент 34 задержки и элемент 35 ИЛИ. Счетчик 31 по импульсу с тактового выхода 27 блока 6 (фиг.1) синхронизации, поступающего через элемент И 33 (фиг.З) по сигнаг.у разрешения с вьгхода элемента ИЛИ 10 (фиг.1), изменяет код на своем информационном выходе. При переполнении счетчика импульсами вырабатывается сигнал переполнения, который поступает на один из входов элемента И 23, второй вход установки в исходное состояние блока 5 упра;зления и через элемент 34 задержки (фиг.З) устанавливает счетчик в нулевое состояние. Коммутатор 32 пропускает инфор мацию на выход, который является адресным выходом блока 2, с выхода счетчика 31 или группы 12 входов таймера в зависимости от сигнала на группе 14 входов задания режима таймера.

Блок 3 формирования информации содержит сумматор 36, коммутатор 37, элемент И 38 и регистр 39.

Блок 4 формирования импульса записи содержит коммутатор 40, триггер

41, триггер 42, элемент И 43, элемент НЕ 44 и элемент ИЛИ 45.

Блок 5 управления содержит регистры 46 и 47, узлы 48 и 49 сравнения, триггер 50, одновибратор 51 и эле-f менты ИЛИ 52 и 53.

Блок 6 синхронизации содержит генератор 54 импульсов, распределитель 55 импульсов, счетчик 56 и дешифраторы 57.

Таймер работает следующим образом.

После включения питания на вход 15 начальной установки поступает сиг- н.ал, по которому триггеры 41 и 50,

Ю

По переднему фронту первого так вого импульса в буферный регистр 3 блока 3 записывается информация с группы 13 входов, которая через ко мутатор 37 поступает на информацио ные входы блока 1 памяти и дешифра ра 7. Единица информационного слов устанавливает выходы дешифратора 7 в нулевое состояние, и регистр 46 блока 5 управления не изменяет сво состояния. При единичном значении сигнала на входе 16 разрешения зап си, поступающего на вход коммутато с выхода элемента НЕ 44 блока 4, н

регистр 46 и счетчик 31 устанавлива- f5 его вькоде нулевой сигнал, запись

в блок 1 памяти не происходит. По заднему фронту положительного импу са на входе 16 разрешения записи, который на выходе блока 4 преобраз ся в передний фронт положительного импульса, происходит запись в ячей блока 1 .памяти, адрес которой уста новлен на адресном входе. Изменяя последовательно адреса на группе 1 входов временных интервалов и выра тывая импульс записи, процессор пр водит блок 1 памяти в исходное сос тояние, что соответствует тому, чт ячейки свободны для принятия инфор ции.

ются в нулеЗзое состояние. Одновременно запускается блок 6 синхронизации, вырабатывающий тактовые импульсы. По заднему фронту импульса с третьего выхода 27 блока 6 устанавливается

в О триггер 42. Магистральные усиII

лители 11 и 24 находятся в состоянии.

третьем

Процессор устанавливает таймер в режим прямого доступа к блоку 1 памяти, при котором сигналом по входам 14 коммутатор 40 блока 4 подключает ВХОД. 16 разрешения записи к входу разрешения записи блока 1 памяти, коммутатор 32 блока 2 формирования адреса подсоединяет шину 12 к группе адресных входов блока 1, мультиплексор 8 подсоединяет вход 17 разрешени чтения таймера к входу разрешения чтения блока 1, коммутатор 37 блока 3 соединяет выход регистра 39 с информационными входами блока 1 памяти Из процессора на входы 12 адреса подается начальный адрес блока 1 памяти, который поступает на его вход через блок 2.

При нулевом сигнале на стробирую- щем входе дешифратор 7 вьфабатывает сигналы в соответствии с входной информацией.

.Мультиплексор 8 пропускает на вход разрешения чтения блока 1 памяти сигналы с входа 17 разрешения чте НИН или выхода элемента И 9 в зависимости от сигналов группы 14 входов задания режима таймера.

Магистральные усилители 11 и 24 при единичном сигнале на входах управления пропускают информацию с входа на выход, при нулевом сигнале управления выходы устана вливаются в третье состояние.

По переднему фронту первого тактового импульса в буферный регистр 39 блока 3 записывается информация с группы 13 входов, которая через коммутатор 37 поступает на информационные входы блока 1 памяти и дешифратора 7. Единица информационного слова устанавливает выходы дешифратора 7 в нулевое состояние, и регистр 46 блока 5 управления не изменяет своего состояния. При единичном значении - сигнала на входе 16 разрешения записи, поступающего на вход коммутатора с выхода элемента НЕ 44 блока 4, на

5 его вькоде нулевой сигнал, запись

0

5

0

,„

в блок 1 памяти не происходит. По заднему фронту положительного импульса на входе 16 разрешения записи, который на выходе блока 4 преобразуется в передний фронт положительного импульса, происходит запись в ячейку блока 1 .памяти, адрес которой установлен на адресном входе. Изменяя последовательно адреса на группе 13 входов временных интервалов и вырабатывая импульс записи, процессор приводит блок 1 памяти в исходное состояние, что соответствует тому, что ячейки свободны для принятия информации.

В режиме прямого доступа к блоку 1 памяти процессором может быть записана требуемая информация в любую ячейку. В этом же режиме процессор

« имеет возможность считать информацию из любой ячейки блока 1 памяти. Для этого на группе 13 входов временных интервалов выставляется адрес, который блоком 2 передается на адресный

0 вход блока 1. Затем на вход 17 разрешения чтения подается импульс, по которому из ячейки узла 28 памяти по установленному адресу считывается информация, которая переписывается

5 в регистр 29. Сигналом с входа 17 разрешения чтения магистральный усилитель 11 устанавливается в режим пропускания информации с выходов блока 1 памяти, и считанная информация поступает на группу 13 входов для передачи в процессор.

После приведения в исходное состояние блока 1 памяти таймер устанав- , ливается в режим автономной работы.

5 В автономном режиме таймер может

осуществлять следующие операции: запись выставляемой по группе 13 входов информации (номер реле времени, длительность интервала времени, которая

5135

должна быть отработана )з;анным реле, дискретность отсчета задаваемого интервала и признак занятости ячейки) в свободную ячейку запоминающего устройства блока 1 памяти, а также отсчет записанных в ячейках блока 1 -интервалов времени с заданными диск- ретностями и выдачу номеров отработавших реле времени через магистраль ный усилитель 24 на группу 18 выходо таймера.

Запись в автономном режиме осуществляется в следующей последовательности: поиск свободной ячейки в блоке 1 памяти; запись требуемой информации в эту ячейку.

Для записи требуемой информации процессором в режиме автономной работы таймера по группе 14 входов зада- кия режима таймера выставляется сигнал, по которому коммутатор 32 блока 2 формирования адреса подключает адресный вход блока 1 памяти к выходу счетчика 31, коммутатор 37 блока 3 формирования информации подсоединяет информационные входы блока 1 памяти и дешифратора 7 к выходу регистра 39, вход разрешения записи блока 1 памяти коммутатор 40 блока 4 соединя ет с выходом элемента И 43, триггер 50 блока 5 управления блокируется (запрещается его установка, в единичное состояние), мультиплексор 8 подключает вход разрешения чтения блока 1 к выходу элемента И 22.

На группу 13 входов процессор выставляет требуемую информацию и вырабатывает по входу 16 разрешения записи импульс, действующий в момент времени существования первого тактового импульса на выходе 25 блока 6 синхронизации. По переднему фронту этого импульса информация с группы 13 входов записывается в буферный ре гистр 39 блока 3 формирования информации. Одновременно импульс разрешения записи поступает на первьй вход записи блока 4 и устанавливает триггер 41 в единичное состояние. Сигнал 1 с выхода триггера 41 через выход запуска блока 4 поступает на один из входов элементов И 22 и 23 и через элемент ИЛИ 10 на элемент И 33 блока 2, подготавливая их к проггусканию на выход сигнала на втором входе. На управляющем входе дешифратора 7 присутствует нулевой сигнал с первого информационного вькода блока 3, которьй разрешает прохождение преобразо-. ванного кода значения дискретности с выхода дешифратора 7 на первьп информационный вход блока 5 управления, который записывается в регистр 46 заявки (в одном из разрядов, соответствующем данной дискретности этого разряда, появляется 1).

Первый тактовый импульс с выхода 25 через элемент К 22 и мультиплексор 8 считывает информационное слово из ячейки нулевого адреса блока 1 и переписывает его в буферный регистр 29 Информация признака занятости ячейки поступает на информационный вход триггера 42 блока 4 и по заднему фронту первого тактового импульса записывается в триггер 42-. Так как данная ячейка свободна, то триггер 42 устанавливается в единичное состояние.

При действии второго тактового импульса с выхода 26 элемент И 43 блока 4, на двух входах которого присутствуют единичные сигналы, пропускает его через коммутатор 40 на вход разрешения записи блока 1 памлти. Передний фронт этого импульса записывает- в нулевой адрес блока 1 памяти слово с информационных выходов блока 3 формирования информации (с выхода регистра 39) . Задний второго тактового импульса устанавливает в нулевое состояние триггер 41 блока 4 и через его выход запуска обнуляет счетчик 31 блока 2 формирования адреса. Нулевой сигнал на выходе запуска блока 4 (выход триггера 41) запрещает прохождение сигнала элемента И 23 и через элемент ИЛИ 10 запрещает прохождение импульсов первого тактового выхода 25 блока 6 . через элементы И 22 и 33.

Третий тактовый импульс с выхода 27 устанавливает триггер 42 блока 4 в нулевое состояние. Цикл записи установленной процессором информации в свободную ячейку закончен.

Для записи следующего слова про- .цессор, не изменяя состояния по группе 14 входов задания режима таймера, выставляет по группе 13 входов требуемое слово и в момент действия первого тактового импульса с выхода 25 вырабатывает на входе 16 разр ешения записи таймера импульс записи, по которому в регистр 39 блока 3 данная информация записывается и через коммутатор 37 поступает на информационные входы блока 1 памяти и дешифратора 7. Одновременно импульс записи устанавливает на выходе запуска блока 4 (триггер 41 приведен в циничное состояние) сигнал 1, разрешающий работу блока 2 формирования адреса и элемента И 22.

Третий тактовый им 27 сбрасывает триггер нулевое состояние. Ци информации закончен, вом адресах блока 1 п

О на первом информационном выхо- д требуемая информация.

де блока 3 формирования информации разрешает работу дешифратора 7, с выхода которого в регистр 46 блока 5 управления записывается величина дискретности данного слова (на соответствующем вьпсоде регистра 46 появляется или подтверждается 1).

Первый тактовьй импульс с выхода

25через элемент И 22 и мультиплек- .сор 8 считывает из нулевого адреса,

установленного блоком 2, информационное слово, где присутствует О - признак занятости данной ячейки. С первого информационного выхода блока 1 памяти О поступает на информа- ;ционный вход триггера 42 и по задне- ;му фронту первого импульса подтверждает его нулевое состояние.

Второй тактовый импульс с выхода

26не проходит через элемент И 43, блок 4 не вырабатывает импульса записи на-своем выходе.

Третий тактовьй импульс с выхода

27через элемент И 33 блока 2 поступает на счетньй вход счетчика 31, увеличивает его содержимое на единицу, и блок 2 формирования адреса выставляет на адресный вход блока 1 памяти новый адрес (в данном случае первый). Следующий первый тактовьй

;импульс с выхода 25 считывает из первого адреса блока t памяти информационное слово, которое содержит 1 - признак незанятости ячейки. Этот единичный сигнал с первого информационного выхода блока 1 по заднему фронту импульса с выхода 25 записьшается в триггер 42 блока 4, и при появлении второго тактового импульса с выхода 26 блок 4 вырабатывает на своем выходе импульса записи сигнал, по которому в первый адрес блока 1 памяти записывается информация с выходов блока 3.

По заднему фронту тактового импульса с выхода 26 на выходе запуска блока 4 исчезает сигнал (триггер 41 устанавливается в нулевое состояние) и вырабатывается импульс на его вы20

25

30

10

В случае, если в N

записана нулевая инфо писи процессором (N+1 4 формирования импуль 15 батывает сигнал запус счетчик 31 блока 2 фо са начинает считать и да 27, последовательн , самым все адреса, из дому импульсу с выход тываться информация. вом информационном вы время присутствует О вырабатывает импульсо са адреса, и счетчик пульс переполнения. Ч задержки счетчик 31 у в исходное нулевое со налу на выходе 20, ко одним из векторов пре сор переходит на вьшол ствующей программы.

В конце операции з ном режиме работы тай 46 заявки блока 5 упр значения всех дискрет хранятся в блоке 1 пам О в поле признака ки, а в поле интервал ячеек записан интервал версном коде, которьй работать данному реле

После этого таймер операцию отсчета зада времени. По группе 14 режима таймера устана по которому коммутатор подключает выходы сче ресному входу блока 1 татор 37 блока 3 подс сумматора 36 и элемен мационньгм входам блок шифратора 7, коммутат подсоединяет выход ра блока 5 управления к решения записи блока блокируется тригг ер 5 ления, мультиплексор выход элемента И 22 к

35

40

45

50

55

ходе сброса, устанавливающий счетчик 31 блока 2 формирования адреса в нулевое состояние.

Третий тактовый импульс с выхода 27 сбрасывает триггер 42 блока 4 в нулевое состояние. Цикл записи новой информации закончен, в нулевом и первом адресах блока 1 памяти записана

требуемая информация.

требуемая информация.

В случае, если в N адресах блока 1

записана нулевая информация, при записи процессором (N+1)-ro слова блок;: 4 формирования импульса записи выра- батывает сигнал запуска, по которому счетчик 31 блока 2 формирования адреса начинает считать импульсы с выхода 27, последовательно изменяя тем самым все адреса, из которых по каж-. дому импульсу с выхода 26 будет считываться информация. Так как на первом информационном выходе блока 1 все время присутствует О, то блок 4 не вырабатывает импульсов записи и сброса адреса, и счетчик 31 вьщает им- пульс переполнения. Через элемент 34 задержки счетчик 31 устанавливается в исходное нулевое состояние. По сигналу на выходе 20, которьй является одним из векторов прерывания, процес- сор переходит на вьшолнение соответствующей программы.

В конце операции записи в автономном режиме работы таймера в регистре 46 заявки блока 5 управления записаны значения всех дискретностей, которые хранятся в блоке 1 памяти, содержащих О в поле признака занятости ячейки, а в поле интервала времени этих ячеек записан интервал времени в инверсном коде, которьй необходимо отработать данному реле.

После этого таймер осзтдествляет операцию отсчета заданных интервалов времени. По группе 14 входов задания режима таймера устанавливается сигнал по которому коммутатор 32 блока 2 подключает выходы счетчика 31 к адресному входу блока 1 памяти, коммутатор 37 блока 3 подсоединяет выходы сумматора 36 и элемента И 38 к инфор- мационньгм входам блока 1 памяти и дешифратора 7, коммутатор 40 блока 4 подсоединяет выход разрешения записи блока 5 управления к входу блока разрешения записи блока 1 памяти, раз- блокируется тригг ер 50 блока 5 управления, мультиплексор 8 подключает выход элемента И 22 к входу разреше

ния чтения блока 1 памяти. В этот момент времени на всех выходах блока

4формирования импульса записи установлен О, на выходе запуска блока

5управления (выход триггера 50 - сигнал О, импульсы на выходе элемента И 22 отсутствуют, импульсы на счетном входе счетчика 31 отсутствуют, на адресном входе блока 1 памяти Q стоит код нулевого адреса.

Блок 6 синхронизации циклически вырабатывает сигналы, соответствующие текущей дискретности времени, которые с его выхода дискретов записы- 15

ваются в регистр 47 блока 5 управления. Элемент 48 сравнения поразрядно сравнивает заявленные дискретности

(информацию регистра 46) с текущими (информация регистра 47). При совпа- 20 дении одного или нескольких разрядов узел 18 сравнения вырабатывает сигнал, свидетельствующий о том, что в блоке 1 памяти имеется хотя бы одно слово, в котором записанный интер- 25 вал времени необходимо отсчитывать с текущей дискретностью, и который устанавливает триггер 50 в единичное состояние.

Единичный сигнал с выхода запуска ЗО блока 5 управления (выход триггера

50 поступает на выход 21 запуска таймера и через элемент ИЛИ 10 на один из входов элементов И 22 и 33. Од- новибратор 51 вырабатывает импульс по единичному сигналу триггера 50 и через элемент ИЛИ 52 устанавливает все разряды регистра 46 в О. По первому тактовому импульсу с выхода 25, который поступает через элемент 40 И 22 и мультиплексор 8 на вход разрешения чтения блока 1 памяти, из ячейки нулевого адреса считывается информационное слово, которое посту35

пает на первьш и второй информацион- 5 т вход разрешения записи блока 1 и ные входы блока 3 формирования инфор- в адрес, установленный на адресных

мации. 1 на выходе 21 запуска свидетельствует о том, что таймер выполняет операцию счета и запись со стороны процессора не разрешается.

Код длительности интервала времени поступает в сумматор 36, который увеличивает его на единицу и передает на входы элемента И 38 и соответствующие разряды первого входа коммутатора 40. Если на выходе сумматора 36 хотя бы в одном разряде присутствует О, то на первом информационном выходе блока 3 (на выходе

50

55

входах блока 1 памяти, записывается новое информационное слово с выходов блока 3.

По третьему тактовому импульсу с выхода 27 счетчик 31 блока 2 формирования адреса увеличивает свое- состояние на единицу; и через коммутатор 32 передает сигнал на адресные входы блока 1 памяти.

Следующий импульс с выхода 25 через элемент И 22 и мультиплексор 8 считывает по новому установленному адресу информационное слово и изме

5

О

0

5

элемента И 38) устанавливается О, который свидетельствует о том, что данньш интервал еще не отработан. В случае, если на всех разрядах сумматора 36 присутствует 1, элемент И 38 вырабатывает 1, поступающую через коммутатор 37 на первый информационный выход.

При сигнале на стробирующем входе дешифратора 7, равном нулю (случай, когда время не отработано), дешифратор 7 пропускает позиционный код дискретности (единица в том разряде, который соответствует заданной дискретности) на вход регистра 46 и один, из входов узла 48 сравнения блока 5 управления. В регистр 46 записывается код дискретности данного слова, а узел 48 сравнивает значения текущей дискретности на выходе регистра 47 и дискретности данного слова на первом информационном входе блока 5 управления.

Пулевой сигнал с выхода записи блока 5 поступает на второй вход разрешения записи блока 4 (на третий вход коммутатора 40) и через него на вход разрешения записи блока 1 памяти. Запись информационного слова с входов блока 3 формирования информации не происходит, и информация в данной ячейке блока 1 памяти не изменяется.

В случае, если единице на первом информационном входе блока 5 управления в разряде, соответствующем значению дискретности считанного слова, в аналогичном разряде регистра 47 соответствует 1, узел 48 сравнения вырабатывает единичный сигнал на выход записи блока 5 управления. Этот единичный сигнал через блок 4 формирования импульса записи лоступа0

5

входах блока 1 памяти, записывается новое информационное слово с выходов блока 3.

По третьему тактовому импульсу с выхода 27 счетчик 31 блока 2 формирования адреса увеличивает свое- состояние на единицу; и через коммутатор 32 передает сигнал на адресные входы блока 1 памяти.

Следующий импульс с выхода 25 через элемент И 22 и мультиплексор 8 считывает по новому установленному адресу информационное слово и изменяет его, если необходимо, как описано.

Блок 2 формирования адреса периодически по такту выхода 27 увеличивает адрес блока 1 памяти, из которого по такту выхода 25 считывается информация, и в зависимости от требуемой дискретности отсчета времени в данном слове и текущей дискретности блок 5 управления (узел 48 сравнения) вырабатывает импульс разрешения записи новой информации в блок 1 памяти по текущему адресу, при наличии О на первом информационном выходе блока 3 с выхода дешифратора 7 в регистр 46 заявки блока 5 управления записывается значение дискретности данного слова. При переполне- НИИ счетчика 31 блока 2 формирования адреса импульс с выхода переполнения адреса через второй вход начальной установки устанавливает в исходное состояние блок 5, сбрасывает регистр 47 и триггер 50 в нулевое состояние, запрещая тем самым прохождение импульса с выхода 27 на счетньй вход счетчика 31 блока 2 формирования адреса и импульса с выхода 25 на вход разрешения чтения блока 1 памяти. Одновременно через элемент 34 задержки импульсом переполнения счетчик 31 сбрасывается в нулевое состояние .

Таким образом, к моменту переполнения счетчика после опроса всех адресов ячеек блока 1 памяти в регистре 46 блока 5 управления записаны величины дискретов, с которыми необходимо отработать каждый интервал времени (не отработанный к данному моменту времени), записанный в запоминающее устройство блока 1 памяти, регистр 47 установлен в нулевое состояние и готов к приему сигналов с выходов блока 6 синхронизации.

При отработке временного интервал одним из реле времени в информационном слове, считанном из определенной ячейки блока 1 памяти, длительность интервала времени во всех разрядах, кроме младшего, содержит 1. Сумматор 36 блока 3 увеличивает код на единицу и на его выходе во всех разрядах присутствуют 1, которые поступают на вход элемента И 38. 1 с выхода элемента И 38 через коммутатор 37 поступает на управляющий вход дешифратора 7 и устанавливает на его

выходе все О (т.е. содержимое регистра 46 блока 5 не изменяется), и на один из входов элемента И 9, на втором входе которого присутствует 1 с первого информационного выхода блока 1 памяти (признак занятости ячейки).

Элемент И 9 вьфабатывает сигнал 1, поступающий на стробирующий выход 19 таймера и управляющий вход магистрального усилителя 24, который пропускает с третьего информационно- го выхода блока 1 памяти код номера отработанного реле времени на группе 18 информационных выходов таймера. В ячейку, из которой считалось отработанное реле времени, записыва- ется с выходов блока 3 слово, т.е. признак того, что данная ячейка сво-i бодна и в нее можно записывать следующую информацию (новое реле времени) .

Операция записи информации про- цессором в блок 1 памяти таймера в автономном режиме производится в те моменты времени, когда на выходе 21 запуска таймера присутствует О, т.е. когда нет сравнения разрядов регистров 46 и 47 блока 5 управления. Это позволяет оперативно вводить параметры новых реле времени взамен отработавших, не прерывая операций отсчета времени, имеющихся в блоке 1 памяти.

Формула изобретения

1. Таймер, содержащий блок памяти, дешифратор и элемент И, отличающийся тем, что, с целью расширения функциональных возможностей за счет повьш1ения точности отсчета временных интервалов, в него вве- дены блок формирования адреса, блок формирования информации, блок формирования импульса записи, блок синхронизации, блок управления, два магистральных усилителя и мультиплек- сор, причем первый выход блока памяти соединен с входом разрешения работы блока формирования импульса записи, с первым входом первого элемента и с первым информационным входом первого магистрального усилителя, первая группа выходов блока памяти оединена с первой группой информационных входов первого магистрального усилителя и с первой группой информаujioHHbix входов блока формирования информации, вторая группа выходов блока памяти соединена с второй группой информа1дионных входов первого магистрального усилителя, с второй группой информационных входов блока .формирования информации и с группой информационных входов второго магистрального усилителя, группа выходов которого является группой информа- ционных выходов таймеров, выход первого элемента И соединен с управляю- ntHM входом второго магистрального у силителя и является выходом строба т;аймера, первьй выход блока формирования информации соединен со строби- рующим входом дешифратора, с вторым бходом первого элемента И и- с инфорг ационным входом блока памяти, первая 20 динен с вторым входом разрешения за

г руппа информационных выходов блока формирования информации соединена с группой информационных входов дешифратора и с первой группой информационных входов блока памяти, вторая Группа информационных выходов блока формирования информации соединена с Второй группой информационных входов блока памяти, группа выходов первого магистрального усилителя соединена с третьей группой информационных входов блока формирования информации и Является группой входов-выходов временных интервалов таймера, вход разрешения записи таймера соединен с входом разрешения записи блока формирования информации и с первым входом разрешения записи блока формирования импульса, записи, группа входов задания режима таймера соединена с группой управляющих входов блока формирования и тульсов записи, с группой управляющих входов блока формирования Адреса, с группой управляюш1-1х входов

блока управления, с группой управляю- 45 является выходом занятости таймера, щих входов блока формирования инфор- информационньш выход блока формирои

мации и с группой управляюгцих входов мультиплексора, выход которого соединен с входом разрешения чтения блока памяти, вход разрешения чтения таймера соединен с управляюпщм входом первого магистрального усилителя и с первым информационным входом мультиплексора, второй информационньш вход которого соединен с выходом второго элемента И, выход разрешения записи блока формирования импульса записи соединен с входом разрешения записи блока памяти, группа адресных

50

55

вания импульса записи соединен с информационным вхйдом блока формирования адреса, причем блок управления содержит триггер, одновибратор, два элемента ИЛИ, два регистра, два бло ка сравнения, группа yпpaвляющ x вх дов блока управления соединена с группой входов первого элемента ИЖ первый вход которого соединен с пер вым входом второго э.пемента ИЛИ и является первьм входом начальной ус тановки блока управления, второй вход начальной установки которого

входов которого соединена с группой выходов блока формирования адреса, группа информационных входов которого является группой адресных входов таймера, вход начальной установки таймера соединен с входом начальной установки блока формирования адреса, с входом начальной установки блока формирования импульса записи и с первым входом начальной установки блока управления, вход запуска блока формирования адреса соединен с выходом элемента ИЛИ и с первым входом второго элемента И, выход блока формирования адреса соединен с первым входом третьего элемента И и вторым входом начальной установки блока уп- равления, первьй выход которого сое0

5

5

0

писи блока формирования импульса записи, второй выход блока управления соединен с первым входом элемента ИЛИ и является .выходом флага таймера, группа выходов дешифратора соединена с группой адресных входов блока управления , группа тактовых входов которого соединена с первой группой выходов блока синхронизации, первый выход второй группы которого соединен с первьм тактовым входом блока формирования -импульса записи, с вторым входом второго элемента И, второй выход второй группы блока синхронизации соединен с вторьп тактовым входом блока формирования импульсе, записи, третий выход второй группы блока синхронизации соединен с тактовым входом блока формирования адреса и с третьим тактовым входом- блока формирования импульса, записи, выход запуска которого соединен с вторым входом элемента ИПИ и с вторым входом третьего элемента И, выход которого

0

5

вания импульса записи соединен с информационным вхйдом блока формирования адреса, причем блок управления содержит триггер, одновибратор, два элемента ИЛИ, два регистра, два блока сравнения, группа yпpaвляющ x входов блока управления соединена с группой входов первого элемента ИЖ, первый вход которого соединен с первым входом второго э.пемента ИЛИ и является первьм входом начальной установки блока управления, второй вход начальной установки которого

oeflMffeH с вторым входом первого элеента ИЛИ и с входом разрешения записи первого регистра, группа информационных входов которого является . группой тактовых входов блока управения, группа выходов первого региста соединена с первой группой входов первого блока сравнения и с первой группой входов второго блока сравнения, вторая группа входов которого соединена с группой выходов второго регистра, вход разрешения записи которого соединен с выходом второго элемента ИЛИ, группа адресных входов блока управления соединена с группой

нформационных входов второго регистра и с второй группой входов первого блока сравнения, выход равенства первого блока сравнения является вторым выходом блока управления, выход равенства второго блока сравнения соединен с единичным входом триггера, выход которого соединен с входом од- новибратора, выход которого соединен с вторым входом второго элемента ИЛИ, блок формирования адреса содерит счетчик, элемент И, элемент ИЛИ, элемент задержки и коммутатор, причем тактовый вход блока формирования соединен с первым входом элемента И, второй вход которого является входом запуска блока формирования адреса, выход элемента И соединен с синхро- входом счетчика, счетный вход которого является информационным входом блока формирования адреса, группа выходов разрядов счетчика соединена с первой группой информационных вхоов коммутатора, вторая группа входов которого является группой адресных входов блока формирования адреса, группа управляющих входов блока формирования адреса соединена с группой управляющих входов коммутатора, группа выходов которого является группой информационных выходов блока формирования адреса, вход начальной установки блока соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом элемента задержки, выход элемента ИЛИ соединен с входом сброса счетчика, выход переполнения которого соединен с входом элемента задержки и является выходом переполнения счетчика, блок формирования нформации содержит регистр, элемент И, сумматор и коммутатор, причем вход разрешения записи блока формиро

вания информации соединен с входом разрешения записи регистра, первая группа информационных входов блока формирования информации соединена с группой входов сумматора и с первой группой информационных входов коммутатора, вторая группа информационных входов блока формирования информации

соединена с второй группой информационных входов коммутатора, выходы сумматора соединены с соответствующими входами элементов И и с третьей группой информационных входов коммутатора, выход элемент.а И соединен с информационным входом коммутатора, третья группа информационных входов блока формирования информации соеди- нена с группой информационных входов

регистра, группа выходов регистра соединена с четвертой группой информационных входов коммутатора, выход коммутатора является первым выходом блока формирования информации, первая и вторая группа выходов коммутатора являются соответственно первой и второй группами выходов формирования информации, вход сумматора соединен с шиной единичного потенциала

таймера, управляющие входы коммутатора соединены с группой управляющих входов блока формирования информации.

2. Таймер поп,1, отлича ющ и и с я тем, что блок формирования импульса записи содержит два триггера, элемент ИЛИ, элемент НЕ, коммутатор, причем вход начальной установки блока соединен с первым

входом элемента РШИ, первый вход

группы управляющих входов блока соединен с вторым входом элемента ИЛИ, входы с второго по п-й группы управляющих входов блока соединены с

группой управляющих входов коммутато-- ра, вход разрешения записи блока соединен с входом элемента НЕ и с единичным входом первого триггера, нулевой вход которого соединен с выходом

элемента ИЛИ, выход элемента НЕ соединен с первым информационным входом .коммутатора, второй информационный вход которого соединен с выходом элемента И и с третьим входом элемента

ИЛИ, выход первого триггера соединен с первым входом эдемента И и является выходом запуска блока, первый тактовый вход блока соединен с син- хровходом второго триггера, второй

тактовый вход блока соединен с вто- pbiM входом элемента И, третий такто- Вьй вход блока соединен с нулевым входом второго триггера, информационный вход которого является ззходом разрешения работы блока, выход второго триггера соединен с третьим входом элемента И, выход коммутатора является выходом разрешения записи блока, третий информационный вход коммутатора является вторым входом раз- р ешения записи блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2024920C1 |

| Устройство для сопряжения цифровых вычислительных машин с каналами связи | 1985 |

|

SU1287171A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Генератор псевдослучайных сигналов | 1986 |

|

SU1347166A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Устройство контролируемого пункта | 1983 |

|

SU1211784A1 |

| Устройство для отсчета времени | 1990 |

|

SU1817085A1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2079165C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для реализации программ управления несколькими объектами и технологическими процессами, требунщих различных временных задержек выдачи и снятия управляющих сигналов и команд. Особенностью являет(Л со СП о 00 со

сриг.2

15

фиг.З

74fi

16

13

39

J7

сриг.

25 26 21

Составитель Н, Торопова Редактор О. Юрковецкая Техред А.Кравчук Корректор М. Максимишинец

Заказ 5999/49 Тираж 671

ВНИИГШ Государственного комитета СССР

по делам изобретений .и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно

-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

(иг.6

фиг л

Подписное

| Таймер | 1981 |

|

SU1038931A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Программно-временное устройство | 1981 |

|

SU1003025A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-12-07—Публикация

1985-04-01—Подача