f

Изобретение относится к радиотехнике и может (5ыть использовано в устройствах для формирования и обработки сигналов, при построении автоматических корреляторов и устройств для вычисления свертки функций.

Целью изобретения является расширение области применения аналогоцифрового устройства задержки за счет возможности получения плавной перестройки времени задержки по закону, близкому к линейному, и возможности изменения скорости перестройки времени задержки.

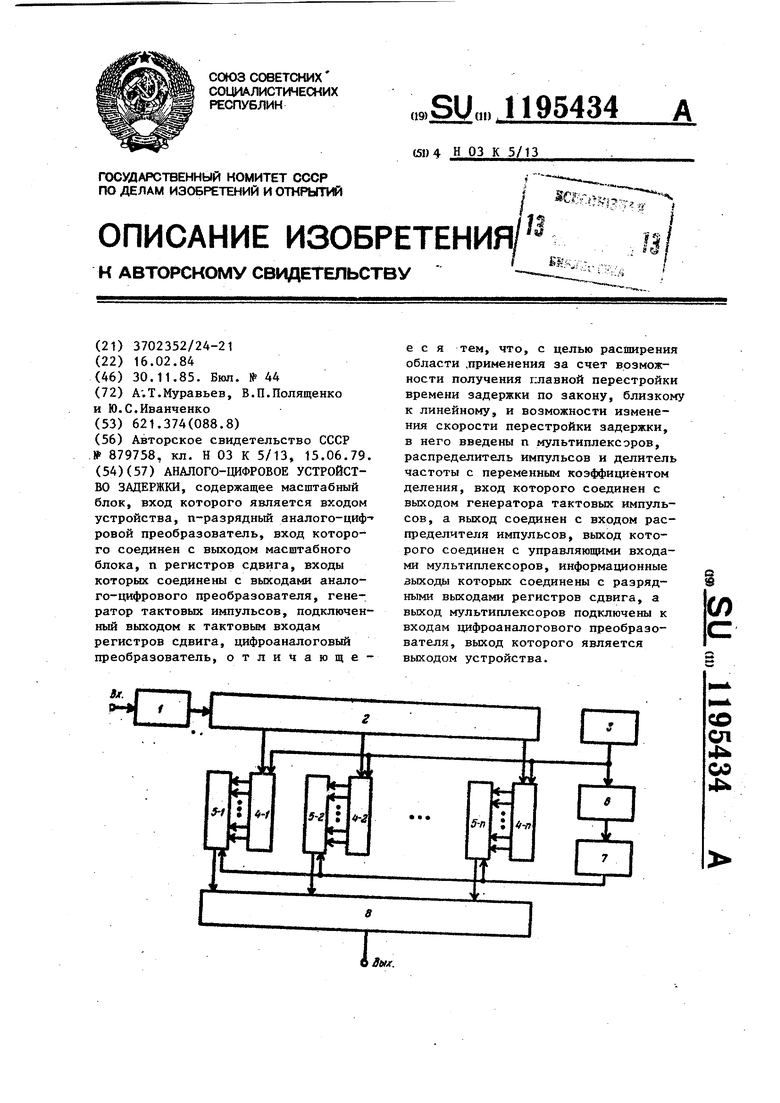

На чертеже представлена структурная схема аналого-цифрового устройства задержки.

Аналого-цифровое устройство задержки содержит масштабный блок 1, аналого-цифровой преобразователь (АЦП) 2, генератор 3 тактовых импульсов (ГТИ), п регистров 4-1-4-п сдвига, п мультиплексоров 5-1-5-п, делитель 6 частоты с переменным коэффициентом деления (ДПКД), распределитель 7 импульсов и цифроаналоговый преобразователь (ЦАП) 8.

Вход масштабного блока 1 является входом устройства, а его выход подключен к входу АЦП 2. Выходы АЦП подключены к входам регистров 4-1-4-п сдвига, тактовые входы которых соединены с выходом тактового генератора 3, а разрядные выходы с информационными входами мультиплесоров 5-1-5-п. Вход ДПКДб подключен к выходу тактового генератора 3, а выход - к входу распределителя 7 импульсов, вьпсоды которого соединены с управляющими входами мультиплексоров 5-1-5-п. Выходы мультиплексоров 5-1-5-п подключены к входам ЦАП 8, выход которого является выходом устройства.

, Масштабный блок 1 представляет собой усилитель с автоматической регулировкой усиления, в качестве которого можно гспользовать например микросхемы 235 УРЗ и 235 УР9. -I,

АЦП 2 представляет собой типовой блок и может быть выполнен например на интегральной микросхеме К 572 ПВ 1А-В,

Генератор 3 тактовых импульсов выполнен по схеме автоколебательного мультивибратора с кварцевой ста54342

билизацией частоты на микросхеме

155 ЛАЗ.

ДПКД 6 выполнен на микросхеме 155 ЛЕВ, коэффициент деления может

5 устанавливаться например, вручную при помощи переключателей.

ЦАП 8 выполнен на микросхеме К 575 ПА1А.

Мультиплексор 5 также может предto ставлять собой типовой блок, например, на интегральной микросхеме 155КП5.

Распределитель 7 импульсов может быть вьшолнен, например, в виде

15 двоичного счетчика, разрядные выходы которого подключены к управляющим входам мультиплексоров 5-1-5-п. Аналого-цифровое устройство задержки работает следукицим образом.

20 Исследуемый аналоговый сигнал, подлежащий задержке, поступает на масштабный блок 1, где он усиливается по амплитуде и подается на вход АЦП 2, который преобразует аналоговый

25 сигнал в разрядный цифровой сигнал, представленньй в параллельном коде. Далее цифровой сигнал с выходов АЦП 2 подается на входы регистров 4-1-4-п сдвига, где происходит

2д временная задержка исследуемого сигнала за счет его записи и сдвига , в разрядах регистров 4-1-4-п с помощью импульсов, поступающих от генератора 3 тактовых импульсов.

Величина задержки в каждый момент времени определяется номером разрядов регистров, с которого производится считывание информации и который, в свою очередь, соответствует коду, поступающему на управляющие входы мультиплексоров 5-1-5-п с выхода распределителя 7 импульсов. При поступлении импульсов на вход распределителя 7 импульсов с ДПКД .6 изменяется состояние сигналов на его выходах и соответственно на управлянщих входах мультиплексоров 5-1-5-п. Вр,/.мя задержки при этом изменяется дискретно, величина дискрета задержки определяется временем задержки одного разряда регистра. Время перестройки линии задержки от О до ti..(Kc определяется коэффициентом деления ДКДЦ 6. Изменение времени задержки аппроксимируется при этом линейным законом.

При необходимости время задержки такого устройства можно изменять по произвольному закону, который

3 11954344

задается распределителем 7 импуль-няться в широких пределах с посов, в качестве которого может бытьмощью изменения коэффициента деиспользована жесткая логика, ЦВМ илиления ДПКД 6. С выходов, мульклавишное наборное поле. Скоростьтиплексоров 5- 1- 5 - п задерперестройки времени задержки опре-5 жанкый цифровой сигнал поступает

деляется частотой следования импуль-на входы ЦАП 8, с выхода косов, подаваемых на вход распреде-торого снимается задержанный аналителя 7 импульсов, и может изме-логовый сигнал.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЛЕДЯЩАЯ ЛИНИЯ ЗАДЕРЖКИ | 1993 |

|

RU2085026C1 |

| Цифровой фазовращатель | 2024 |

|

RU2823429C1 |

| УПРАВЛЯЕМАЯ ЛИНИЯ ЗАДЕРЖКИ | 2011 |

|

RU2450432C1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Устройство для задержки прямоугольных импульсов переменной амплитуды | 1986 |

|

SU1370749A1 |

| Аналого-цифровое вычислительное устройство | 1987 |

|

SU1425725A2 |

| Синтезатор частот | 1984 |

|

SU1293841A1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2009 |

|

RU2396721C1 |

| Устройство формирования систем двукратных производных кодовых дискретно-частотных сигналов | 2016 |

|

RU2626331C1 |

| Функциональный преобразователь многих переменных | 1990 |

|

SU1742836A1 |

АНАЛОГО-ЦИФРОВОЕ УСТРОЙСТВО ЗАДЕРЖКИ, содержащее масштабный блок, вход которого является входом устройства, п-разрядный аналого-цифровой преобразователь, вход которо го соединен с выходом масштабного блока, п регистров сдвига, входы которых соединены с выходами аналого-цифрового преобразователя, генератор тактовых импульсов, подключенный выходом к тактовым входам регистров сдвига, цифроаналоговый преобразователь, отличающееся тем, что, с целью расширения области .применения за счет возможности получения плавной перестройки времени задержки по закону, близкому к линейному, и возможности изменения скорости перестройки задержки, в него введены п мультиплексоров, распределитель импульсов и делитель частоты с переменным коэффициентом деления, вход которого соединен с выходом генератора тактовых импульсов, а выход соединен с входом распределителя импульсов, выход которого соединен с управляющими входами мультиплексоров, информационные выходы которых соединены с разрядными вькодами регистров сдвига, а л выход мультиплексоров подключены к входам цифроаналогового преобразователя, выход которого является выходом устройства. СО сд 4 00 4

| Дискретно-аналоговое устройство задержки | 1979 |

|

SU879758A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-11-30—Публикация

1984-02-16—Подача