(54) ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частот | 1983 |

|

SU1190457A1 |

| Цифровой синтезатор частот | 1979 |

|

SU813677A1 |

| Цифровой синтезатор частот | 1990 |

|

SU1774464A1 |

| Цифровой синтезатор частоты | 1986 |

|

SU1374398A2 |

| Преобразователь кодов | 1978 |

|

SU744548A1 |

| Цифровой синтезатор частот | 1984 |

|

SU1210198A1 |

| Цифровой синтезатор частот | 1989 |

|

SU1691926A1 |

| Цифровой генератор периодических функций | 1987 |

|

SU1441372A1 |

| Цифровой линеаризатор | 1982 |

|

SU1056453A1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

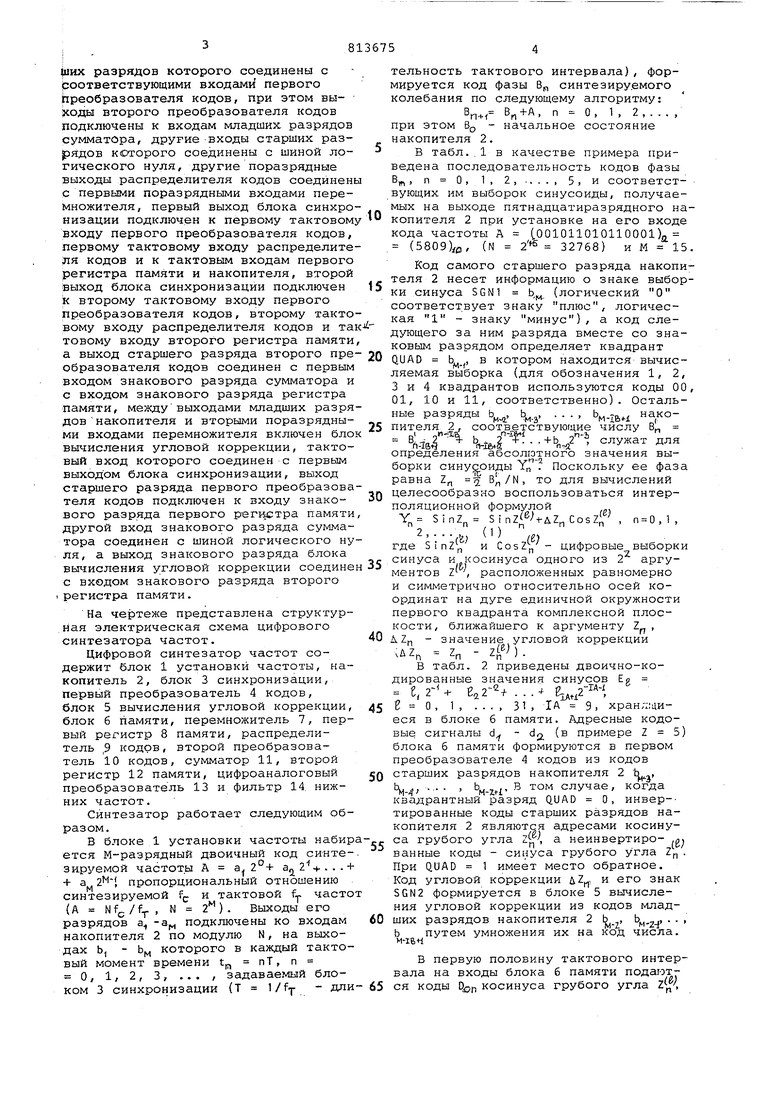

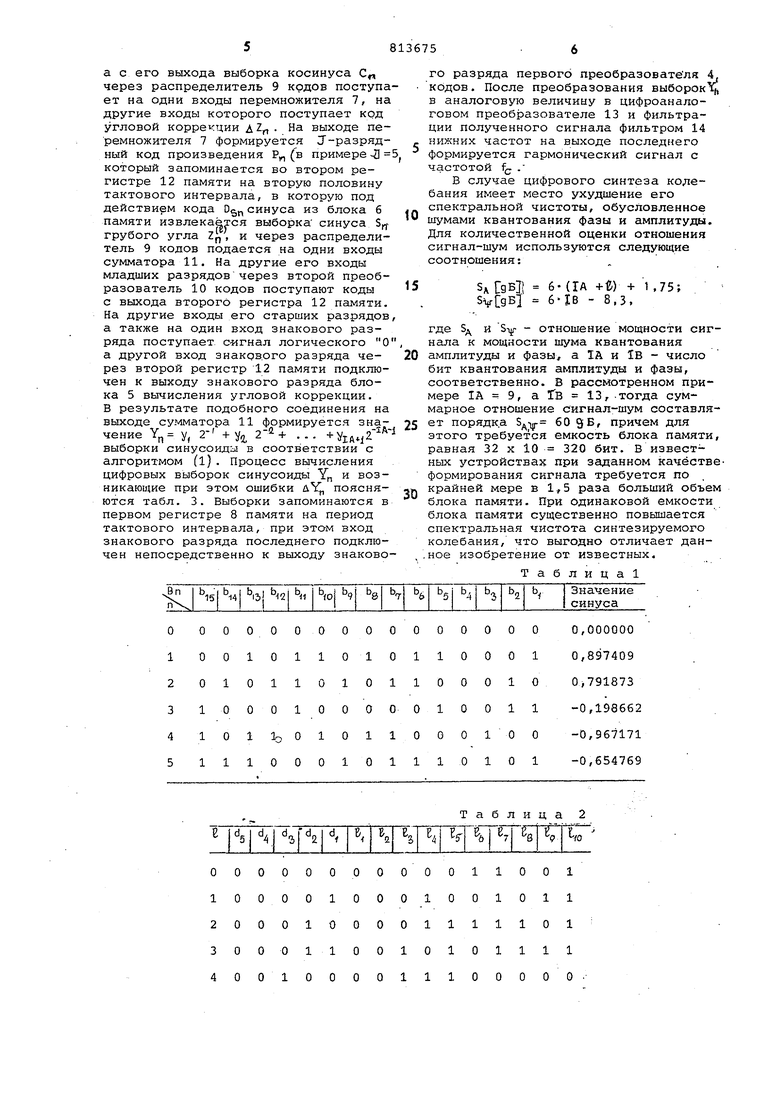

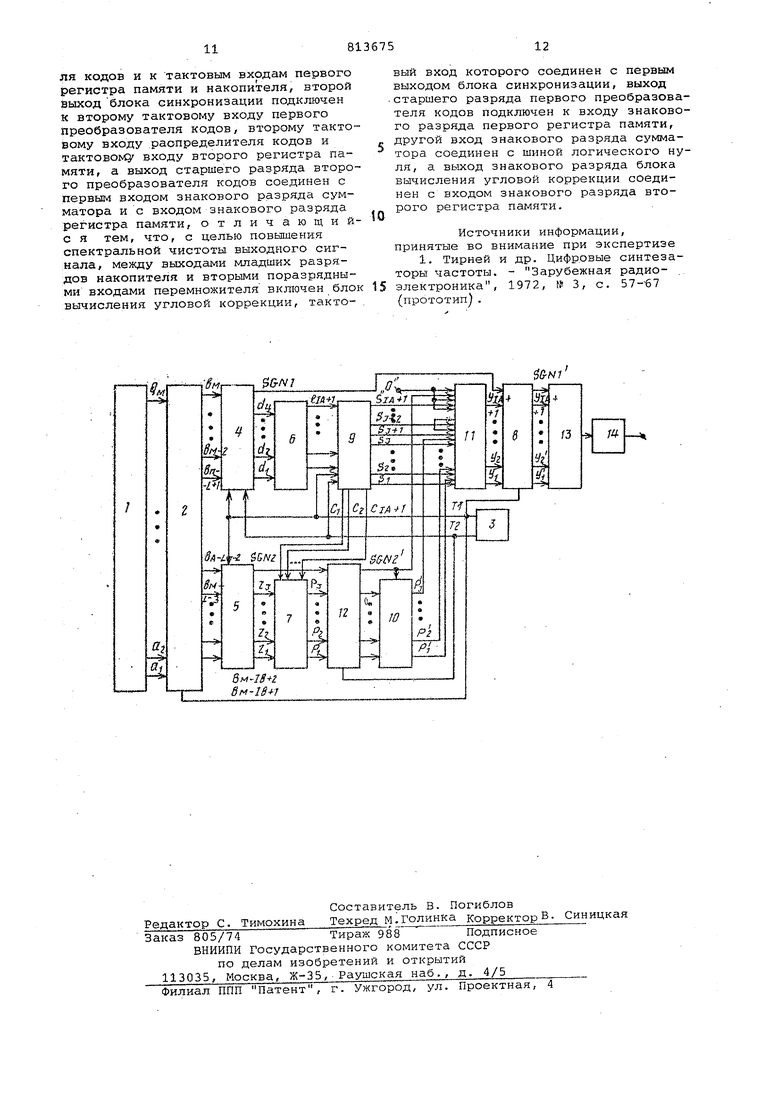

Изобретение относится к радиотехнике и может использоваться в ка- честве источника стабильных частот. Известен цифровой синтезатор частот, содержащий последовательно соединенные первый преобразователь кодов, блок памяти, распределитель кодов, сумматор, первый регистр памяти цифроаналоговый преобразователь к фильтр нижних частот, а также последовательно соединенныео перемножитель второй регистр памяти и второй преобразователь кодов, блок синхронизации и последовательно сбединеняые блок установки частоты и накопитель, выходы старших разрядов которого соединены с соответствующими входами первого преобразователя кодов, при этом выходы второго преобразователя кодов подключены к входам младших разрядов сумматора, другие входы старших разрясдов которого соединены- с шиной логического нуля, другие поразрядные выходы распределителя кодов соединены с первыми поразрядными входами пере множителя, первый выход блока синхронизации подключен к.первому тактовому входу первого преобразователя кодов, первому тактовому входу распределителя кодов и к тактовым входам первого регистра памяти и накопителя, второй выход блока синхронизации подключен к второму тактовому входу первого преобразователя кодов, второму тактовому входу распределителя кодов и тактовому входу второго регистра памяти , а выход старшего разряда второго преобразователя кодов соединен с первым входом знакового разряда с мматора и с входом знакового разряда регистра памяти . Однако такой синтезатор не обеспечивает достаточной спектральной чистоты выходного сигнала. Цель изобретения -« повьоиение спектральной чистоты выходного сигнала. Для достижения этой цели в цифровом синтезаторе частот, содержащем последовательно соединенные первый преобразователь кодов, блок памяти, распределитель кодов, сумматор, первый регистр памяти, дифроаналоговый преобразователь и фильтр нижних частот, а также последовательно соединенные перемножитель,, второй регистр памяти и второй .преобразователь кодов, блок синхронизации и последовательно соединенные блок установки частоты и накопитель, выходы-стар-. iuHX разрядов которого соединены с Соответствующими входами первого Преобразователя кодов, при этом выходы второго преобразователя кодов подключены к входам младших разрядов сумматора, другие входы старших разря:дов которого соединены с шиной логического нуля, другие поразрядные выходы распределителя кодов соединен с первыми поразрядными входами перемножителя, первый выход блока синхро низации подключен к первому тактовом входу первого преобразователя кодов, первому тактовому входу распределите ля кодов и к тактовым входам первого регистра памяти и накопителя, второй выход блока синхронизации подключен к второму тактовому входу первого преобразователя кодов, второму такто вому входу распределителя кодов и та товому входу второго регистра памяти а выход старшего разряда второго пре образователя кодов соединен с первым входом знакового разряда сумматора и с входом знакового разряда регистра памяти, мезгоду выходами младших разря дов накопителя и вторыми поразрядными входами перемножителя включен бло вычисления угловой коррекции, тактовый вход которого соединен с первым выходом блока синхронизации, выход старшего разряда первого преобразова теля кодов подключен к входу знакового разряда первого регистра памяти другой вход знакового разряда сумматора соединен с шиной логического ну ля, а выход знакового разряда блока вычисления угловой коррекции соедине с входом знакового разряда второго 1 регистра памяти. На чертеже представлена структурная электрическая схема цифрового синтезатора частот. Цифровой синтезатор частот содержит блок 1 установки частоты, накопитель 2, блок 3 синхронизации, первый преобразователь 4 кодов, блок 5 вычисления угловой коррекции, блок 6 памяти, перемножитель 7, первый регистр 8 памяти, распределитель ,9 кодов, второй преобразователь 10 кодов, сумматор 11, второй регистр 12 памяти, цифроаналоговый преобразователь 13 и фильтр 14. нижних частот. Синтезатор работает следующим образом. В блоке 1 установки частоты набир ется М-разрядный двоичный код синтезкруемой частоты А а,2+.-- + + а пропорциональный отношению синтезируемой fj- и тактовой f часто (А Nfj;/f, N 2). Выходы его разрядов а -а подключены ко входам накопителя 2 по модулю N, на выходах Ь, - Ь которого в каждый тактовый момент времени t, пТ, п О, 1, 2, 3, ... , задаваемый блоком 3 синхронизации (Т 1/fr. Дли тельность тактового интервала), формируется код фазы Вр, синтезируемого колебания по следующему алгоритму: Вп+г п О, 1, 2,. ... при этом BQ - начальное состояние накопителя 2. В табл..1 в качестве примера приведена последовательность кодов фазы В, п 0,1, 2, 5, и соответствующих им выборок синусоиды, получаемых на выходе пятнадцатиразрядного накопителя 2 при установке на его входе кода частоты А (.001011010110001)„ (5809)0, (N 2« 32768) и М 15. Код самого старшего разряда накопителя 2 несет информацию о знаке выборки синуса SGN1 Ь| (логический О соответствует знаку плюс, логическая 1 - знаку минус), а код следующего за ним разряда вместе со знаковым разрядом определяет квадрант QUAD , в котором находится вычисляемая выборка (для обозначения 1, 2, 3 и 4 квадрантов используются коды 00, 01, 10 и 11, соответственно). Остальные разряды Ь Ьмчьн °м-i -э пителя 2, соответствующие числу В„ ll.r Ь.Г1..+Ь,2- служат для определения абсолга тного значения выборки синусоиды ХГ. Поскольку ее фаза равна 2„ :g В„/М, то для вычислений целесообразно воспользоваться интерполяционной формулой Х, SinZ SinZ(,Coszf ,1, где S i nz, и - цифровые выборки .косинуса одного из 2 аргусинуса и косинуса одного из 2 ментов z , расположенных равномерно и симметрично относительно осей координат на дуге единичной окружности первого квадранта комплексной плоскости, ближайшего к аргументу 2, Llf - значение угловой коррекции Л2 п - 4)В табл. 2. приведены двоично-кодированные значения синусов Ео -f - ч- Р f -с,, н- с. -i -f . . . Е О, 1, ..., 31, IA 9, хранящиеся в блоке б памяти. Адресные кодовые сигналы d - dg (в примере Z 5) блока б памяти формируются в первом преобразователе 4 кодов из кодов старших разрядов накопителя 2 t,, Ц., ... . , b.,j.. В том случае, когда квадрантный разряд Q.UAD О, инвер-тированные коды старших разрядов накопителя 2 являются адресами косинуса грубого угла , а неинвертиро- ,g ванные коды - синуса грубого угла Z . При QUAD 1 имеет место обратное. Код угловой коррекции uZ, и его знак SGN2 формируется в блоке 5 вычисления угловой коррекции из кодов младших разрядов накопителя 2 Ь, о.2, Ь путем умножения их на код числа. В первую половину тактового интервала на входы блока 6 памяти подаются коды D.on косинуса грубого угла , а с его выхода выборка косинуса С через распределитель 9 кодов поступа ет на одни входы перемножителя 7, на другие входы которого поступает код угловой коррекции д2,. На выходе перемножителя 7 формируется СГ-разрядный код произведения Р„ (в примере-Л который запоминается во втором регистре 12 памяти на вторую половину тактового интервала, в которую под действием кода синуса из блока б памяти извлекается выборка синуса S, грубого угла Zp, и через распределитель 9 кодов подается на одни входы сумматора 11. На другие его входы младших разрядовчерез второй преобразователь 10 кодов поступают коды с выхода второго регистра 12 памяти. На другие входы его старших разрядов а также на один вход знакового разряда поступает сигнал логического О а другой вход знакового разряда через второй регистр 12 памяти подключен к выходу знакового разряда блока 5 вычисления угловой коррекции. В результате подобного соединения на выходе сумматора 11 формируется значение Y у, 2 + у. 2 + ... + выборки синусоиды в соответствии с алгоритмом (1). Процесс вычисления цифровых выборок синусоиды Yn и возникающие при этом ошибки ui поясняются табл. 3. Выборки запоминаются в первом регистре 8 памяти на период тактового интервала, при этом вход знакового разряда последнего подключен непосредственно к выходу знаково0000000000000010010110101100 20101101011000 31000100000100 4lOlOoOlOllOOOl 51110001011101

000000000011001 000010001001011 000100001111101 000110010101111 001000011100000.

Т а

л и ц а 1

Таблица 2 го разряда первого преобразователя 4, кодов. После преобразования выборок в аналоговую величину в цифроаналоговом преобразователе 13 и фильтрации полученного сигнала фильтром 14 нижних частот на выходе последнего формируется гармонический сигнал с частотой f . В случае цифрового синтеза колебания имеет место ухудшение его спектральной чистоты, обусловленное шумами квантования фазы и амплитуды. Для количественной оценки отношения сигнал-шум используются следующие соотношения: 6- (ГА +t) + 1 ,75; SA СэВЦ svCgB SlB - 8,3, где 5д и SY - отношение мощности сигнала к мощности шума квантования амплитуды и фазы, а lA и 1В - число бит квантования амплитуды и фазы, соответственно. В рассмотренном примере , аГв 13, .тогда суммарное отношение сигнал-шум составляет порядка 60 9Б, причем для этого требуется емкость блока памяти, равная 32 х 10 320 бит. В известных устройствах при заданном качествеформирования сигнала требуется по крайней мере в 1,5 раза больший объем блока памяти. При одинаковой емкости блока памяти существенно повышается спектральная чистота синтезируемого колебания, что выгодно отличает данное изобретение от известных. 000,000000 010,897409 100,791873 11-0,198662 OO-0,967171 01-0,654769

S6N1 0 Dg 00000

dUAD О Og «11111

SGN2 1 uZ -11001

(+ 0,00000OOOODj

8136758

Продолжение табл. 2

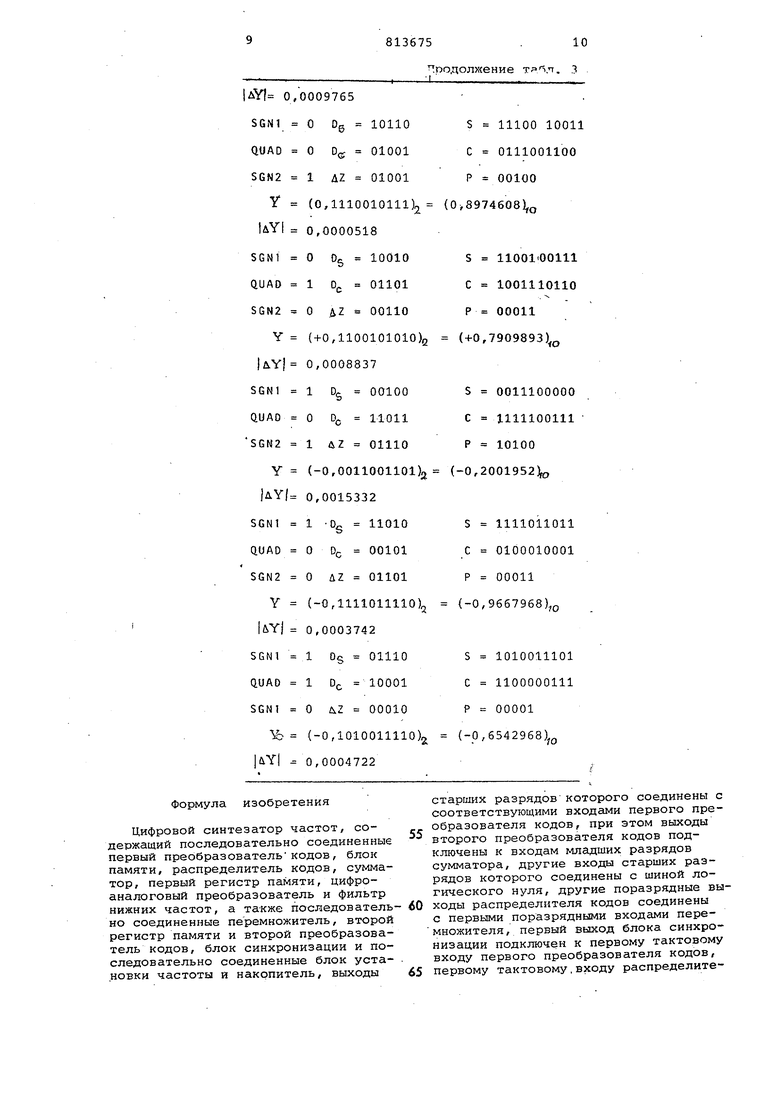

S 00000 11001 с 11111 11111 P 11001 (+0,0009765),o

|ДУ 0,0009765

SGN1 0 Dg 10110S 11100 10011

QUAD 0 DO: 01001С 0111001100

SGN2 1 Д7. 01Q01Р 00100

Y (0,1110010111), {0 8974608),о UYI 0,0000518

SGN1 0 Og 10010S llOOliOOlll

QUAD 1 Og 01101С 1001110110

SGN2 О Д2 00110Р 00011

Y (+0,1100101010)2 (+0,7909893)0 UY| 0,0008837

SGN1 1 Dg 00100S 0011100000

QUAD 0 DC 11011С 1111100111SGK2 1 uZ OHIOP 10100

Y (-0,0011001101)3 (-0,2001952) |дУ( 0,0015332

SGNl 1 -02 11010S 1111011011

QUAD 0 DC 00101С 0100010001

SGN2 0 uZ 01101P 00011

Y (-0,1111011110), (-0,9667968)0 I&Y 0,0003742

SGNl 1 DS OHIOS lOlOQlllOl

QUAD 10 10001С 1100000111

SGNl 0 Z 00010P 00001

16 (-0,1010011110)2, (-0,6542968)0 |uY| 0,0004722

Формула изобретениястарших разрядов которого соединены с

Цифровой синтезатор частот, со- . обраэователя кодов, при этом выходы держащий последовательно соединенные второго преобразователя кодов подпервый преобразователькодов, блок ключены к входам младших разрядов памяти, распределитель кодов, сумма- сумматора, другие входы старших разтор, первый регистр памяти, цифро- рядов которого соединены с шиной лоаналоговый преобразователь и фильтр гического нуля, другие поразрядные вынижних частот, а также последователь- 60 ходы распределителя кодов соединены но соединенные перемножитель, второй с первыми поразрядными входами перерегистр памяти и второй преобразова- множителя, первый выход блока синхротель кодов, блок синхронизации и по- низации подключен к первому тактовому следовательно соединенные блок уста- . входу первого преобразователя кодов, новки частоты и накопитель, выходы 65 первому тактовому,входу распределите813675.10

родолх ение . 3

соответствующими входами первого преля кодов и к тактовым входам первого |5егистра памяти и накопителя, второй выход блока синхронизации подключен к второму тактовому входу первого преобразователя кодов, второму тактовому входу .распределителя кодов и тактовому входу второго регистра памяти, а выход старшего разряда второго преобразователя кодов соединен с первым входом знакового разряда сумматора и с входом знакового разряда регистра памяти, отличающийс я тем, что, с целью повышения спектральной чистоты выходного сигнала, между выходами младших разрядов накопителя и вторыми поразрядными входами перемножителя включен блок вычисления угловой коррекции, такто- ,

вый вход которого соединен с первым выходом блока синхронизации, выход .старшего разряда первого преобразователя кодов подключен к входу знакового разряда первого регистра памяти, другой вход знакового разряда сумматора соединен с шиной логического нуля, а. выход знакового разряда блока вычисления угловой коррекции соединен с входом знакового разряда второго регистра памяти.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-03-15—Публикация

1978-10-25—Подача