Изобретение относится к устройствам для синхронизации псевдошумо

вого сигнала и может быть использовано для .установления начальной синхронизации приемника и передатчика.

Цель изобретения - уменьшение времени синхронизации.

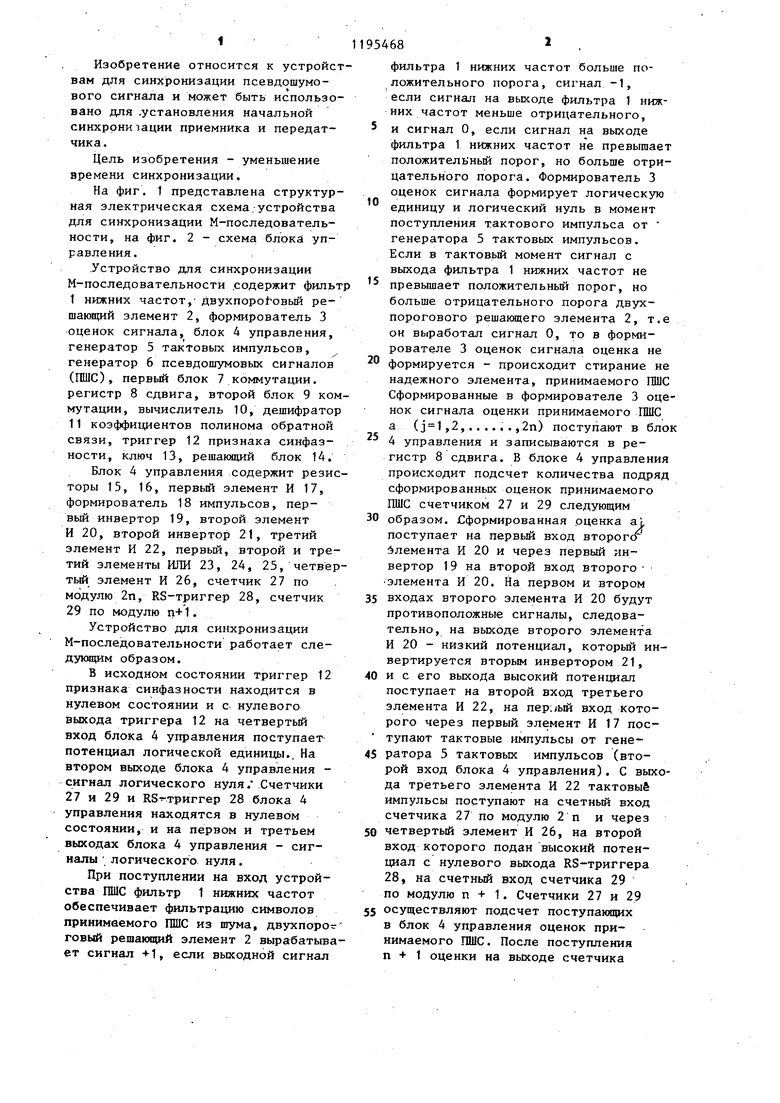

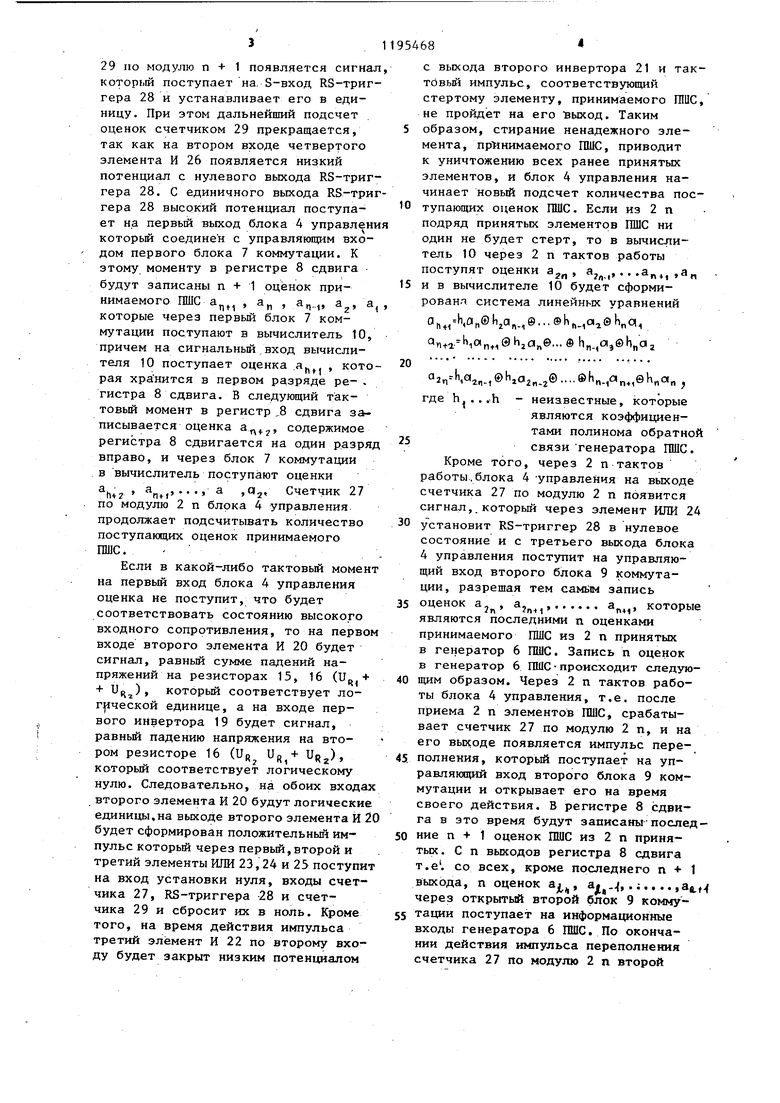

На фиг. 1 представлена структурная электрическая схема,-устройства для синхронизации М-последрвательности, на фиг. 2 - схема блока управления.

Устройство для синхронизации М-последовательности .содержит фильт

Iнижних частот, Двyxпopo oвый решанщий элемент 2, формирователь 3 оценок сигнала, блок 4 управления, генератор 5 тактовых импульсов, генератор 6 псевдошумовьк сигналов (ПШС), первый блок 7 коммутации, регистр 8 сдвига, второй блок 9 коммутации, вычислитель 10, дешифратор

I1коэффициентов полинома обратной связи, триггер 12 признака синфазности, ключ 13, решакмций блок 14.

Блок 4 управления содержит резисторы 15, 16, первый элемент И 17, формирователь 18 импульсов, первый инвертор 19, второй элемент И 20, второй инвертор 21, третий элемент И 22, первый, второй и третий элементы ИЛИ 23, 24, 25, четвертый элемент И 26, счетчик 27 по модулю 2п, RS-триггер 28, счетчик 29 по модулю n+l.

Устройство для синхронизации М-последовательности работает следукмцим образом.

В исходном состоянии триггер 12 признака синфазности находится в нулевом состоянии и с нулевого выхода триггера 12 на четвертый вход блока 4 управления поступает потенциал логической единицы., На втором выходе блока 4 управления сигнал логического нуля. Счетчики 27 и 29 и КЗ триггер 28 блока 4 управления находятся в нулевом состоянии, и на первом и третьем выходах блока 4 управления - сигналы логического нуля.

При поступлении на вход устройства ПШС фильтр 1 нижних частот обеспечивает фильтрацию символов принимаемого ПШС из шума, двухпороговый решающий элемент 2 вырабатывает сигнал +1, если выходной сигнал

фильтра 1 нижних частот больше положительного порога, сигнал -1, если сигнал на выходе фильтра 1 нижних частот меньше отрицательного,

и сигнал О, если сигнал на выходе фильтра 1 нижних частот не превышает положительный порог, но больше отрицательного порога. Формирователь 3 оценок сигнала формирует логическую единицу и логический нуль в момент поступления тактового импульса от генератора 5 тактовых импульсов. Если в тактовьй момент сигнал с выхода фильтра 1 нижних частот не

превышает положительный порог, но больше отрицательного порога двухпорогового решающего элемента 2, т.е он вьфаботал сигнал О, то в формирователе 3 оценок сигнала оценка не

формируется - происходит стирание не надежного элемента, принимаемого ПШС Сформированные в формирователе 3 оценок сигнала оценки принимаемого ПШС а (,2,......,2п) поступают в блок

4 управления и записываются в регистр 8 сдвига. В блоке 4 управления происходит подсчет количества подряд сформированных оценок принимаемого ПШС счетчиком 27 и 29 следующим

образом. Сформированная оценка aY. поступает на первый вход второго Элемента И 20 и через первый инвертор 19 на второй вход второго элемента И 20. На первом и втором

входах второго элемента И 20 будут противоположные сигналы, следовательно, на выходе второго элемента И 20 - низкий потенциал, который инвертируется вторым инвертором 21,

и с его выхода высокий потенциал поступает на второй вход третьего элемента И 22, на пер:;ый вход которого через первый элемент И 17 поступают тактовые импульсы от генератора 5 тактовых импульсов (второй вход блока 4 управления). С выхода третьего элемента И 22 тактовые импульсы поступают на счетный вход счетчика 27 по модулю 2 п и через

четвертый элемент И 26, на второй вход которого подан высокий потенциал с нулевого выхода RS-триггера 28, на счетный вход счетчика 29 по модулю п + 1. Счетчики 27 и 29

осуществляют подсчет поступающих в блок 4 управления оценок принимаемого ПШС. После поступления п + 1 оценки на выходе счетчика 29 no модулю n + 1 появляется сигна который поступает на. S-вход RS-триг гера 28 и устанавливает его в единицу. При этом дальнейший подсчет . оценок счетчиком 29 прекращается, так как на втором входе четвертого элемента И 26 появляется низкий потенциал с нулевого выхода RS-триг гера 28. С единичного выхода RS-три гера 28 высокий потенциал поступает на первый выход блока 4 управлен которьй соединен с управляющим входом первого блока 7 коммутации. К этому моменту в регистре 8 сдвига будут записаны n + 1 оценок принимаемого ПШС а, , а„ , а..,, а, а которые через первьй блок 7 коммутации поступают в вычислитель 10, причем на сигнальньй/вход вычислителя 10 поступает оценка .а. , кото рая хранится в первом разряде ре- гистра 8 сдвига. В следующий тактовый момент в регистр ,8 сдвига записывается оценка a.f, содержимое регистра 8 сдвигается на один разря вправо, и через блок 7 коммутации в вычислитель поступают оценки Счетчик 27 по модулю 2 n блока 4 управления продолжает подсчитывать количество поступающих оценок принимаемого ПШС. Если в какой-либо тактовый момен на первый вход блока 4 управления оценка не поступит, что будет соответствовать состоянию высокого входного сопротивления, то на перво входе второго элемента И 20 будет сигнал, равный сумме падений напряжений на резисторах 15, 16 (U.+ + Уц.) , который соответствует лог ческой единице, а на входе первого инвертора 19 будет сигнал, равньй падению напряжения на втором резисторе 16 (Up „„ „,, UR,- и«а. который соответствует логическому нулю. Следовательно, на обоих входа второго элемента И 20 будут логически единицы,на выходе второго элемента И будет сформирован положительный импульс который через первый, второй и третий элементы ИЛИ 23, 24 и 25 поступи на вход установки нуля, входы счетчика 27, RS-триггера 28 и счетчика 29 и сбросит их в ноль. Кроме того, на время действия импульса третий элемент И 22 по второму вхоДУ будет закрыт низким потенциалом 8 с вьсхода второго инвертора 21 и тактовый импульс, соответствующий стертому элементу, принимаемого ГП11С, не пpoйдieт на его :выход. Таким образом, стирание ненадежного элемента, принимаемого ПНЮ, приводит к уничтожению всех ранее принятых элементов, и блок 4 управления начинает новый подсчет количества поступающих оценок ПШС. Если из 2 n подряд принятых элементов ПШС ни один не будет стерт, то в вычислитель 10 через 2 п тактов работы поступят оценки а , а ,,.. .а„,, ,а„ и в вычислителе 10 будет сформирована система линейных уравнений .,®...®Ь.,а.,©Ь„а, а,+а.-Ь,ап,,.„® Н„.,о1,0Ь„аг гг,К«2пм® а2„.2©....®Ь„.,с1п„еЬ„а„ где h...h - неизвестные, которые являются коэффициентами полинома обратной связи генератора ПШС. Кроме того, через 2 п тактов работы., блока 4 -управления на выходе счетчика 27 по модулю 2 п появится сигнал,, который через элемент ИЛИ 24 установит RS-триггер 28 в нулевое состояние и с третьего выхода блока 4 управления поступит на управляющий вход второго блока 9 коммутации, разрешая тем самим запись а„,, которые оценок а являются последними п оценками принимаемого Ш1С из 2 п принятых в генератор 6 ПШС. Запись п оценок в генератор 6 ПШСпроисходит следующим образом. Через 2 п тактов работы блока 4 управления, т.е. после приема 2 п элементов Ш11С, срабатывает счетчик 27 по модулю 2 п, и на его выходе появляется импульс переполнения, который поступает на управляюпрсй вход второго блока 9 коммутации и открывает его на время своего действия. В регистре 8 сдвига в это время будут записаны-послед - ние п + 1 оценок ПШС из 2 п принятых. С п выходов регистра 8 сдвига т.е . со всех, кроме последнего п 1 выхода, п оценок aj|, а., .;а. через открытый второй блок 9 коммутации поступает на информационные входы генератора 6 ПШС. По окончании действия импульса переполнения счетчика 27 по модулю 2 п второй блок 9 коммутации закрывается и на его выходах будут нули, и с этого момента генератор 6 ПШС начинает генерировать М-последовательность. Этот же сигнал с третьего выхода блока 4 управления поступает на управляющий вход вычислителя 10 в в нем осуществляется решение систем линейных уравнений (1). Если система линейных уравнений (1) решена верно, т.е. коэффициентып (,..., полученные, в результате решения, совпадают с заданными, то на выходе дешифратора 11 коэффициентов пол нома обратной связи появляется положительный сигнал, которьй поступает на единичный выход триггера 12 признака синфазности и устанавли вает его в единичное состояние. Положительньш потенциал с единичного выхода триггера 12 признака синфазности поступает на управляющий вход ключа 13, разрешая тем самым прохож дение опорного ПШС с выхода генератора 6 ПШС-через ключ 13 на выход устройства синхронизации. Нулевой п тенциал с нулевого выхода триггера 12 признака синфазности поступает на четвертый блок 4 управления и закрывает первый элемент И 17 блока 4 управления, запрещая тем самым да нейший подсчет оценок принимаемого ПШС. Процесс формирования синфазного опорного ПШС заканчивается. Если система линейньк уравне,НИИ (1) решена невернЬ, т.е. в принятьк 2 п элементах ПШС содержится ошибка, то триггер 12 признака синфазности остается в нулевом состоянии, следовательно, ключ 13 будет закрыт и. опорная М-последовательность, которая в этом случае является несинфазной с принимаемой не пройдет на выход ключа 13. Блок 4 управления и в этом случае продолжает прием и подсчет новой серии 2 п оценок ПШС. Через п тактов работы в вычислителе 10 будет сформирована новая система ;шмейных 686 уравнений (1), а в генератор 6 ПШС запишется новое начальное состояние, начиная с которого он будет генерировать новую М-последовательность и так до тех пор, пока система линейных уравнений (.1) не будет решена верно. Синфазный ПШС z выхода ключа 13 поступает также и на второй вход решающего блока 14, который в данном случае выполняет роль детектора синфазности. В том случае, если по какой-либо причине произойдет с сбой синхронизации, то на выходе решакнцего блока 14 появится положительньй потенциал, который поступает на третий вход блока 4 управления, в нем - на вход формирователя 18 импульса, который в момент поступления положительного перепада напряжения сформирует положительньй импульс установки устройства синхронизации в начальное состояние. Этот импульс поступает на входы первого, второго и третьего элементов ИЛИ 23, 24 и 25 и устанавливает в исходноесостояние счетчик 27 RS-триггер 28 и счетчик 29. С первого выхода блока 4 управления импульс поступает на вход установки нуля триггера 12 признака синфазности и на вход установки нуля регистра 8 сдвига и устанавливает их в нулевое состояние. Ключ 13 закрывается и опорная М-последовательность не поступает на выходе устройства. Блок 4 управления начинает подсчет новой серии из 2 п подряд следующих оценок принимаемого ПШС, и процесс установления синхронизации начинается сначала. Таким образом, решение о том, что принимаемый и опорньй ПШС будут синфазны, выносится после того, как триггер 12 признака синфазности установится в единичное состояние, т.е. после правильного решения системы линейных уравнений (1),

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 2013 |

|

RU2550563C1 |

| Устройство для синхронизации @ -последовательности | 1981 |

|

SU1003375A1 |

| Устройство поиска псевдошумового сигнала по задержке | 1988 |

|

SU1626426A1 |

| УСТРОЙСТВО ПОИСКА ПСЕВДОШУМОВОГО СИГНАЛА ПО ЗАДЕРЖКЕ | 1991 |

|

RU2017337C1 |

| Автокорреляционный измеритель параметров псевдослучайного фазоманипулированного сигнала | 1987 |

|

SU1518894A2 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИЕМОПЕРЕДАЧИ ДАННЫХ | 2001 |

|

RU2209524C2 |

| Следящий приемник асинхронных шумоподобных сигналов | 1986 |

|

SU1403381A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1302435A1 |

УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ М-ПОСЖДОВАТЕЛЬНОСТИ, содержа щее вычислитель и фильтр нижних частот, вход которого объединен с первым входом решающего блока и является входом устройства, а выход фильтра нижних частот через последовательно объединенные двухпороговый решающий элемент и формирователь оценок сигнала подключен к первому входу блока управления, к второму входу которого, а также к второму входу формирователя оценок сигнала и тактовому входу генератора псевдопгумового сигнала (ГШ1С) подключен выход генератора тактовых импульсов при этом выход решающего блока подключен к третьему входу блока управления, первый выход которого подключен к управляющему входу первого блока коммутации, отличающееся тем, что,- с целью уменьшения времени синхронизации, введены второй блок коммутации, регистр сдвига, дешифратор коэффициентов полинома обратной связи, триггер признака синфазности и ключ, выход которого подключен к второму входу решающего блока и является выходом устройства, а к информационному и управляющему входам ключа подсоединены соответственно выход генератора ПШС и единичный выход триггера признака синфазности, нулевой выход которого подключен к четвертому входу блока управления, второй выход которого подключен к входам установк-и нуля триггера признака синфазности и регистра сдвига к инфорS мационному и тактовому входам кото(Л рого подключены соответственно выход формирователя оценок сигнала и выход генератора тактовых импульсов, а третий выход блока управления подключен к управляющим входам второго блока коммутации и вычислителя, к сигнальному входу которого через первьй блок коммутации подключен первый выход регистра сдвига, остальные выходы которого через первый блок ;0 сд коммутации подключены к соответствующим входам вычислителя, выходы 4 0 которого подключены к входам дешифратора коэффициентов полинома обрат00 ной связи, выход которого подключен к единичному входу триггера признака синфазносфи, причем выходы регистра сдвига кроме п + 1 через второй блок коммутации подключены к информационным входам генератора ПШС.

| Устройство для определения фазы двоичного псевдошумового сигнала с последовательным выбором оценок | 1973 |

|

SU468187A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для синхронизации @ -последовательности | 1981 |

|

SU1003375A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-11-30—Публикация

1984-04-25—Подача