Цд 05 00

ел

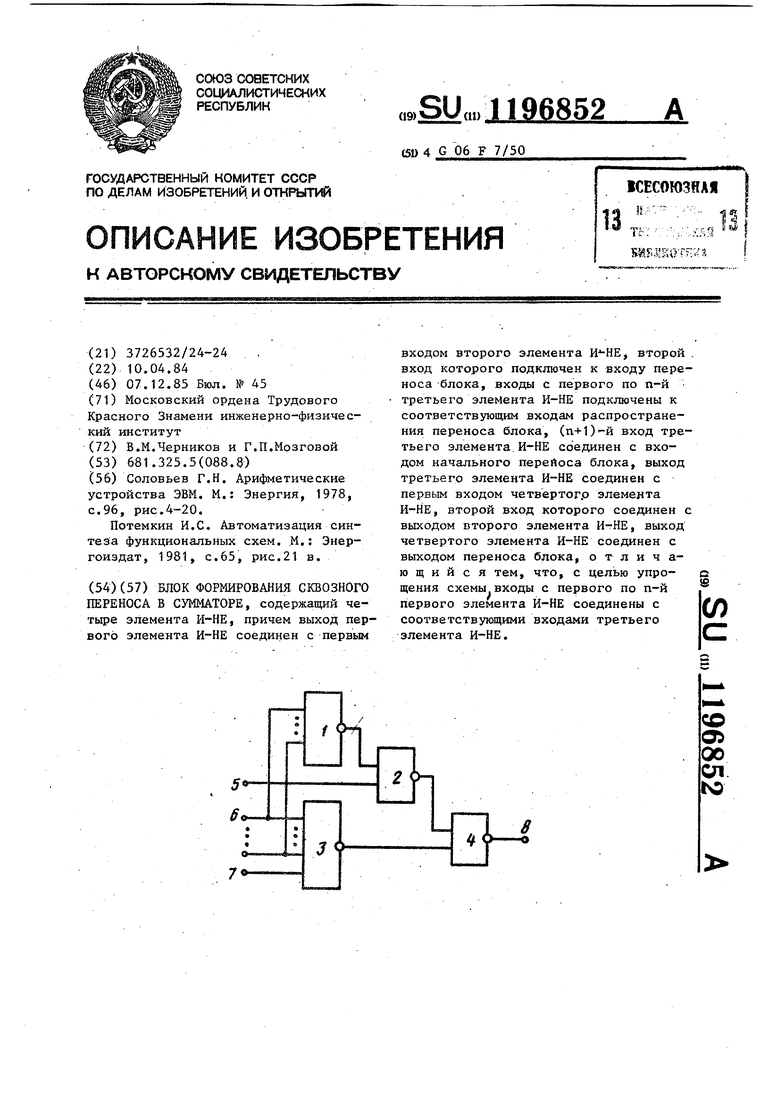

tsD 1 Изобретение относится к вычислительной технике и может быть исполь зовано при построении многоразряд-ных быстродействующих сумматоров. Целью изобретения является упрощение блока формирования сквозного переноса в сумматоре. , Иа чертеже приведена функционал ная схема блока формирования сквозного переноса в сумматоре. Блок содержит четыре элемента И1-4 и имеет вход 5 переноса, входь 6 распространения переноса, вход 7 начального переноса, а также выход 8 переноса, Блок работает следующим образом. На вход 7 поступает сигнал начал ного переноса-Со, а на входы 6 - си наль распространения переноса Р- Х ®, где Х , Y - двоичные разряды слагаемых (i 1,2,...,п). Сфор мированньш п-разрядным сумматором сигнал неускоренного переноса С Vt по тупает на вход 5 блока, В п-разрядных сумматорах как для ускоренного, так и для неускоренного сигналов переноса должно выполняться следующее логическое выражениег ,,Р,й,,др„.,....-а,р„...Р, С,Р„...Р, ,-C 2 Y . V сигнал генерации пегде Ч . реноса из {-го-разряда. Коммутация элементов И-НЕ 1-4 выполнена таким образом, что на выходе 8 формируется сигнал: ,р,....р,с,р,...р, . Подставляя в (2) выражение (1) для сигнала S, подаваемого на вход 5, и учитывая, что СцР С для сигнала С , формируемого на выходе 8, приходим к выражению , (1). Таким образом, формируемый на выходе 8 устройства сигнал является сигналом переноса, что является свидетельством работоспособности блока. Блоки формирования сквозного пе.реноса предназначены -для ускорения распространения переноса в случае 9 Р,..- Р 1. Данньй блок позволяет исключить влияние сигнала С| , подаваемого на вход 5 устройства, на сигнал С, формируемый на выходе 8 устройства, при Р Pj ... Р„ 1. В этом случае, как следует из выраже- . ния (2), Сп Сс , и данный блок обеспечивает быстрое формирование сигнала Ср, на выходе 8 при переключениях сигнала С,, на входе 7 как из -о на входе так и из 1 в О в Г

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Параллельный сумматор с контролем по четности | 1982 |

|

SU1121674A1 |

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

| Блок формирования переносов параллельного сумматора | 1988 |

|

SU1571576A1 |

| Трехвходовой параллельный сумматор | 1983 |

|

SU1136150A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1987 |

|

SU1413627A1 |

| Устройство для умножения двоичных чисел | 1989 |

|

SU1784973A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1008736A1 |

БЛОК ФОРМИРОВАНИЯ. СКВОЗНОГО ПЕРЕНОСА В СУММАТОРЕ, содержащий четыре элемента И-НЕ, причем выход первого элемента И-НЕ соединен с первым входом второго элемента , второй , вход которого подключен к входу переноса -блока, входы с первого по п-й третьего элемента И-НЕ подключены к соответствующим входам распространения переноса блока, (п+1)-й вход третьего элемента.И-НЕ соединен с входом начального перейоса блока, выход третьего элемента И-НЕ соединен с первым входом четвертогр элемента И-НЕ, второй вход которого соединен с выходом второго элемента И-гНЕ, выход четвертого элемента И-НЕ соединен с выходом переноса блока, отличающийся тем, что, с целью упрощения схемы входы с первого по п-й (Л первого элемента И-НЕ соединены с соответствующими входами третьего элемента И-НЕ.

| Соловьев Г.Н | |||

| Арифметические устройства ЭВМ | |||

| М.: Энергия, 1978, с.96, РИС.4--20 | |||

| Потемкин И.С | |||

| Автоматизация синтеза функциональных схем | |||

| М.: Энергоиздат, 1981, с.65, рис.21 в. |

Авторы

Даты

1985-12-07—Публикация

1984-04-10—Подача