1 13108102

Изобретение относится к вычисли- этом на выходах элементов И 2 матри- тельной технике и может быть исполь- цы 1 формируются одноразрядные частичные произведения х.,Ур., (k 1,2, ,,., N, Р 1,2,.,,, М), Частичные 5 произведения Xj,.,yg., (Z 1,2,,,.,М-1) и X;., y.,(i 1,2,,,., N-1) поступают на вторые входы соответствующих элезовано в арифметических устройствах высокопроизводительных ЭВМ и в вычислительных системах, работающих в реальном масштабе времейи.

Цель изобретения - расширение функциональных возможностей устройства за счет выполнения умножения с накоплением положительных, отрицательных и комплексных чисел.

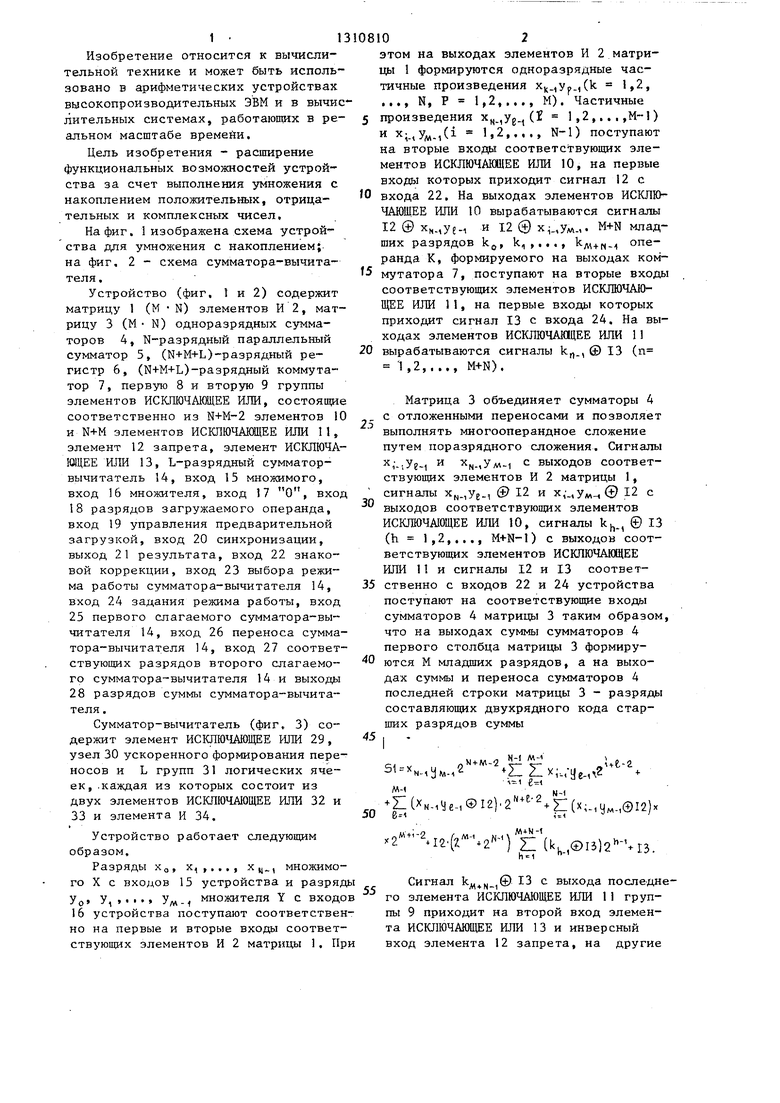

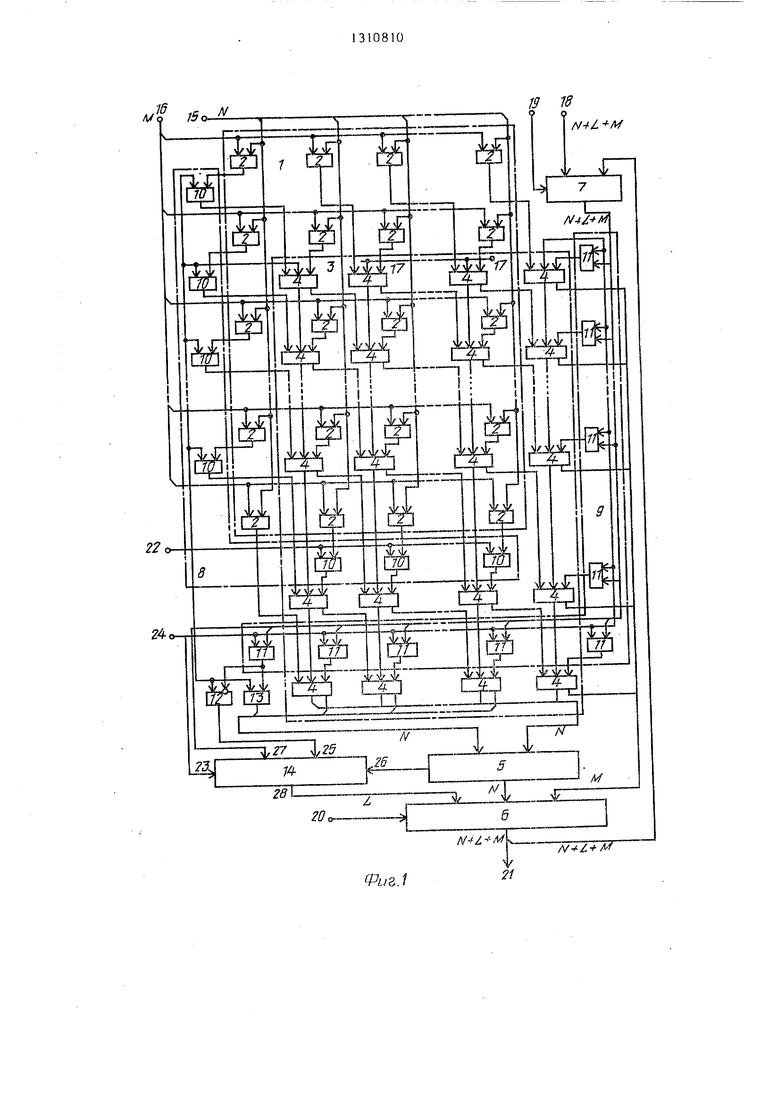

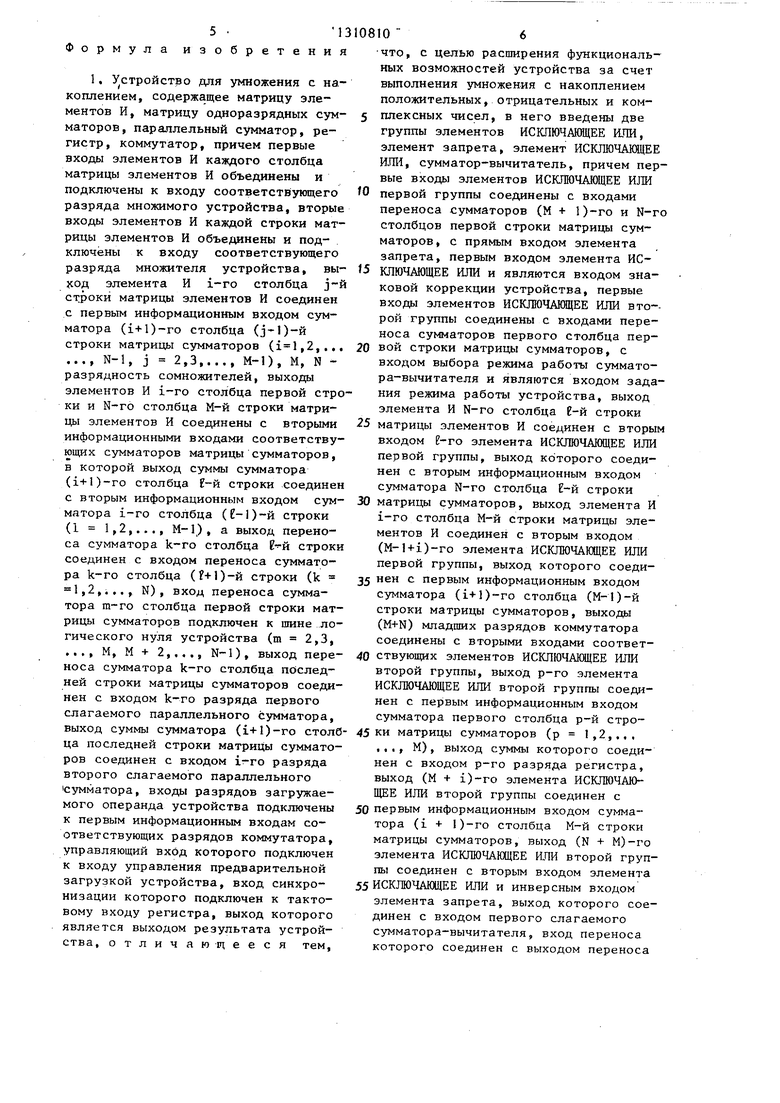

На фиг, 1 изображена схема устройства для умножения с накоплением; на фиг, 2 - схема сумматора-вычита- теля,

Устройство (фиг, 1 и 2) содержит матрицу 1 (М N) элементов И 2, матрицу 3 (М N) одноразрядных сумматоров 4, N-разрядный параллельный сумматор 5, (N+M+L)-разрядный регистр 6, (N+M+L)-разрядный коммутатор 7, первую 8 и вторую 9 группы элементов ИСКЛЮЧАЩЕЕ ИЛИ, состоящие соответственно из N+M-2 элементов 10 и N+M элементов ИСКПЮЧАЩЕЕ ИЛИ 11, элемент 12 запрета, элемент ИСКЛЮЧАЩЕЕ ШШ 13, L-разрядный сумматор- вычитатель 14, вход 15 множимого, вход 16 множителя, вход 17 О, вход 18 разрядов загружаемого операнда, вход 19 управления предварительной загрузкой, вход 20 синхронизации, выход 21 результата, вход 22 знаковой коррекции, вход 23 выбора режима работы сумматора-вычитателя 14, вход 24 задания режима работы, вход 25 первого слагаемого сумматора-вычитателя 14, вход 26 переноса сумматора-вычитателя 14, вход 27 соответствующих разрядов второго слагаемого сумматора-вычитателя 14 и выходы 28 разрядов суммы сумматора-вычитателя ,

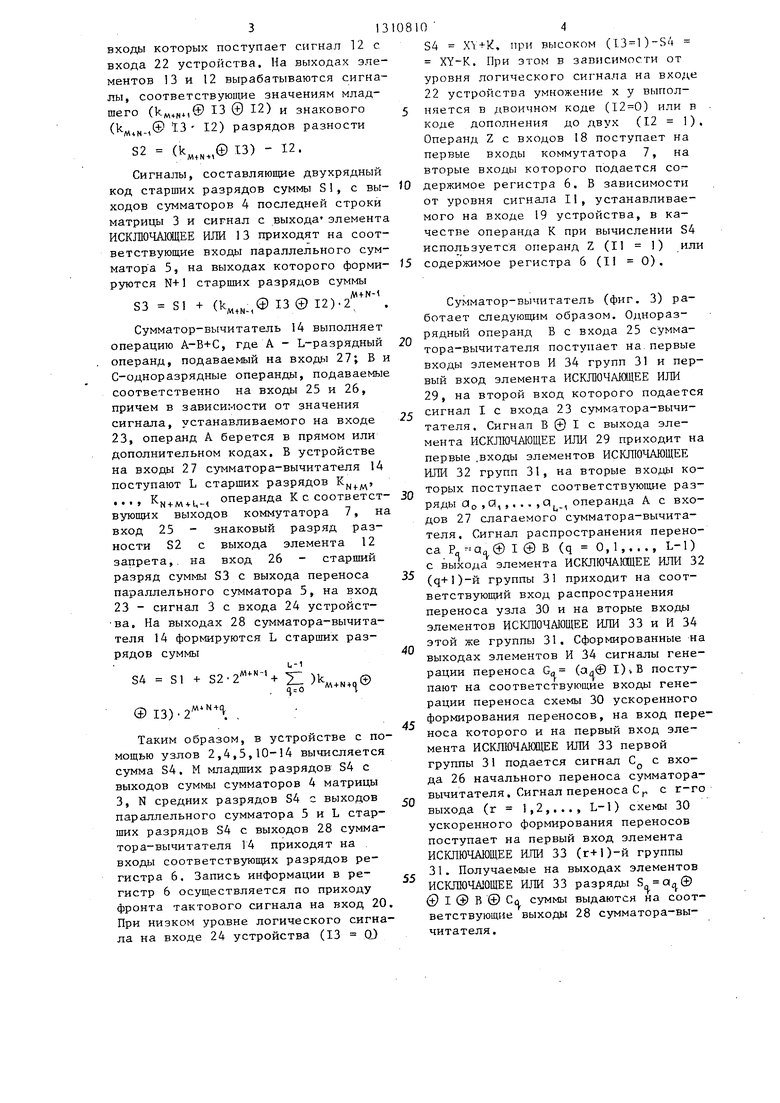

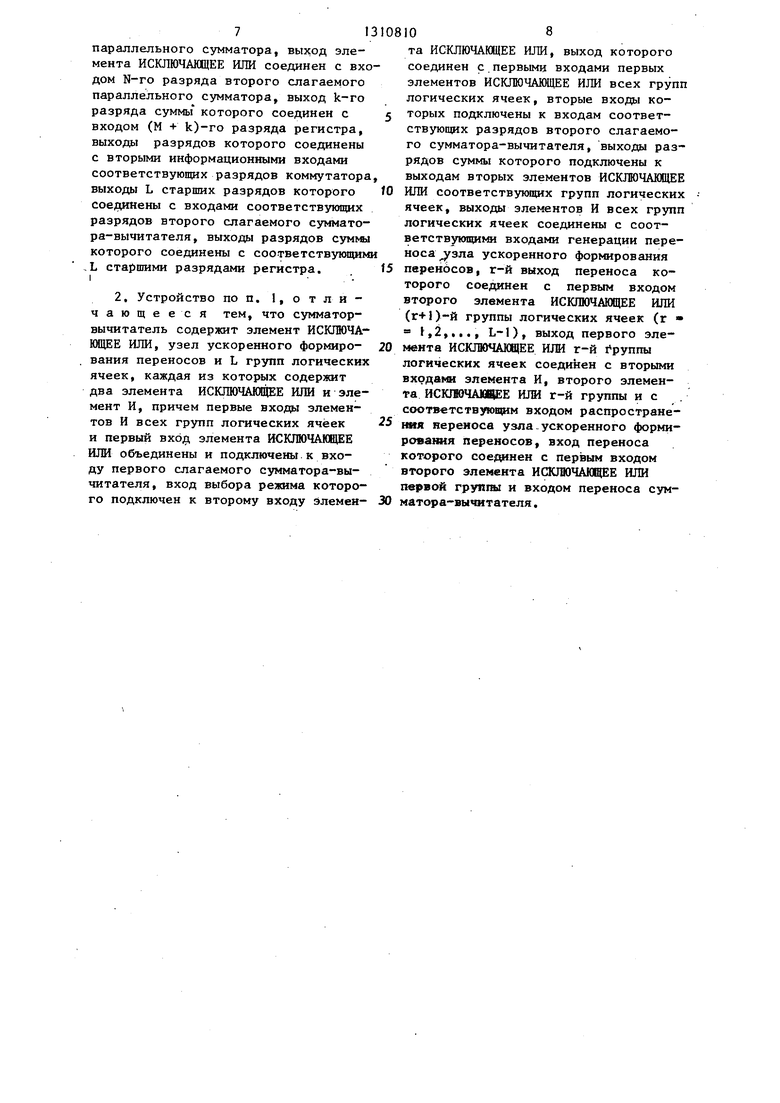

Сумматор-вычитатель (фиг. 3) содержит элемент ИСКЛЮЧАЮЩЕЕ РШИ 29, узел 30 ускоренного формирования переносов и L групп 31 логических ячеек, .каждая из которых состоит из двух элементов ИСКЛЮЧАЮЩЕЕ ШШ 32 и 33 и элемента И 34,

Устройство работает следующим образом.

ментов ИСКЛЮЧАЮЩЕЕ ИЛИ 10, на первые входы которых приходит сигнал 12 с

О входа 22, На выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 10 вырабатываются сигналы 12 ® х.,уе-1 и 12 (Э х.,Ум.,. M+N младших разрядов kg, k, ,,,., .;, операнда К, формируемого на выходах комf5 мутатора 7, поступают на вторые входы соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ П, на первые входы которых приходит сигнал 13 с входа 24, На выходах элементов ИСКЛЮЧАЩЕЕ ИЛИ 11

20 вырабатываются сигналы k , © 13 (п 1,2,.,,, M+N).

25

30

Матрица 3 объединяет сумматоры 4 с отложенными переносами и позволяет выполнять многооперандное сложение путем поразрядного сложения. Сигналы 5.;Уе, и Х|.,удд, с выходов соответ- ствую1щх элементов И 2 матрицы 1, сигналы Х,.,У., ® 12 и x,., 12 с выходов соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 10, сигналы k,,, © 13 (h 1,2,,,,, M+N-1) с выходов соответствующих элементов ИСКПЮЧАЩЕЕ ИЛИ П и сигналы 12 и 13 соответ- 35 ственно с входов 22 и 24 устройства поступают на соответствующие входы сумматоров 4 матрицы 3 таким образом, что на выходах суммы сумматоров 4 первого столбца матрицы 3 формируются М младших разрядов, а на выходах суммы и переноса сумматоров 4 последней строгий матрицы 3 - разряды составляющих двухрядного када старших разрядов суммы

40

45

51 ,Ум- М-(

хц.м-2 „Ut-г

,2 I:I:x;.ae.лг

N-(

50

Г (ХМ.,У е, © 12). Г (Х;.,у„.,®12)х I2{z -42 -Vi: k,.,©B).

х2

М+1-2

h-1

Разряды Хо, X,

Ху, МНОЖИМОГО X С входов 15 устройства и разряды УО У, ,«, УМ-, множителя Y с входов 16 устройства поступают соответственно на первые и вторые входы соответствующих элементов И 2 матрицы 1. При

ментов ИСКЛЮЧАЮЩЕЕ ИЛИ 10, на первые входы которых приходит сигнал 12 с

О входа 22, На выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 10 вырабатываются сигналы 12 ® х.,уе-1 и 12 (Э х.,Ум.,. M+N младших разрядов kg, k, ,,,., .;, операнда К, формируемого на выходах комf5 мутатора 7, поступают на вторые входы соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ П, на первые входы которых приходит сигнал 13 с входа 24, На выходах элементов ИСКЛЮЧАЩЕЕ ИЛИ 11

20 вырабатываются сигналы k , © 13 (п 1,2,.,,, M+N).

Матрица 3 объединяет сумматоры 4 с отложенными переносами и позволяет выполнять многооперандное сложение путем поразрядного сложения. Сигналы 5.;Уе, и Х|.,удд, с выходов соответ- ствую1щх элементов И 2 матрицы 1, сигналы Х,.,У., ® 12 и x,., 12 с выходов соответствующих элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 10, сигналы k,,, © 13 (h 1,2,,,,, M+N-1) с выходов соответствующих элементов ИСКПЮЧАЩЕЕ ИЛИ П и сигналы 12 и 13 соответ- ственно с входов 22 и 24 устройства поступают на соответствующие входы сумматоров 4 матрицы 3 таким образом, что на выходах суммы сумматоров 4 первого столбца матрицы 3 формируются М младших разрядов, а на выходах суммы и переноса сумматоров 4 последней строгий матрицы 3 - разряды составляющих двухрядного када старших разрядов суммы

51 ,Ум- М-(

хц.м-2 „Ut-г

,2 I:I:x;.ae.лг

N-(

0

Г (ХМ.,У е, © 12). Г (Х;.,у„.,®12)х I2{z -42 -Vi: k,.,©B).

х2

М+1-2

h-1

Сигнал k,,© 13

с выхода последнего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 11 группы 9 приходит на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 и инверсный вход элемента 12 запрета, на другие

31

входы которых поступает сигнал 12 с входа 22 устройства. На выходах элементов 13 и 12 вырабатываются сигналы, соответствующие значениям младшего (,® 13 © 12) и знакового ( 12) разрядов разности

52 (Ч,,.,© 13) - 12.

Сигналы, составляющие двухрядный код старших разрядов суммь S, с выходов сумматоров 4 последней строки матрицы 3 и сигнал с выхода элемента ИСКЛЮЧАЩЕЕ ИЛИ 13 приходят на соответствующие входы параллельного сумматора 5, на выходах которого формируются N+1 старших разрядов суммы

53 S + (,® 13 © 12).

Сумматор-вычитатель 14 выполняет операцию А-В+С, где А - L-разрядный операнд, подаваемый на входы 27; Б и С-одноразрядные операнды, подаваемые соответственно на входы 25 и 26, причем в зависимости от значения сигнала, устанавливаемого на входе 23, операнд А берется в прямом или дополнительном кодах. В устройстве на входы 27 сумматора-вычитателя 14 поступают L старших разрядов К, ..., , операнда К с соответствующих выходов коммутатора 7, на вход 25 - знаковый разряд разности S2 с выхода элемента 12 запрета,, на вход 26 - старший разряд суммы S3 с выхода переноса параллельного сумматора 5, на вход 23 - сигнал 3 с входа 24 устройст- ва. На выходах 28 сумматора-вычитателя 14 формируются L старших разрядов суммы

L-1

84 S1 + S2 2

, Ъ

® 13)

Таким образом, в устройстве с помощью узлов 2,4,5,10-14 вычисляется сумма S4. М младших разрядов S4 с выходов суммы сумматоров 4 матрицы 3, N средних разрядов 84 с выходов параллельного сумматора 5 и L старших разрядов 84 с выходов 28 сумматора-вычитателя 14 приходят на входы соответствующих разрядов регистра 6, Запись информации в регистр 6 осуществляется по приходу фронта тактового сигнала на вход 20, При низком уровне логического сигнала на входе 24 устройства (13 Ш

0810 4

84 XY+K, при высоком ()S4 XY-K. При этом в зависимости от уровня логического сигнала на входе 22 устройства умножение х у выпол- 5 няется в двоичном коде () или в коде дополнения до двух (12 1). Операнд Z с входов 18 поступает на первые входы ко тмутатора 7, на вторые входы которого подается со

10 держимое регистра 6. В зависимости от уровня сигнала II, устанавливаемого на входе 19 устройства, в качестве операнда К при вычислении S4 используется операнд Z (II 1) или

15 содержимое регистра 6 (II 0).

Сумматор-вычитатель (фиг. 3) работает следуюш 1м образом. Одноразрядный операнд В с входа 25 сумматора-вычитателя поступает на первые входы элементов И 34 групп 31 и первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 29, на второй вход которого подается

5 сигнал I с входа 23 сумматора-вычитателя. Сигнал В @ 1 с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 29 приходит на первые .входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 32 групп 31, на вторые входы ко торых поступает соответствующие разряды а ,а, ,... ,а., операнда А с входов 27 слагаемого сумматора-вычитателя. Сигнал распространения переноса Р- а, ® I @ В (q 0,1,..., L-1) с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 32 (q+l)-й группы 31 приходит на соответствующий вход распространения переноса узла 30 и на вторые входы элементов ИСКШОЧАЮЩЕЕ ИЛИ 33 и И 34 этой же группы 31. Сформированные на выходах элементов И 34 сигналы генерации переноса Ga ( I)kB поступают на соответствующие входы генерации переноса схемы 30 ускоренного формирования переносов, на вход пере0

5

0

5

носа которого и на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 33 первой группы 31 подается сигнал С с входа 26 начального переноса сумматора- вычитателя. Сигнал переноса С с г-го

выхода (г 1,2L-1) схемы 30

ускоренного формирования переносов поступает на первый вход элемента ИСКЛЮЧАЮЩЕЕ КПИ 33 (г+1)-й группы 31. Получаемые на выходах элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 33 разряды S (±) I ® В © Сл суммы выдаются на соответствующие выходы 28 сумматора-вычитателя.

Формула изобретения

1, Устройство для умножения с накоплением, содержащее матрицу элементов И, матрицу одноразрядных сумматоров, параллельный сумматор, регистр, коммутатор, причем первые входы элементов И каждого столбца матрицы элементов И объединены и подключены к входу соответствующего разряда множимого устройства, вторые входы элементов И каждой строки матрицы элементов И объединены и подключены к входу соответствующего разряда множителя устройства, ход элемента И i-ro столбца строки матрицы элементов И соединен с первым информационным входом сумматора (i+l)-ro столбца (- О-й

что, с целью расширения функциональных возможностей устройства за счет выполнения умножения с накоплением положительных, отрицательных и ком- 5 плексных чисел, в него введены две группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент запрета, элемент ИСКЛЮЧАЩЕЕ ИЛИ, сумматор-вычитатель, причем первые входы элементов ИСКЛЮЧАЮЩЕЕ ШЖ О первой группы соединены с входами

переноса сумматоров (М + О-го и N-ro столбцов первой, строки матрицы сумматоров, с прямым входом элемента запрета, первым входом элемента ИС- вы- f5 КЛЮЧАЮЩЕЕ ИЛИ и являются входом зна- ковой коррекции устройства, первые

входы элементов ИСКЛЮЧАЮЩЕЕ ШШ вто-- рой группы соединены с входами переноса сумматоров первого столбца пер- строки матрицы сумматоров (,2,.,. 20 вой строки матрицы сумматоров, с N-1, j 2,3,..., М-1), М, N - входом выбора режима работы суммато- разрядность сомножителей, выходы ра-вычитателя и являются входом зада- элементов И i-ro столбца первой стро- ния режима работы устройства, выход ки и N-ro столбца М-й строки матри- элемента И N-ro столбца В-й строки цы элементов И соединены с вторыми 25 матрицы элементов И соединен с вторым

входом Е-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, выход ко торого соединен с вторым информационным входом сумматора N-ro столбца Е-й строки

информационными входами соответствующих сумматоров матрицы сумматоров, в которой выход суммы сумматора (i+l)-ro столбца Е-й строки соединен

с вторым информационным входом сум- 30 матрицы сумматоров, выход элемента И

матора i-ro столбца (-1)-й строки (1 1,2,.,., М-1), а выход переноса сумматора k-ro столбца В-й строки соединен с входом переноса сумматора k-ro столбца (+1)-й строки (k 1,2,..., N), вход переноса сумматора га-го столбца первой строки матрицы сумматоров подключен к шине логического нуля устройства (т 2,3, ..., М, М + 2,..., N-I), выход переноса сумматора k-ro столбца последней строки матрицы сумматоров соединен с входом k-ro разряда первого слагаемого параллельного сумматора.

i-ro столбца М-й строки матрицы элементов И соединен с вторым входом (M-H-i)-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, выход которого соеди35 нен с первым информационным входом сумматора ()-ro столбца (М-1)-и строки матрицы сумматоров, выходы (M+N) младших разрядов коммутатора соединены с вторыми входами соответ40 ствующих элементов ИСКЛЮЧАЩЕЕ ИЛИ второй группы, выход р-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы соединен с первым информационным входом

сумматора первого столбца р-й стро- выход суммы сумматора (1+1)-го столб- 45 ки матрицы сумматоров (р 1,2,..,

..., М), выход суммы которого соединен с входом р-го разряда регистра, выход (М i)-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы соединен с 50 первым информационным входом сумматора (i + 1)-го столбца М-й строки матрицы сумматоров, выход (N + М)-го элемента ИСКЛЮЧАЮЩЕЕ И,ЛИ второй группы соединен с вторым входом элемента 55 ИСКЛЮЧАЮЩЕЕ ИЛИ и инверсным входом элемента запрета, выход которого соединен с входом первого слагаемого сумматора-вычитателя, вход переноса которого соединен с выходом переноса

ца последней строки матрицы сумматоров соединен с входом 1-го разряда второго слагаемого параллельного сумматора, входы разрядов загружаемого операнда устройства подключены к первым информационным входам соответствующих разрядов коммутатора, управляющий вход которого подключен к входу управления предварительной загрузкой устройства, вход синхронизации которого подключен к тактовому входу регистра, выход которого является выходом результата устройства, отличающееся тем.

i-ro столбца М-й строки матрицы элементов И соединен с вторым входом (M-H-i)-ro элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, выход которого соеди35 нен с первым информационным входом сумматора ()-ro столбца (М-1)-и строки матрицы сумматоров, выходы (M+N) младших разрядов коммутатора соединены с вторыми входами соответ40 ствующих элементов ИСКЛЮЧАЩЕЕ ИЛИ второй группы, выход р-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы соединен с первым информационным входом

713

параллельного сумматора, выход элемента ИСКЛЮЧАЮЩЕЕ ШШ соединен с входом N-ro разряда второго слагаемого параллельного сумматора, выход k-ro разряда суммы которого соединен с входом (М + k)-ro разряда регистра, выходы разрядов которого соединены с вторыми информационными входами соответствующих разрядов коммутатора выходы L старших разрядов которого соединены с входами соответствующих разрядов второго слагаемого суммато- ра-вычитателя, выходы разрядов суммз которого соединены с соответствующим

.L старшими разрядами регистра.

I .

2. Устройство по п. 1, о т л и - чающееся тем, что сумматор- вычитатель содержит элемент ИСКЛЮЧА- КИЦЕЕ ИЛИ, узел ускоренного формиро- вания переносов и L групп логических ячеек, каждая из которых содержит два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент И, причем первые входы элементов И всех групп логических ячеек и первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ объединены и подключены к входу первого слагаемого сумматора-вы- читателя, вход выбора режима которого подключен к второму входу элемен-

108

та ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первыми входами первых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ всех групп логических ячеек, вторые входы которых подключены к входам соответствующих разрядов второго слагаемого сумматора-вычитателя, выходы разрядов суммы которого подключены к выходам вторых элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соответствукнцих групп логических ячеек, выходы элементов И всех групп логических ячеек соединены с соот- вeтcтвyющи ffl входами генерации переноса зла ускоренного формирования перенЬсов, г-й выход переноса которого соединен с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ (г+1)й группы логических ячеек (г t,2,.,., L-1), выход первого элемента ИСКЛОЧАЮЩЕЕ ИЛИ г-й Группы логических ячеек соединен с вторыми входами элемента И, второго элемента ИСКЛОЧАЩЕЕ ИЛИ г-й группы и с соответствуювщм входом распространения переносе узла-ускоренного формирования переносов, вход переноса которого с первым входом второго элемента ИСКЛЮЧАЮЩЕЕ ШШ первой группы и входом переноса сумматора-вычитателя .

л/f /5а

fPuz.l

70

28

( f f

t f f f

31

j/

J7

J4

:DE

30

(риг,2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в квадрат,извлечения квадратного корня,умножения и деления | 1981 |

|

SU1059571A1 |

| Устройство для умножения | 1989 |

|

SU1714592A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для умножения в дополнительном коде | 1984 |

|

SU1234830A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU938282A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1108440A1 |

| Оптический модуль для сложения и вычитания | 1990 |

|

SU1775719A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1034032A1 |

| Устройство для умножения | 1979 |

|

SU849208A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах высокопроизводительных ЭВМ и в вычислительных системах, работающих в реальном масштабе времени. Иобретение позволяет расширить функциональные возможности устройства за счет выполнения умножения с накоплением положительных, отрицательных и комплексных чигсел. Устройство содержит матрицу M-N элементов -И, матрицу M- N одноразрядных сумматоров, N-pas- рядный параллельный сумматор (N.-+-M+L)- разрядный регистр, (N+M+L)-разрядный коммутатор, первую и вторую группы элементов ИСКЛЮЧАНХЦЕЕ ИЖ, элемент запрета, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, L-разрядный сумматор-вычитатель. I 3.п. ф-лы, 2 ил. i (Л со о 00

| Патент США № 4215416, кл | |||

| Способ получения мыла | 1920 |

|

SU364A1 |

| Устройство для умножения с накоплением | 1982 |

|

SU1108087A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-15—Публикация

1986-02-05—Подача