1

Изобретение относится к вычислительной технике и может быть использовано для вьтолнения операции деления дробных и целых двоичных чисел,, представленных дополнительным кодом, в быстродействующих вычислителях и ЭВМ.

Цель изобретения сокращение аппаратурных затрат при построении матричных устройств для деления, у ко- .торых операнды имеют большую разрядность. : ,

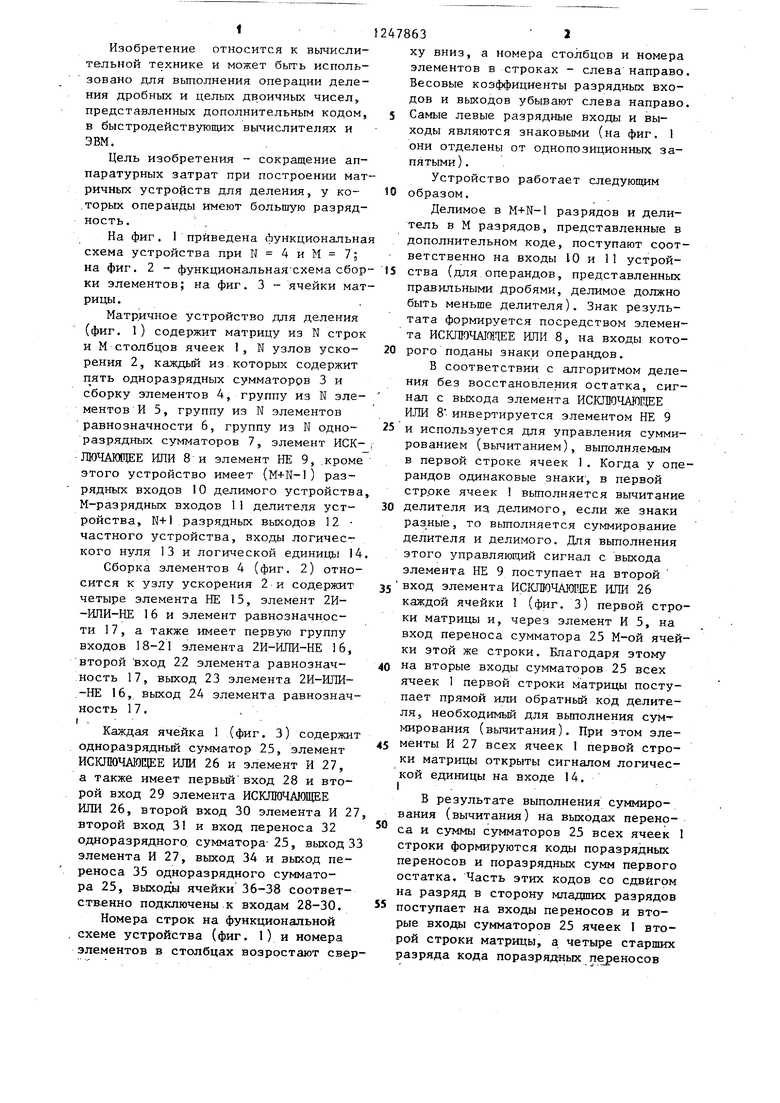

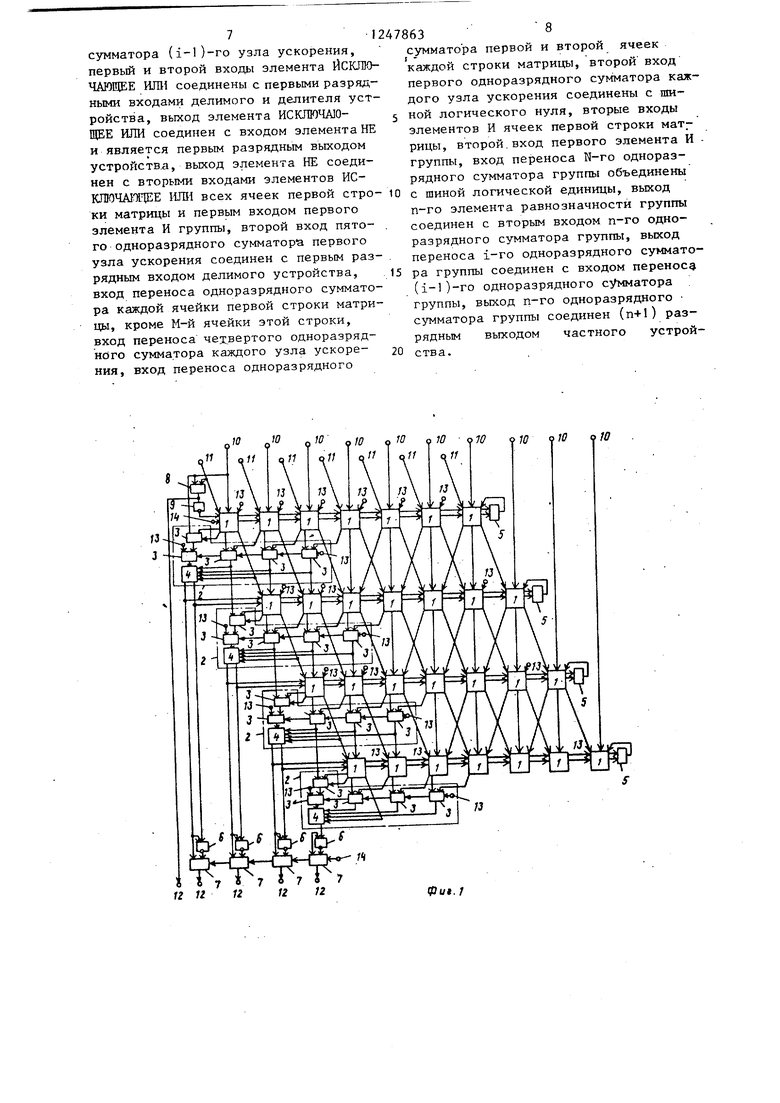

На фиг. 1 приведена функциональна схема устройства при N 4 и М 7; на фиг. 2 - функциональная схема сборки элементов; на фиг. 3 - ячейки матрицы .

Матричное устройство для деления (фиг. 1 ) содержит матрицу из N строк и М столбцов ячеек 1, N узлов ускорения 2, каждьй из которых содержит одноразрядных сумматоррв 3 и сборку элементов 4, группу из N элементов И 5, группу из N элементов равнозначности 6, группу из N одноразрядных сумматоров 7, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 8 и элемент НЕ 9, .кроме этого устройство имеет (М+N-l) разрядных входов 10 делимого устройства М-разрядных входов 11 делителя устройства, N+1 разрядных выходов 12 частного устройства, входы логического нуля 13 и логической единицы 14

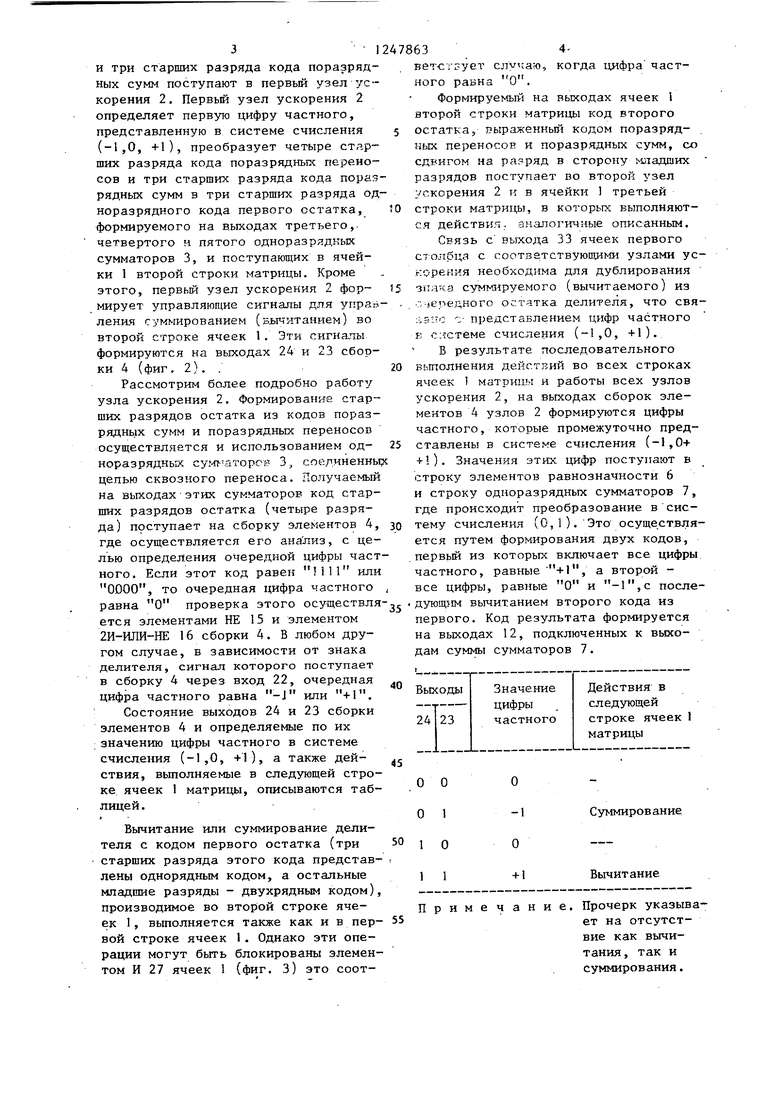

Сборка элементов 4 (фиг. 2) относится к узлу ускорения 2 и содержит четыре элемента НЕ 15, элемент 2И- -ИЛИ-НЕ 16 и элемент равнозначности 17, а также имеет первую группу входов 18-2 элемента 2И-ИЛИ-НЕ 16, второй вход 2:2 элемента равнозначность 17, выход 23 элемента 2И-И11И- .-НЕ 16, выход 24 элемента равнозначность 17.,

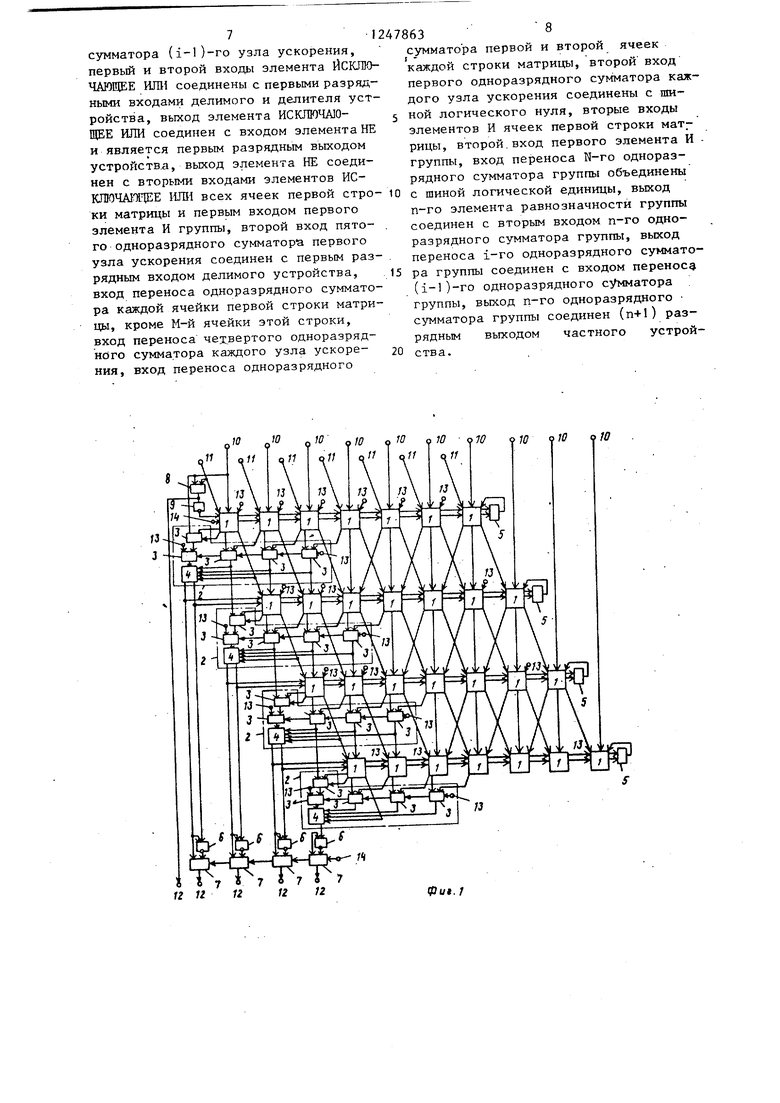

Каждая ячейка 1 (фиг. З) содержит одноразрядный сумматор 25, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 26 и элемент И 27, а также имеет первый вход 28 и второй вход 29 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 26, второй вход 30 элемента И 27 второй вход 31 и вход переноса 32 одноразрядного, сумматора- 25, выход 33 элемента И 27, выход 34 и выход переноса 35 одноразрядного сумматора 25, выходы ячейки 36-38 соответственно подключены к входам 28-30.

Номера строк на функциональной . схеме устройства (фиг. Он номера элементов в столбцах возростают свер47863 2

ху вниз, а номера столбцов и номера элементов в строках - слева направо. Весовые коэффициенты разрядных входов и выходов убывают слева направо.

5 Самые левые разрядные входы и выходы являются знаковыми (на фиг. 1 они отделены от однопозиционных запятыми ).

Устройство работает следующим

10 образом.

Делимое в M+N-1 разрядов и делитель в М разрядов, представленные в дополнительном коде, поступают соответственно на входы 10 и П устрой5 ства (для операндов, представленных правильными дробями, делимое должно быть меньше делителя). Знак результата формируется посредством элемента ИСКЛЮЧАЮПЕЕ ИЛИ 8, на входы кото20 рого поданы знаки операндов.

В соответствии с алгоритмом деления без восстановления остатка, сигнал с выхода элемента ИСКЛЮ ЧАЮС ЕЕ ИЛИ 8 инвертируется элементом НЕ 9

25 и используется для управления суммированием (вычитанием), выполняемым в первой строке ячеек 1 . Когда у операндов одинаковые знаки , в первой стр.оке ячеек выполняется вычитание

30 делителя из делимого, если же знаки разные, то вьтолняется суммирование делителя и делимого. Для выполнения этого управляющий сигнал с выхода элемента НЕ 9 поступает на второй

35 вход элемента ИСКЛЮЧАЮР ЕЕ ИЛИ 26

каждой ячейки 1 (фиг. 3) первой строки матрицы и, через элемент И 5, на вход переноса сумматора 25 М-ой ячейки этой же строки. Благодаря этому

40 на вторые входы сумматоров 25 всех ячеек 1 первой строки матрицы поступает прямой или обратньй код делителя, необходимьш для выполнения сум- 1чирования (вычитания). При этом эле5 менты И 27 всех ячеек 1 первой строки матрицы открыты сигналом логической единицы на входе 14. I .

В результате выполнения суммирования (вычитания) на выходах переноса и суммы сумматоров 23 всех ячеек 1 строки формируются коды поразрядных переносов и поразрядных сумм первого остатка. Часть этих кодов со сдвигом на разряд в сторону младших разрядов поступает на входы переносов и вторые входы сумматоров 25 ячеек I второй строки матрицы, а четыре старших разряда кода поразрядных переносов

50

55

и три старших разряда кода поразрядных сумм поступают в первьй узел ускорения 2. Первьй узел ускорения 2 определяет первую цифру частного, представленную в системе счисления (-1,0, +1), преобразует четыре старших разряда кода поразрядных переносов и три старших разряда кода поразрядных сумм в три старших разряда одноразрядного кода первого остатка, формируемого на выходах третьего,, четвертого и пятого одноразрядных сумматоров 3, и поступающих в ячейки 1 второй строки матрицы. Кроме этого, первый узел ускорения 2 фор- мирует управляющие сигналы для управ ления суммированием (вычитанием) во второй строке ячеек 1. Эти сигналы формируются на выходах 24 и 23 сборки 4 (фиг, 2). .

Рассмотрим более подробно работу узла ускорения 2, Формирование старших разрядов остатка из кодов поразрядных сумм и поразрядных переносов осуществляется и использованием од- поразрядных cyJ - тopoв 3, соединенньр цепью сквозного переноса. Получаемый на выходах этих сумматоров код старших разрядов остатка (четыре разряда) поступает на сборку элементов 4, где осуществляется его анализ, с целью определения очередной цифры частного. Если этот код равен ПП или ODOO, то очередная цифра частного равна О проверка этого осуществля ется элементами НЕ 15 и элементом 2И-ИЛИ-НЕ 16 сборки 4. В любом другом случае, в зависимости от знака делителя, сигнал которого поступает в сборку 4 через вход 22, очередная цифра частного равна -J или +1,

Состояние выходов 24 и 23 сборки элементов 4 и определяемые по их значению цифры частного в системе счисления (-1,0, +1), а также действия, вьтолняемые в следующей строке ячеек 1 матрицы, описываются таблицей.

Вычитание или суммирование делителя с кодом первого остатка (три старших разряда этого кода представ- лены однорядным кодом, а остальные младшие разряды - двухрядным кодом), производимое во второй строке ячеек 1, выполняется также как и в пер- вой строке ячеек 1. Однако эти операции могут быть блокированы элементом И 27 ячеек 1 (фиг. 3) это соот

вет-стБует сличаю, когда цифра частного равна О.

Формируемый на выходах ячеек 1 второй строки матрицы код второго остатка, выраженньп кодом поразрядных переносок и поразрядных сумм, со сдвигом на разряд в сторону младших разрядов поступает во второй узел ускорения 2 и в ячейки 1 третьей строки матри1у 1, в которьк выполняются действия- эналоптчные описанным.

Связь с вькода 33 ячеек первого столбца с соответствующими узлами ускорения необходима для дублирования знака суммируемого (вычитаемого) из ::.чередного остатка делителя, что свя : представлением цифр частного в системе счисления (-1,0, +1).,

В результате последовательного выполнения действий во всех строках ячеек 1 матриц и работы всех узлов ускорения 2, на выходах сборок элементов 4 узлов 2 формируются цифры частного, которые промежуточно представлены в системе счисления (-1,0+ +). Значения этих цифр поступают в строку элементов равнозначности 6 и строку одноразрядных сумматоров 7, где происходит преобразование в систему счисления (0,1). Это осуществляется путем формирования двух кодов, первьй из которых включает все цифры частного, равные , а второй - все цифры, равные О и -1,с последующим вычитанием второго кода из первого. Код результата формируется на выходах 12, подключенных к выходам суммы сумматоров 7.

25 зр

40

45

римечание. Прочерк указывает на отсутствие как вычитания, так и суммирования.

Формула

5

3 о

бретения

Матричное устройство для деления, содержащее матрицу ячеек из N строк и М столбцов, каждая из которых содержит одноразрядный сумматор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент И, N узлов ускорения, причем вход переноса одноразрядного сумматора ячейки 1-й строки j-ro столбца матрицы (1 2,3...N, j 3,4, . . М-2) соединел с выходом переноса одноразрядного сумматора ячейки (1 1-й строки) (j+2)-ro столбца матрицы, первый вход одноразрядного сумматора ю-й ячейки первой строки матрицы (т 1,2 .. . М) и первьш вход одноразрядного сумматора i-й ячейки М-го столбца соединены с т-м и с (i+M+l)-M разрядными входами делимого устройства соответственно, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ т-й ячейки каждой строки мат- рицы соединен с т-ым разрядным входом делителя устройства, первый вход

одноразрядного сумматора i-й строки 25 -НЕ и с выходами первого, второго, 1-го столбца (1 3,4,..,,М-1) соеди- третьего и четвертого сумматоров

20 с первым разрядным входом делителя устройства, входы первого, второго третьего и четвертого элемента НЕ узла ускорения соединены с пе вой группой входов элемента 2И-Ш1И

нен с выходом одноразрядного сумматора (i-l)-й ячейки (1+1)-го столбца матрицы, входы переноса одноразрядньпс сумматоров К-х ячеек (К 1,2,,..,М-2) зо первой строки матрицы и входы переноса одноразрядных сумматоров ячеек - (M-l.)-ro столбца каждой строки мат-, рицы соединены с шиной логического нуля, отличающееся тем, что, с целью сокращения аппаратурных затрат, оно содержит группу из N

35

этого узла ускорения соответственно, вькоды первого, второго, третьего и четвертого элементов НЕ п-го узла ускорения соединены с второй группой. Входов элемента 2И-ШШ-НЕ этого же узла ускорения, первый и второй входы р-го одноразрядного сумматора п-го узла ускорения (р 2,3,4) соединены соответственно с выходами одноразрядного сумматора (р-1)-й ячейки и выходами переноса р-й ячейки п-й строки матрицы, выход переноса р-го одноразрядного сумматора п-го

элементов И, группу из N элементов равнозначности и группу из W одноразрядных сумматоров, элемент ИСКЛЮЧАЮ- да УЗла ускорения соединен с входом це- ЩЕЕ ЕЛИ, элемент НЕ, причем каждый реноса (р-1)-го одноразрядного сум- узел ускорения содержит пять одноразрядных сумматоров, четыре элемен- . та НЕ, элемент 2И-ИЛИ-НЕ и элемент

матора этого же узла ускорения, первый вход первого одноразрядного сумматора п-го узла ускорения соединен

равнозначности, причем выход элемен- с выходом пятого одноразрядного сумта ИСКЛЮЧАЮЩЕЕ ИЛИ каждой ячейки матрицы соединен с первым входом элемента И этой же ячейки, выход которого соединен с вторым ;входом однорааряд- ного сумматора этой же ячейки, выход JQ элемента 2И-ШШ-НЕ (i-l)-ro узла ускорения соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ каждой ячейки i-й строки матрицы, первым входом (i-l)-fo элемента равнозначности группы и первым входом эле- мента И группы, выход элемента 2И-ИПИ-НЕ N-ro узла ускорения соединен с первым входом N-ro элемента

матора этого же узла ускорения, первый вход и вход переноса которого соединены соответственно с выходом элемента И и выходом переноса одноразрядного сумматора первой ячейки п-й строки матрицы, первые входы одноразрядных сумматоров первой и второй ячеек i-й строки матрицы соединены соответственно с выходами третьего и четвертого одноразрядных сумматоров (i-l)-ro узла ускорения, второй вход пятого одноразрядного сумматора i-ro узла ускорения соединен с выходом второго одноразрядного

t247863

-НЕ и с выходами первого, второго, третьего и четвертого сумматоров

равнозначности группы, выход элемента равнозначности (i-l)-ro узла ускорения соединен с вторым входом элемента ИСКПЮ ШОЩЕЕ ИЛИ каждой ячей- ки i-й строки матрицы, с вторь 1М входом элемента равнозначности группы, с первым входом (i-l)-ro одноразрядного сумматора группы и вторым входом i-ro элемента И группы, выход .

элемента равнозначности N-ro узла ускорения соединен с вторым входом N-ro элемента равнозначности группы и первым входом N-ro одноразрядного сумматора группы, вьсход п-го элемента И группы (п 1,2,...,N) соединен с входом переноса одноразрядного сумматора п-й ячейки М-го столбца матрицы, первый вход элемента равнозначности п-го узла ускорения соединен

с первым разрядным входом делителя устройства, входы первого, второго, третьего и четвертого элемента НЕ узла ускорения соединены с первой группой входов элемента 2И-Ш1И

этого узла ускорения соответственно, вькоды первого, второго, третьего и четвертого элементов НЕ п-го узла ускорения соединены с второй группой. Входов элемента 2И-ШШ-НЕ этого же узла ускорения, первый и второй входы р-го одноразрядного сумматора п-го узла ускорения (р 2,3,4) соединены соответственно с выходами одноразрядного сумматора (р-1)-й ячейки и выходами переноса р-й ячейки п-й строки матрицы, выход переноса р-го одноразрядного сумматора п-го

УЗла ускорения соединен с входом це- реноса (р-1)-го одноразрядного сум-

УЗла ускорения соединен с входом це- реноса (р-1)-го одноразрядного сум-

матора этого же узла ускорения, первый вход первого одноразрядного сумматора п-го узла ускорения соединен

матора этого же узла ускорения, первый вход и вход переноса которого соединены соответственно с выходом элемента И и выходом переноса одноразрядного сумматора первой ячейки п-й строки матрицы, первые входы одноразрядных сумматоров первой и второй ячеек i-й строки матрицы соединены соответственно с выходами третьего и четвертого одноразрядных сумматоров (i-l)-ro узла ускорения, второй вход пятого одноразрядного сумматора i-ro узла ускорения соединен с выходом второго одноразрядного

сумматора (i-l)-ro узла ускорения, первый и второй входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединены с первыми разрядными входами делимого и делителя устройства, выход элемента ИСКЛЮЧА 0- ЩЕЕ ИЛИ соединен с входом элемента НЕ и является первым разрядным выходом устройств.а, выход элемента НЕ соединен с вторыми входами элементов ИС12

КЛЮЧМТЩЕЕ 1ШИ всех ячеек первой стро- ю с шиной логической единицы, выход

ки матрицы и первым входом первого элемента И группы, второй вход пятого одноразрядного сумматора первого узла ускорения соединен с первым раз- рядным входом делимого устройства, вход переноса одноразрядного сумматора каждой ячейки первой строки матрицы, кроме М-й ячейки этой строки, вход переноса четвертого одноразряд- Hdro сумматора каждого узла ускоре- НИН, вход переноса одноразрядного

1247863

сумматора первой и второй ячеек

I -.

каждой строки матрицы, второй вход

первого одноразрядного сумматора каждого узла ускорения соединены с шиной логического нуля, вторые входы элементов И ячеек первой строки матрицы, второй.вход первого элемента И группы, вход переноса N-ro одноразрядного сумматора группы объединены

п-го элемента равнозначности группы соединен с вторым входом п-го одноразрядного сумматора группы, выход переноса i-ro одноразрядного сумматора группы соединен с входом переносу (i-l)-ro одноразрядного сумматора группы, выход п-го одноразрядного сумматора группы соединен (п+1) разрядным выходом частного устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричное вычислительное устройство | 1988 |

|

SU1541599A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1149245A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1984 |

|

SU1171787A1 |

| Матричное устройство для деления | 1987 |

|

SU1462297A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1034032A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Устройство для умножения | 1980 |

|

SU1001803A1 |

| Матричное вычислительное устройство | 1983 |

|

SU1124284A1 |

| Вычислительное устройство | 1982 |

|

SU1164697A1 |

Изобретение относится к вычислительной технике и может быть.ис пользовано в быстродействующих вычислителях и ЭВМ для выполнения деления в дополнительных кодах. Целью изобретения является сокращение аппаратурных затрат. Поставленная цель достигается сокращением объема схем, каждая из которых в устройстве определяет знак очередного остатка, при зтом очередные остатки представлены.двумя кодами: кодом поразрядных сумм и кодом поразрядных переносов. Сокращение этих схем достигнуто переходом к анализу четырех старших разрядов кодов поразрядных сумм и поразрядных переносов. В устройстве эту функцию выполняют узлы ускорения, которые остаются неизменными с увеличением роста разрядности операндов. 3 ил. 2 SS (Л tc 4 00 о: со

о О о ° 0 „да

о Ю о10 ) W 1)10

Фи. 1

. г

35

| Карцев М.А | |||

| и Брик В.А | |||

| Вычислительные системы и синхронная арифметика | |||

| М.: Радио и связь, 1981, с.238, рис.5.4.1 | |||

| Матричное устройство для деления /его варианты/ | 1981 |

|

SU1035602A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Карцев М.А | |||

| и Брик В.А | |||

| Вычисли- | |||

| тельные системы и синхронная арифметика | |||

| М.: Радио и связь, 1981, с.239,, рис.5.4.3. | |||

Авторы

Даты

1986-07-30—Публикация

1985-02-04—Подача